### 8-bit MCU & LCD Dot Matrix Controller

#### 1. Features

- 8-bit MCU C51 core based (See TEMIC 8-bit Microcontrollers Databook)

- 512 bytes of internal RAM

- 32K bytes of internal ROM/OTP

- Four 8-bit I/O Ports

- Two General Purpose Ports (P0 and P2)

- P0, P1, P2 and P3 can drive LEDs (but 24 max can be used simultaneously)

- Three specific 8-bit Ports

- Two 8-bit Keyboard scan Ports (P5 and P6)

- One specific port (P4)

- 4-bit Keyboard read Port (p4.0 to P4.3)

- 2 comparator input (P4.4 and P4.5)

- 2 general purpose bit (P4.6 and P4.7) which can drive LEDs

- Three 16-bit Timers/Counters

- Timer 0, 1 and 2 of the standard 80C51

- Serial I/O Port (UART)

- Internal Baud Rate Generator

- Power Monitoring and Management

- Double Crystal inputs for speed and low current application

- Dual Data Pointer

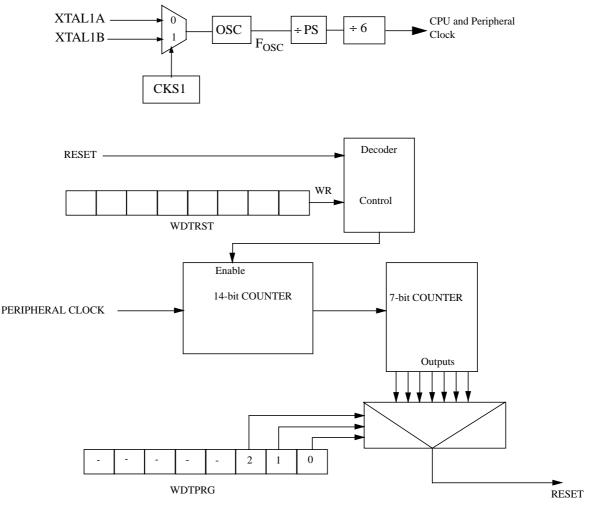

- Watchdog Timer

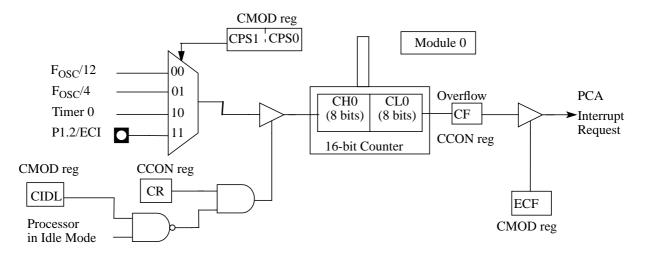

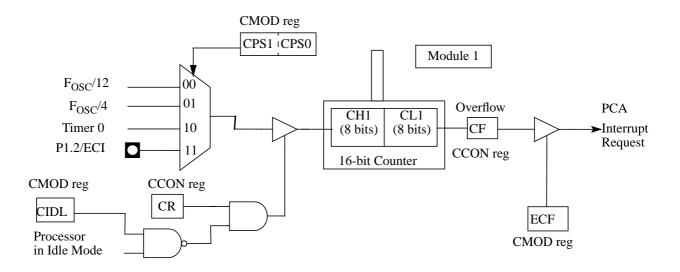

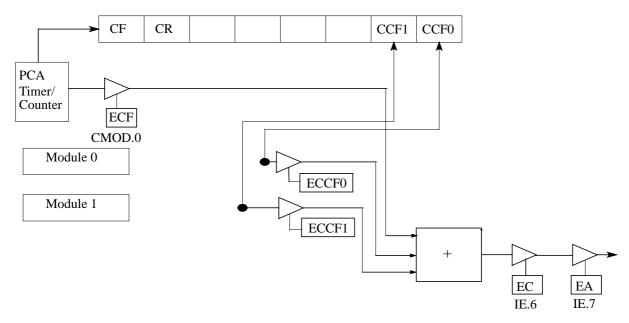

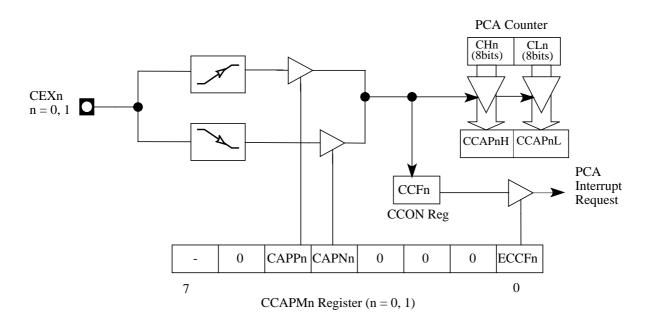

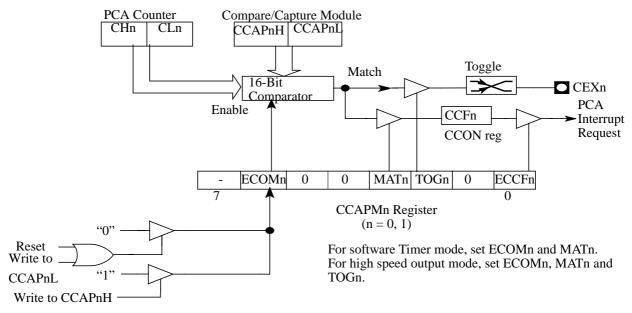

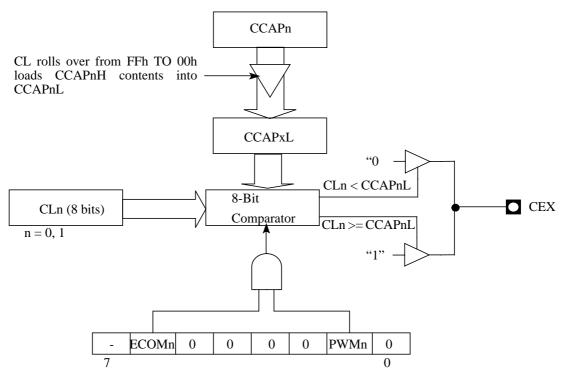

- PCA (2 channels)

- I2C

#### 2. Description

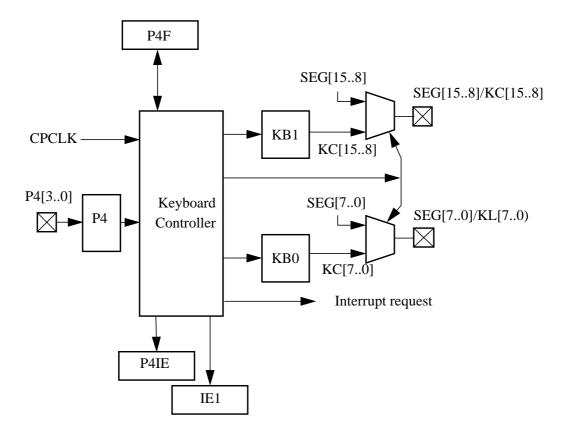

The PAROS is a display oriented microcontroller based on a C51 compatible core including a LCD display controller/driver, keyboard control and LED drivers.

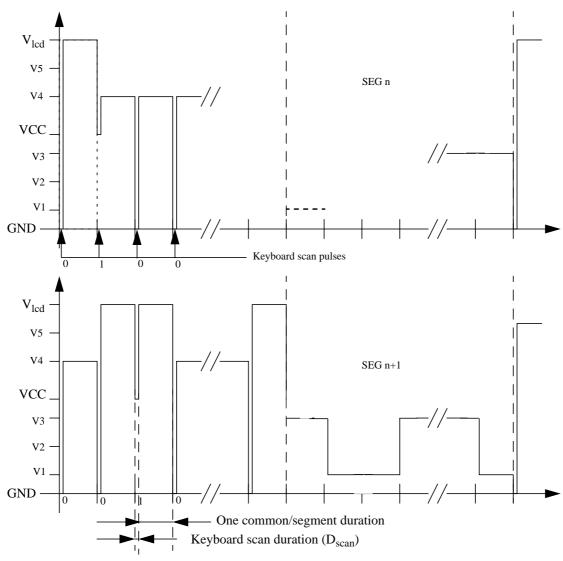

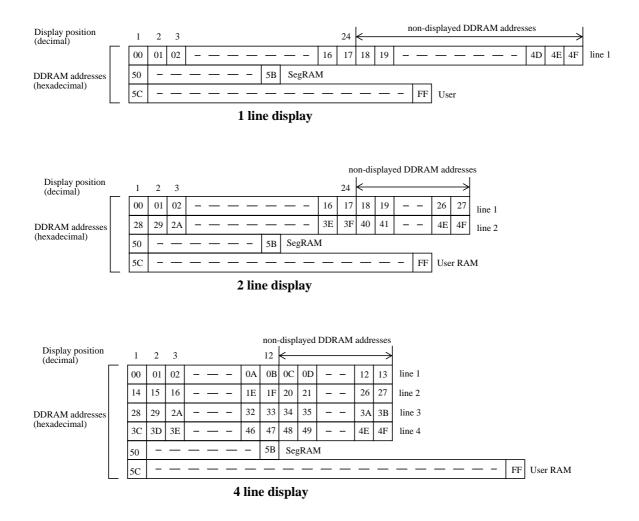

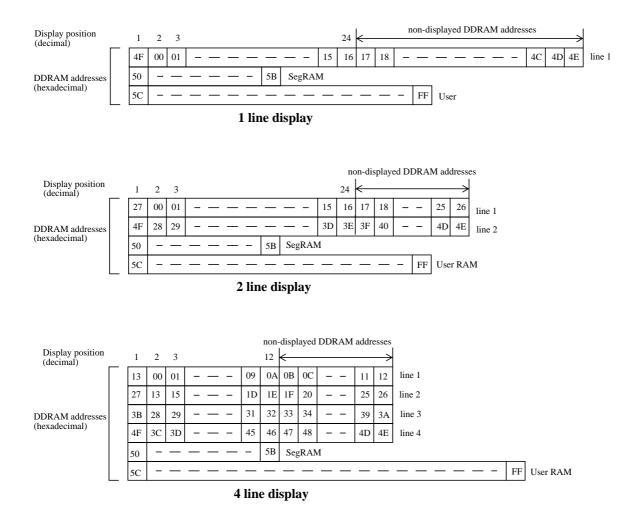

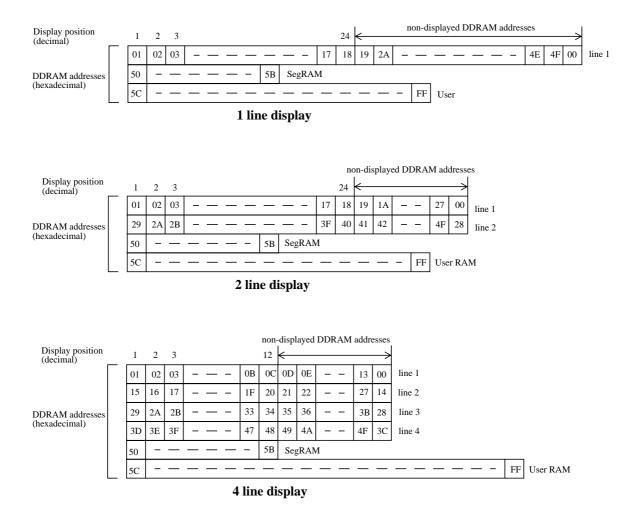

The PAROS provides all features for most embedded applications needing low-power LCD controller and driver designed to drive a split screen dot matrix LCD display of 1 or 2 lines by 24 characters, or 2 or 4 lines by 12 characters with 5x8 dot format. All necessary functions for the LCD display are provided by this component with a combined LCD/Keyboard scan port

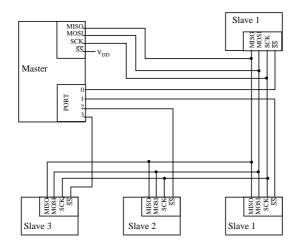

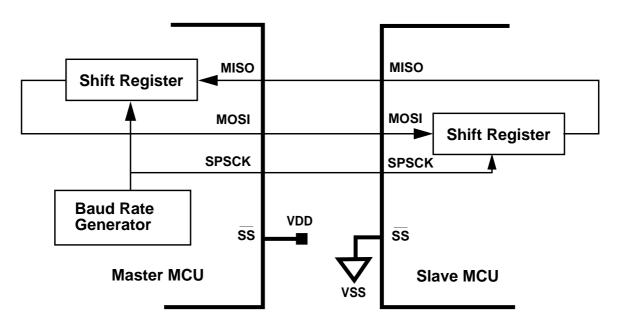

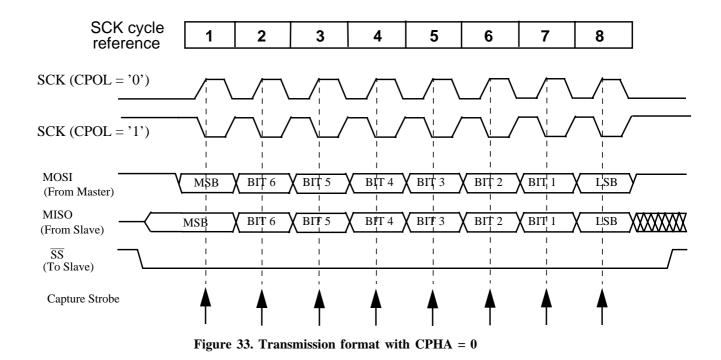

- SPI

- Master/Slave mode

- LCD Display Controller Driver

- Capable of displaying 1 line or 2 lines of up to 24 characters, or 2 or 4 lines of up to 12 characters

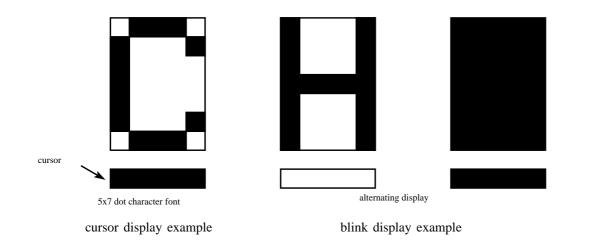

- 5x7 character format plus cursor; 5x8 for kana and user defined symbols

- 60 segments, 34 commons and 60 icons

- Direct programming of the special character patterns by Character Generator RAM

- Character Generator RAM : 1024 bits (16 characters)

- Character Generator ROM : 9600 bits (240 characters)

- Display Data RAM : 640 bits (80 characters)

- Segment Data RAM : 128 bits (60 icons max)

- Mux rate 1:17 and 1:33

- Programmable LCD voltage

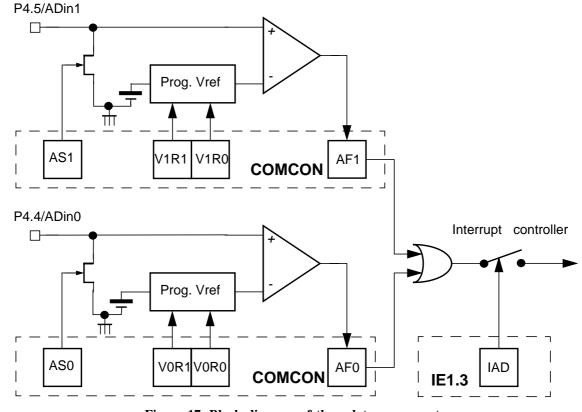

- 2 Voltage comparators e.g. for LCD voltage adaption to temperature variations

- LCD active in power save mode

- Power fail management

- Up to 33MHz at 5V±10% and Up to 12MHz at 3V ±10%

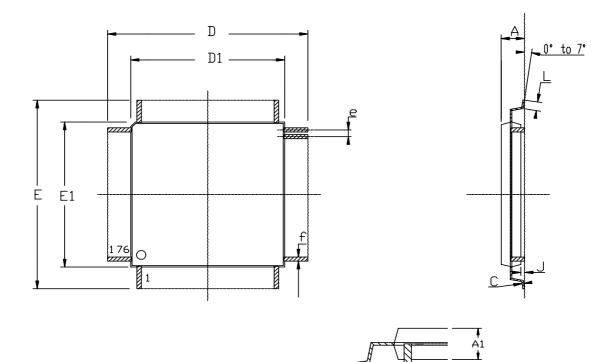

- Die form and TQFP176 package

- Power supply  $V_{DD}$ :  $3V\pm10\%$  to  $5V\pm10\%$

- Temperature range: commercial (0 to 70 °C)

and up to 34 LED drives. For acoustical signals, the buzzer function is programmable in a wide frequency range. All LED drives support 10mA sink current.

Large applications can also be designed with Paros like portable equipments thanks to its low power consumption capability and its "on-board" features like timers and general purpose I/Os. A Clock switching mechanism to the second low frequency oscillator e.g. 32KHz during idle mode permits to minimize current consumption while the MCU is running. To save more power, the Power-down mode can be also selected i.e. in this

configuration the clock is only provided to the LCD controller. It is possible to stop the Power-down mode by an external interrupt or by a keyboard interrupt.

Three serial interfaces are available to communicate with other applications: the standard USART which can handle a large panel of baud rates with its own baud rate generator and the SPI and I2C able to act as slave or master.

#### 3. alias SFR Mapping

The Special Function Registers (SFRs) of the PAROS belongs to the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3, P4, KB0, KB1

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON, BRL, BDRCON

- Power and clock control registers: CKSEL, OSCCON, PCON, CKRL

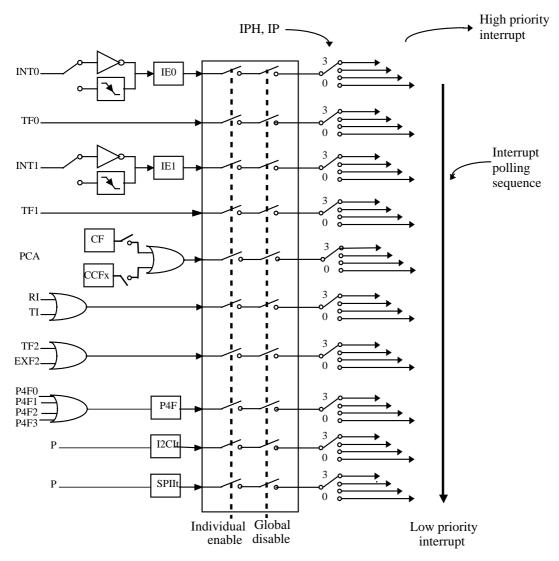

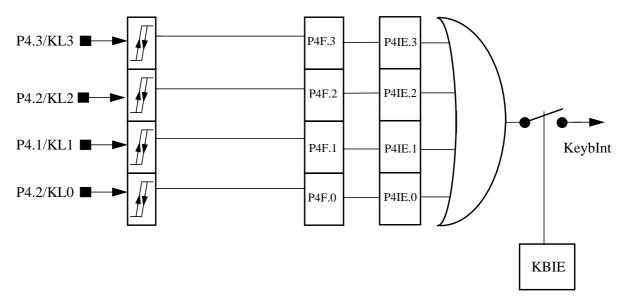

- Interrupt system registers: IE, IE1, IPL0, IPL1, IPH0, IPH1, P4F, P4IE

- WatchDog Timer: WDTRST, WDTPRG

- LCD Controller: LCDCON, LCDAC, LCDIR, LCDDR, LCDPS

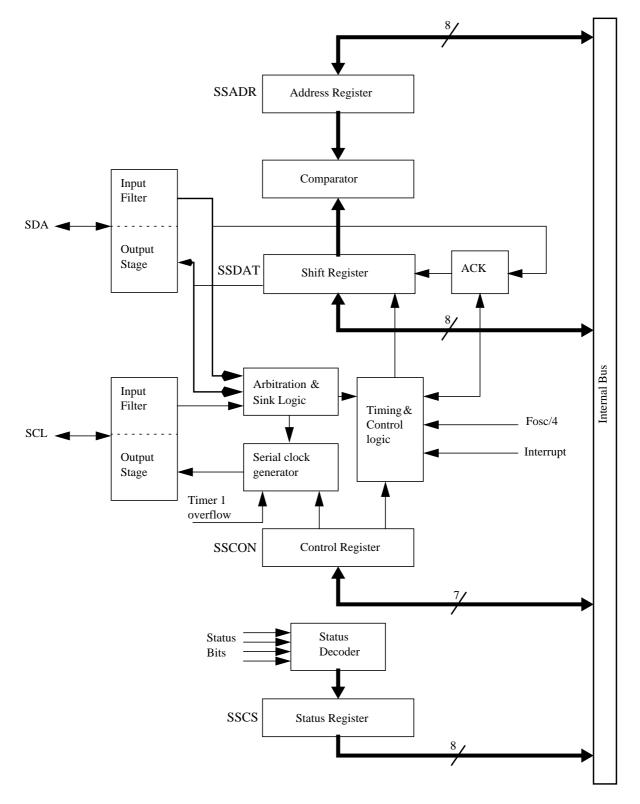

- I2C: SSCON, SSCS, SSDAT, SSADR

- SPI: SPCR, SPSCR, SPDR

- PCA: CCAP0L, CCAP1L, CCAP0H, CCAP1H, CCAPM0, CCAPM1, CL, CH, CMOD, CCON

- Others: AUXR, AUXR1, COMCON

|             |                     |                    | Table 1.            | SFR Addres          | ses and Res        | et Values          |                     |                     |

|-------------|---------------------|--------------------|---------------------|---------------------|--------------------|--------------------|---------------------|---------------------|

|             | 0/8                 | 1/9                | 2/A                 | 3/B                 | <i>4/C</i>         | 5/D                | 6/E                 | 7/F                 |

| F8h         | KB1/P6<br>1111 1111 | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX |                    |                    |                     |                     |

| F0h         | B<br>0000 0000      |                    |                     |                     |                    |                    |                     |                     |

| E8h         | KB0/P5<br>1111 1111 | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX |                    |                    |                     |                     |

| E0h         | ACC<br>0000 0000    |                    |                     | LCDCON<br>0000 0000 | LCDPS<br>0000 0000 | LCDAC<br>0000 0000 | LCDIR<br>0000 0000  | LCDDR<br>0000 0000  |

| D8h         | CCON<br>00XX XX00   | CMOD<br>0XXX X000  | CCAPM0<br>0000 0000 | CCAPM1<br>0000 0000 |                    |                    |                     |                     |

| D0h         | PSW<br>0000 0000    |                    |                     |                     |                    |                    |                     |                     |

| C8h         | T2CON<br>0000 0000  | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000   | TH2<br>0000 0000   |                     |                     |

| C0h         | IE1<br>XXXX X000    |                    |                     | SPCR<br>0001 0100   | SPSCR<br>0000 0000 | SPDR<br>XXXX XXXX  |                     |                     |

| B8h         | IPL0<br>X000 000    | SADEN<br>0000 0000 |                     |                     |                    |                    |                     |                     |

| B0h         | P3<br>1111 1111     | P4<br>1111 111     | IPL1<br>XXXX X000   | IPH1<br>XXXX X000   |                    |                    |                     | IPH0<br>X000 0000   |

| 4 <i>8h</i> | IE<br>0000 0000     | SADDR<br>0000 0000 |                     |                     |                    |                    |                     |                     |

| 4 <i>0h</i> | P2<br>1111 1111     |                    | AUXR1<br>XXXX XXX0  | COMCON<br>0100 0100 |                    |                    | WDRST<br>0000 0000  | WDTPRG<br>0000 0000 |

| 98h         | SCON<br>0000 0000   | SBUF<br>XXXX XXXX  | BRL<br>0000 0000    | BDRCON<br>0XXX 0000 |                    | P4IE<br>XXXX 0000  | P4F<br>XXXX 0000    |                     |

| 90h         | P1<br>1111 1111     |                    |                     | SSCON<br>0000 0000  | SSCS<br>1111 1000  | SSDAT<br>1111 1111 | SSADR<br>1111 1110  | CKRL<br>1111 1111   |

| 88h         | TCON<br>0000 0000   | TMOD<br>0000 0000  | TL0<br>0000 0000    | TL1<br>0000 0000    | TH0<br>0000 0000   | TH1<br>0000 0000   | AUXR<br>XXXX XXX0   |                     |

| 80h         | P0<br>1111 1111     | SP<br>0000 0111    | DPL<br>0000 0000    | DPH<br>0000 0000    |                    | CKSEL<br>XXXX X000 | OSCCON<br>XXXX X001 | PCON<br>00X1 0000   |

|             | 0/8                 | 1/9                | 2/A                 | 3/B                 | 4/C                | 5/D                | 6/E                 | 7/F                 |

#### Table 1. SFR Addresses and Reset Values

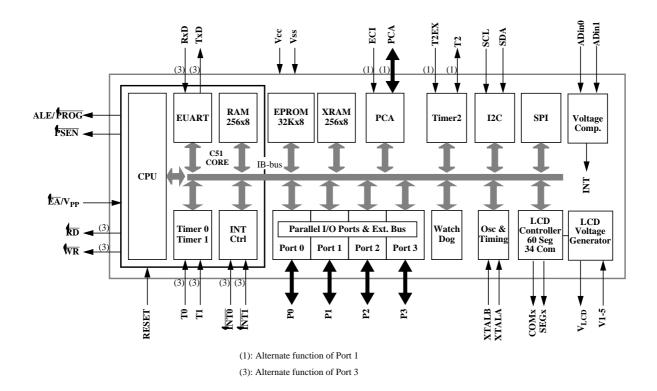

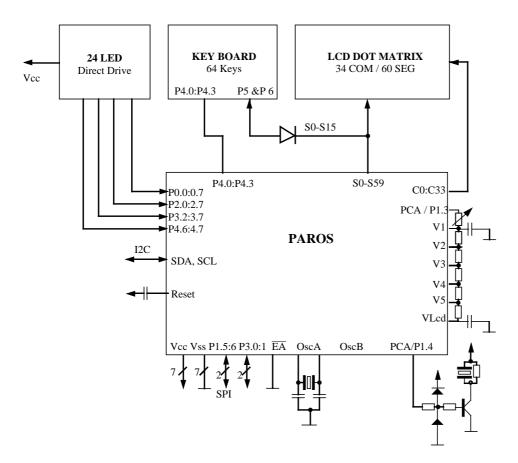

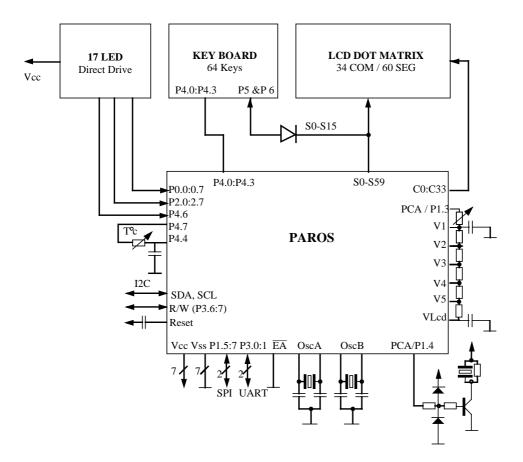

### 4. Block Diagram

Figure 1. Paros Block Diagram

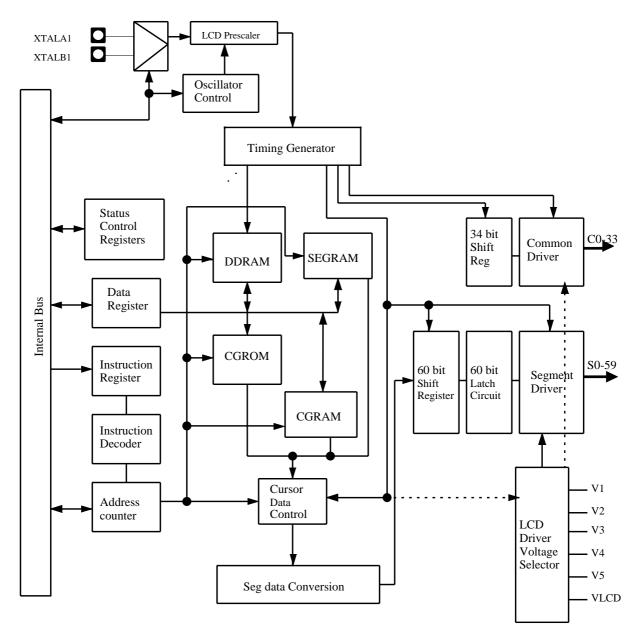

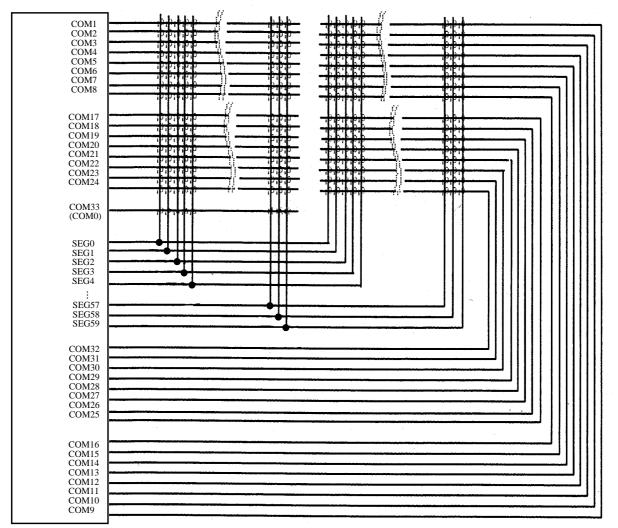

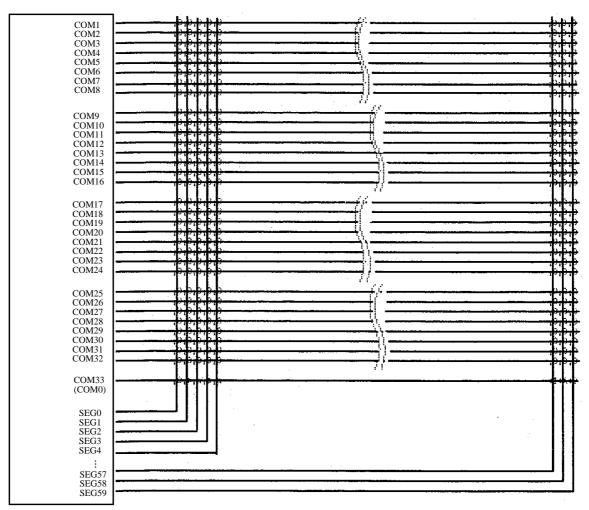

Figure 2. LCD Controller Driver Diagram

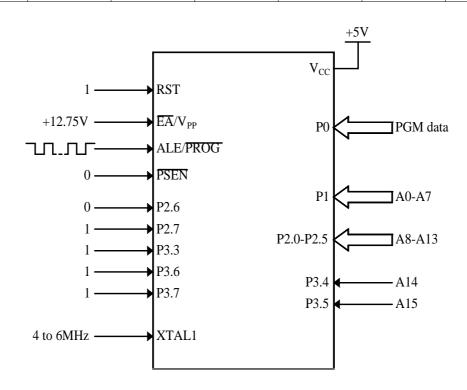

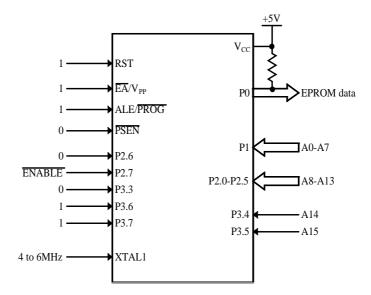

### **5.** Pin Configuration

#### Table 2. Pin Description

| Pin Name    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| VSS         | GND  | Circuit ground potential. (4 Vss buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| VCC         |      | Supply voltage during normal, idle, and power-down operation. (4 Vcc buffers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| V1:5/Vlcd   |      | LCD Voltage Generator and Bias Voltage Inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| P0.0:7      | I/O  | Port 0 is an 8 bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in that state can be used as high-impedance inputs. Port 0 is also the data bus during accesses to external Data Memory. In this application it uses strong internal pull-ups when emitting 1's. Each Port 0 pin can sink 10 mA* for direct drive of LEDs. Port 0 is used as data bus during EPROM programming and program verification                                                                                                                                             |  |  |  |  |  |

|             |      | Port 1 is an 8 bit bi-directional I/O port with internal pull-ups. Port 1 pins that have 1's written to them are pulled high by the internal pull-ups, and in that state can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL, in the DC section) because of the internal pull-ups. Port 1 can sink /source 3 LS TTL inputs. It can drive CMOS inputs without external pull-ups. Port 1 can sink 10 mA* on each pin for direct drive of LED. Port1 also serves the functions of the following special features of Paros as listed below: |  |  |  |  |  |

| P1.0:7      | I/O  | Port PinAlternate FunctionP1.0T2Timer/Counter 2 external count input/clockoutP1.1T2EX/SSTimer/Counter 2 reload/capture/direction control/ SPI Slave Selection.SS = 0 slave, $\overline{SS} = 1$ masterP1.2ECIExternal Counter Input for PCA module                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|             |      | P1.3       CEX0       Compare/Capture Input for module 0         P1.4       CEX1/       Compare/Capture Input for module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|             |      | <ul> <li>P1.5 MISO SPI master input Slave output</li> <li>P1.6 SPSCK clock/SPI &amp; serial clock, output for master, input for slave.</li> <li>P1.7 MOSI synchronous serial link data &amp; SPI master output, Slave Input</li> <li>Port 1 receives the low-order address byte during EPROM programming and program verification.</li> </ul>                                                                                                                                                                                                                                                   |  |  |  |  |  |

| P2.0:7      | I/O  | Port 2 is an 8 bit bi-directional I/O port with internal pull-ups. Port 2 pins that have 1's written to them are pulled high by the internal pull-ups, and in that state can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current ( $I_{IL}$ , in the DC section) because of the internal pull-ups. Port 2 can sink 10 mA* on each pin for direct drive of LED. It can drive CMOS inputs without external pull-ups. Some Port 2 pins receive the high-order address bits and control signals during EPROM programming and program verification.   |  |  |  |  |  |

|             |      | Port 3 is an 8 bit bi-directional I/O port with internal pull-ups. Port 3 pins that have 1's written to them are pulled high by the internal pull-ups, and in that state can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current ( $I_{IL}$ , in the DC section) because of the pull-ups. Port 3 can sink 10 mA* on each pin for direct drive of LED. Port 3 also serves the functions of various special features of the TEMIC's C51 Family, as listed below:                                                                                   |  |  |  |  |  |

| P3.0:7      | I/O  | Port Pin       Alternate Function         P3.0       RxD       Serial port input         P3.1       TxD       Serial port output         P3.2       INT0       (external interrupt 0)         P3.3       INT1       (external interrupt 1)         P3.4       T0       timer 0 external input         P3.5       T1       timer 1 external input         P3.6       WR       external Data Memory write strobe         P3.7       RD       external Data Memory read strobe         Port 3 can sink/source three LS TTL inputs. It can drive CMOS inputs without external pull-ups. Some Port   |  |  |  |  |  |

| P4.0:7      | I/O  | <ul> <li>Port 3 can shirk source three LS TTE inputs, it can urve CMOS inputs without external pun-ups, some Port 3 pins receive control signals during EPROM programming and program verification.</li> <li>Port 4 is a specific port.</li> <li>P4.0 to 4.3: Keyboard controller with interrupt capability</li> <li>P4.4 and P4.5: comparator input</li> <li>P4.6 and P4.7: 2 general purpose specially designed to strongly drive important loads and to be able to provide</li> </ul>                                                                                                        |  |  |  |  |  |

|             |      | up to 10mA* per port bit line. The pins that have 1's written to them are pulled high by the internal pull-ups, and in that state can be used as inputs. As inputs, Port 4 pins that are externally being pulled low will source current (IIL, in the DC section) because of the pull-ups.                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| P5.0:7/S0:7 | 0    | Port 5 is an 8 bit Output port dedicated for Keyboard scan. Port 5 is also multiplexed with the LCD Segment control S0-S7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

#### Table 2. Pin Description

| Pin Name     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6.0:7/S8:15 | 0    | Port 6 is an 8 bit Output port dedicated for Keyboard scan. Port 6 is also multiplexed with the LCD Segment control S8-S15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| S16:S59      | 0    | Dedicated LCD Segment driver for Segments S16 to S59.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| C0:33        | 0    | Dedicated LCD Common driver for Commons C0:33.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

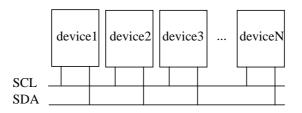

| SCL          | I/O  | I2C Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SDA          | I/O  | I2C Serial Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RST          | I    | A high level on this pin for two machine cycles while the oscillator is running resets the device. An internal pull-down resistor permits Power-on reset using only a capacitor connected to $V_{CC}$ . The port pins will be driven to their reset condition when a minimum $V_{IH1}$ voltage is applied whether the oscillator is started or not (asynchronous reset).                                                                                                                                                                                                                                                                                                                                                                            |

| ALE/PROG     | I/O  | Address Latch Enable output for latching the low byte of the address during accesses to external memory. ALE is activated as though for this purpose at a constant rate of 1/6 the oscillator frequency except during an external data memory access at which time one ALE pulse is skipped. ALE can sink/source 8 LS TTL inputs. It can drive CMOS inputs without external pull-up. If desired, to reduce EMI, ALE operation can be disabled by setting bit 0 of SFR location 8Eh (AUXR). With this bit set, the pin is weakly pulled high. However, ALE remains active during MOVX, MOVC instructions and external fetches. Setting the ALE disable bit has no effect if the microcontroller is in external execution mode ( $\overline{EA}$ =0). |

| PSEN         | 0    | Program Store Enable output is the read strobe to external Program Memory. PSEN is activated twice each machine cycle during fetches from external Program Memory. (However, when executing out of external Program Memory, two activations of <u>PSEN</u> are skipped during each access to external Data Memory). <u>PSEN</u> is not activated during fetches from internal Program Memory. <u>PSEN</u> can sink/source 8 LS TTL inputs. It can drive CMOS inputs without an external pull-up.                                                                                                                                                                                                                                                    |

| ĒA/VPP       | I/O  | External Access enable. EA must be strapped to VSS in order to enable the device to fetch code from external Program Memory locations 0000h to FFFFh. Note however, that if any of the Security bits are programmed, $\overline{EA}$ will be internally latched on reset. $\overline{EA}$ should be strapped to V <sub>CC</sub> for internal program execution. This pin also receives the programming supply voltage (VPP) during EPROM programming.                                                                                                                                                                                                                                                                                               |

| XTALA1       | I    | Input to the inverting amplifier that forms the oscillator. Receives the external oscillator signal when an external oscillator is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| XTALA2       | 0    | Output from the inverting amplifier that forms the oscillator. This pin should be floated when an external oscillator is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XTALB1       | Ι    | Input to the inverting amplifier that forms the oscillator. Receives the second external oscillator signal when a second external oscillator is used to minimize consumption in Idle mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| XTALB2       | 0    | Output from the inverting amplifier that forms the second oscillator. This pin should be floated when an external oscillator is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

\* Maximal 24 LEDs are permitted and max. 4 can be switched by the same instruction.

# PAROS

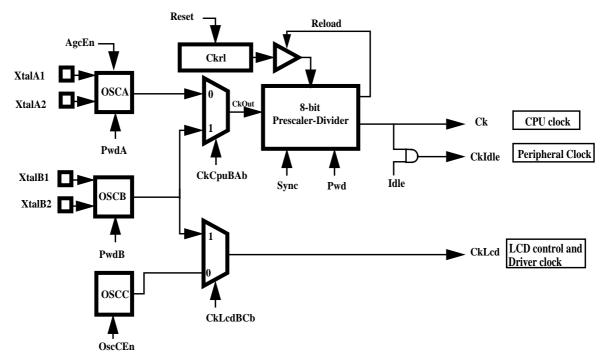

#### 6. CLOCK

#### 6.1 Overview

This core is monophase, edge sensitive . Two oscillators are available for CPU :

- OSCA used for high frequency : Upto 33MHZ @5V +/- 10%

- OSCB used for slow frequency : 32.768KHZ

Several operating modes are available and programmable by software :

- to switch for OSCA to OSCB and vice-versa

- to stop OSCA and/or OSCB to reduce consumption

In order to optimize the power consumption and the execution time needed for a specific task, an internal prescaler feature has been implemented between the selected oscillator and the CPU.

A third oscillator OSCC (internal) is dedicated for display controller only and can be switched off by software too.

#### 6.2 Registers :

#### Table 3. CKSEL (85h) Reset value : XXXXX100b Located in MISC block

| Located in Milbe block |   |   |   |   |      |      |      |  |  |

|------------------------|---|---|---|---|------|------|------|--|--|

| 7                      | 6 | 5 | 4 | 3 | 2    | 1    | 0    |  |  |

| -                      | - | - | - | - | RSTD | CKS1 | CKS0 |  |  |

| Bit Number | Mnemonic | Description                                                                                                                                                                                                        |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          |          | Reserved                                                                                                                                                                                                           |

| 6          |          | Reserved                                                                                                                                                                                                           |

| 5          |          | Reserved                                                                                                                                                                                                           |

| 4          |          | Reserved                                                                                                                                                                                                           |

| 3          |          | Reserved                                                                                                                                                                                                           |

| 2          | RSTD     | Reset Detector Disable Bit                                                                                                                                                                                         |

| 1          | CKS1     | Cpu Ocillator Select Bit : (CkCpuBAb)<br>When cleared, Cpu and peripherals connected to OSCA<br>When set, Cpu and peripherals connected to OSCB<br>Cleared by hardware after a Power-up (OSCA selected by default) |

| 0          | CKS0     | Cpu Ocillator Select Bit : (CkCpuBCb)<br>When cleared, LCD controller connected to OSCC<br>When set, LCD controller connected to OSCB<br>Cleared by hardware after a Power-up (OSCC selected by default)           |

#### Table 4. OSCCON (86h):

Reset value : XXXXX001b

| 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0      |

|---|---|---|---|---|--------|--------|--------|

| - | - | - | - | - | OscCEn | OscBEn | OscAEn |

| Bit Number | Mnemonic | Description                                                                                                                |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------|

| 7          |          | Reserved                                                                                                                   |

| 6          |          | Reserved                                                                                                                   |

| 5          |          | Reserved                                                                                                                   |

| 4          |          | Reserved                                                                                                                   |

| 3          |          | Reserved                                                                                                                   |

| 2          | OscCEn   | OscC enable bit<br>Set by software to run OscC<br>Cleared by software to stop OscC<br>Cleared by hardware after a Power-up |

| 1          | OscBEn   | OscB enable bit<br>Set by software to run OscB<br>Cleared by software to stop OscB<br>Cleared by hardware after a Power-up |

| 0          | OscAEn   | OscA enable bit<br>Set by software to run OscA<br>Cleared by software to stop OscA<br>Set by hardware after a Power-up     |

### Table 5. CKRL (97h)Reset value : 11111111b

|   | Reset value . IIIIIIII |   |   |   |   |   |   |  |  |  |

|---|------------------------|---|---|---|---|---|---|--|--|--|

| 7 | 6                      | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

| - | -                      | - | - | - | - | - | - |  |  |  |

| Bit Number | Mnemonic | Description                                |

|------------|----------|--------------------------------------------|

| 7:0        | CKRL     | Clock Reload Register :<br>Prescaler value |

#### Table 6. PCON Register

#### PCON - Power Control Register (87h)

| 7             | 6               | 5                     | 4                                                                                                                                                   | 2   | 1   | 0  |     |  |  |  |

|---------------|-----------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|-----|--|--|--|

| SMOD1         | SMOD            | -                     | POF                                                                                                                                                 | GF1 | GF0 | PD | IDL |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                       | Description                                                                                                                                         |     |     |    |     |  |  |  |

| 7             | SMOD1           |                       | Example 2 Set to select double baud rate in mode 1, 2 or 3.                                                                                         |     |     |    |     |  |  |  |

| 6             | SMOD0           | Clear to se           | erial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register.                                     |     |     |    |     |  |  |  |

| 5             | -               | Reserved<br>The value | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                                                     |     |     |    |     |  |  |  |

| 4             | POF             |                       | Power-Off Flag<br>Clear to recognize next reset type.<br>Set by hardware when VCC rises from 0 to its nominal voltage. Can also be set by software. |     |     |    |     |  |  |  |

| 3             | GF1             |                       | F <b>lag</b><br>v user for general p<br>r for general purpo                                                                                         |     |     |    |     |  |  |  |

| 2             | GF0             | Cleared by            | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.                                        |     |     |    |     |  |  |  |

| 1             | PD              | Cleared by            | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                      |     |     |    |     |  |  |  |

| 0             | IDL             | -                     | Idle mode bit<br>Clear by hardware when interrupt or reset occurs.<br>Set to enter idle mode.                                                       |     |     |    |     |  |  |  |

Reset Value = 00X1 0000b Not bit addressable

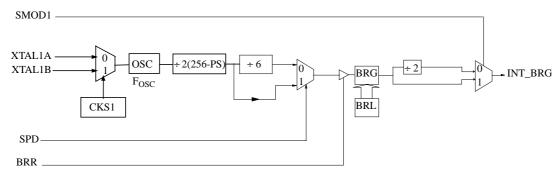

#### 6.3 Functional Block diagram

Figure 3. Functional block diagram

#### 6.4 Operating modes

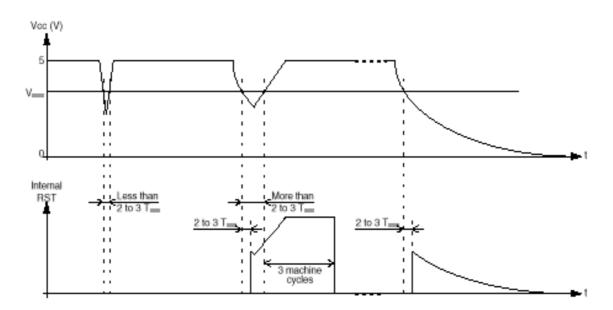

#### 6.4.1 Reset

- An hardware RESET put the Clock generator in the following state :

- OscAEn = 1 & OscBEn = 0: OscA is running, OSCB is stopped .

- OscCEn = 1: OSCC is stopped .

- CkCpuBAb = 0 : OSCA is selected for CPU .

- CkLcdBCb = 0: OSCC is selected for LCD controller.

- Sync signal is used for tester synchronization and provided by the dedicated test mode .

#### 6.4.2 Functional modes :

#### 6.4.2.1 NORMAL MODES :

- CPU and Peripherics clock depend on the software selection using CKCON and CKRL registers

- CkCpuBAb bit selects either OSCA or OSCB

- CKRL register determines the frequency of the selected clock

- It is always possible to switch dynamicly by software from OSCA to OSCB, and vice versa by changing CkCpuBAb bit, a synchronization cell allowing to avoid any spike during transition.

#### 6.4.2.2 IDLE MODES :

- IDLE modes are achieved by using any instruction that writes into PCON.0 sfr

- IDLE modes A and B depend on previous software sequence, prior to writing into PCON.0 register :

# PAROS

- IDLE MODE A : OSCA is running (OscAEn = 1) and selected (CkCpuBAb = 0)

- IDLE MODE B: OSCB is running (OscBEn = 1) and selected (CkCpuBAb = 1)

- The unused oscillator OSCA or OSCB can be stopped by software by clearing OscAEn or OscBEn respectively

- IDLE mode can be canceled either by Reset, or by activation of any enabled interruption

- In both case, PCON.0 is cleared by hardware

- Exit from IDLE modes will leave Ocillators control bits inchanged (OscEnA,OscEnB,CkCpuBAb)

#### 6.4.2.3 POWER DOWN MODES :

- POWER DOWN modes are achieved by using any instruction that writes into PCON.1 sfr

- POWER DOWN modes A and B depend on previous software sequence, prior to writing into PCON.1 register :

- If CkLcdBCb = 1, then only OSCA will be stopped, OSCB can be used by Lcd

- If CkLcdBCb = 0, then both OSCA and OSCB will be stopped, OSCC can be used by Lcd

- POWER DOWN mode can be cancelled either by an harware Reset, by an external interruption, or by the keyboard .

- By ResetB signal : The CPU will restart in NORMAL mode A .

- By interruptions INT0 or INT1 interruptions, if enabled : standard behavorial, request on Pads must be driven low enough to ensure correct restart of the oscillator which was selected when entering in Power down.

- By keyboard in enabled : a hardware clear of the PCON.1 flag ensure the restart of the oscillator which was selected when entering in Power down .

#### 6.4.2.4 Overview :

| PCON.<br>1 | PCON.<br>0 | OscCE<br>n | OscBE<br>n | OscAE<br>n | CkLcd<br>BbC | CkCpu<br>BAb | Selected Mode                  | Comment                                                                               |

|------------|------------|------------|------------|------------|--------------|--------------|--------------------------------|---------------------------------------------------------------------------------------|

| 0          | 0          | Х          | 0          | 1          | Х            | 0            | NORMAL MODE A,<br>OSCB stopped | Default mode after power-up or Warm<br>Reset                                          |

| 0          | 0          | Х          | 1          | 1          | Х            | 0            | NORMAL MODE A,<br>OSCB running | Same + OSCB running                                                                   |

| 0          | 0          | Х          | 1          | 0          | Х            | 1            | NORMAL MODE B,<br>OSCA stopped | OSCB running and selected                                                             |

| 0          | 0          | Х          | 1          | 1          | Х            | 1            | NORMAL MODE B,<br>OSCA running | Same + OSCA running                                                                   |

| X          | X          | Х          | 0          | 0          | Х            | Х            | INVALID                        | OSCA & OSCB cannot be stopped at the same time                                        |

| X          | X          | Х          | Х          | 0          | Х            | 0            | INVALID                        | OSCA must not be stopped, as used for CPU and peripherics                             |

| X          | X          | Х          | 0          | Х          | Х            | 1            | INVALID                        | OSCB must not be stopped as used for CPU and peripherics                              |

| 0          | 1          | Х          | х          | 1          | Х            | 0            | IDLE MODE A                    | The CPU is off, OSCA supplies the<br>peripherics<br>OSCB can be disabled (OscBEn = 0) |

| 0          | 1          | Х          | 1          | Х          | Х            | 1            | IDLE MODE B                    | The CPU is off, OSCB supplies the peripherics,<br>OSCA can be disabled (OscAEn = 0)   |

| 1          | X          | Х          | Х          | 1          | 0            | Х            | POWER DOWN MODE<br>A           | The CPU and peripherics are off, but<br>OSCB is still running for Lcd                 |

| 1          | X          | 0          | Х          | Х          | 1            | Х            | TOTAL POWER DOWN               | The CPU is off, OSCA and OSCB are<br>stopped<br>OSCC in stopped                       |

| 1          | X          | 1          | х          | Х          | 1            | х            | PAUSE                          | The CPU is off, OSCA and OSCB are<br>stopped<br>Lcd is supplied by OSCC               |

| X          | X          | Х          | 0          | Х          | 0            | Х            | INVALID                        | OSCB must not be stopped as used by Lcd                                               |

#### Table 7. Control clocks configurations

#### **6.5 Design considerations**

#### **6.5.1 Oscillators control :**

- PwdOscA and PwdOscB signals are generated in the Clock generator and used to control the hard blocks of oscillators A and B .

- PwdOscA = '1' stops OSCA

- PwdOscB = '1' stops OSCB

- The following tables summarize the 1.6 paragraph concerning Operating modes :

| PCON.1 | OscAEn | PwdOscA | Comments                        |

|--------|--------|---------|---------------------------------|

| 0      | 1      | 0       | OSCA running                    |

| 1      | X      | 1       | OSCA stopped by Power-down mode |

| 0      | 0      | 1       | OSCA stopped by clearing OscAEn |

#### Table 8. OSCA control

|        | Table 9. OSCB control |          |         |                                                                 |  |  |  |  |  |

|--------|-----------------------|----------|---------|-----------------------------------------------------------------|--|--|--|--|--|

| PCON.1 | OscBEn                | CkLcdBCb | PwdOscB | Comments                                                        |  |  |  |  |  |

| 0      | 1                     | Х        | 0       | OSCB running                                                    |  |  |  |  |  |

| 1      | 1                     | 0        | 0       | Although PCON.1 is set, OSCB cannot be stopped , as used by Lcd |  |  |  |  |  |

| 1      | Х                     | 1        | 1       | OSCB stopped by Power-down mode                                 |  |  |  |  |  |

| 0      | 0                     | Х        | 1       | OSCB stopped by clearing OscBEn                                 |  |  |  |  |  |

#### Table 10. OSCC control

| OscCEn | PwdOscC                             | Comments     |

|--------|-------------------------------------|--------------|

| 1      | 0                                   | OSCC running |

| 0      | 0 1 OSCC stopped by clearing OscCEn |              |

#### **6.5.2 Prescaler Divider :**

- An hardware RESET put the precaler divider in the following state :

- CKRL = FFh : internal clock = FoscA/2 (Standard C51 feature)

- CkCpuBAb signal selects OSCA or OSCB : Fosc = FoscA or FoscB

- Any value between FFh downto 00h can be written by software into CKRL sfr in order to divide frequency of the selected oscillator :

- CKRL = 00h : minimum frequency = Fosc/512

- CKRL = FFh : maximum frequency= Fosc/2 (Standard C51 feature)

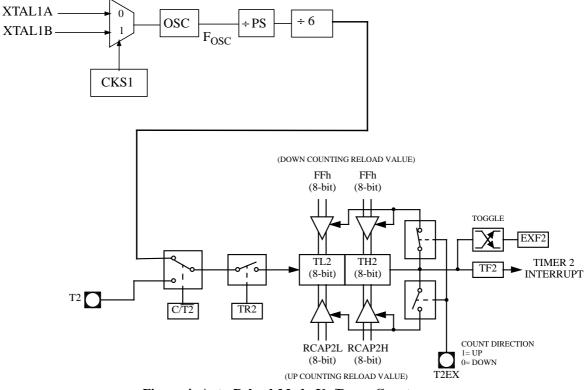

#### 7. Timer 2

The timer 2 in the PAROS is compatible with the timer 2 in the 80C52.

It is a 16-bit timer/counter: the count is maintained by two eight-bit timer registers, TH2 and TL2, connected in cascade. It is controlled by T2CON register (See Table 11.) and T2MOD register (See Table 12.). Timer 2 operation is similar to Timer 0 and Timer 1. C/T2 selects  $F_{OSC}/6$  (timer operation) or external pin T2 (counter operation) as the timer register input. Setting TR2 allows TL2 to be incremented by the selected input.

Timer 2 includes the following enhancements:

- Auto-reload mode (up or down counter)

- Programmable clock-output

#### 7.1 Auto-Reload Mode

The auto-reload mode configures timer 2 as a 16-bit timer or event counter with automatic reload. This feature is controlled by the DCEN bit in T2MOD register (See Table 12.). Setting the DCEN bit enables timer 2 to count up or down as shown in Figure 4. In this mode the T2EX pin controls the direction of count.

When T2EX is high, timer 2 counts up. Timer overflow occurs at FFFFh which sets the TF2 flag and generates an interrupt request. The overflow also causes the 16-bit value in RCAP2H and RCAP2L registers to be loaded into the timer registers TH2 and TL2.

When T2EX is low, timer 2 counts down. Timer underflow occurs when the count in the timer registers TH2 and TL2 equals the value stored in RCAP2H and RCAP2L registers. The underflow sets TF2 flag and reloads FFFFh into the timer registers.

The EXF2 bit toggles when timer 2 overflows or underflows according to the direction of the count. EXF2 does not generate any interrupt. This bit can be used to provide 17-bit resolution.

Figure 4. Auto-Reload Mode Up/Down Counter

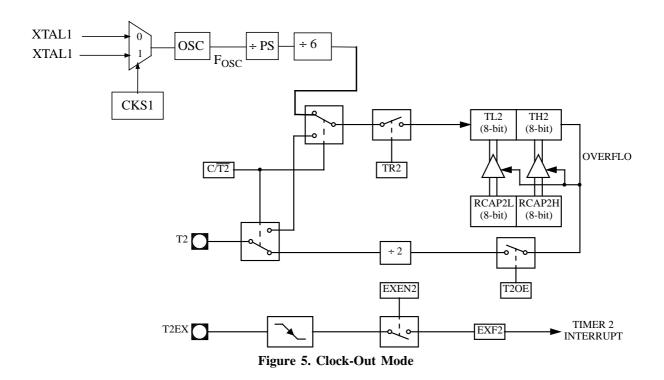

#### 7.2 Programmable Clock-Output

In the clock-out mode, timer 2 operates as a 50%-duty-cycle, programmable clock generator (See Figure 5.) . The input clock increments TL2 at frequency  $F_{OSC}/2$ . The timer repeatedly counts to overflow from a loaded value. At overflow, the contents of RCAP2H and RCAP2L registers are loaded into TH2 and TL2. In this mode, timer 2 overflows do not generate interrupts. The formula gives the clock-out frequency as a function of the system oscillator frequency and the value in the RCAP2H and RCAP2L registers:

$$Clock - OutFrequency = \frac{F_{OSC}}{4 \times (65536 - RCAP2H/(RCAP2L))} \times \frac{1}{(256 - PS)}$$

PS is the oscillator prescalar

For a 16 MHz system clock with Prescalar value PS=255, timer 2 has a programmable frequency range of 61 Hz  $(F_{OSC}/2^{18})$  to 4 MHz  $(F_{OSC}/4)$ . The generated clock signal is brought out to T2 pin (P1.0).

Timer 2 is programmed for the clock-out mode as follows:

- Set T2OE bit in T2MOD register.

- Clear  $C/\overline{T2}$  bit in T2CON register.

- Determine the 16-bit reload value from the formula and enter it in RCAP2H/RCAP2L registers.

- Enter a 16-bit initial value in timer registers TH2/TL2. It can be the same as the reload value or a different one depending on the application.

- To start the timer, set TR2 run control bit in T2CON register.

It is possible to use timer 2 as a baud rate generator and a clock generator simultaneously. For this configuration, the baud rates and clock frequencies are not independent since both functions use the values in the RCAP2H and RCAP2L registers.

PAROS

#### Table 11. T2CON Register

#### T2CON - Timer 2 Control Register (C8h)

| 7             | 6               | 5                                                                                                                                                                                                                                                                                                          | 4                                                                                                                                                                                                                                                           | 3                                           | 2   | 1                     | 0                    |  |  |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|-----------------------|----------------------|--|--|

| TF2           | EXF2            | RCLK                                                                                                                                                                                                                                                                                                       | TCLK                                                                                                                                                                                                                                                        | EXEN2                                       | TR2 | C/T2#                 | CP/RL2#              |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                                                                                                                                                                                                                            | Description                                                                                                                                                                                                                                                 |                                             |     |                       |                      |  |  |

| 7             | TF2             | Cleared by                                                                                                                                                                                                                                                                                                 | Finer 2 overflow Flag           Cleared by hardware when processor vectors to interrupt routine.           Set by hardware on timer 2 overflow.                                                                                                             |                                             |     |                       |                      |  |  |

| 6             | EXF2            | Set when a Set to cause                                                                                                                                                                                                                                                                                    | <b>Fimer 2 External Flag</b><br>Set when a capture or a reload is caused by a negative transition on T2EX pin if EXEN2=1.<br>Set to cause the CPU to vector to timer 2 interrupt routine when timer 2 interrupt is enabled.<br>Must be cleared by software. |                                             |     |                       |                      |  |  |

| 5             | RCLK            | Receive Clock bit<br>Clear to use timer 1 overflow as receive clock for serial port in mode 1 or 3.<br>Set to use timer 2 overflow as receive clock for serial port in mode 1 or 3.                                                                                                                        |                                                                                                                                                                                                                                                             |                                             |     |                       |                      |  |  |

| 4             | TCLK            |                                                                                                                                                                                                                                                                                                            | e timer 1 overflow                                                                                                                                                                                                                                          | v as transmit clock<br>as transmit clock fo |     |                       |                      |  |  |

| 3             | EXEN2           |                                                                                                                                                                                                                                                                                                            | ore events on T2<br>a capture or reload                                                                                                                                                                                                                     | EX pin for timer 2<br>when a negative tran  |     | n is detected, if tir | ner 2 is not used to |  |  |

| 2             | TR2             | Clear to tur                                                                                                                                                                                                                                                                                               | Timer 2 Run control bit<br>Clear to turn off timer 2.<br>Set to turn on timer 2.                                                                                                                                                                            |                                             |     |                       |                      |  |  |

| 1             | C/T2#           | <b>Timer/Counter 2 select bit</b><br>Clear for timer operation (input from internal clock system: F <sub>OSC</sub> ).<br>Set for counter operation (input from T2 input pin).                                                                                                                              |                                                                                                                                                                                                                                                             |                                             |     |                       |                      |  |  |

| 0             | CP/RL2#         | Timer 2 Capture/Reload bit         If RCLK=1 or TCLK=1, CP/RL2# is ignored and timer is forced to auto-reload on timer 2 overflow         Clear to auto-reload on timer 2 overflows or negative transitions on T2EX pin if EXEN2=1.         Set to capture on negative transitions on T2EX pin if EXEN2=1. |                                                                                                                                                                                                                                                             |                                             |     |                       |                      |  |  |

Reset Value = 0000 0000b Bit addressable

#### Table 12. T2MOD Register T2MOD - Timer 2 Mode Control Register (C9h) 7 6 5 4 3 2 1 0 DCEN . ----T2OE -Bit Bit Mne-Description Number monic Reserved 7 The value read from this bit is indeterminate. Do not set this bit. Reserved 6 The value read from this bit is indeterminate. Do not set this bit. Reserved 5 The value read from this bit is indeterminate. Do not set this bit. Reserved 4 \_ The value read from this bit is indeterminate. Do not set this bit. Reserved 3 The value read from this bit is indeterminate. Do not set this bit. Reserved 2 The value read from this bit is indeterminate. Do not set this bit. Timer 2 Output Enable bit 1 T2OE Clear to program P1.0/T2 as clock input or I/O port. Set to program P1.0/T2 as clock output. Down Counter Enable bit 0 DCEN Clear to disable timer 2 as up/down counter. Set to enable timer 2 as up/down counter.

Reset Value = XXXX XX00b Not bit addressable

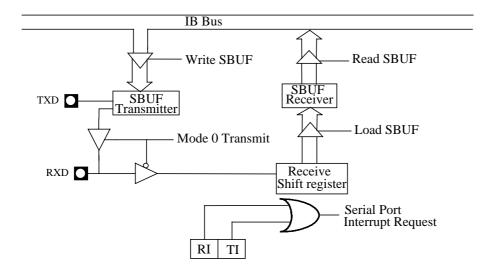

#### 8. Serial I/O Port

The serial I/O ports in the PAROS is entirely compatible with the serial I/O port in the 80C52. It provides both synchronous and asynchronous communication modes. It operates as an Universal Asynchronous Receiver and Transmitter (UART) in three full-duplex modes (Modes 1, 2 and 3). Asynchronous transmission and reception can occur simultaneously and at different baud rates

Serial I/O port includes the following enhancements:

- Framing error detection and Automatic Address Recognition

- Internal Baud Rate Generator

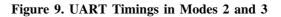

Figure 6. Serial I/O UART Port Block Diagram

#### **8.1 Framing Error Detection**

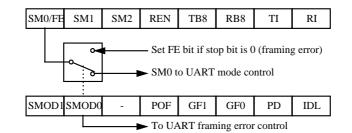

Framing bit error detection is provided for the three asynchronous modes. To enable the framing bit error detection feature, set SMOD0 bit in PCON register (See Table 19.).

Figure 7. Framing Error Block Diagram

When this feature is enabled, the receiver checks each incoming data frame for a valid stop bit. An invalid stop bit may result from noise on the serial lines or from simultaneous transmission by two CPUs. If a valid stop bit is not found, the Framing Error bit (FE) in SCON register bit is set.

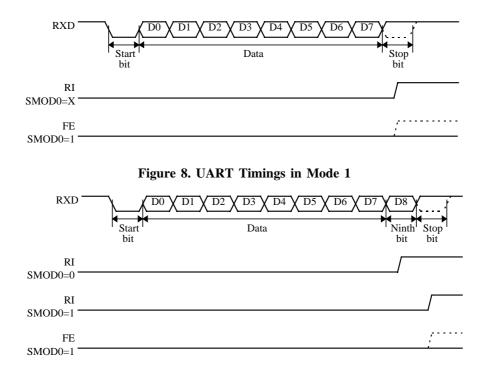

Software may examine FE bit after each reception to check for data errors. Once set, only software or a reset clear FE bit. Subsequently received frames with valid stop bits cannot clear FE bit. When FE feature is enabled, RI rises on stop bit instead of the last data bit (See Figure 8. and Figure 9.).

#### 8.2 Automatic Address Recognition

The automatic address recognition feature is enabled when the multiprocessor communication feature is enabled (SM2 bit in SCON register is set).

Implemented in hardware, automatic address recognition enhances the multiprocessor communication feature by allowing the serial port to examine the address of each incoming command frame. Only when the serial port recognizes its own address, the receiver sets RI bit in SCON register to generate an interrupt. This ensures that the CPU is not interrupted by command frames addressed to other devices.

If desired, you may enable the automatic address recognition feature in mode 1. In this configuration, the stop bit takes the place of the ninth data bit. Bit RI is set only when the received command frame address matches the device's address and is terminated by a valid stop bit.

To support automatic address recognition, a device is identified by a given address and a broadcast address.

NOTE: The multiprocessor communication and automatic address recognition features cannot be enabled in mode 0 (i.e. setting SM2 bit in SCON register in mode 0 has no effect).

#### 8.2.1 Given Address

Each device has an individual address that is specified in SADDR register; the SADEN register is a mask byte that contains don't-care bits (defined by zeros) to form the device's given address. The don't-care bits provide the flexibility to address one or more slaves at a time. The following example illustrates how a given address is formed. To address a device by its individual address, the SADEN mask byte must be 1111 1111b. For example:

SADDR 0101 0110b SADEN 1111 1100b Given 0101 01XXb

The following is an example of how to use given addresses to address different slaves:

```

Slave A: SADDR1111 0001b

<u>SADEN 1111 1010b</u>

Given 1111 0X0Xb

Slave B: SADDR1111 0011b

<u>SADEN 1111 1001b</u>

Given 1111 0XX1b

Slave C: SADDR1111 0010b

<u>SADEN 1111 1101b</u>

Given 1111 00X1b

```

The SADEN byte is selected so that each slave may be addressed seFG\_Lefttely.

For slave A, bit 0 (the LSB) is a don't-care bit; for slaves B and C, bit 0 is a 1. To communicate with slave A only, the master must send an address where bit 0 is clear (e.g. 1111 0000b).

For slave A, bit 1 is a 0; for slaves B and C, bit 1 is a don't care bit. To communicate with slaves A and B, but not slave C, the master must send an address with bits 0 and 1 both set (e.g. 1111 0011b).

To communicate with slaves A, B and C, the master must send an address with bit 0 set, bit 1 clear, and bit 2 clear (e.g. 1111 0001b).

#### 8.2.2 Broadcast Address

A broadcast address is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-care bits, e.g.:

SADDR

0101

0110b

SADEN

1111

1100b

SADDR OR

SADEN1111

111Xb

The use of don't-care bits provides flexibility in defining the broadcast address, however in most applications, a broadcast address is FFh. The following is an example of using broadcast addresses:

```

Slave A:SADDR1111 0001b

<u>SADEN1111 1010b</u>

Given1111 1X11b,

Slave B:SADDR1111 0011b

<u>SADEN1111 1001b</u>

Given1111 1X11B,

Slave C:SADDR=1111 0010b

<u>SADEN1111 1101b</u>

Given1111 1111b

```

For slaves A and B, bit 2 is a don't care bit; for slave C, bit 2 is set. To communicate with all of the slaves, the master must send an address FFh. To communicate with slaves A and B, but not slave C, the master can send and address FBh.

#### 8.2.3 Reset Addresses

On reset, the SADDR, SADEN register are initialized to 00h, i.e. the given and broadcast addresses are XXXX XXXXb (all don't-care bits). This ensures that the serial port is backwards compatible with the 80C51 microcontrollers that do not support automatic address recognition.

#### 8.3 Baud Rate Selection for UART

The Baud Rate Generator for transmit and receive clocks can be selected separately via the BDRCON register.

#### 8.4 Internal Baud Rate Generator (BRG)

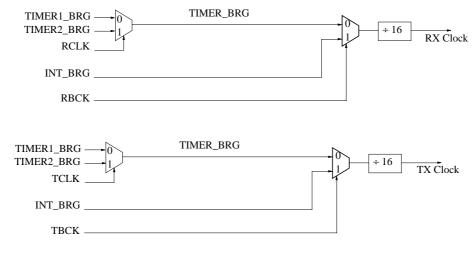

When the internal Baud Rate Generator is used, the Baud Rates are determined by the BRG overflow, the value of SPD bit (Speed Mode) in BRCON register and the value of the SMOD1 bit in PCON register:

Figure 11. Internal Baud Rate

PS is the oscillator prescalar

## PAROS

• SPD = 1

$$BaudRate = \frac{2^{SMOD1} \times F_{XTAL}}{2 \times 2 \times 6^{(1-SPD)} \times 16 \times [256 - (BRL)]} \times \frac{1}{(256 - PS)}$$

$$BRL= 256 - \frac{2^{SMOD1} \times F_{XTAL}}{64 \times BaudRate} \times \frac{1}{(256 - PS)}$$

PS is the oscillator prescalar

• SPD = 0 (Default Mode)

$$BaudRate = \frac{2^{SMOD1} \times F_{XTAL}}{2 \times 2 \times 6^{(1-SPD)} \times 16 \times [256 - (BRL)]} \times \frac{1}{(256 - PS)}$$

$$BRL= 256 - \frac{2^{SMOD1} \times F_{XTAL}}{384 \times BaudRate} \times \frac{1}{(256 - PS)}$$

| Baud Rates | $\mathbf{F}_{\mathbf{XTAL}} = 1$ | 6.384 MHz | $F_{XTAL} = 24MHz$ |           |  |

|------------|----------------------------------|-----------|--------------------|-----------|--|

|            | BRL Error (%)                    |           | BRL                | Error (%) |  |

| 4800       | 247                              | 1.25      | 243                | 0.16      |  |

| 2400       | 238                              | 1.25      | 230                | 0.16      |  |

| 1200       | 220                              | 1.25      | 202                | 0.37      |  |

| 600        | 185                              | 0.16      | 152                | 0.16      |  |

PS is the oscillator prescalar

# TEMIC

|               |                 |                        | Tabl         | le 14. |   |   |   |

|---------------|-----------------|------------------------|--------------|--------|---|---|---|

| SADEN - Slave | e Address Masl  | k Register (B9h)       |              |        |   |   |   |

| 7             | 6               | 5                      | 4            | 3      | 2 | 1 | 0 |

|               |                 |                        |              |        |   |   |   |

| Reset Value = | = 0000 0000b    | -                      |              | 1      | 1 |   | 1 |

|               |                 |                        | Tabl         | le 15. |   |   |   |

| SADDR - Slav  | e Address Regi  | ster (A9h)             |              |        |   |   |   |

| 7             | 6               | 5                      | 4            | 3      | 2 | 1 | 0 |

|               |                 |                        |              |        |   |   |   |

| Reset Value = | = 0000 0000b    |                        | 1            | 1      | 1 | I | 1 |

|               |                 |                        | Tabl         | le 16. |   |   |   |

| SBUF - Serial | Buffer Register | <b>· (99h</b> )        |              |        |   |   |   |

| 7             | 6               | 5                      | 4            | 3      | 2 | 1 | 0 |

|               |                 |                        |              |        |   |   |   |

| Reset Value : | = XXXX XXX      | <br>XXh                |              |        |   |   |   |

| Reset value - | - 707070707070  |                        | <b>T</b> -11 | . 17   |   |   |   |

| DDI David     | ata Dalaa d Daa | ·                      |              | le 17. |   |   |   |

|               |                 | ister (9Ah) for U<br>- |              |        |   | _ |   |

| 7             | 6               | 5                      | 4            | 3      | 2 | 1 | 0 |

|               |                 |                        |              |        |   |   |   |

| Reset Value = | = 0000 0000b    |                        |              |        |   |   |   |

#### Table 18. SCON Register

#### SCON (S:98h)

Serial Control Register

| 7             | 6               | 5                              | 4                                                                                                                                                                                                                   | 3                                      | 2                    | 1                                      | 0  |  |  |

|---------------|-----------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------|----------------------------------------|----|--|--|

| FE/SM0        | SM1             | SM2                            | REN                                                                                                                                                                                                                 | TB8                                    | RB8                  | TI                                     | RI |  |  |

| Bit<br>Number | Bit<br>Mnemonic |                                |                                                                                                                                                                                                                     | Descrip                                | tion                 |                                        |    |  |  |

| 7             | FE              | Set by hardw                   | s function, set SM                                                                                                                                                                                                  | 10D0 bit in PCO<br>n invalid stop bit. | N register.          |                                        |    |  |  |

|               | SM0             | To select this<br>Software wri | Serial Port Mode bit 0.<br>To select this function, clear SMOD0 bit in PCON register.<br>Software writes to bits SM0 and SM1 to select the Serial Port operating mode.<br>Refer to SM1 bit for the mode selections. |                                        |                      |                                        |    |  |  |

| 6             | SM1             | To select thi<br>Software wri  |                                                                                                                                                                                                                     |                                        |                      |                                        |    |  |  |

| 5             | SM2             | address recog                  | ites to bit SM2 to<br>gnition features.<br>he Serial Port to o                                                                                                                                                      |                                        | ×.                   | sor communication<br>and frames and to |    |  |  |

| 4             | REN             |                                |                                                                                                                                                                                                                     |                                        | and to enable trans  | smission in mode (                     | 0. |  |  |

| 3             | TB8             |                                | 1 1: Not used.<br>1 3: Software writ                                                                                                                                                                                | tes the ninth data                     | bit to be transmitte | ed to TB8.                             |    |  |  |

| 2             | RB8             | Mode 1 (SM                     | Receiver bit 8<br>Mode 0: Not used.<br>Mode 1 (SM2 cleared): Set or cleared by hardware to reflect the stop bit received.<br>Modes 2 and 3 (SM2 set): Set or cleared by hardware to reflect the ninth bit received. |                                        |                      |                                        |    |  |  |

| 1             | TI              | •                              | . 0                                                                                                                                                                                                                 | e last data bit is ti                  | ansmitted.           |                                        |    |  |  |

| 0             | RI              | •                              |                                                                                                                                                                                                                     | top bit of a frame                     | has been received    | 1.                                     |    |  |  |

**Reset Value= 0000 0000b**

PAROS

#### Table 19. PCON Register

#### PCON - Power Control Register (87h)

| 7             | 6               | 5                                                                                                       | 4                                                                                                                | 3                  | 2                | 1                 | 0            |  |

|---------------|-----------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------|------------------|-------------------|--------------|--|

| SMOD1         | SMOD            | -                                                                                                       | POF                                                                                                              | GF1                | GF0              | PD                | IDL          |  |

| Bit<br>Number | Bit<br>Mnemonic |                                                                                                         |                                                                                                                  | Descrip            | otion            |                   |              |  |

| 7             | SMOD1           | Serial port Mode Set to sele                                                                            | bit 1<br>ect double baud ra                                                                                      | te in mode 1, 2 or | : 3.             |                   |              |  |

| 6             | SMOD0           | Clear to se                                                                                             | Serial port Mode bit 0<br>Clear to select SM0 bit in SCON register.<br>Set to to select FE bit in SCON register. |                    |                  |                   |              |  |

| 5             | -               | Reserved<br>The value                                                                                   | Reserved<br>The value read from this bit is indeterminate. Do not set this bit.                                  |                    |                  |                   |              |  |

| 4             | POF             |                                                                                                         | cognize next reset<br>lware when VCC                                                                             |                    | nominal voltage. | Can also be set t | by software. |  |

| 3             | GF1             |                                                                                                         | <b>`lag</b><br>user for general p<br>for general purpo                                                           | 1 0                |                  |                   |              |  |

| 2             | GF0             | Cleared by                                                                                              | General purpose Flag<br>Cleared by user for general purpose usage.<br>Set by user for general purpose usage.     |                    |                  |                   |              |  |

| 1             | PD              | Power-Down mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.          |                                                                                                                  |                    |                  |                   |              |  |

| 0             | IDL             | Idle mode bit         Clear by hardware when interrupt or reset occurs.         Set to enter idle mode. |                                                                                                                  |                    |                  |                   |              |  |

Reset Value = 00X0 0000b Not bit addressable

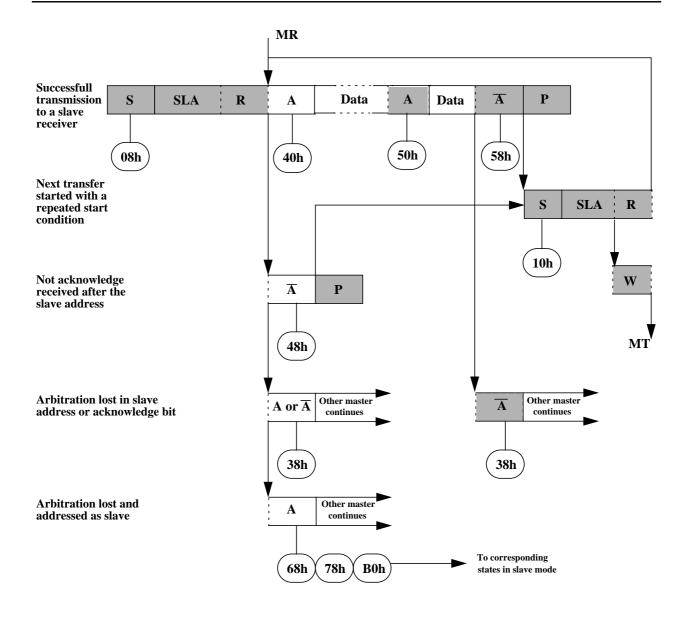

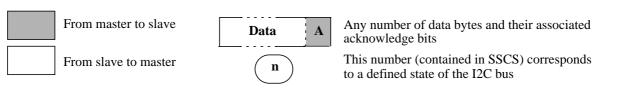

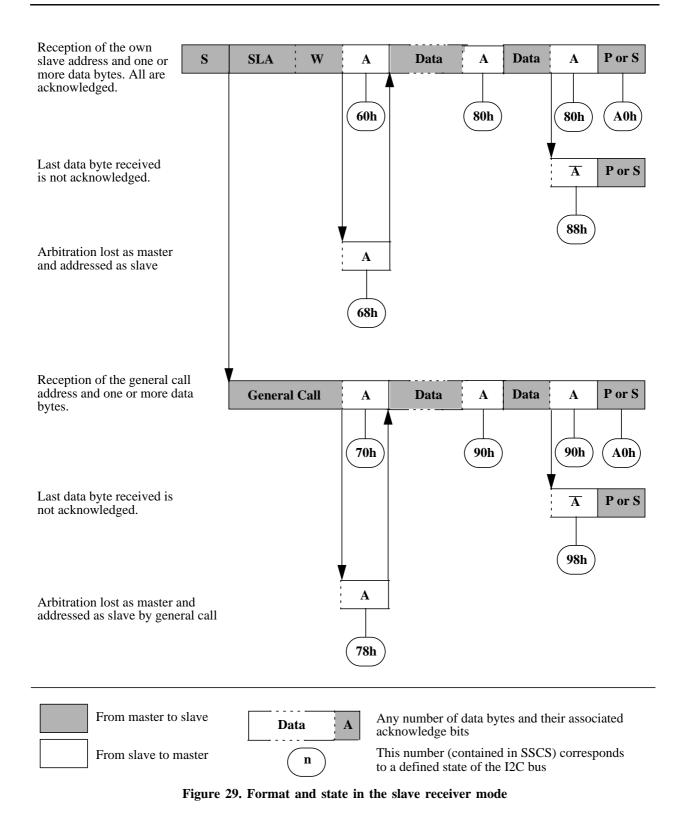

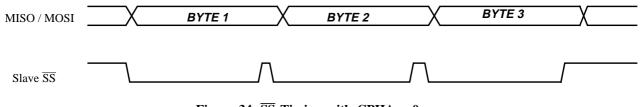

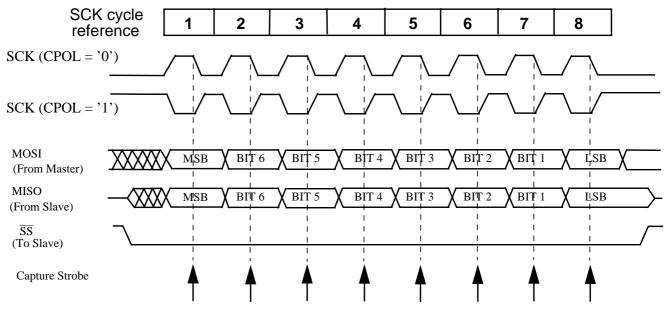

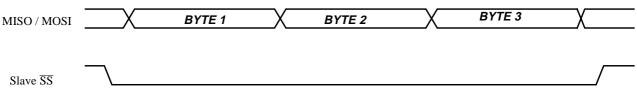

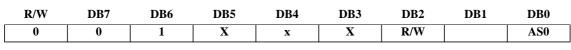

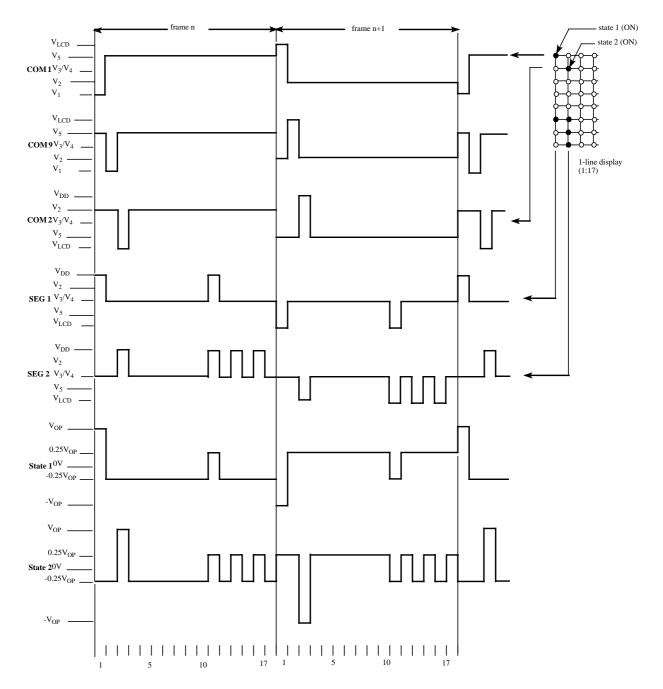

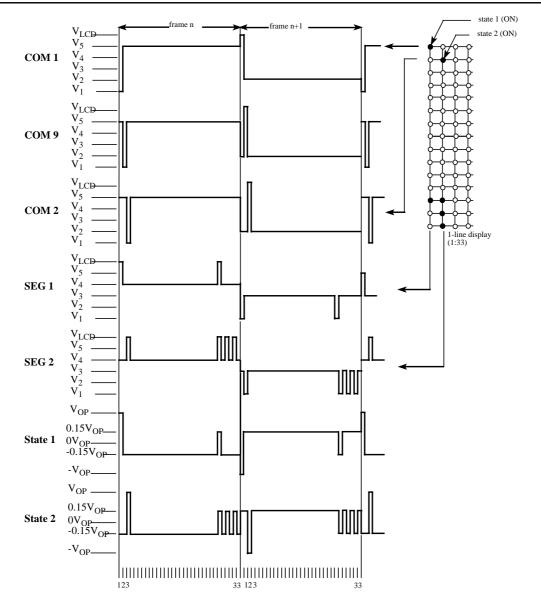

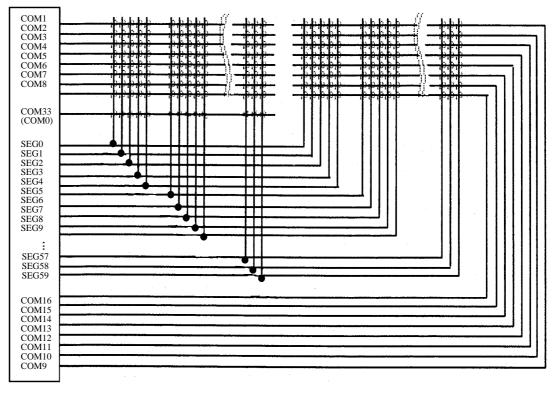

| Table | 20. | BDRCON | Register |