# DP80390 Pipelined High Performance Microcontroller

# Instructions set details ver 3.10

#### Contents

| 1. Overview                                                    |          |

|----------------------------------------------------------------|----------|

| 1.1. Document structure.                                       | 7        |

| 2. Instructions set brief                                      |          |

| 2.1. Instruction set notes                                     | 7        |

| 2.2. Instruction set brief – functional order                  |          |

| 2.2.1. Arithmetic operations                                   | 8        |

| 2.2.2. Logic operations                                        | 9        |

| 2.2.3. Boolean manipulation                                    |          |

| 2.2.4. Data transfers                                          |          |

| 2.2.5. Program branches                                        |          |

| 2.3. Instruction set brief – hexadecimal order                 |          |

| 3. Instructions set details                                    | 15       |

| 3.1. ACALL *                                                   | 15       |

| 3.1.1. LARGE                                                   | 15       |

| 3.1.2. FLAT                                                    | 16       |

| 3.2. ADD                                                       |          |

| 3.2.1. ADD A, Rn                                               |          |

| 3.2.2. ADD A, direct                                           |          |

| 3.2.3. ADD A, @Ri                                              |          |

| 3.2.4. ADD A, #data                                            |          |

| 3.3. ADDC                                                      | 19       |

| 3.3.1. ADDC A, Rn                                              | 19       |

| 3.3.2. ADDC A, direct                                          |          |

| 3.3.3. ADDC A, @Ri<br>3.3.4. ADDC A, #data                     | 20<br>20 |

|                                                                | 21       |

| 3.4.1. LARGE                                                   | 21       |

| 3.4.2. FLAT                                                    | 22       |

| 3.5. ANL                                                       | 23       |

| 3.5.1. ANL A, Rn                                               |          |

| 3.5.2. ANL A, direct                                           | 23       |

| 3.5.3. ANL A, @Ri                                              |          |

| 3.5.4. ANL A, #data                                            |          |

| 3.5.5. ANL direct, A                                           |          |

| 3.5.6. ANL direct, #data                                       |          |

| 3.5.7.         ANL C, bit           3.5.8.         ANL C, /bit |          |

|                                                                |          |

|                                                                | 26       |

| 3.6.1. CJNE A, direct, rel<br>3.6.2. CJNE A, #data, rel        | 26       |

| 3.6.2. CJNE A, #data, rel<br>3.6.3. CJNE RN, #data, rel        | 21       |

| 3.6.4. CJNE @Ri, #data, rel                                    |          |

| 3.7. CLR                                                       |          |

| 3.7.1. CLR A                                                   |          |

| 3.7.2. CLR bit                                                 |          |

| 3.7.3. CLR C                                                   |          |

| 3.8. CPL                                                       | 31       |

| 3.8.1. CPL A                                                   | 31       |

| 3.8.2. CPL bit                                                 | 31       |

All trademarks mentioned in this document are trademarks of their respective owners.

| 3.8.3. CPL C                                           | 32 |

|--------------------------------------------------------|----|

| 3.9. DA                                                | 33 |

| 3.10. DEC                                              | 34 |

| 3.10.1. DEC A                                          | 34 |

| 3.10.2. DEC Rn                                         | 34 |

| 3.10.3. DEC direct                                     | 35 |

| 3.10.4. DEC @Ri                                        | 35 |

| 3.11. DIV                                              | 36 |

| 3.12. DJNZ                                             |    |

| 3.12.1. DJNZ Rn, rel                                   |    |

| 3.12.2. DJNZ direct, rel                               |    |

| 3.13. INC                                              | 39 |

| 3.13.1. INC A<br>3.13.2. INC Rn                        |    |

| 3.13.3. INC direct                                     |    |

| 3.13.4. INC @Ri                                        |    |

| 3.13.5. INC DPTR*                                      | 40 |

| 3.14. JB                                               | 41 |

| 3.15. JBC                                              |    |

| 3.16. JC                                               |    |

| 3.17. JMP*                                             | 44 |

| 3.18. JNB                                              | 45 |

| 3.19. JNC                                              | 46 |

| 3.20. JNZ                                              |    |

| 3.21. JZ                                               | 48 |

| 3.22. LCALL *                                          | 49 |

| 3.22.1. LARGE                                          | 49 |

| 3.22.2. FLAT                                           | 50 |

| 3.23. LJMP *                                           | 51 |

| 3.23.1. LARGE                                          | 51 |

| 3.23.2. FLAT                                           | 51 |

| 3.24. MOV                                              |    |

| 3.24.1. MOV A, Rn                                      |    |

| 3.24.2. MOV A, direct                                  |    |

| 3.24.3. MOV A, @Ri<br>3.24.4. MOV A, #data             |    |

| 3.24.5. MOV Rn, A                                      |    |

| 3.24.6. MOV Rn, direct                                 |    |

| 3.24.7. MOV Rn, #data                                  |    |

| 3.24.8. MOV direct, A                                  | 54 |

| 3.24.9. MOV direct, Rn                                 |    |

| 3.24.10. MOV direct, direct                            |    |

| 3.24.11. MOV direct, @Ri<br>3.24.12. MOV direct, #data |    |

| 3.24.13. MOV @Ri, A                                    |    |

| 3.24.14. MOV @Ri, direct                               |    |

| 3.24.15. MOV @Ri, #data                                | 55 |

| 3.24.16. MOV C, bit                                    |    |

| 3.24.17. MOV bit, C                                    | 56 |

| 3.24.18. MOV DPTR, #data16 - LARGE                     | 5/ |

| 3.24.19. MOV DPTR, #data24* - FLAT  | 57       |

|-------------------------------------|----------|

|                                     | 58       |

| 3.25.1. MOVC A, @A + DPTR           | 58       |

| 3.25.2. MOVC A, @A + PC             | 58       |

| 3.26. MOVX*                         | 59       |

| 3.26.1. MOVX A, @Ri                 | 59       |

| 3.26.2. MOVX A, @DPTR               |          |

| 3.26.3. MOVX @Ri, A                 |          |

| 3.26.4. MOVX @DPTR, A               | 60       |

| 3.27. MUL                           | 61       |

| 3.28. NOP                           | 62       |

| 3.29. ORL                           | 63       |

| 3.29.1. ORL A, Rn                   | 63       |

| 3.29.2. ORL A, direct               |          |

| 3.29.3. ORL A, @Ri                  |          |

| 3.29.4. ORL A, #data                |          |

| 3.29.5. ORL direct, A               |          |

| 3.29.7. ORL C, bit                  | 65       |

| 3.29.8. ORL C, /bit                 |          |

| 3 30 POP*                           | 66       |

| <b>3.30. POP</b> *                  |          |

| 3.30.2. FLAT                        |          |

|                                     |          |

| <b>3.31.</b> PUSH*                  | 07<br>67 |

| 3.31.2. FLAT                        |          |

|                                     |          |

| <b>3.32. RET</b> *<br>3.32.1. LARGE |          |

| 3.32.2. FLAT                        | 68       |

|                                     |          |

| <b>3.33. RETI</b> *                 | 60       |

| 3.33.2. FLAT                        |          |

| 3.34. RL                            | 71       |

| 3.35. RLC                           | 72       |

| 3.36. RR                            | 73       |

| 3.37. RRC                           | 74       |

| 3.38. SETB                          | 75       |

| 3.38.1. SETB C                      | 75       |

| 3.38.2. SETB bit                    | 75       |

| 3.39. SJMP                          |          |

|                                     |          |

| <b>3.40. SUBB</b>                   |          |

| 3.40.2. SUBB A, direct              | 77       |

| 3.40.3. SUBB A, @RI                 | /8       |

| 3.40.4. SUBB A, #data               | 78       |

| 3.41. SWAP                          | 79       |

| 3.42. XCH                           | 80       |

| 3.42.1. XCH A, Rn                   | 80       |

| 3.42.2. XCH A, direct               | 80       |

| 3.42.3. XCH A, @Ri        | 80 |

|---------------------------|----|

| 3.43. XCHD                | 81 |

| 3.44. XRL                 | 82 |

| 3.44.1. XRL A, Rn         | 82 |

| 3.44.2. XRL A, direct     |    |

| 3.44.3. XRL A, @ Ri       | 83 |

| 3.44.4. XRL A, #data      | 83 |

| 3.44.5. XRL direct, A     | 83 |

| 3.44.6. XRL direct, #data | 83 |

| 4. Contacts               | 84 |

#### Tables

| Table 1. Notes on data addressing modes             | 7  |

|-----------------------------------------------------|----|

| Table 2. Notes on program addressing modes          | 7  |

| Table 3. Arithmetic operations                      | 8  |

| Table 4. Logic operations                           | 9  |

| Table 5. Boolean manipulation                       | 9  |

| Table 6. Data transfer                              | 10 |

| Table 7. Program branches                           | 11 |

| Table 8. Instruction set brief in hexadecimal order | 14 |

All trademarks mentioned in this document are trademarks of their respective owners.

# 1. OVERVIEW

#### **1.1. DOCUMENT STRUCTURE.**

Document contains brief description of DP80390 instructions. This manual is intended for design engineers who are planning to use the DP80390 HDL core in conjunction with software assembler, compiler and debugger tools.

# 2. INSTRUCTIONS SET BRIEF

#### **2.1. INSTRUCTION SET NOTES**

The DP80390 has five different addressing modes: immediate, direct, register, indirect and relative. In the immediate addressing mode the data is contained in the opcode. By direct addressing an eight bit address is a part of the opcode, by register addressing, a register is selected in the opcode for the operation. In the indirect addressing mode, a register is selected in the opcode to point to the address used by the operation. The relative addressing mode is used for jump instructions.

The following tables give a survey about the instruction set cycles of the DP80390 microcontroller core. **One cycle is equal to one clock period**.

Table 1 and Table 2 contain notes for mnemonics used in Instruction set tables. Tables 3 - 7 show instruction hexadecimal codes, number of bytes and machine cycles that each instruction takes to execute.

| Rn      | Working register R0-R7                                                    |

|---------|---------------------------------------------------------------------------|

| direct  | 128 internal RAM locations, any Special Function Registers                |

| @Ri     | Indirect internal or external RAM location addressed by register R0 or R1 |

| #data   | 8-bit constant included in instruction                                    |

| #data16 | 16-bit constant included as bytes 2 and 3 of instruction                  |

| #data24 | 24-bit constant included as bytes 2,3 and 4 of instruction                |

| bit     | 256 software flags, any bit-addressable I/O pin, control or status bit    |

| А       | Accumulator                                                               |

#### Table 1. Notes on data addressing modes

| addr24 | Destination address for LCALL and LJMP may be anywhere within the 16 MB of      |

|--------|---------------------------------------------------------------------------------|

|        | program memory address space in FLAT mode.                                      |

| addr19 | Destination address for ACALL and AJMP will be within the same 512 KB page of   |

|        | program memory as the first byte of the following instruction in FLAT mode      |

| addr16 | Destination address for LCALL and LJMP may be anywhere within the 64 kB of      |

|        | program memory address space in LARGE mode.                                     |

| addr11 | Destination address for ACALL and AJMP will be within the same 2 KB page of     |

|        | program memory as the first byte of the following instruction in LARGE mode     |

| rel    | SJMP and all conditional jumps include an 8-bit offset byte. Range is +127/-128 |

|        | bytes relative to the first byte of the following instruction                   |

|        |                                                                                 |

Table 2. Notes on program addressing modes

All trademarks mentioned in this document are trademarks of their respective owners.

# **2.2.** INSTRUCTION SET BRIEF – FUNCTIONAL ORDER

#### **2.2.1. ARITHMETIC OPERATIONS**

| Mnemonic       | Description                                 | Code      | Bytes | Cycles |

|----------------|---------------------------------------------|-----------|-------|--------|

| ADD A,Rn       | Add register to accumulator 0x28-0          |           | 1     | 1      |

| ADD A, direct  | Add direct byte to accumulator              | 0x25      | 2     | 2      |

| ADD A,@Ri      | Add indirect RAM to accumulator             | 0x26-0x27 | 1     | 2      |

| ADD A,#data    | Add immediate data to accumulator           | 0x24      | 2     | 2      |

| ADDC A,Rn      | Add register to accumulator with carry flag | 0x38-0x3F | 1     | 1      |

| ADDC A, direct | Add direct byte to A with carry flag        | 0x35      | 2     | 2      |

| ADDC A,@Ri     | Add indirect RAM to A with carry flag       | 0x36-0x37 | 1     | 2      |

| ADDC A,#data   | Add immediate data to A with carry flag     | 0x34      | 2     | 2      |

| SUBB A,Rn      | Subtract register from A with borrow        | 0x98-0x9F | 1     | 1      |

| SUBB A, direct | Subtract direct byte from A with borrow     | 0x95      | 2     | 2      |

| SUBB A,@Ri     | Subtract indirect RAM from A with borrow    | 0x96-0x97 | 1     | 2      |

| SUBB A,#data   | Subtract immediate data from A with borrow  | 0x94      | 2     | 2      |

| INC A          | Increment accumulator                       | 0x04      | 1     | 1      |

| INC Rn         | Increment register                          | 0x08-0x0F | 1     | 2      |

| INC direct     | Increment direct byte                       | 0x05      | 2     | 3      |

| INC @Ri        | Increment indirect RAM                      | 0x06-0x07 | 1     | 3      |

| DEC A          | Decrement accumulator                       | 0x14      | 1     | 1      |

| DEC Rn         | Decrement register                          | 0x18-0x1F | 1     | 2      |

| DEC direct     | Decrement direct byte                       | 0x15      | 1     | 3      |

| DEC @Ri        | Decrement indirect RAM                      | 0x16-0x17 | 2     | 3      |

| INC DPTR       | Increment data pointer                      | 0xA3      | 1     | 1      |

| MUL A,B        | Multiply A and B                            | 0xA4      | 1     | 2      |

| DIV A,B        | Divide A by B                               | 0x84      | 1     | 6      |

| DA A           | Decimal adjust accumulator                  | 0xD4      | 1     | 3      |

Table 3. Arithmetic operations

All trademarks mentioned in this document are trademarks of their respective owners.

#### 2.2.2. LOGIC OPERATIONS

| Mnemonic         | Description                                     | Code      | Bytes | Cycles |

|------------------|-------------------------------------------------|-----------|-------|--------|

| ANL A,Rn         | AND register to accumulator                     | 0x58-0x5F | 1     | 1      |

| ANL A, direct    | AND direct byte to accumulator                  | 0x55      | 2     | 2      |

| ANL A,@Ri        | AND indirect RAM to accumulator                 | 0x56-0x57 | 1     | 2      |

| ANL A,#data      | AND immediate data to accumulator               | 0x54      | 2     | 2      |

| ANL direct,A     | AND accumulator to direct byte                  | 0x52      | 2     | 3      |

| ANL direct,#data | AND immediate data to direct byte               | 0x53      | 3     | 3      |

| ORL A,Rn         | OR register to accumulator                      | 0x48-0x4F | 1     | 1      |

| ORL A, direct    | OR direct byte to accumulator                   | 0x45      | 2     | 2      |

| ORL A,@Ri        | OR indirect RAM to accumulator                  | 0x46-0x47 | 1     | 2      |

| ORL A,#data      | OR immediate data to accumulator                | 0x44      | 2     | 2      |

| ORL direct,A     | OR accumulator to direct byte                   | 0x42      | 2     | 3      |

| ORL direct,#data | OR immediate data to direct byte                |           |       | 3      |

| XRL A,Rn         | Exclusive OR register to accumulator 0x68-0x6F  |           | 1     | 1      |

| XRL A, direct    | Exclusive OR direct byte to accumulator         | 0x65      | 2     | 2      |

| XRL A,@Ri        | Exclusive OR indirect RAM to accumulator 0x66-0 |           | 1     | 2      |

| XRL A,#data      | Exclusive OR immediate data to accumulator      | 0x64      | 2     | 2      |

| XRL direct,A     | Exclusive OR accumulator to direct byte         | 0x62      | 2     | 3      |

| XRL direct,#data | Exclusive OR immediate data to direct byte      | 0x63      | 3     | 3      |

| CLR A            | Clear accumulator                               | 0xE4      | 1     | 1      |

| CPL A            | Complement accumulator                          | 0xF4      | 1     | 1      |

| RL A             | Rotate accumulator left                         | 0x23      | 1     | 1      |

| RLC A            | Rotate accumulator left through carry           | 0x33      | 1     | 1      |

| RR A             | Rotate accumulator right 0                      |           | 1     | 1      |

| RRC A            | Rotate accumulator right through carry          | 0x13      | 1     | 1      |

| SWAP A           | Swap nibbles within the accumulator             | 0xC4      | 1     | 1      |

Table 4. Logic operations

#### **2.2.3. BOOLEAN MANIPULATION**

| Mnemonic   | Description                           | Code | Bytes | Cycles |

|------------|---------------------------------------|------|-------|--------|

| CLR C      | Clear carry flag                      | 0xC3 | 1     | 1      |

| CLR bit    | Clear direct bit                      | 0xC2 | 2     | 3      |

| SETB C     | Set carry flag                        | 0xD3 | 1     | 1      |

| SETB bit   | Set direct bit                        | 0xD2 | 2     | 3      |

| CPL C      | Complement carry flag                 | 0xB3 | 1     | 1      |

| CPL bit    | Complement direct bit                 | 0xB2 | 2     | 3      |

| ANL C,bit  | AND direct bit to carry flag          | 0x82 | 2     | 2      |

| ANL C,/bit | AND complement of direct bit to carry | 0xB0 | 2     | 2      |

| ORL C,bit  | OR direct bit to carry flag           | 0x72 | 2     | 2      |

| ORL C,/bit | OR complement of direct bit to carry  | 0xA0 | 2     | 2      |

| MOV C,bit  | Move direct bit to carry flag         | 0xA2 | 2     | 2      |

| MOV bit,C  | Move carry flag to direct bit         | 0x92 | 2     | 3      |

Table 5. Boolean manipulation

All trademarks mentioned in this document are trademarks of their respective owners.

#### 2.2.4. DATA TRANSFERS

| Mnemonic             | Des                                         | scription                                       |         | Code      | Bytes  | Cycles |

|----------------------|---------------------------------------------|-------------------------------------------------|---------|-----------|--------|--------|

| MOV A,Rn             | Move register to accur                      | nulator                                         |         | 0xE8-0xEF | 1      | 1      |

| MOV A, direct        | Move direct byte to ac                      | cumulator                                       |         | 0xE5      | 2      | 2      |

| MOV A,@Ri            | Move indirect RAM to                        | accumulator                                     |         | 0xE6-0xE7 | 1      | 2      |

| MOV A,#data          | Move immediate data                         | to accumulator                                  |         | 0x74      | 2      | 2      |

| MOV Rn,A             | Move accumulator to r                       | egister                                         |         | 0xF8-0xFF | 1      | 1      |

| MOV Rn, direct       | Move direct byte to reg                     |                                                 |         | 0xA8-0xAF | 2      | 3      |

| MOV Rn,#data         | Move immediate data                         |                                                 |         | 0x78-0x7F | 2      | 2      |

| MOV direct,A         | Move accumulator to c                       |                                                 |         | 0xF5      | 2      | 2      |

| MOV direct,Rn        | Move register to direct                     | byte                                            |         | 0x88-8F   | 2      | 2      |

| MOV direct1, direct2 | Move direct byte to direct                  |                                                 |         | 85        | 3      | 3      |

| MOV direct,@Ri       | Move indirect RAM to                        |                                                 |         | 86-87     | 2      | 3      |

| MOV direct,#data     | Move immediate data                         | to direct byte                                  |         | 75        | 3      | 3      |

| MOV @Ri,A            | Move accumulator to in                      |                                                 |         | F6-F7     | 1      | 2      |

| MOV @Ri,direct       | Move direct byte to inc                     |                                                 |         | A6-A7     | 2      | 3      |

| MOV @Ri,#data        | Move immediate data                         | to indirect RAM                                 |         | 76-77     | 2      | 2      |

| MOV DPTR,#data16     | Load 16-bit constant ir<br>LARGE mode       | Load 16-bit constant into active DPH and DPL in |         |           | 3      | 3      |

| MOV DPTR,#data24     | Load 24-bit constant ir<br>DPL in FLAT mode | nto active DPX, DPH                             | H and   | 90        | 4      | 4      |

| MOVC A,@A+DPTR       | Move code byte relativ                      | e to DPTR to accur                              | nulator | 93        | 1      | 5      |

| MOVC A,@A+PC         | Move code byte relativ                      | e to PC to accumul                              | ator    | 83        | 1      | 4      |

| MOVX A,@Ri           | Move external RAM (8                        | -bit address) to A                              |         | E2-E3     | 1      | 3*     |

| MOVX A,@DPTR         | Move external RAM (1                        | 6-bit address) to A                             |         | E0        | 1      | 2*     |

| MOVX @Ri,A           | Move A to external                          | CODE inside ROM destination XRAM                |         | F2-F3     | 1      | 4*     |

|                      | RAM (8-bit address)                         | all other cases                                 |         | 1210      | •      | 5*     |

| MOVX @DPTR,A         | Move A to external                          | CODE inside ROM<br>destination XRAM             |         | F0        | 1      | 3*     |

|                      | RAM (16-bit address)                        | all other cases                                 | 1       |           |        | 4*     |

| PUSH direct          | Push direct byte onto stack LARGE FLAT      |                                                 | C0      | 2         | 3<br>3 |        |

| POP direct           | Pop direct byte from stack  LARGE FLAT      |                                                 | D0      | 2         | 2      |        |

| XCH A,Rn             | Exchange register with accumulator          |                                                 | C8-CF   | 1         | 2      |        |

| XCH A, direct        |                                             | Exchange direct byte with accumulator           |         | C5        | 2      | 3      |

| XCH A,@Ri            | Exchange indirect RAM                       |                                                 |         | C6-C7     | 1      | 3      |

| XCHD A,@Ri           | Exchange low-order ni                       |                                                 | with A  | D6-D7     | 1      | 3      |

#### Table 6. Data transfer

\* MOVX cycles depends on external data memory access time (READY pin)

All trademarks mentioned in this document are trademarks of their respective owners.

Copyright 1999-2003 DCD – Digital Core Design. All Rights Reserved.

#### 2.2.5. PROGRAM BRANCHES

| Mnemonic            | Description                                     |                                    | Code      | Bytes | Cycles |

|---------------------|-------------------------------------------------|------------------------------------|-----------|-------|--------|

| ACALL addr11        | Absolute subroutine call                        | LARGE                              | 0x11-0xF1 | 2     | 4      |

| ACALL addr19        |                                                 | FLAT                               |           | 3     | 5      |

| LCALL addr16        | Long subroutine call                            | LARGE                              | 03        | 3     | 4      |

| LCALL addr24        |                                                 | FLAT                               | 00        | 4     | 6      |

| RET                 | Return from subroutine                          | LARGE                              | 22        | 1     | 4      |

|                     |                                                 | FLAT                               |           | •     | 5      |

| RETI                | Return from interrupt                           | LARGE                              | 32        | 1     | 4      |

|                     |                                                 | FLAT                               | 02        | •     | 5      |

| AJMP addr11         | Absolute jump                                   | LARGE                              | 01-E1     | 2     | 3      |

| AJMP addr19         |                                                 | FLAT                               | 01 21     | 3     | 4      |

| LJMP addr16         | Long jump                                       | LARGE                              | 02        | 02 3  | 4      |

| LJMP addr24         |                                                 | FLAT                               | 02        | 4     | 5      |

| SJMP rel            | Short jump (relative address)                   | 80                                 | 2         | 3     |        |

| JMP @A+DPTR         | Jump indirect relative to the DPTR              | Jump indirect relative to the DPTR |           | 1     | 5      |

| JZ rel              | Jump if accumulator is zero                     | 60                                 | 2         | 4     |        |

| JNZ rel             | Jump if accumulator is not zero                 |                                    | 70        | 2     | 4      |

| JC rel              | Jump if carry flag is set                       |                                    | 40        | 2     | 3      |

| JNC rel             | Jump if carry flag is not set                   |                                    | 50        | 2     | 3      |

| JB bit,rel          | Jump if direct bit is set                       |                                    | 20        | 3     | 5      |

| JNB bit,rel         | Jump if direct bit is not set                   |                                    | 30        | 3     | 5      |

| JBC bit, direct rel | Jump if direct bit is set and clear bit         |                                    | 10        | 3     | 5      |

| CJNE A, direct rel  | Compare direct byte to A and jump if n          | B5                                 | 3         | 5     |        |

| CJNE A,#data rel    | Compare immediate to A and jump if not equal    |                                    | B4        | 3     | 4      |

| CJNE Rn,#data rel   | Compare immediate to reg. and jump if not equal |                                    | B8-BF     | 3     | 4      |

| CJNE @Ri,#data rel  | Compare immediate to ind. and jump if not equal |                                    | B6-B7     | 3     | 5      |

| DJNZ Rn,rel         | Decrement register and jump if not zero         |                                    | D8-DF     | 2     | 4      |

| DJNZ direct,rel     | Decrement direct byte and jump if not zero      |                                    | D5        | 3     | 5      |

| NOP                 | No operation                                    |                                    | 00        | 1     | 1      |

Table 7. Program branches

All trademarks mentioned in this document are trademarks of their respective owners.

| Opcode       | Mnemonic               | Opcode | Mnemonic                 |

|--------------|------------------------|--------|--------------------------|

| 00 H         | NOP                    | 30 H   | JNB bit.rel              |

| 01 H         | AJMP addr11/addr19     | 31 H   | ACALL addr11/addr19      |

| 02 H         | LJMP addr16 /addr24    | 32 H   | RETI                     |

| 03 H         | RR A                   | 33 H   | RLC A                    |

| 04 H         | INC A                  | 34 H   | ADDC A,#data             |

| 05 H         | INC direct             | 35 H   | ADDC A, direct           |

| 06 H         | INC @R0                | 36 H   | ADDC A,@R0               |

| 07 H         | INC @R1                | 37 H   | ADDC A,@R1               |

| 08 H         | INC R0                 | 38 H   | ADDC A,R0                |

| 09 H         | INC R1                 | 39 H   | ADDC A,R1                |

| 0A H         | INC R2                 | 3A H   | ADDC A,R2                |

| 0B H         | INC R3                 | 3B H   | ADDC A,R3                |

| 0C H         | INC R4                 | 3C H   | ADDC A,R4                |

| 0D H         | INC R5                 | 3D H   | ADDC A,R5                |

| 0E H         | INC R6                 | 3E H   | ADDC A,R6                |

| 0F H         | INC R7                 | 3F H   | ADDC A,R7                |

| 10 H         | JBC bit,rel            | 40 H   | JC rel                   |

| 10 H         | ACALL addr11/addr19    | 41 H   | AJMP addr11/addr19       |

| 12 H         | LCALL addr16/addr24    | 42 H   | ORL direct,A             |

| 13 H         | RRC A                  | 43 H   | ORL direct,#data         |

| 14 H         | DEC A                  | 44 H   | ORL A,#data              |

| 15 H         | DEC direct             | 45 H   | ORL A,direct             |

| 16 H         | DEC @R0                | 46 H   | ORL A,@R0                |

| 17 H         | DEC @R1                | 47 H   | ORL A,@R1                |

| 18 H         | DEC R0                 | 48 H   | ORL A,R0                 |

| 19 H         | DEC R1                 | 49 H   | ORL A,R1                 |

| 10 H         | DEC R2                 | 4A H   | ORL A,R2                 |

| 1B H         | DEC R3                 | 4B H   | ORL A,R3                 |

| 1C H         | DEC R4                 | 4C H   | ORL A,R4                 |

| 1D H         | DEC R5                 | 4D H   | ORL A,R5                 |

| 1E H         | DEC R6                 | 4E H   | ORL A,R6                 |

| 1F H         | DEC R7                 | 4F H   | ORL A,R7                 |

| 20 H         | JB bit.rel             | 50 H   | JNC rel                  |

| 20 H         | AJMP addr11/addr19     | 51 H   | ACALL addr11/addr19      |

| 22 H         | RET                    | 52 H   | ANL direct,A             |

| 23 H         | RLA                    | 53 H   | ANL direct,#data         |

| 23 H<br>24 H | ADD A,#data            | 54 H   | ANL A,#data              |

| 25 H         | ADD A,direct           | 55 H   | ANL A, direct            |

| 25 H         | ADD A,@R0              | 56 H   | ANL A,@R0                |

| 2011<br>27 H | ADD A,@R0<br>ADD A,@R1 | 57 H   | ANL A, @R0<br>ANL A, @R1 |

| 28 H         | ADD A, @KT             | 58 H   | ANL A, @KT               |

| 20 H         | ADD A,R1               | 59 H   | ANL A,R1                 |

| 2911<br>2A H | ADD A,R1<br>ADD A,R2   | 59 H   | ANL A,R2                 |

| 28 H         | ADD A,R3               | 58 H   | ANL A,R3                 |

| 26 H<br>2C H | ADD A,R3<br>ADD A,R4   | 50 H   | ANL A,R3                 |

| 20 H<br>2D H | ADD A,R4<br>ADD A,R5   | 5D H   | ANL A,R4                 |

| 20 H<br>2E H | ADD A,R5<br>ADD A,R6   | 5E H   | ANL A,R6                 |

| 2E H<br>2F H | ADD A,R6<br>ADD A,R7   | 5E H   | ANL A,RO<br>ANL A,R7     |

| 25 1         |                        |        |                          |

# **2.3.** INSTRUCTION SET BRIEF – HEXADECIMAL ORDER

All trademarks mentioned in this document are trademarks of their respective owners.

| Opcode | Mnemonic            | Opcode | Mnemonic                             |

|--------|---------------------|--------|--------------------------------------|

| 60 H   | JZ rel              | 90 H   | MOV DPTR,#data16<br>MOV DPTR,#data24 |

| 61 H   | AJMP addr11         | 91 H   | ACALL addr11                         |

| 62 H   | XRL direct,A        | 92 H   | MOV bit,C                            |

| 63 H   | XRL direct,#data    | 93 H   | MOVC A,@A+DPTR                       |

| 64 H   | XRL A,#data         | 94 H   | SUBB A,#data                         |

| 65 H   | XRL A, direct       | 95 H   | SUBB A, direct                       |

| 66 H   | XRL A,@R0           | 96 H   | SUBB A,@R0                           |

| 67 H   | XRL A,@R1           | 97 H   | SUBB A,@R1                           |

| 68 H   | XRL A, 80           | 98 H   | SUBB A,R0                            |

| 69 H   | XRL A,R1            | 99 H   | SUBB A,R1                            |

| 6A H   | XRL A,R2            | 9A H   | SUBB A,R2                            |

| 6B H   | XRL A,R3            | 9B H   | SUBB A,R3                            |

| 6C H   | XRL A,R4            | 9C H   | SUBB A,R4                            |

| 6D H   | XRL A,R5            | 9D H   | SUBB A,R5                            |

| 6E H   | XRL A,R6            | 9E H   | SUBB A,R6                            |

| 6F H   | XRL A,R7            | 9F H   | SUBB A,R7                            |

| 70 H   | JNZ rel             | A0 H   | ORL C,bit                            |

| 70 H   | ACALL addr11/addr19 | A1 H   | AJMP addr11/addr19                   |

| 71 H   | ORL C, direct       | A2 H   | MOV C,bit                            |

| 72 H   | JMP @A+DPTR         | A3 H   | INC DPTR                             |

| 74 H   | MOV A,#data         | A4 H   | MUL AB                               |

| 74 H   | MOV direct,#data    | A5 H   | -                                    |

| 76 H   | MOV @R0,#data       | A6 H   | MOV @R0,direct                       |

| 70 H   | MOV @R1,#data       | A7 H   | MOV @R1,direct                       |

| 78 H   | MOV @1(1,#data      | A8 H   | MOV @RI,direct                       |

| 70 H   | MOV R1.#data        | A9 H   | MOV R0,direct                        |

| 70 H   | MOV R2.#data        | AAH    | MOV R2,direct                        |

| 7B H   | MOV R3.#data        | ABH    | MOV R3,direct                        |

| 7C H   | MOV R4.#data        | AC H   | MOV R4,direct                        |

| 7D H   | MOV R5.#data        | AD H   | MOV R5,direct                        |

| 7E H   | MOV R6.#data        | AEH    | MOV R6, direct                       |

| 7F H   | MOV R7.#data        | AFH    | MOV R7, direct                       |

| 80 H   | SJMP rel            | B0 H   | ANL C,bit                            |

| 81 H   | AJMP addr11/addr19  | B1 H   | ACALL addr11/addr19                  |

| 82 H   | ANL C,bit           | B2 H   | CPL bit                              |

| 83 H   | MOVC A,@A+PC        | B3 H   | CPL C                                |

| 84 H   | DIV AB              | B4 H   | CJNE A,#data,rel                     |

| 85 H   | MOV direct, direct  | B5 H   | CJNE A,direct,rel                    |

| 86 H   | MOV direct,@R0      | B6 H   | CJNE @R0,#data,rel                   |

| 87 H   | MOV direct,@R1      | B7 H   | CJNE @R1,#data,rel                   |

| 88 H   | MOV direct,R0       | B8 H   | CJNE R0,#data,rel                    |

| 89 H   | MOV direct,R1       | B9 H   | CJNE R1,#data,rel                    |

| 8A H   | MOV direct,R2       | BAH    | CJNE R2,#data,rel                    |

| 8B H   | MOV direct,R3       | BBH    | CJNE R3,#data,rel                    |

| 8C H   | MOV direct,R4       | BC H   | CJNE R4,#data,rel                    |

| 8D H   | MOV direct,R5       | BD H   | CJNE R5,#data,rel                    |

| 8E H   | MOV direct,R6       | BEH    | CJNE R6,#data,rel                    |

| 8F H   | MOV direct,R7       | BFH    | CJNE R7,#data,rel                    |

| Opcode | Mnemonic            | Opcode | Mnemonic            |

|--------|---------------------|--------|---------------------|

| C0 H   | PUSH direct         | E0 H   | MOVX A,@DPTR        |

| C1 H   | AJMP addr11/addr19  | E1 H   | AJMP addr11/addr19  |

| C2 H   | CLR bit             | E2 H   | MOVX A,@R0          |

| C3 H   | CLR C               | E3 H   | MOVX A,@R1          |

| C4 H   | SWAP A              | E4 H   | CLR A               |

| C5 H   | XCH A, direct       | E5 H   | MOV A, direct       |

| C6 H   | XCH A,@R0           | E6 H   | MOV A,@R0           |

| C7 H   | XCH A,@R1           | E7 H   | MOV A,@R1           |

| C8 H   | XCH A,R0            | E8 H   | MOV A,R0            |

| C9 H   | XCH A,R1            | E9 H   | MOV A,R1            |

| CA H   | XCH A,R2            | EA H   | MOV A,R2            |

| CB H   | XCH A,R3            | EB H   | MOV A,R3            |

| CC H   | XCH A,R4            | EC H   | MOV A,R4            |

| CD H   | XCH A,R5            | ED H   | MOV A,R5            |

| CE H   | XCH A,R6            | EE H   | MOV A,R6            |

| CF H   | XCH A,R7            | EF H   | MOV A,R7            |

| D0 H   | POP direct          | F0 H   | MOVX @DPTR,A        |

| D1 H   | ACALL addr11/addr19 | F1 H   | ACALL addr11/addr19 |

| D2 H   | SETB bit            | F2 H   | MOVX @R0,A          |

| D3 H   | SETB C              | F3 H   | MOVX @R1,A          |

| D4 H   | DA A                | F4 H   | CPL A               |

| D5 H   | DJNZ direct, rel    | F5 H   | MOV direct, A       |

| D6 H   | XCHD A,@R0          | F6 H   | MOV @R0,A           |

| D7 H   | XCHD A,@R1          | F7 H   | MOV @R1,A           |

| D8 H   | DJNZ R0,rel         | F8 H   | MOV R0,A            |

| D9 H   | DJNZ R1,rel         | F9 H   | MOV R1,A            |

| DA H   | DJNZ R2,rel         | FA H   | MOV R2,A            |

| DB H   | DJNZ R3,rel         | FB H   | MOV R3,A            |

| DC H   | DJNZ R4,rel         | FC H   | MOV R4,A            |

| DD H   | DJNZ R5,rel         | FD H   | MOV R5,A            |

| DE H   | DJNZ R6,rel         | FE H   | MOV R6,A            |

| DF H   | DJNZ R7,rel         | FF H   | MOV R7,A            |

Table 8. Instruction set brief in hexadecimal order

All trademarks mentioned in this document are trademarks of their respective owners.

Copyright 1999-2003 DCD – Digital Core Design. All Rights Reserved.

# **3.** INSTRUCTIONS SET DETAILS

## 3.1. ACALL \*

#### 3.1.1. LARGE

- **Instruction:** ACALL addr11

- Function: Absolute call

- **Description:** ACALL unconditionally calls a subroutine located at the indicated address. The instruction increments the PC twice to obtain the address of the following instruction, then pushes the 16-bit result onto the stack (low-order byte first) and increments the stack pointer twice. The destination address is obtained by successively concatenating the five high-order bits of the incremented PC, opcode bits 7-5, the second byte of the instruction. The subroutine called must therefore start within the same 2K block of program memory as the first byte of the instruction following ACALL. No flags are affected.

| Operation:        | (PC)             | )    | ←            | (PC  | ) + 2 |       |    |    |

|-------------------|------------------|------|--------------|------|-------|-------|----|----|

| •                 | (SP)             | )    | $\leftarrow$ | (SP) | ) + 1 |       |    |    |

|                   | ((SP             | '))  | ←            | (PC  | 7-0)  |       |    |    |

|                   | (SP)             |      | ←            | (SP) | ) + 1 |       |    |    |

|                   | ((SP             | '))  | $\leftarrow$ | (PC  | 15-8) | )     |    |    |

|                   | (PC <sup>-</sup> | 10-0 | ) ←          | page | e ado | dress | 6  |    |

| Bytes:<br>Cycles: | 2<br>4           |      |              |      |       |       |    |    |

| Encoding:         |                  |      |              |      |       |       |    |    |

|                   | a10              | a9   | a8           | 1    | 0     | 0     | 0  | 1  |

|                   | a7               | a6   | a5           | a4   | a3    | a2    | a1 | a0 |

All trademarks mentioned in this document are trademarks of their respective owners.

Instruction: ACALL addr19

- **Function:** Absolute call

- **Description:** ACALL unconditionally calls a subroutine located at the indicated address. The instruction increments the PC triple to obtain the address of the following instruction, then pushes the 24-bit result onto the stack (low-order byte first) and increments the stack pointer triple. The destination address is obtained by successively concatenating the five high-order bits of the incremented PC, opcode bits 7-5, the second and third byte of the instruction. The subroutine called must therefore start within the same 512K block of program memory as the first byte of the instruction following ACALL. No flags are affected.

| Operation:        | (PC)<br>(SP)<br>((SP))<br>(SP)<br>((SP))<br>(SP)<br>((SP))<br>(PC18-0) | $\leftarrow (PC) + 3$ $\leftarrow (SP) + 1$ $\leftarrow (PC7-0)$ $\leftarrow (SP) + 1$ $\leftarrow (PC15-8)$ $\leftarrow (SP) + 1$ $\leftarrow (PC23-16)$ $\leftarrow page address$ |

|-------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bytes:<br>Cycles: | 3<br>5                                                                 |                                                                                                                                                                                     |

Encoding:

| a | a18 | a17 | a16 | 1   | 0   | 0   | 0  | 1  |

|---|-----|-----|-----|-----|-----|-----|----|----|

| a | a15 | a14 | a13 | a12 | a11 | a10 | a9 | a8 |

|   | a7  | a6  | a5  | a4  | a3  | a2  | a1 | a0 |

\* instruction modified regarding to standard 80C51

All trademarks mentioned in this document are trademarks of their respective owners.

# 3.2. ADD

Instruction: ADD A, <src-byte>

- **Function**: Adds A to the source operand and returns the result to A.

- **Description:** ADD adds the byte variable indicated to the accumulator, leaving the result in the accumulator. The carry and auxiliary carry flags are set, respectively, if there is a carry out of bit 7 or bit 3, and cleared otherwise. When adding unsigned integers, the carry flag indicates an overflow occurred. OV is set if there is a carry out of bit 6 but not out of bit 7, or a carry out of bit 7 but not out of bit 6; otherwise OV is cleared. When adding signed integers, OV indicates a negative number produced as the sum of two positive operands, or a positive sum from two negative operands. Four source operand addressing modes are allowed: register, direct, register- indirect, or immediate.

#### 3.2.1. ADD A, RN

| Operation:         | $\begin{array}{l} (PC) \leftarrow (PC) + 1 \\ (A)  \leftarrow (A) + (Rn) \end{array}$     |

|--------------------|-------------------------------------------------------------------------------------------|

| Bytes:<br>Cycles:  | 1<br>1                                                                                    |

| Encoding:          | 0 0 1 0 1 r r r                                                                           |

| 3.2.2. ADD A       | A, DIRECT                                                                                 |

| <b>Operation</b> : | $\begin{array}{l} (PC) \leftarrow (PC) + 2 \\ (A)  \leftarrow (A) + (direct) \end{array}$ |

| Bytes:<br>Cycles:  | 2<br>2                                                                                    |

| Encoding:          |                                                                                           |

All trademarks mentioned in this document are trademarks of their respective owners.

0 0

http://www.DigitalCoreDesign.com http://www.dcd.pl

direct address

1 0 0 1 0 1

# 3.2.3. ADD A, @RI

| Operation:        | (PC)<br>(A) | · · | · / | + 1<br>((Ri) | ) |   |   |

|-------------------|-------------|-----|-----|--------------|---|---|---|

| Bytes:<br>Cycles: | 1<br>2      |     |     |              |   |   |   |

| Encoding:         | 0           | 0   | 1   | 0            | 0 | 1 | 1 |

|                   |             |     |     |              |   |   |   |

#### 3.2.4. ADD A, #DATA

| Operation:        | (PC)<br>(A) | ) ← (<br>← ( | . , |   | ta |   |   |   |                |

|-------------------|-------------|--------------|-----|---|----|---|---|---|----------------|

| Bytes:<br>Cycles: | 2<br>2      |              |     |   |    |   |   |   |                |

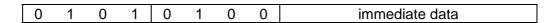

| Encoding:         |             |              |     |   | i  |   |   |   |                |

|                   | 0           | 0            | 1   | 0 | 0  | 1 | 0 | 0 | immediate data |

|                   |             |              |     |   |    |   |   |   |                |

All trademarks mentioned in this document are trademarks of their respective owners.

http://www.DigitalCoreDesign.com http://www.dcd.pl

i

# 3.3. ADDC

**Instruction:** ADDC A, < src-byte>

- **Function:** Adds A and the source operand, then adds one (1) if CY is set, and puts the result in A.

- **Description:** ADDC simultaneously adds the byte variable indicated, the carry flag and the accumulator contents, leaving the result in the accumulator. The carry and auxiliary carry flags are set, respectively, if there is a carry out of bit 7 or bit 3, and cleared otherwise. When adding unsigned integers, the carry flag indicates an overflow occurred. OV is set if there is a carry out of bit 6 but not out of bit 7, or a carry out of bit 7 but not out of bit 6; otherwise OV is cleared. When adding signed integers, OV indicates a negative number produced as the sum of two positive operands or a positive sum from two negative operands. Four source operand-addressing modes are allowed: register= direct, registerindirect, or immediate.

#### 3.3.1. ADDC A, RN

| Operation: | $\begin{array}{ll} (PC) \leftarrow (PC) + 1 \\ (A) & \leftarrow (A) + (C) + (Rn) \end{array}$ |

|------------|-----------------------------------------------------------------------------------------------|

| Bytes:     | 1                                                                                             |

| Cycles:    | 1                                                                                             |

**Encoding:**

| 0 0 1 1 | 1 r | r | r |

|---------|-----|---|---|

|---------|-----|---|---|

#### 3.3.2. ADDC A, DIRECT

| _ |

|---|

All trademarks mentioned in this document are trademarks of their respective owners.

# - 20 -

# 3.3.3. ADDC A, @RI

| Operation:        | (PC)<br>(A) |   | ` ' | + 1<br>(C) | + ((R | (i)) |   |   |

|-------------------|-------------|---|-----|------------|-------|------|---|---|

| Bytes:<br>Cycles: | 1<br>2      |   |     |            |       |      |   |   |

| Encoding:         |             |   |     |            |       |      |   |   |

|                   | 0           | 0 | 1   | 1          | 0     | 1    | 1 | i |

|                   |             |   |     |            |       |      |   |   |

#### 3.3.4. ADDC A, #DATA

| Operation:        | • •    | ) ← (<br>← ( |   |   | + #da | ata |   |   |                |

|-------------------|--------|--------------|---|---|-------|-----|---|---|----------------|

| Bytes:<br>Cycles: | 2<br>2 |              |   |   |       |     |   |   |                |

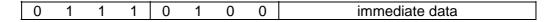

| Encoding:         |        |              |   |   |       |     |   |   |                |

| _                 | 0      | 0            | 1 | 1 | 0     | 1   | 0 | 0 | immediate data |

|                   |        |              |   |   |       |     |   |   |                |

All trademarks mentioned in this document are trademarks of their respective owners.

## 3.4. AJMP \*

#### 3.4.1. LARGE

- Instruction: AJMP addr11

- **Function:** Absolute jump

- **Description:** AJMP transfers program execution to the indicated address, which is formed at runtime by concatenating the high-order five bits of the PC (*after* incrementing the PC twice), opcode bits 7-5, the second byte of the instruction. The destination must therefore be within the same 2K block of program memory as the first byte of the instruction following AJMP.

| Operation:        | (PC)<br>(PC10-0) | $\leftarrow (PC) + 2 \\ \leftarrow page address$ |  |

|-------------------|------------------|--------------------------------------------------|--|

| Bytes:<br>Cycles: | 2<br>3           |                                                  |  |

| Encoding:         |                  |                                                  |  |

| a10<br>a7 | a9 | a8 | 0  | 0  | 0  | 0  | 1  |

|-----------|----|----|----|----|----|----|----|

| a7        | a6 | a5 | a4 | a3 | a2 | a1 | a0 |

#### 3.4.2. FLAT

| Instruction: | AJMP addr19 |

|--------------|-------------|

|--------------|-------------|

- **Function:** Absolute jump

- **Description:** AJMP transfers program execution to the indicated address, which is formed at runtime by concatenating the high-order five bits of the PC (*after* incrementing the PC triple), opcode bits 7-5, the second and the third byte of the instruction. The destination must therefore be within the same 512K block of program memory as the first byte of the instruction following AJMP.

| Operation: | ( ) | $\leftarrow (PC) + 3 \\ \leftarrow page address$ |

|------------|-----|--------------------------------------------------|

| Bytes:     | 3   |                                                  |

4

Cycles:

#### **Encoding:**

| a18 | a17 | a16 | 0   | 0   | 0   | 0  | 1  |

|-----|-----|-----|-----|-----|-----|----|----|

| a15 | a14 | a13 | a12 | a11 | a10 | a9 | a8 |

| a7  | a6  | a5  | a4  | a3  | a2  | a1 | a0 |

\* instruction modified regarding to standard 80C51

# 3.5. ANL

Instruction: ANL <dest-byte>, <src-byte>

- **Function:** Logical AND for byte operands

- **Description:** ANL performs the bit wise logical AND operation between the variables indicated and stores the results in the destination variable. No flags are affected (except P, if <dest-byte> = A). The two operands allow six addressing mode combinations. When the destination is a accumulator, the source can use register, direct, register-indirect, or immediate addressing; when the destination is a direct address, the source can be the accumulator or immediate data.

- **Note:** When this instruction is used to modify an output port, the value used as the original port data will be read from the output data latch, not the input pins.

#### 3.5.1. ANL A, RN

| Operation: | $\begin{array}{ll} (PC) \leftarrow (PC) + 1 \\ (A) & \leftarrow (A) \text{ and } (Rn) \end{array}$ |

|------------|----------------------------------------------------------------------------------------------------|

| Bytes:     | 1                                                                                                  |

| Cycles:    | 1                                                                                                  |

**Encoding:**

| 0 1 0 1 | 1 r | r | r |

|---------|-----|---|---|

|---------|-----|---|---|

#### 3.5.2. ANL A, DIRECT

| Operation:        | $\begin{array}{l} (PC) \leftarrow (PC) + 2 \\ (A)  \leftarrow (A) \text{ and (direct)} \end{array}$ |   |   |          |   |   |   |   |                |

|-------------------|-----------------------------------------------------------------------------------------------------|---|---|----------|---|---|---|---|----------------|

| Bytes:<br>Cycles: | 2<br>2                                                                                              |   |   |          |   |   |   |   |                |

| Encoding:         |                                                                                                     |   |   | <u>.</u> | - |   |   |   |                |

|                   | 0                                                                                                   | 1 | 0 | 1        | 0 | 1 | 0 | 1 | direct address |

All trademarks mentioned in this document are trademarks of their respective owners.

#### 3.5.3. ANL A, @RI

| Operation: | $\begin{array}{ll} (PC) \leftarrow (PC) + 1 \\ (A) & \leftarrow (A) \text{ and } ((Ri)) \end{array}$ |

|------------|------------------------------------------------------------------------------------------------------|

| Bytes:     | 1                                                                                                    |

| Cycles:    | 2                                                                                                    |

Cycles:

**Encoding:**

#### 3.5.4. ANL A, #DATA

| Operation: | (PC) $\leftarrow$ (PC) + 2<br>(A) $\leftarrow$ (A) and #data |

|------------|--------------------------------------------------------------|

|            |                                                              |

| Bytes:  | 2 |

|---------|---|

| Cycles: | 2 |

#### **Encoding:**

#### 3.5.5. ANL DIRECT, A

| Operation:        | (PC)<br>(dire |   | • | ' | 2<br>and | (A) |   |   |                |

|-------------------|---------------|---|---|---|----------|-----|---|---|----------------|

| Bytes:<br>Cycles: | 2<br>3        |   |   |   |          |     |   |   |                |

| Encoding:         | 0             | 1 | 0 | 1 | 0        | 0   | 1 | 0 | direct address |

#### 3.5.6. ANL DIRECT, #DATA

| Operation:        | (PC)<br>(dire  |      | ⊢ (P<br>⊢ (di                                                               | ,    |   | #da | ta |   |

|-------------------|----------------|------|-----------------------------------------------------------------------------|------|---|-----|----|---|

| Bytes:<br>Cycles: | 3<br>3         |      |                                                                             |      |   |     |    |   |

| Encoding:         |                |      |                                                                             |      |   |     |    |   |

|                   | 0              | 1    | 0                                                                           | 1    | 0 | 0   | 1  | 1 |

|                   | direct address |      |                                                                             |      |   |     |    |   |

|                   | immediate data |      |                                                                             |      |   |     |    |   |

| Instruction:      | ANL            | C, < | <src-l< th=""><th>oit&gt;</th><th></th><th></th><th></th><th></th></src-l<> | oit> |   |     |    |   |

All trademarks mentioned in this document are trademarks of their respective owners.

**Function:** Logical AND for bit operands

**Description:** If the Boolean value of the source bit is a logic 0 then clear the carry flag; otherwise leave the carry flag in its current state. A slash ("/" preceding the operand in the assembly language indicates that the logical complement of the addressed bit is used as the source value, *but the source bit itself is not affected.* No other flags are affected. Only direct bit addressing is allowed for the source operand.

#### 3.5.7. ANL C, BIT

| Operation: | $(PC) \leftarrow (PC) + 2$     |

|------------|--------------------------------|

|            | (C) $\leftarrow$ (C) and (bit) |

|            |                                |

2 2

Bytes: Cycles:

**Encoding:**

#### 3.5.8. ANL C, /BIT

| Operation:        | (PC)<br>(C) | ) ← (<br>← ( |   |   | (bit) |   |   |   |             |

|-------------------|-------------|--------------|---|---|-------|---|---|---|-------------|

| Bytes:<br>Cycles: | 2<br>2      |              |   |   |       |   |   |   |             |

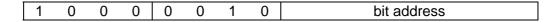

| Encoding:         |             |              | 4 |   |       |   |   | 0 |             |

|                   | 1           | 0            | 1 | 1 | 0     | 0 | 0 | 0 | bit address |

# 3.6. CJNE

**Instruction:** CJNE <dest-byte >, < src-byte >, rel

- **Function:** Compare and jump if not equal.

- **Description:** CJNE compares the magnitudes of the first two operands, and branches if their values are not equal. The branch destination is computed by adding the signed relative displacement in the last instruction byte to the PC, after incrementing the PC to the start of the next instruction. The carry flag is set if the unsigned integer value of <dest-byte> is less than the unsigned integer value of <src-byte>; otherwise, the carry is cleared. Neither operand is affected. The first two operands allow four addressing mode combinations: the accumulator may be compared with any directly addressed byte or immediate data, and any indirect RAM location or working register can be compared with an immediate constant.

#### 3.6.1. CJNE A, DIRECT, REL

| Operation:        | $(PC) \leftarrow (PC) + 3$                                                 |

|-------------------|----------------------------------------------------------------------------|

|                   | if (A) < > (direct) then<br>(PC) $\leftarrow$ (PC) + relative offset       |

|                   | if (A) < (direct) then<br>(C) $\leftarrow 1$<br>else<br>(C) $\leftarrow 0$ |

| Bytes:<br>Cycles: | 3<br>5                                                                     |

| Encoding:         |                                                                            |

|                   | 1 0 1 1 0 1 0 1                                                            |

|                   | direct address                                                             |

|                   | relative address                                                           |

All trademarks mentioned in this document are trademarks of their respective owners.

#### 3.6.2. CJNE A, #DATA, REL

| Operation:        | $(PC) \leftarrow (PC) + 3$                                             |

|-------------------|------------------------------------------------------------------------|

|                   | if (A) < > data then<br>(PC) $\leftarrow$ (PC) + relative offset       |

|                   | if (A) < data then<br>(C) $\leftarrow 1$<br>else<br>(C) $\leftarrow 0$ |

| Bytes:<br>Cycles: | 3<br>4                                                                 |

| Encoding:         |                                                                        |

| 1                | 0              | 1 | 1 | 0 | 1 | 0 | 0 |  |

|------------------|----------------|---|---|---|---|---|---|--|

|                  | immediate data |   |   |   |   |   |   |  |

| relative address |                |   |   |   |   |   |   |  |

Copyright 1999-2003 DCD - Digital Core Design. All Rights Reserved.

#### 3.6.3. CJNE RN, #DATA, REL

| Operation:        | $(PC) \leftarrow (PC) + 3$                                              |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

|                   | if (Rn) < > data then<br>(PC) $\leftarrow$ (PC) + relative offset       |  |  |  |  |  |  |

|                   | if (Rn) < data then<br>(C) $\leftarrow 1$<br>else<br>(C) $\leftarrow 0$ |  |  |  |  |  |  |

| Bytes:<br>Cycles: | 3<br>4                                                                  |  |  |  |  |  |  |

| Encoding:         |                                                                         |  |  |  |  |  |  |

|                   | 1 0 1 1 1 r r r                                                         |  |  |  |  |  |  |

|                   | immediate data                                                          |  |  |  |  |  |  |

|                   | relative address                                                        |  |  |  |  |  |  |

|                   |                                                                         |  |  |  |  |  |  |

#### 3.6.4. CJNE @RI, #DATA, REL

| Operation:        | $(PC) \leftarrow (PC) + 3$                                                |

|-------------------|---------------------------------------------------------------------------|

|                   | if ((Ri)) < > data then<br>(PC) $\leftarrow$ (PC) + relative offset       |

|                   | if ((Ri)) < data then<br>(C) $\leftarrow 1$<br>else<br>(C) $\leftarrow 0$ |

| Bytes:<br>Cycles: | 3<br>5                                                                    |

| Encoding:         |                                                                           |

|                   | 1 0 1 1 0 1 1                                                             |

|                   | immediate data                                                            |

relative address

All trademarks mentioned in this document are trademarks of their respective owners.

http://www.DigitalCoreDesign.com http://www.dcd.pl

i

Copyright 1999-2003 DCD – Digital Core Design. All Rights Reserved.

# 3.7. CLR

#### 3.7.1. CLR A

**Description:** The accumulator is cleared (all bits set to zero). No flags are affected.

| Operation:        | (PC)<br>(A) | • | , | + 1 |   |   |   |   |

|-------------------|-------------|---|---|-----|---|---|---|---|

| Bytes:<br>Cycles: | 1<br>1      |   |   |     |   |   |   |   |

| Encoding:         | 1           | 1 | 1 | 0   | 0 | 1 | 0 | 0 |

#### 3.7.2. CLR BIT

| Function:         | Clear bit                                                                    |

|-------------------|------------------------------------------------------------------------------|

| Description:      | The indicated bit is cleared (reset to zero). No other flags are affected.   |

| Operation:        | $\begin{array}{l} (PC) \leftarrow (PC) + 2 \\ bit  \leftarrow 0 \end{array}$ |

| Bytes:<br>Cycles: | 2<br>3                                                                       |

| Encoding:         | 1 1 0 0 0 0 1 0 bit address                                                  |

All trademarks mentioned in this document are trademarks of their respective owners.

#### 3.7.3. CLR C

| Function:         | Clear carry                                                                   |

|-------------------|-------------------------------------------------------------------------------|

| Description:      | The carry flag is cleared (reset to zero). No other flags are affected.       |

| Operation:        | $\begin{array}{l} (PC) \leftarrow (PC) + 1 \\ (C) & \leftarrow 0 \end{array}$ |

| Bytes:<br>Cycles: | 1<br>1                                                                        |

| Encoding:         |                                                                               |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |

|---|---|---|---|---|---|---|---|

|   |   | 0 | 0 | 0 | 0 |   |   |

All trademarks mentioned in this document are trademarks of their respective owners.

## 3.8. CPL

#### 3.8.1. CPL A

- Function: Complement accumulator

- **Description:** Each bit of the accumulator is logically complemented (one's complement). Bits which previously contained a one are changed to zero and vice versa. No flags are affected.

**Operation:** (PC)  $\leftarrow$  (PC) + 1 (A)  $\leftarrow$  / (A)

1

1

Bytes: Cycles:

#### **Encoding:**

| 1 1 1 1 | 0 1 | 0 0 |

|---------|-----|-----|

|---------|-----|-----|

#### 3.8.2. CPL BIT

| Function: | Complement bit |

|-----------|----------------|

|-----------|----------------|

- **Description:** The bit variable specified is complemented. A bit which had been a one is changed to zero and vice versa. No other flags are affected. CPL can operate on the carry or any directly addressable bit.

- **Note:** When this instruction is used to modify an output pin, the value used as the original data will be read from the output data latch, not the input pin.

$(PC) \leftarrow (PC) + 2$ **Operation:** (C)  $\leftarrow$  (bit) Bytes: 2 3 Cycles: Encoding: 1 0 1 1 0 0 1 0 bit address

All trademarks mentioned in this document are trademarks of their respective owners.

#### 3.8.3. CPL C

| Function:          | Complement carry                                                                               |  |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Description:       | he carry flag is complemented. A bit which had been a one is changed<br>b zero and vice versa. |  |  |  |  |  |  |

| <b>Operation</b> : | $\begin{array}{l} (PC) \leftarrow (PC) + 1 \\ (C)  \leftarrow / (C) \end{array}$               |  |  |  |  |  |  |

| Bytes:<br>Cycles:  | 1<br>1                                                                                         |  |  |  |  |  |  |

| Encoding:          | 1 0 1 1 0 0 1 1                                                                                |  |  |  |  |  |  |

All trademarks mentioned in this document are trademarks of their respective owners.

http://www.DigitalCoreDesign.com http://www.dcd.pl

Copyright 1999-2003 DCD – Digital Core Design. All Rights Reserved.

# 3.9. DA

Instruction: DA A

**Function:** Decimal adjust accumulator for addition

**Description:** DA A adjusts the eight-bit value in the accumulator resulting from the earlier addition of two variables (each in packed BCD format), producing two four-bit digits. Any ADD or ADDC instruction may have been used to perform the addition. If accumulator bits 3-0 are greater than nine (xxxx1010-xxxx1111), or if the AC flag is one, six is added to the accumulator producing the proper BCD digit in the low- order nibble. This internal addition would set the carry flag if a carry-out of the low-order four-bit field propagated through all high-order bits, but it would not clear the carry flag otherwise.

If the carry flag is now set, or if the four high-order bits now exceed nine (1010xxxx-1111xxxx), these high-order bits are incremented by six, producing the proper BCD digit in the high-order nibble. Again, this would set the carry flag if there was a carry-out of the high-order bits, but wouldn't clear the carry. The carry flag thus indicates if the sum of the original two BCD variables is greater than 100, allowing multiple precision decimal addition. OV is not affected.

All of this occurs during the one instruction cycle. Essentially; this instruction performs the decimal conversion by adding 00 H, 06 H, 60 H, or 66 H to the accumulator, depending on initial accumulator and PSW conditions.

0

- **Note:** DA A *cannot* simply convert a hexadecimal number in the accumulator to BCD notation, nor does DA A apply to decimal subtraction.

- Operation:  $(PC) \leftarrow (PC) + 1$ if  $[[(A3-0) > 9] \land [(AC) = 1]]$  then  $(A3-0) \leftarrow (A3-0) + 6$ next if  $[[(A7-4) > 9] \land [(C) = 1]]$  then  $(A7-4) \leftarrow (A7-4) + 6$

| Cycles.   | 3 |   |   |   |   |   |   |

|-----------|---|---|---|---|---|---|---|

| Encoding: |   |   |   |   |   |   |   |

|           | 1 | 1 | 0 | 1 | 0 | 1 | 0 |

1

2

All trademarks mentioned in this document are trademarks of their respective owners.

Bytes:

Cycles

# 3.10. DEC

Instruction: DEC byte

- Function: Decrement byte

- **Description:** The variable indicated is decremented by 1. An original value of 00 H will underflow to 0FF H. No flags are affected. Four operand addressing modes are allowed: accumulator, register, direct, or register-indirect.

- **Note:** When this instruction is used to modify an output port, the value used as the original port data will be read from the output data latch, *not* the input pins.

#### 3.10.1. DEC A

| Operation:        | $(PC) \leftarrow (PC) + 1$<br>(A) $\leftarrow$ (A) - 1 |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------|--|--|--|--|--|--|

| Bytes:<br>Cycles: | 1<br>1                                                 |  |  |  |  |  |  |

| Encoding:         | 0 0 0 1 0 1 0 0                                        |  |  |  |  |  |  |

| 3.10.2.           | DEC RN                                                 |  |  |  |  |  |  |

| Operation:        | (PC) ← (PC) + 1<br>(Rn) ← (Rn) - 1                     |  |  |  |  |  |  |

| Bytes:<br>Cycles: | 1<br>2                                                 |  |  |  |  |  |  |

| Encoding:         |                                                        |  |  |  |  |  |  |

All trademarks mentioned in this document are trademarks of their respective owners.

| Operation: | $\begin{array}{ll} (PC) & \leftarrow (PC) + 2 \\ (direct) & \leftarrow (direct) - 1 \end{array}$ |

|------------|--------------------------------------------------------------------------------------------------|

| Bytes:     | 2                                                                                                |

Cycles: 3

**Encoding:**

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | direct address |

|---|---|---|---|---|---|---|---|----------------|

| 0 | 0 | 0 |   | 0 |   | 0 |   |                |

| 3.10.4. | DEC @RI |

|---------|---------|

|---------|---------|

| Operation:        | (PC)<br>((Ri)) |   | · / |   |   |

|-------------------|----------------|---|-----|---|---|

| Bytes:<br>Cycles: | 1<br>3         |   |     |   |   |

| Encoding:         |                |   |     |   | - |

|                   | 0              | 0 | 0   | 1 | 0 |

All trademarks mentioned in this document are trademarks of their respective owners.

http://www.DigitalCoreDesign.com http://www.dcd.pl

1

1

i

# 3.11. DIV

| Instruction: | DIV AB |

|--------------|--------|

|--------------|--------|

- Function: Divide

- **Description:** DIV AB divides the unsigned eight-bit integer in the accumulator by the unsigned eight-bit integer in register B. The accumulator receives the integer part of the quotient; register B receives the integer remainder. The carry and OV flags will be cleared.

- **Exception:** If B had originally contained 00 H, the values returned in the accumulator and B register will be undefined and the overflow flag will be set. The carry flag is cleared in any case.

| Operation:        | (A15   | 5-8) | ← (P)<br>← (A)<br>← (A) | ) / (B | ) – re |   |   | 158<br>70 |

|-------------------|--------|------|-------------------------|--------|--------|---|---|-----------|

| Bytes:<br>Cycles: | 1<br>6 |      |                         |        |        |   |   |           |

| Encoding:         | 1      | 0    | 0                       | 0      | 0      | 1 | 0 | 0         |

All trademarks mentioned in this document are trademarks of their respective owners.

# 3.12. DJNZ

- Instruction: DJNZ <byte>, <rel-addr>

- **Function:** Decrement and jump if not zero

- **Description:** DJNZ decrements the location indicated by 1, and branches to the address indicated by the second operand if the resulting value is not zero. An original value of 00 H will underflow to 0FF H. No flags are affected. The branch destination would be computed by adding the signed relative-displacement value in the last instruction byte to the PC, after incrementing the PC to the first byte of the following instruction. The location decremented may be a register or directly addressed byte.

- **Note:** When this instruction is used to modify an output port, the value used as the original port data will be read from the output data latch, not the input pins.

### 3.12.1. DJNZ RN, REL

| Operation: | $(PC) \leftarrow (PC) + 2$   |

|------------|------------------------------|

|            | (Rn) ← (Rn) - 1              |

|            | if (Rn) ≠ 0 then             |

|            | $(PC) \leftarrow (PC) + rel$ |

|            |                              |

| Bytes:  | 2 |

|---------|---|

| Cycles: | 4 |

| Encoding: |   |   |   |   |   |   |   |   |                  |

|-----------|---|---|---|---|---|---|---|---|------------------|

|           | 1 | 1 | 0 | 1 | 1 | r | r | r | relative address |

#### **DJNZ** DIRECT, REL 3.12.2.

| <b>Operation:</b> | $(PC) \leftarrow (PC) + 3$         |

|-------------------|------------------------------------|

|                   | $(direct) \leftarrow (direct) - 1$ |

|                   | if (direct) ≠ 0 then               |