Microcontrollers

Edition 2006-03

Published by

Infineon Technologies AG

81726 München, Germany

© Infineon Technologies AG 2006.

All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XC164CM

16-Bit Single-Chip Microcontroller with C166SV2 Core

Volume 2 (of 2): Peripheral Units

Microcontrollers

XC164CM, Volume 2 (of 2): Peripheral Units Revision History: V1.2, 2006-03

Previous Version(s):

V1.1, 2005-11

V1.0, 2005-06

| v 1.0, 2000                                       | V 1.0, 2000 00                                                                            |  |  |  |  |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Page                                              | Subjects                                                                                  |  |  |  |  |  |  |

| Major Changes from V1.1, 2005-11 to V1.2, 2006-02 |                                                                                           |  |  |  |  |  |  |

| 19-32                                             | Last row: Br8 baudrate changed                                                            |  |  |  |  |  |  |

| 21-10                                             | Figure 21-4 corrected                                                                     |  |  |  |  |  |  |

| 21-11                                             | Formula corrected                                                                         |  |  |  |  |  |  |

| 21-35,                                            | The position of two figures in the CAN chapter swapped.                                   |  |  |  |  |  |  |

| 21-36                                             |                                                                                           |  |  |  |  |  |  |

| Major Cha                                         | inges from V1.0, 2005-06 to V1.1, 2005-11                                                 |  |  |  |  |  |  |

| 21-83                                             | TwinCAN implementation: erroneous references to non-existing pins (P4) corrected.         |  |  |  |  |  |  |

| 17-1                                              | CAPCOM2: erroneous references to T0 and T1 (from CAPCOM1) instead of T7 and T8 corrected. |  |  |  |  |  |  |

| 16-4,<br>16-7                                     | ADC sample time - formula corrected (bittfield ADSTC).                                    |  |  |  |  |  |  |

### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

User's Manual V1.2, 2006-03

# **Table of Contents**

This User's Manual consists of two Volumes, "System Units" and "Peripheral Units". For your convenience this table of contents (and also the keyword index) lists both volumes, so you can immediately find the reference to the desired section in the corresponding document ([1] or [2]).

| 1<br>1.1<br>1.2<br>1.3<br>1.4 | Introduction1-1 [1Members of the 16-bit Microcontroller Family1-3 [1Summary of Basic Features1-5 [1Abbreviations1-9 [1Naming Conventions1-10 [1 |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                             | Architectural Overview                                                                                                                          |

| 2.1                           | Basic CPU Concepts and Optimizations 2-2 [1                                                                                                     |

| 2.1.1                         | High Instruction Bandwidth / Fast Execution 2-4 [1                                                                                              |

| 2.1.2                         | Powerful Execution Units                                                                                                                        |

| 2.1.3                         | High Performance Branch-, Call-, and Loop-Processing 2-6 [1                                                                                     |

| 2.1.4                         | Consistent and Optimized Instruction Formats 2-7 [1                                                                                             |

| 2.1.5                         | Programmable Multiple Priority Interrupt System 2-8 [1                                                                                          |

| 2.1.6                         | Interfaces to System Resources                                                                                                                  |

| 2.2                           | On-Chip System Resources                                                                                                                        |

| 2.3                           | On-Chip Peripheral Blocks                                                                                                                       |

| 2.4                           | Clock Generation                                                                                                                                |

| 2.5                           | Power Management Features                                                                                                                       |

| 2.6                           | On-Chip Debug Support (OCDS)                                                                                                                    |

| 2.7                           | Protected Bits                                                                                                                                  |

| 3                             | Memory Organization 3-1 [1                                                                                                                      |

| 3.1                           | Address Mapping 3-3 [1                                                                                                                          |

| 3.2                           | Special Function Register Areas                                                                                                                 |

| 3.3                           | Data Memory Areas 3-8 [1                                                                                                                        |

| 3.4                           | Program Memory Areas                                                                                                                            |

| 3.5                           | System Stack                                                                                                                                    |

| 3.6                           | IO Areas                                                                                                                                        |

| 3.7                           | Crossing Memory Boundaries                                                                                                                      |

| 3.8                           | The On-Chip Program Flash Module                                                                                                                |

| 3.8.1                         | Flash Operating Modes                                                                                                                           |

| 3.8.2                         | Command Sequences                                                                                                                               |

| 3.8.3                         | Error Correction and Data Integrity                                                                                                             |

| 3.8.4                         | Protection and Security Features                                                                                                                |

| 3.8.5                         | Flash Status Information                                                                                                                        |

| 3.8.6  | Operation Control and Error Handling                           | 3-36 [1] |

|--------|----------------------------------------------------------------|----------|

| 3.9    | Program Memory Control                                         |          |

| 3.9.1  | Address Map                                                    |          |

| 3.9.2  | Flash Memory Access                                            |          |

| 3.9.3  | IMB Control Functions                                          | 3-42 [1] |

| 4      | Central Processing Unit (CPU)                                  |          |

| 4.1    | Components of the CPU                                          |          |

| 4.2    | Instruction Fetch and Program Flow Control                     |          |

| 4.2.1  | Branch Detection and Branch Prediction Rules                   |          |

| 4.2.2  | Correctly Predicted Instruction Flow                           |          |

| 4.2.3  | Incorrectly Predicted Instruction Flow                         |          |

| 4.3    | Instruction Processing Pipeline                                |          |

| 4.3.1  | Pipeline Conflicts Using General Purpose Registers             |          |

| 4.3.2  | Pipeline Conflicts Using Indirect Addressing Modes             |          |

| 4.3.3  | Pipeline Conflicts Due to Memory Bandwidth                     |          |

| 4.3.4  | Pipeline Conflicts Caused by CPU-SFR Updates                   |          |

| 4.4    | CPU Configuration Registers                                    |          |

| 4.5    | Use of General Purpose Registers                               |          |

| 4.5.1  | GPR Addressing Modes                                           |          |

| 4.5.2  | Context Switching                                              |          |

| 4.6    | Code Addressing                                                |          |

| 4.7    | Data Addressing                                                |          |

| 4.7.1  | Short Addressing Modes                                         |          |

| 4.7.2  | Long Addressing Modes                                          |          |

| 4.7.3  | Indirect Addressing Modes                                      |          |

| 4.7.4  | DSP Addressing Modes                                           |          |

| 4.7.5  | The System Stack                                               |          |

| 4.8    | Standard Data Processing                                       | 4-57 [1] |

| 4.8.1  | 16-bit Adder/Subtracter, Barrel Shifter, and 16-bit Logic Unit |          |

| 4.8.2  | Bit Manipulation Unit                                          |          |

| 4.8.3  | Multiply and Divide Unit                                       |          |

| 4.9    | DSP Data Processing (MAC Unit)                                 |          |

| 4.9.1  | Representation of Numbers and Rounding                         |          |

| 4.9.2  | The 16-bit by 16-bit Signed/Unsigned Multiplier and Scaler     |          |

| 4.9.3  | Concatenation Unit                                             |          |

| 4.9.4  | One-bit Scaler                                                 |          |

| 4.9.5  | The 40-bit Adder/Subtracter                                    |          |

| 4.9.6  | The Data Limiter                                               |          |

| 4.9.7  | The Accumulator Shifter                                        |          |

| 4.9.8  | The 40-bit Signed Accumulator Register                         |          |

| 4.9.9  | The MAC Unit Status Word MSW                                   |          |

| 4.9.10 | The Repeat Counter MRW                                         | 4-72 [1] |

**XC164CM**

| 4.10           | Constant Registers                                    | 4-74 [1]             |

|----------------|-------------------------------------------------------|----------------------|

| 5              | Interrupt and Trap Functions                          | 5-1 [1]              |

| 5.1            | Interrupt System Structure                            |                      |

| 5.2            | Interrupt Arbitration and Control                     |                      |

| 5.3            | Interrupt Vector Table                                |                      |

| 5.4            | Operation of the Peripheral Event Controller Channels | 5-18 [1]             |

| 5.4.1          | The PEC Source and Destination Pointers               |                      |

| 5.4.2          | PEC Transfer Control                                  | 5-24 [1]             |

| 5.4.3          | Channel Link Mode for Data Chaining                   | 5-26 [1]             |

| 5.4.4          | PEC Interrupt Control                                 |                      |

| 5.5            | Prioritization of Interrupt and PEC Service Requests  | 5-29 [1]             |

| 5.6            | Context Switching and Saving Status                   | 5-31 [1]             |

| 5.7            | Interrupt Node Sharing                                | 5-34 [1]             |

| 5.8            | External Interrupts                                   | 5-35 [1]             |

| 5.9            | OCDS Requests                                         |                      |

| 5.10           | Service Request Latency                               |                      |

| 5.11           | Trap Functions                                        |                      |

| 6              | General System Control Functions                      | 6-1 [1]              |

| 6.1            | System Reset                                          | 6-2 [1]              |

| 6.1.1          | Reset Sources and Phases                              |                      |

| 6.1.2          | Status After Reset                                    |                      |

| 6.1.3          | Application-Specific Initialization Routine           |                      |

| 6.1.4          | System Startup Configuration                          |                      |

| 6.1.5          | Reset Behavior Control                                |                      |

| 6.2            | Clock Generation                                      |                      |

| 6.2.1          | Oscillator                                            |                      |

| 6.2.2          | Clock Generation and Frequency Control                |                      |

| 6.2.3          | Clock Distribution                                    |                      |

| 6.2.4          | Oscillator Watchdog                                   |                      |

| 6.2.5          | Interrupt Generation                                  |                      |

| 6.2.6          | Generation of an External Clock Signal                |                      |

| 6.3            | Central System Control Functions                      |                      |

| 6.3.1          | Status Indication                                     |                      |

| 6.3.2          | Reset Source Indication                               |                      |

| 6.3.3          | Peripheral Shutdown Handshake                         |                      |

| 6.3.4          | Debug System Control                                  |                      |

| 6.3.5          | Register Security Mechanism                           |                      |

| 6.4            | Power Management                                      |                      |

| 6.4.1          | Power Reduction Modes                                 |                      |

| 6.4.2          | Reduction of Clock Frequencies                        |                      |

| 6.4.2<br>6.4.3 | •                                                     |                      |

| 6.4.3<br>6.5   | Flexible Peripheral Management                        |                      |

| U.U            | vvaionuUU 1111に(VVレー)                                 | U- <del>4</del> / [[ |

| 6.6                                                                                       | Identification Control Block                                                                                                                                                                                                                                                                                                                                               | 6-52 [1]                                                                                             |

|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6                                                    | Parallel Ports Input Threshold Control Output Driver Control Alternate Port Functions Port 1 Port 3 Port 5 Port 9                                                                                                                                                                                                                                                          | . 7-2 [1]<br>. 7-3 [1]<br>. 7-8 [1]<br>. 7-9 [1]<br>7-18 [1]<br>7-30 [1]                             |

| 8                                                                                         | Dedicated Pins                                                                                                                                                                                                                                                                                                                                                             | . 8-1 [1]                                                                                            |

| 9.1<br>9.1.1<br>9.1.2<br>9.2<br>9.2.1<br>9.2.2<br>9.2.3<br>9.2.4<br>9.2.5<br>9.2.6<br>9.3 | The LXBus Controller (EBC) Timing Principles Basic Bus Cycle Protocols Bus Cycle Examples: Fastest Access Cycles Functional Description Configuration Register Overview The Timing Configuration Register TCONCS7 The Function Configuration Register FCONCS7 The Address Window Selection Register ADDRSEL7 Access Control to TwinCAN Shutdown Control EBC Register Table | . 9-1 [1]<br>. 9-1 [1]<br>. 9-2 [1]<br>. 9-3 [1]<br>. 9-3 [1]<br>. 9-5 [1]<br>. 9-6 [1]<br>. 9-8 [1] |

| 10<br>10.1<br>10.2<br>10.3<br>10.4                                                        | The Bootstrap Loader  Entering the Bootstrap Loader  Loading the Startup Code  Exiting Bootstrap Loader Mode  Choosing the Baudrate for the BSL                                                                                                                                                                                                                            | 10-2 [1]<br>10-4 [1]                                                                                 |

| 11<br>11.1<br>11.2<br>11.3<br>11.3.1<br>11.3.2<br>11.4<br>11.4.1                          | Debug System Introduction Debug Interface OCDS Module Debug Events Debug Actions Cerberus Functional Overview                                                                                                                                                                                                                                                              | 11-1 [1]<br>11-2 [1]<br>11-3 [1]<br>11-5 [1]<br>11-6 [1]<br>11-7 [1]                                 |

| 12                                                                                        | Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                    | 12-1 [1]                                                                                             |

| 13                                                                                        | Device Specification                                                                                                                                                                                                                                                                                                                                                       | 13-1 [1]                                                                                             |

| 14                                                                                        | The General Purpose Timer Units                                                                                                                                                                                                                                                                                                                                            | 14-1 [2]                                                                                             |

| 14.1   | Timer Block GPT1                             | 14-2 [2]   |

|--------|----------------------------------------------|------------|

| 14.1.1 | GPT1 Core Timer T3 Control                   |            |

| 14.1.2 | GPT1 Core Timer T3 Operating Modes           |            |

| 14.1.3 | GPT1 Auxiliary Timers T2/T4 Control          |            |

| 14.1.4 | GPT1 Auxiliary Timers T2/T4 Operating Modes  |            |

| 14.1.5 | GPT1 Clock Signal Control                    |            |

| 14.1.6 | GPT1 Timer Registers                         |            |

| 14.1.7 | Interrupt Control for GPT1 Timers            |            |

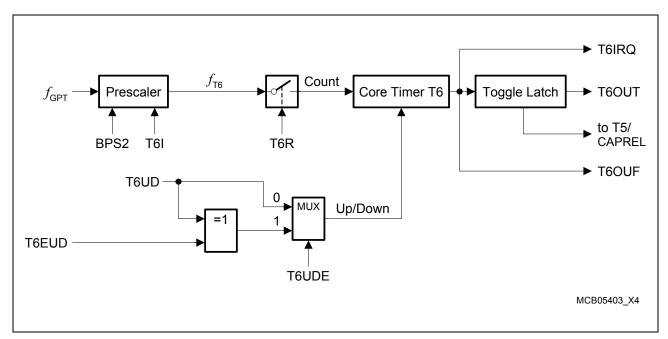

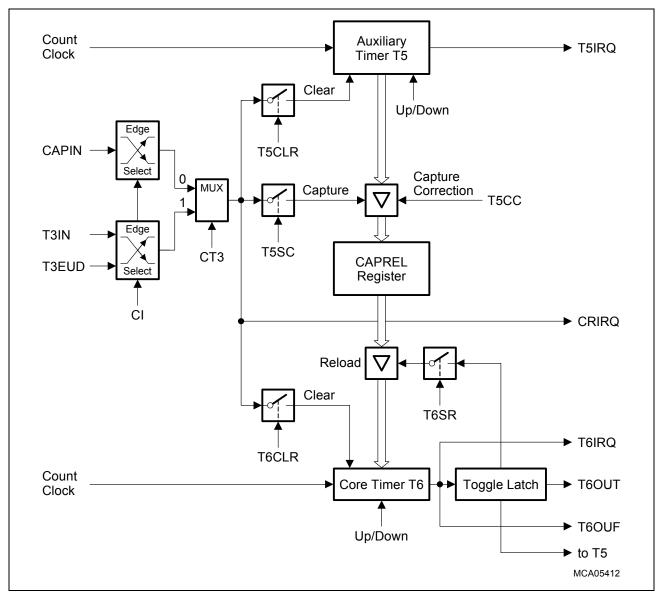

| 14.2   | Timer Block GPT2                             |            |

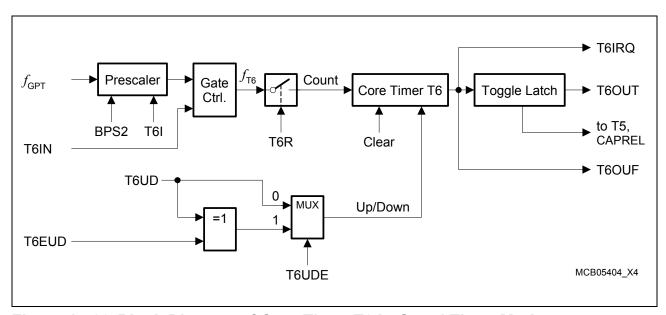

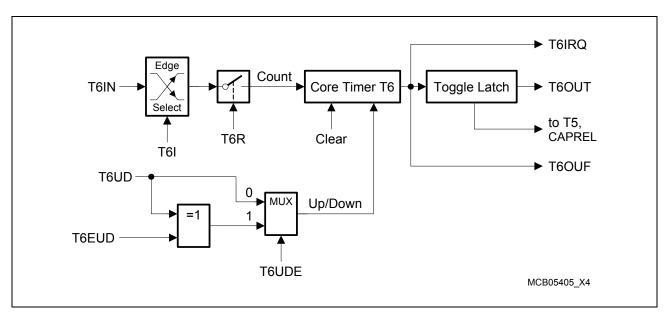

| 14.2.1 | GPT2 Core Timer T6 Control                   |            |

| 14.2.2 | GPT2 Core Timer T6 Operating Modes           |            |

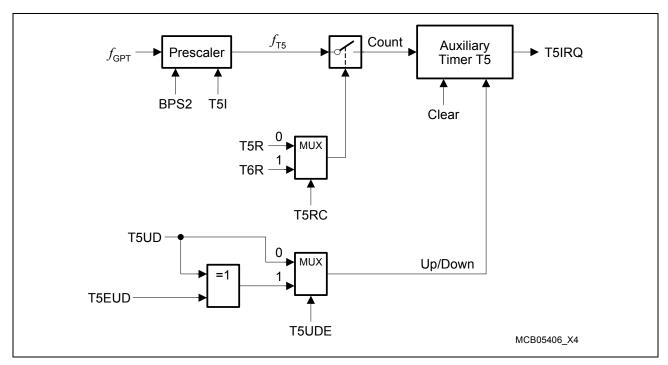

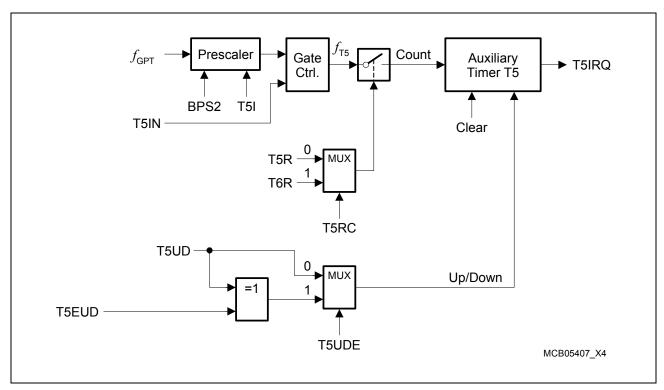

| 14.2.3 | GPT2 Auxiliary Timer T5 Control              |            |

| 14.2.4 | GPT2 Auxiliary Timer T5 Operating Modes      |            |

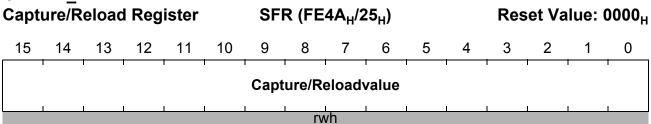

| 14.2.5 | GPT2 Register CAPREL Operating Modes         |            |

| 14.2.6 | GPT2 Clock Signal Control                    |            |

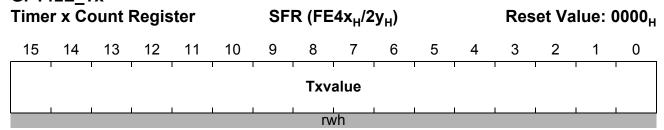

| 14.2.7 | GPT2 Timer Registers                         |            |

| 14.2.8 | Interrupt Control for GPT2 Timers and CAPREL |            |

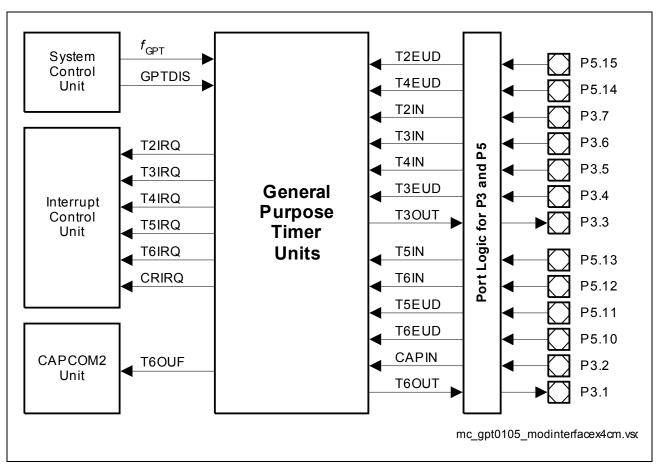

| 14.3   | Interfaces of the GPT Module                 |            |

| 15     | Real Time Clock                              | . 15-1 [2] |

| 15.1   | Defining the RTC Time Base                   | . 15-2 [2  |

| 15.2   | RTC Run Control                              | . 15-5 [2] |

| 15.3   | RTC Operating Modes                          | . 15-7 [2] |

| 15.3.1 | 48-bit Timer Operation                       | 15-10 [2]  |

| 15.3.2 | System Clock Operation                       | 15-10 [2]  |

| 15.3.3 | Cyclic Interrupt Generation                  | 15-11 [2]  |

| 15.4   | RTC Interrupt Generation                     | 15-12 [2]  |

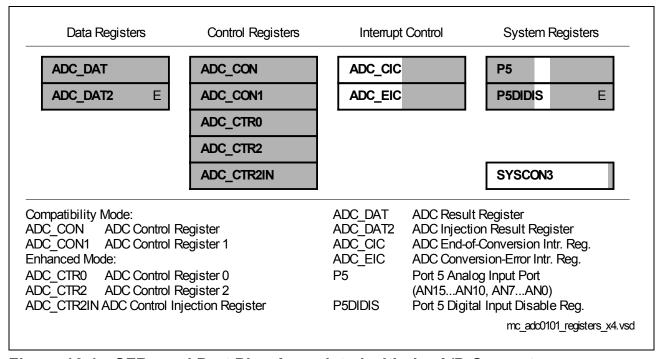

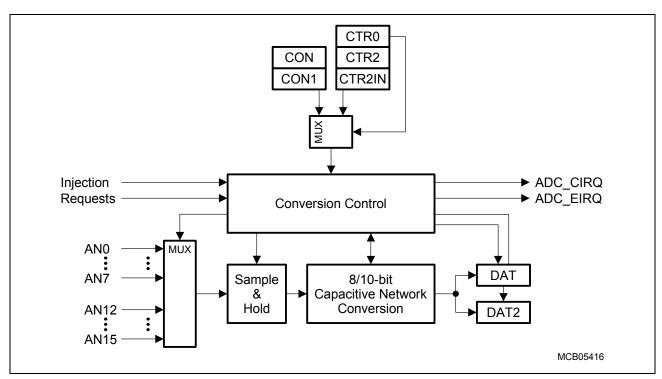

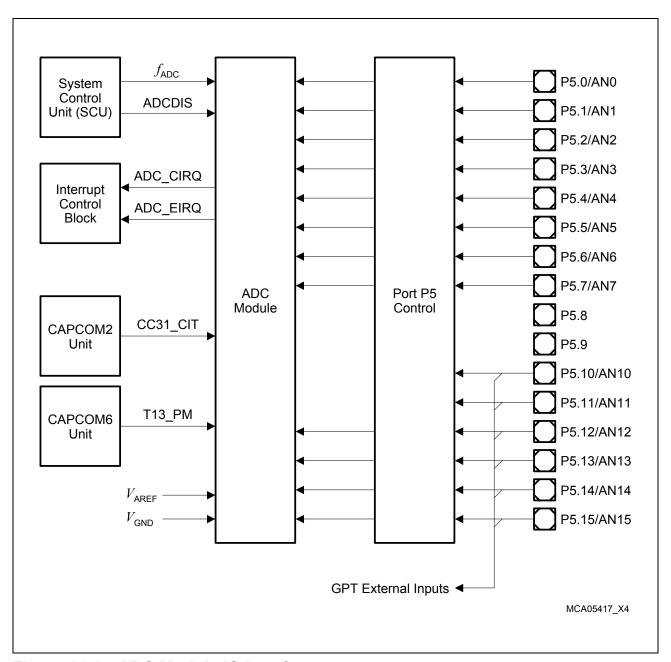

| 16     | The Analog/Digital Converter                 |            |

| 16.1   | Mode Selection                               |            |

| 16.1.1 | Compatibility Mode                           |            |

| 16.1.2 | Enhanced Mode                                |            |

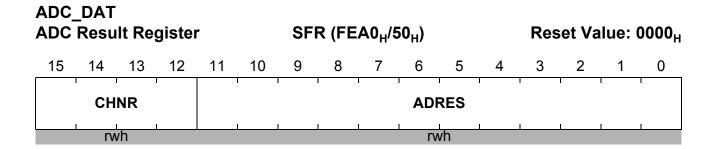

| 16.2   | ADC Operation                                |            |

| 16.2.1 | Fixed Channel Conversion Modes               |            |

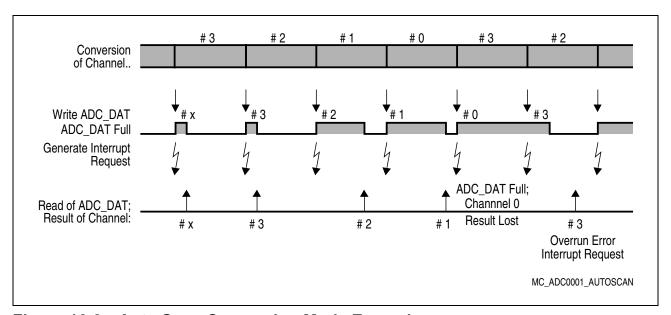

| 16.2.2 | Auto Scan Conversion Modes                   | 16-12 [2]  |

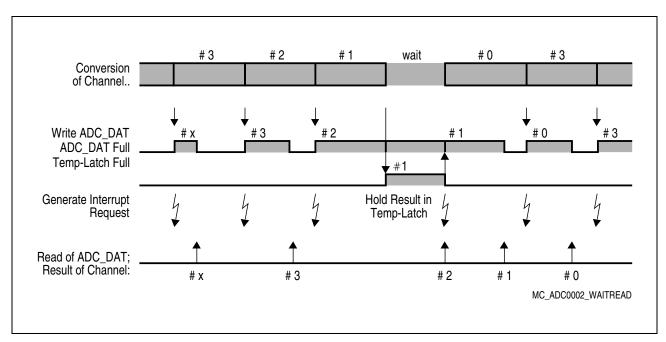

| 16.2.3 | Wait for Read Mode                           |            |

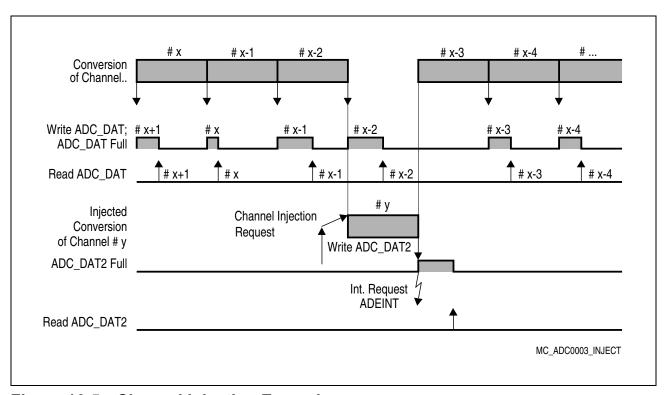

| 16.2.4 | Channel Injection Mode                       | 16-14 [2]  |

| 16.3   | Automatic Calibration                        |            |

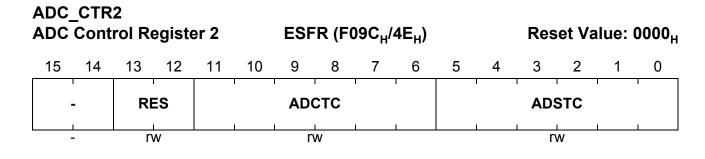

| 16.4   | Conversion Timing Control                    |            |

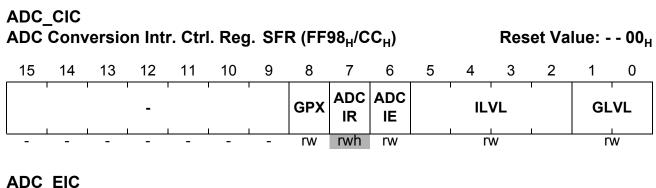

| 16.5   | A/D Converter Interrupt Control              |            |

| 16.6   | Interfaces of the ADC Module                 | 16-22 [2]  |

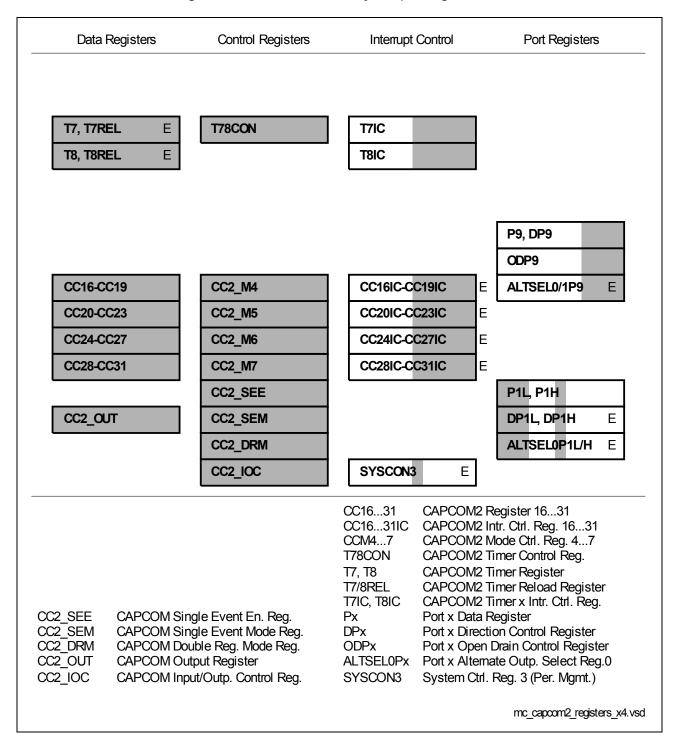

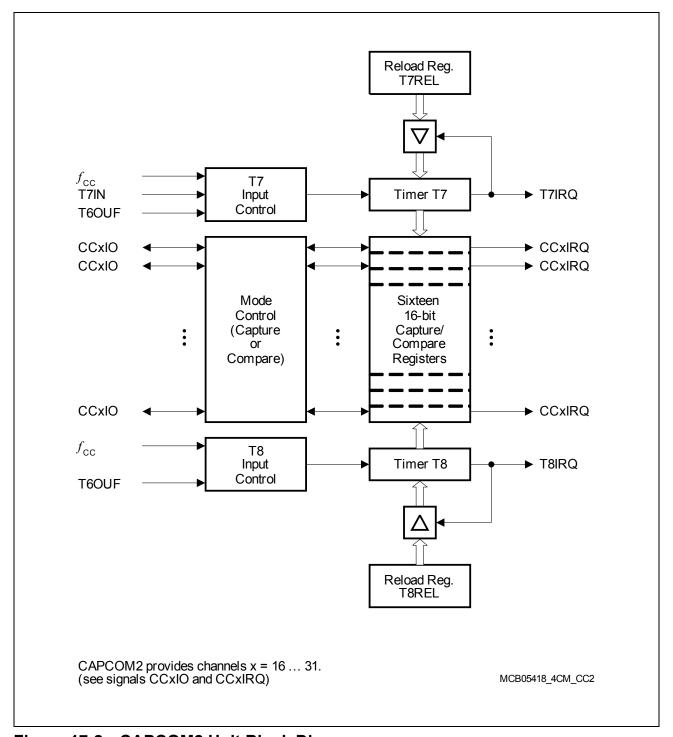

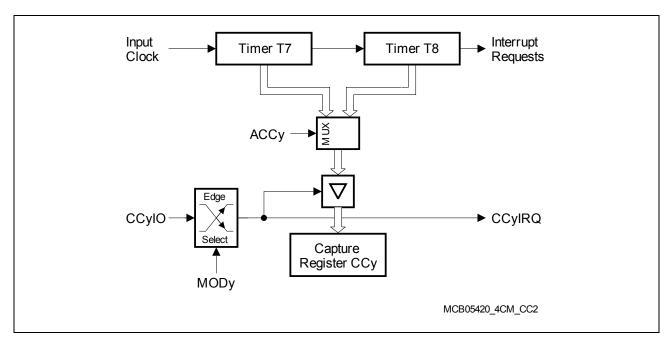

| 17     | Capture/Compare Unit CAPCOM2                 |            |

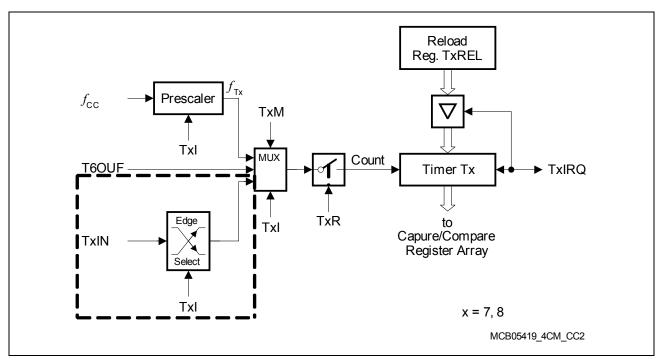

| 17.1   | The CAPCOM2 Timers                           | . 17-4 [2] |

| 17.2   | CAPCOM2 Timer Interrupts                        | 17-9 [2]  |

|--------|-------------------------------------------------|-----------|

| 17.3   | Capture/Compare Channels                        |           |

| 17.4   | Capture Mode Operation                          |           |

| 17.5   | Compare Mode Operation                          |           |

| 17.5.1 | Compare Mode 0                                  |           |

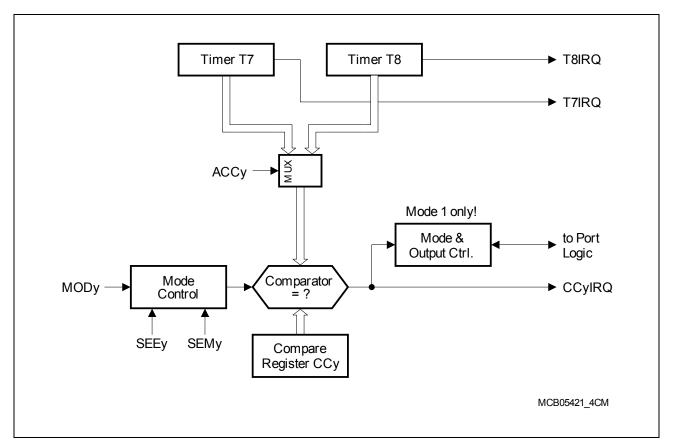

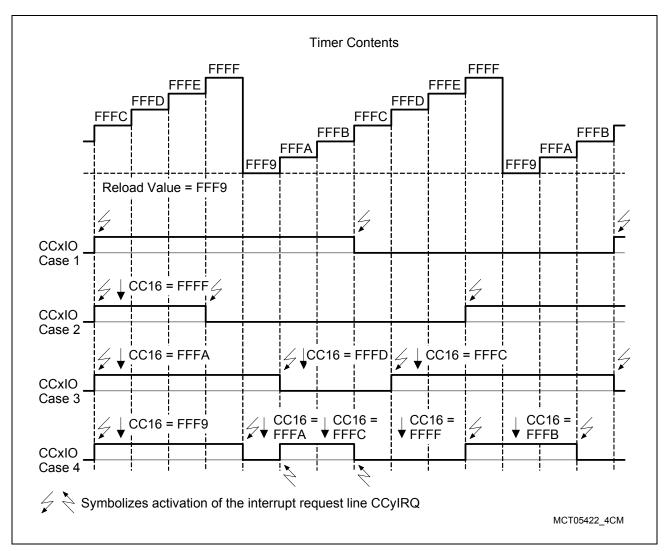

| 17.5.2 | Compare Mode 1                                  | •         |

| 17.5.3 | Compare Mode 2                                  |           |

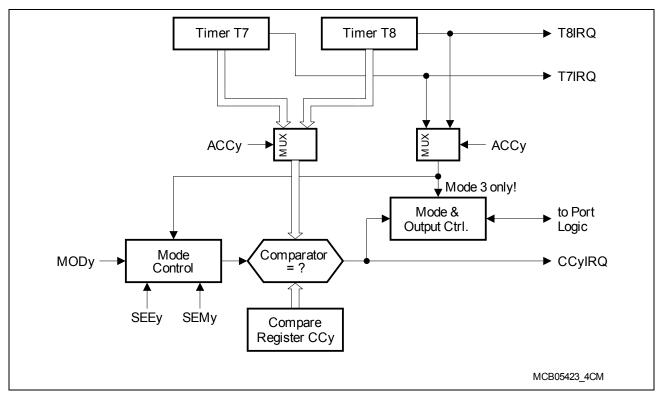

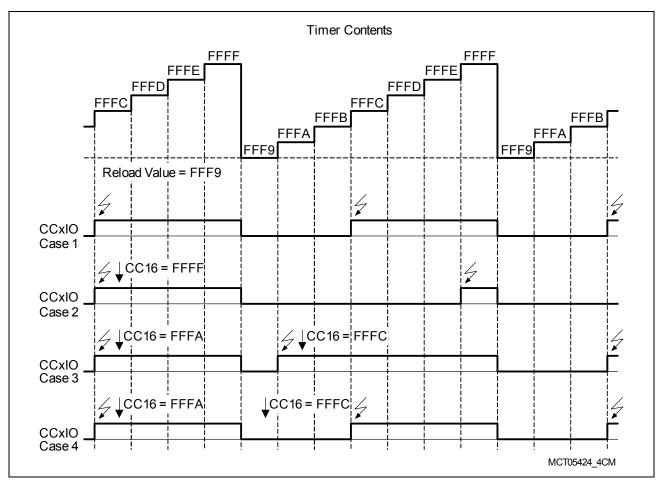

| 17.5.4 | Compare Mode 3                                  | 17-18 [2] |

| 17.5.5 | Double-Register Compare Mode                    |           |

| 17.6   | Compare Output Signal Generation                |           |

| 17.7   | Single Event Operation                          |           |

| 17.8   | Staggered and Non-Staggered Operation           |           |

| 17.9   | CAPCOM2 Interrupts                              |           |

| 17.10  | External Input Signal Requirements              |           |

| 17.11  | Interfaces of the CAPCOM2 Unit                  |           |

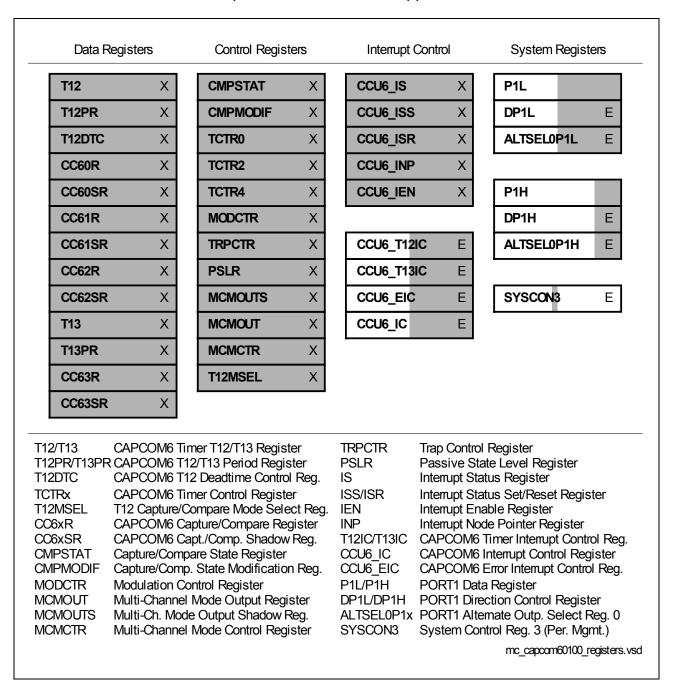

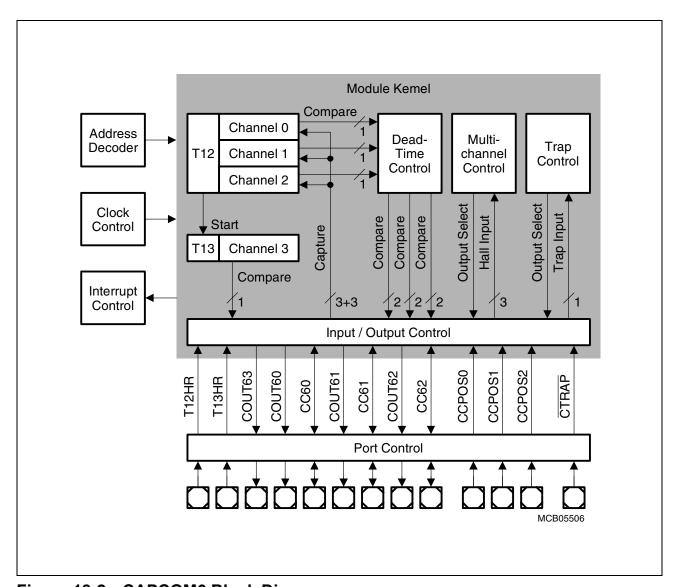

| 18     | Capture/Compare Unit 6 (CAPCOM6)                | 18-1 [2]  |

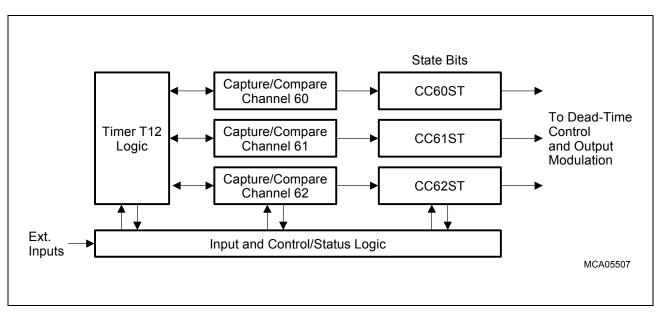

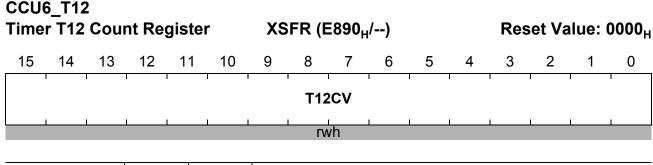

| 18.1   | Timer T12 Block                                 | 18-4 [2]  |

| 18.1.1 | Timer T12 Operation                             | 18-7 [2]  |

| 18.1.2 | T12 Compare Modes                               | 18-12 [2] |

| 18.1.3 | Dead-Time Generation                            | 18-21 [2] |

| 18.1.4 | T12 Capture Modes                               | 18-24 [2] |

| 18.1.5 | Hysteresis-Like Control Mode                    |           |

| 18.2   | Timer T13 Block                                 | 18-29 [2] |

| 18.2.1 | T13 Operation                                   | 18-32 [2] |

| 18.2.2 | T13 Compare Modes                               | 18-37 [2] |

| 18.3   | Timer Block Control                             | 18-41 [2] |

| 18.4   | Multi-Channel Mode                              | 18-47 [2] |

| 18.5   | Hall Sensor Mode                                | 18-50 [2] |

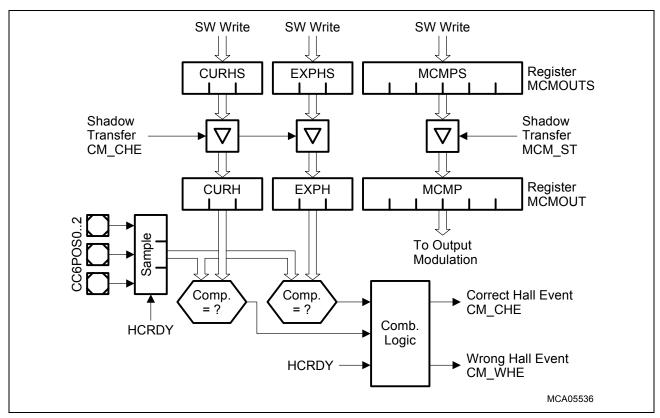

| 18.5.1 | Hall Pattern Compare Logic                      | 18-51 [2] |

| 18.5.2 | Sampling of the Hall Pattern                    | 18-52 [2] |

| 18.5.3 | Brushless DC-Motor Control with Timer T12 Block | 18-53 [2] |

| 18.5.4 | Hall Mode Flags                                 | 18-55 [2] |

| 18.6   | Trap Handling                                   |           |

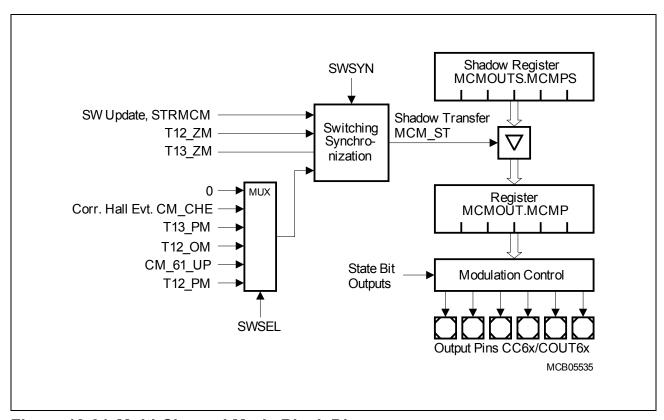

| 18.7   | Output Modulation Control                       | 18-65 [2] |

| 18.8   | Shadow Register Transfer Control                |           |

| 18.9   | Interrupt Generation                            |           |

| 18.10  | Suspend Mode                                    |           |

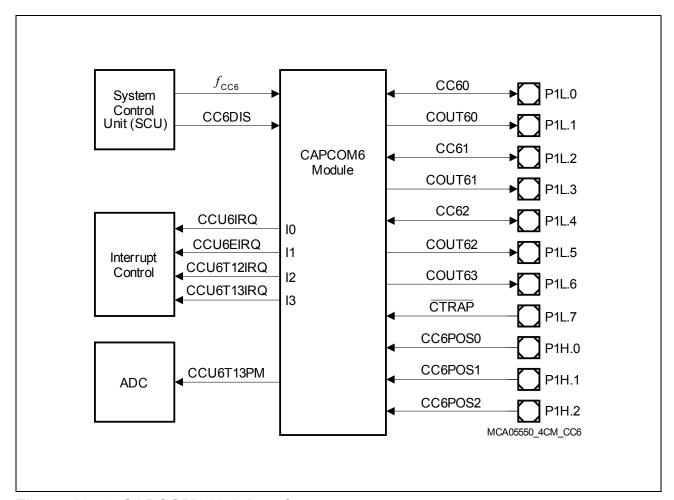

| 18.11  | Interfaces of the CAPCOM6 Unit                  | 18-81 [2] |

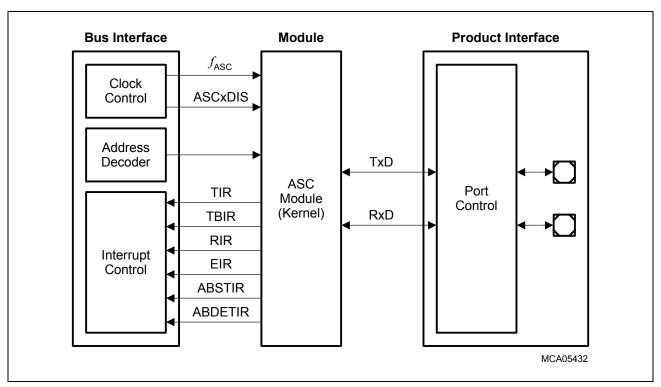

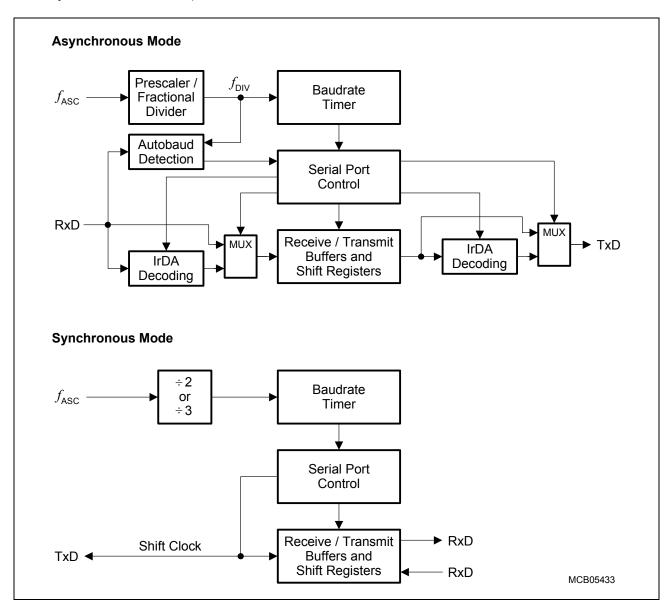

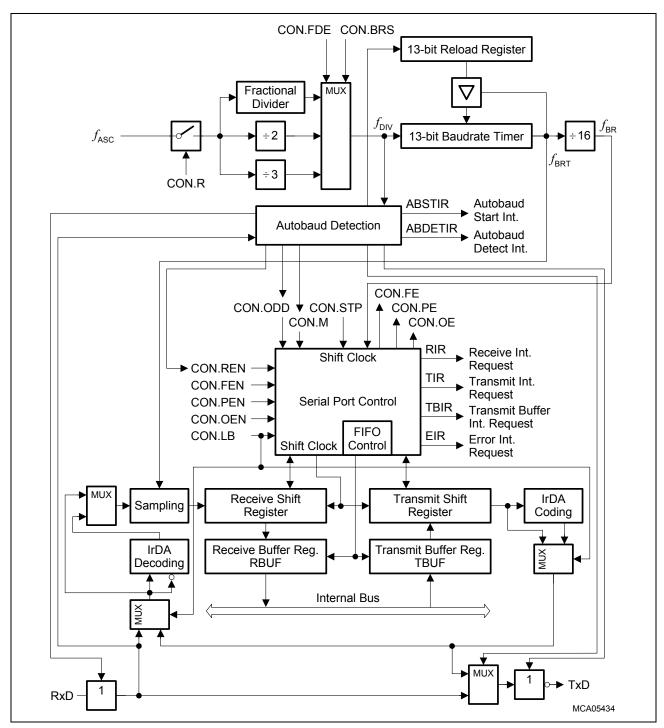

| 19     | Asynchronous/Synchronous Serial Interface (ASC) |           |

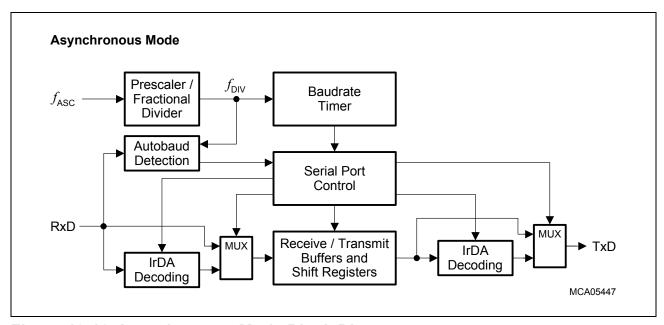

| 19.1   | Operational Overview                            |           |

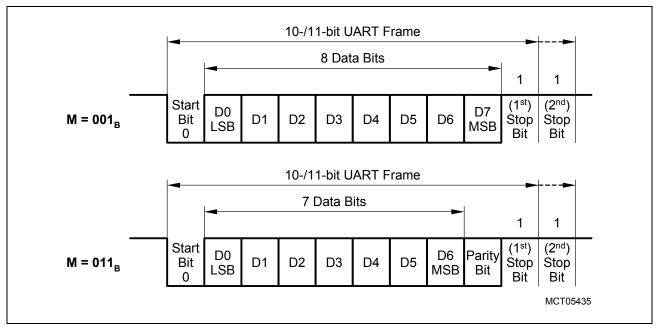

| 19.2   | Asynchronous Operation                          | 19-5 [2]  |

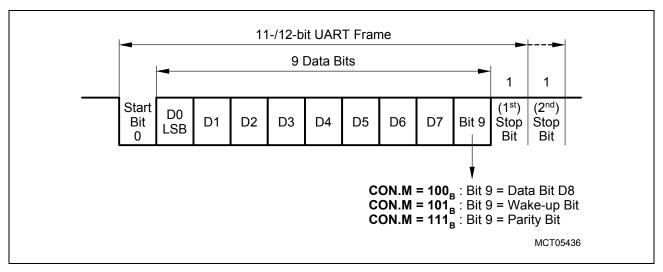

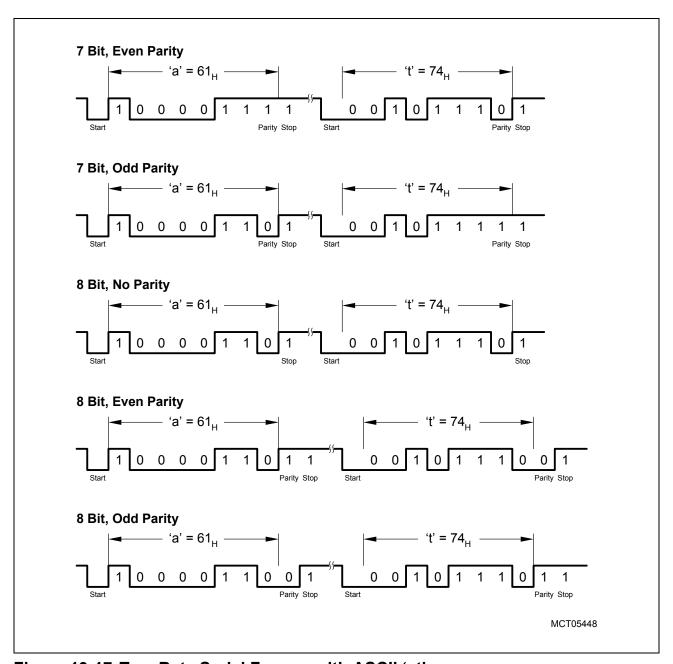

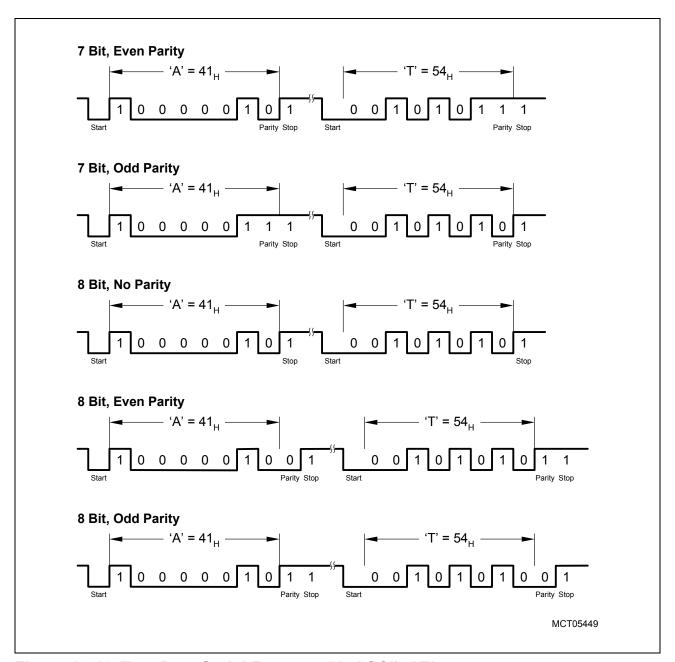

| 19.2.1 | Asynchronous Data Frames                        | 19-6 [2]  |

| 19.2.2   | Asynchronous Transmission                              | 19-9  | [2] |

|----------|--------------------------------------------------------|-------|-----|

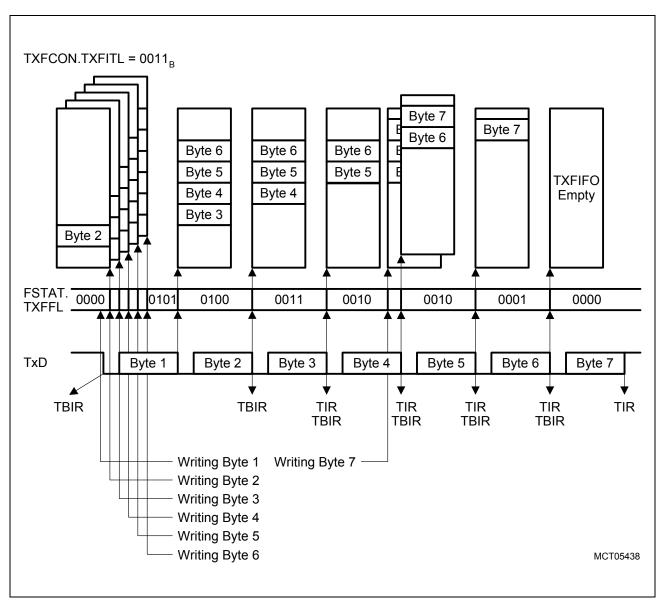

| 19.2.3   | Transmit FIFO Operation                                |       |     |

| 19.2.4   | Asynchronous Reception                                 |       |     |

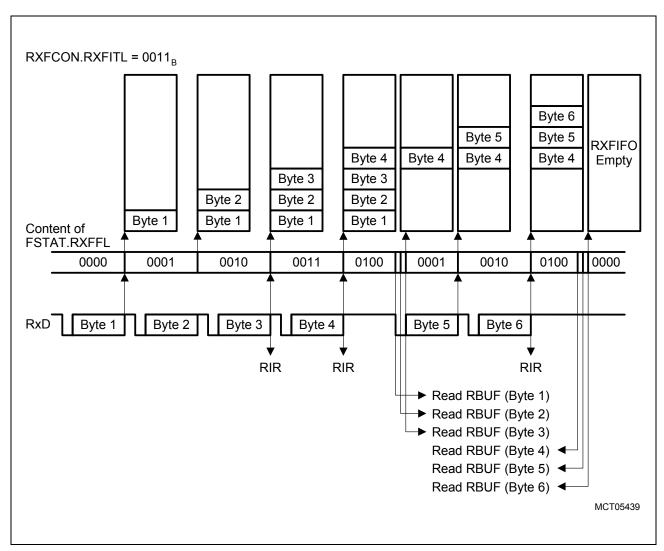

| 19.2.5   | Receive FIFO Operation                                 |       |     |

| 19.2.6   | FIFO Transparent Mode                                  |       |     |

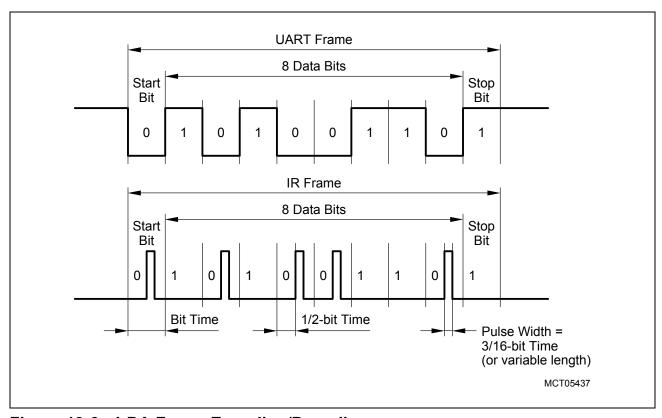

| 19.2.7   | IrDA Mode                                              |       |     |

| 19.2.8   | RxD/TxD Data Path Selection in Asynchronous Modes      |       |     |

| 19.3     | Synchronous Operation                                  | 19-19 | [2] |

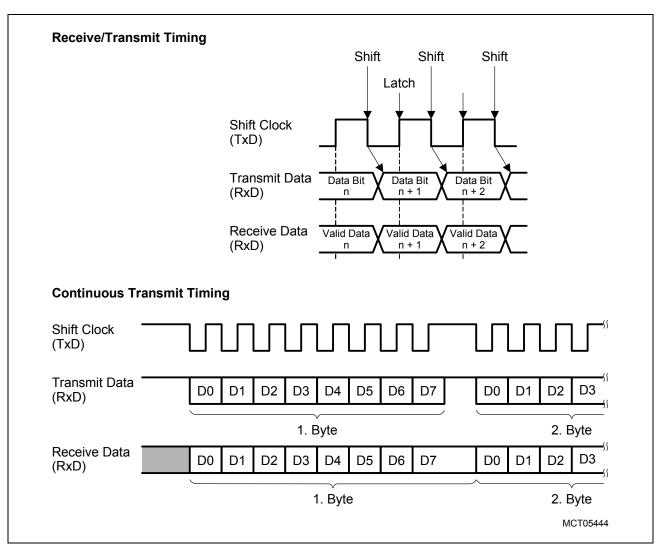

| 19.3.1   | Synchronous Transmission                               | 19-20 | [2] |

| 19.3.2   | Synchronous Reception                                  | 19-20 | [2] |

| 19.3.3   | Synchronous Timing                                     | 19-20 | [2] |

| 19.4     | Baudrate Generation                                    | 19-22 | [2] |

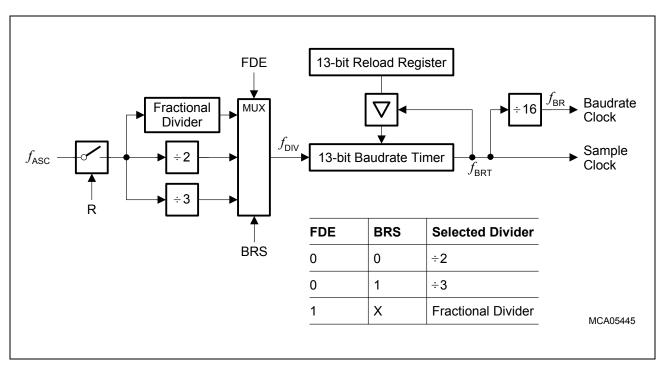

| 19.4.1   | Baudrate in Asynchronous Mode                          | 19-22 | [2] |

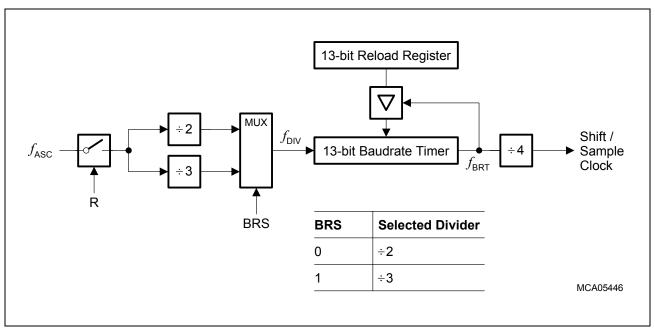

| 19.4.2   | Baudrate in Synchronous Mode                           | 19-26 | [2] |

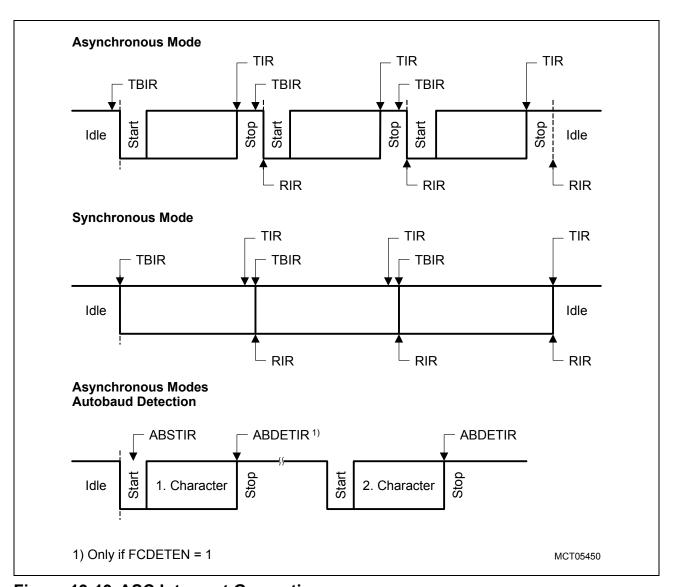

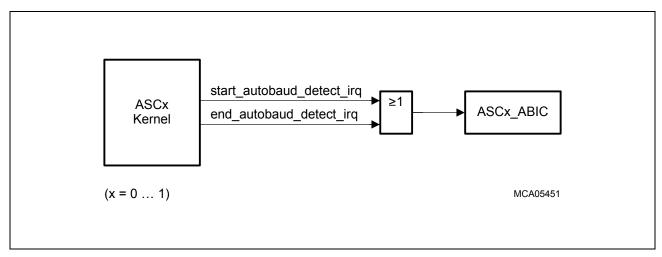

| 19.5     | Autobaud Detection                                     | 19-27 | [2] |

| 19.5.1   | General Operation                                      | 19-27 | [2] |

| 19.5.2   | Serial Frames for Autobaud Detection                   | 19-28 | [2] |

| 19.5.3   | Baudrate Selection and Calculation                     | 19-29 | [2] |

| 19.5.4   | Overwriting Registers on Successful Autobaud Detection | 19-33 | [2] |

| 19.6     | Hardware Error Detection Capabilities                  | 19-34 | [2] |

| 19.7     | Interrupts                                             | 19-35 | [2] |

| 19.8     | Registers                                              |       |     |

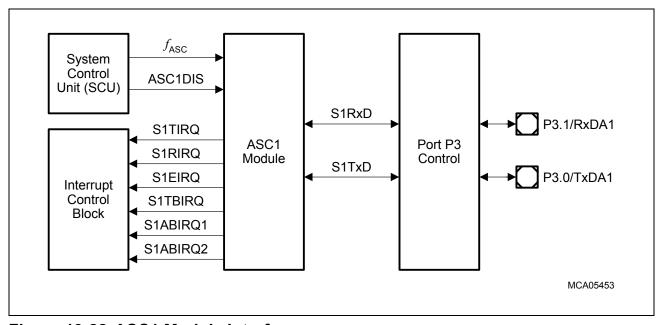

| 19.9     | Interfaces of the ASC Modules                          | 19-56 | [2] |

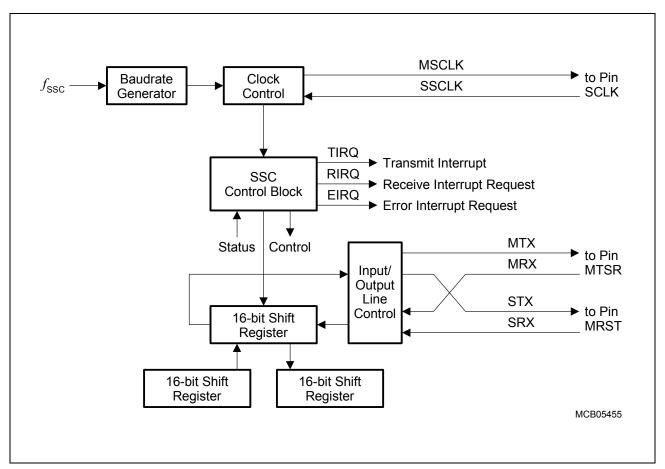

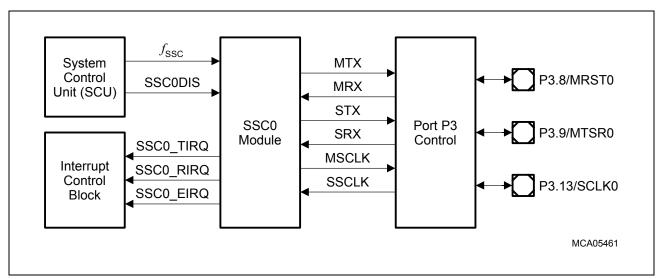

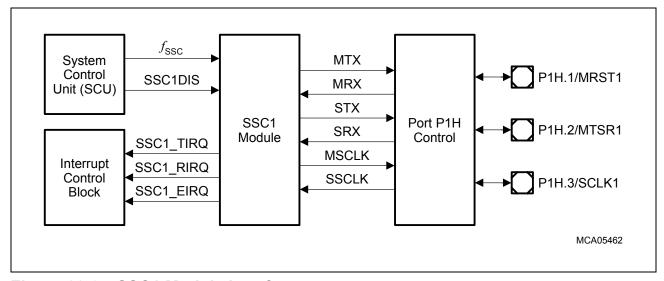

| 20       | High-Speed Synchronous Serial Interface (SSC)          | 20-1  | [2] |

| 20.1     | Introduction                                           |       |     |

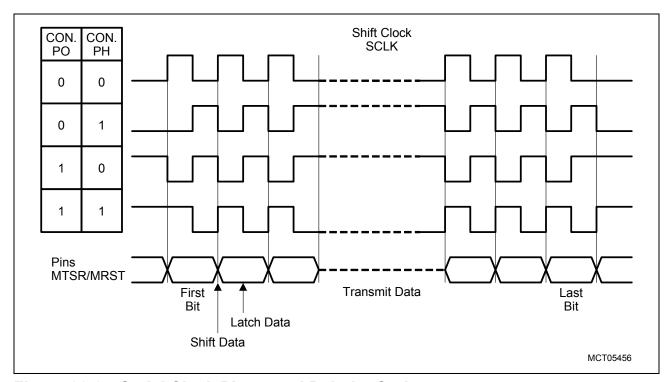

| 20.2     | Operational Overview                                   |       |     |

| 20.2.1   | Operating Mode Selection                               |       |     |

| 20.2.2   | Full-Duplex Operation                                  |       |     |

| 20.2.3   | Half-Duplex Operation                                  | 20-11 | [2] |

| 20.2.4   | Continuous Transfers                                   | 20-12 | [2] |

| 20.2.5   | Baudrate Generation                                    |       |     |

| 20.2.6   | Error Detection Mechanisms                             | 20-14 | [2] |

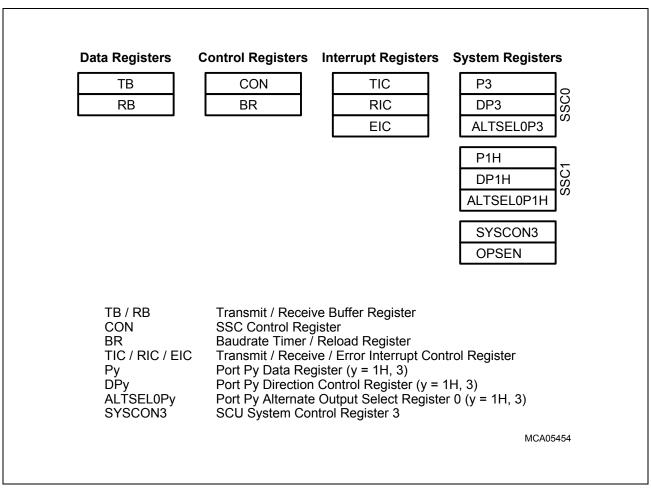

| 20.2.7   | SSC Register Summary                                   | 20-16 | [2] |

| 20.2.8   | Port Configuration Requirements                        | 20-17 | [2] |

| 20.3     | Interfaces of the SSC Modules                          | 20-18 | [2] |

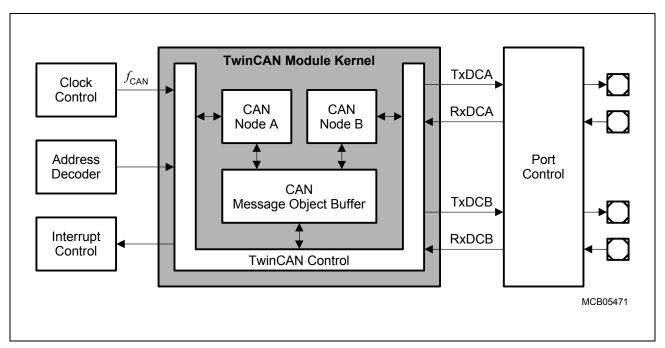

| 21       | TwinCAN Module                                         | 21-1  | [2] |

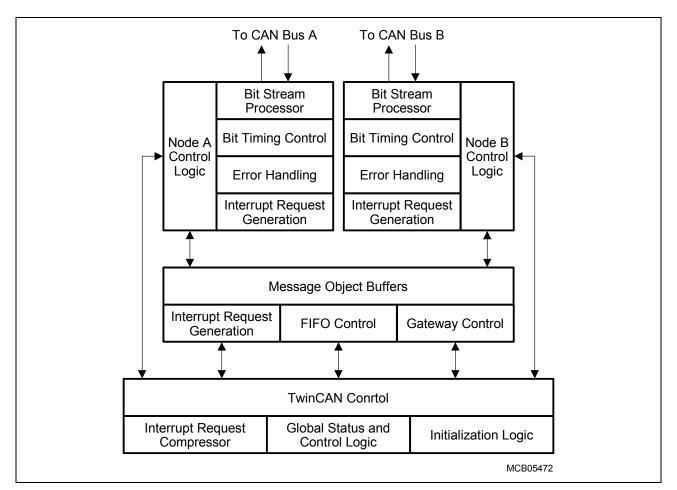

| 21.1     | Kernel Description                                     |       |     |

| 21.1.1   | Overview                                               |       |     |

| 21.1.2   | TwinCAN Control Shell                                  |       |     |

| 21.1.2.1 | Initialization Processing                              |       |     |

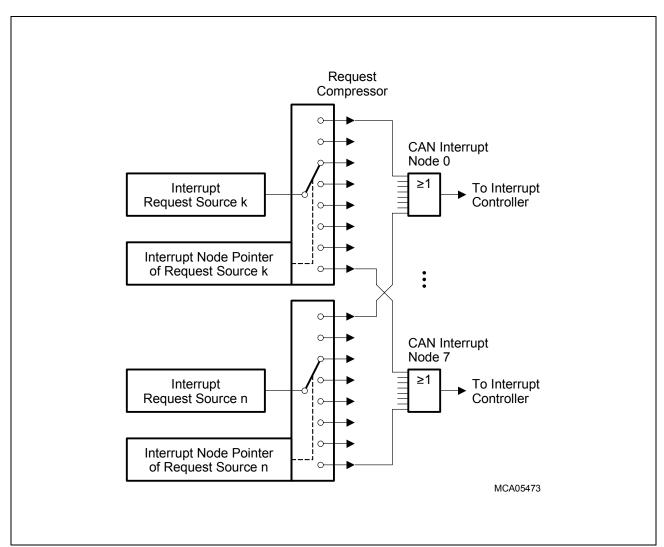

| 21.1.2.2 | Interrupt Request Compressor                           |       |     |

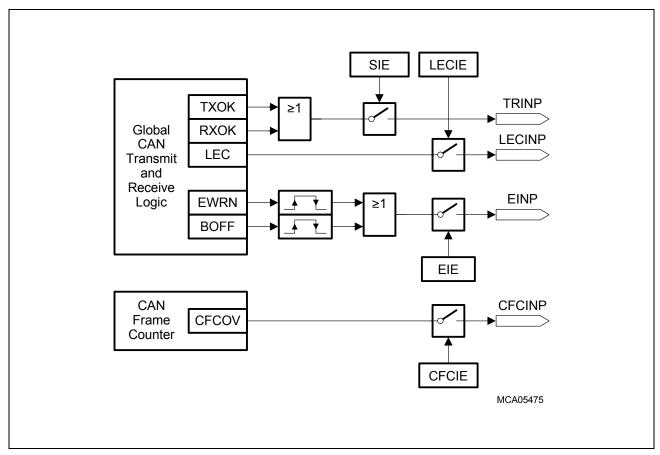

| 21.1.2.3 | Global Control and Status Logic                        |       |     |

| 21.1.3   | CAN Node Control Logic                    | . 21-8 [2] |

|----------|-------------------------------------------|------------|

| 21.1.3.1 | Overview                                  |            |

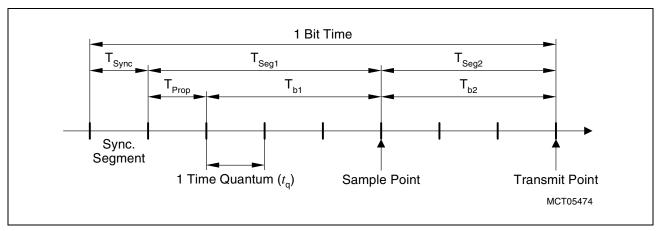

| 21.1.3.2 | Timing Control Unit                       |            |

| 21.1.3.3 | Bitstream Processor                       |            |

| 21.1.3.4 | Error Handling Logic                      |            |

| 21.1.3.5 | Node Interrupt Processing                 |            |

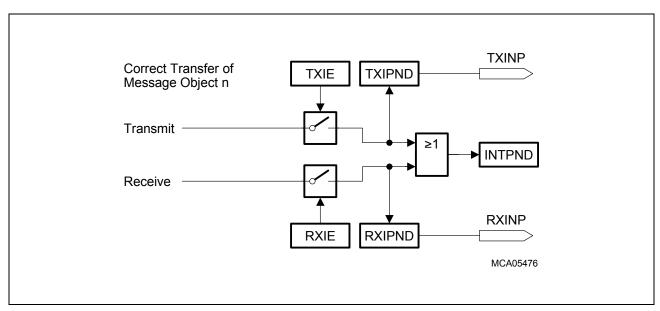

| 21.1.3.6 | Message Interrupt Processing              |            |

| 21.1.3.7 | Interrupt Indication                      |            |

| 21.1.4   | Message Handling Unit                     | 21-16 [2   |

| 21.1.4.1 | Arbitration and Acceptance Mask Register  | 21-17 [2]  |

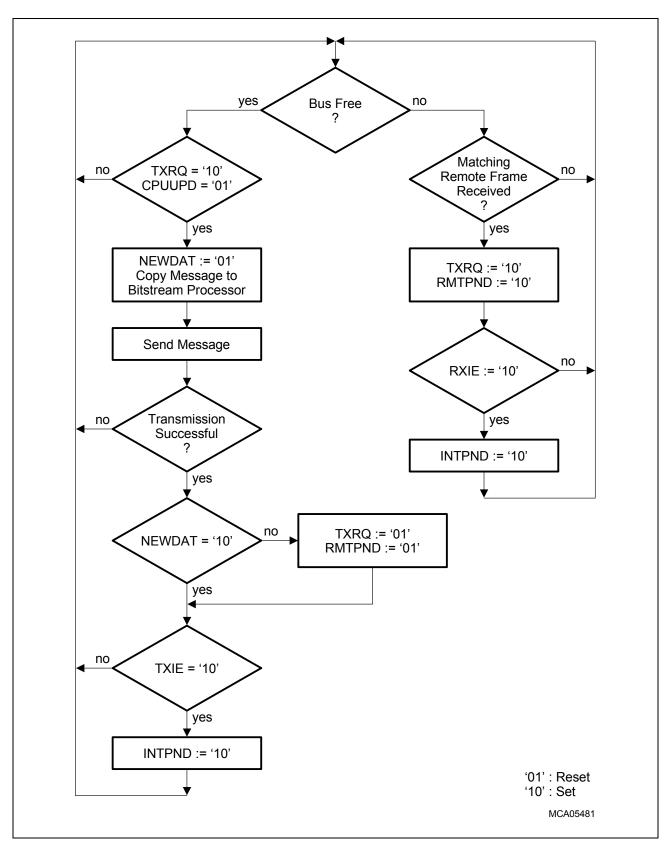

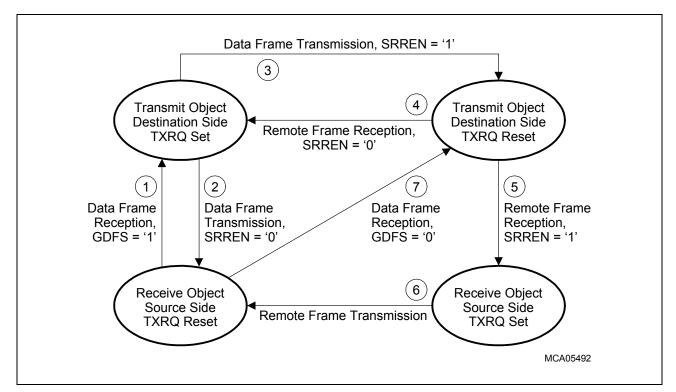

| 21.1.4.2 | Handling of Remote and Data Frames        | 21-18 [2]  |

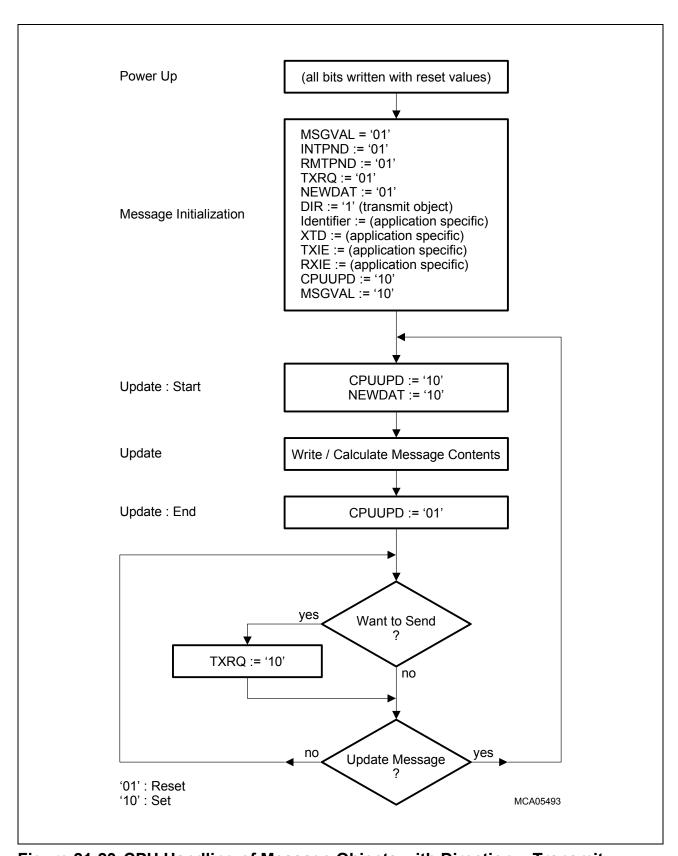

| 21.1.4.3 | Handling of Transmit Message Objects      | 21-19 [2]  |

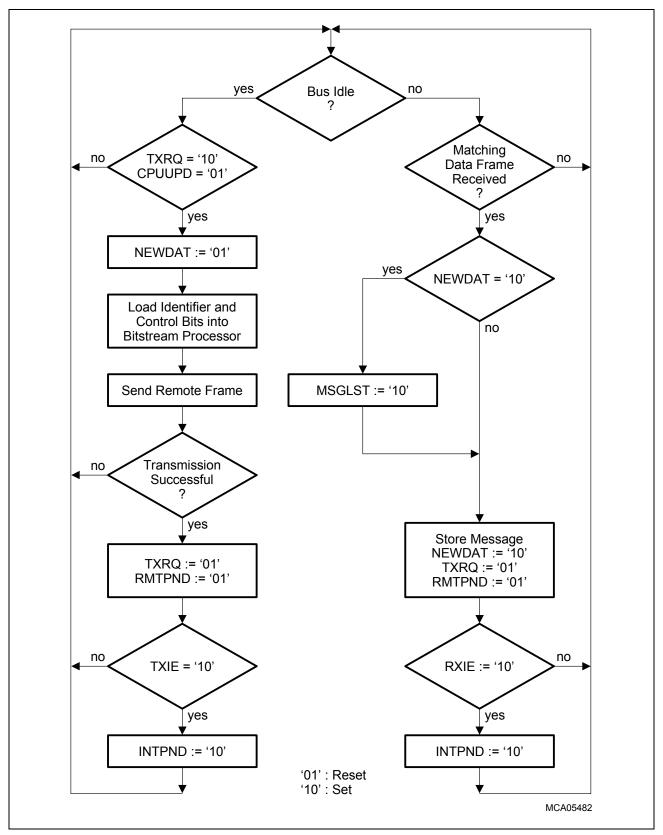

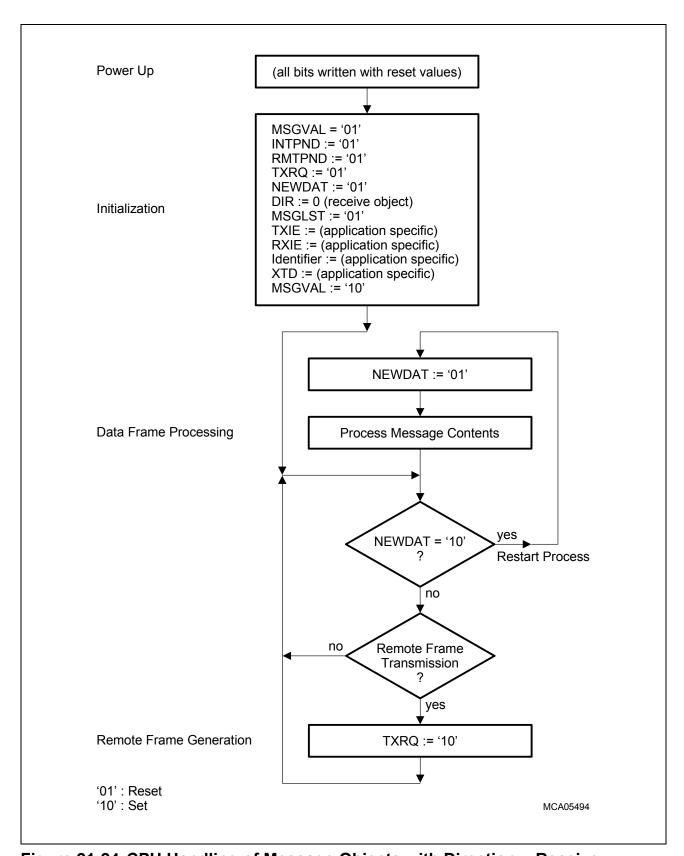

| 21.1.4.4 | Handling of Receive Message Objects       | 21-22 [2]  |

| 21.1.4.5 | Single Data Transfer Mode                 | 21-24 [2]  |

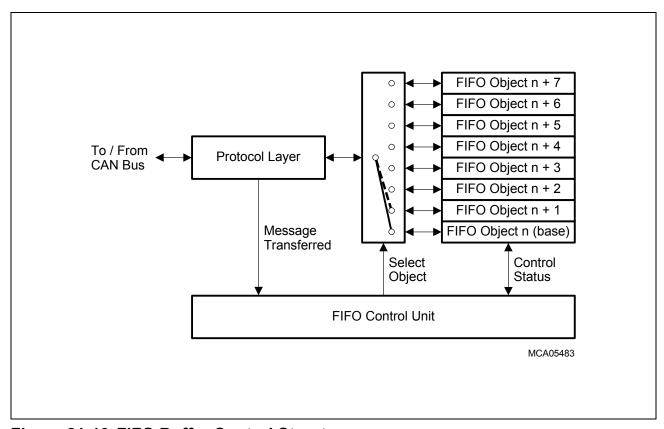

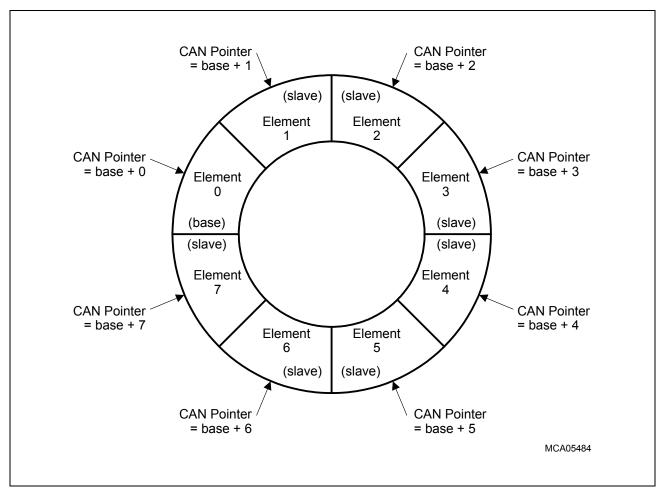

| 21.1.5   | CAN Message Object Buffer (FIFO)          | 21-25 [2]  |

| 21.1.5.1 | Buffer Access by the CAN Controller       | 21-27 [2]  |

| 21.1.5.2 | Buffer Access by the CPU                  | 21-28 [2]  |

| 21.1.6   | Gateway Message Handling                  | 21-29 [2]  |

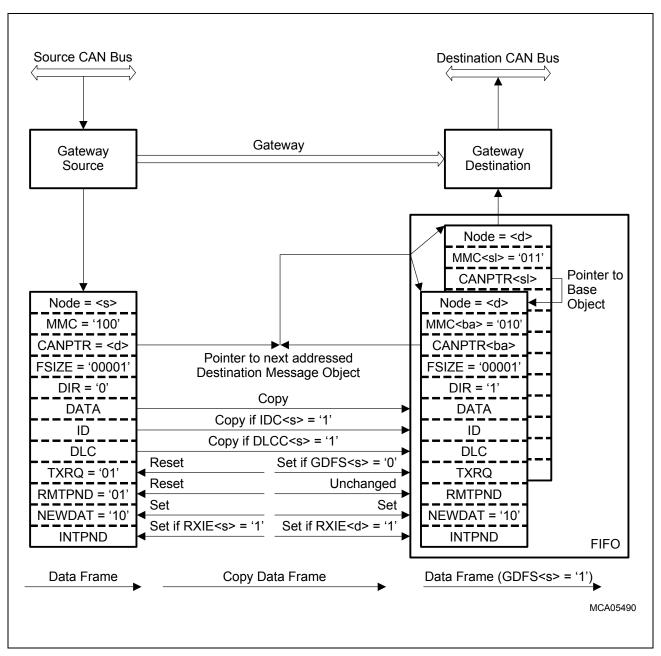

| 21.1.6.1 | Normal Gateway Mode                       | 21-30 [2]  |

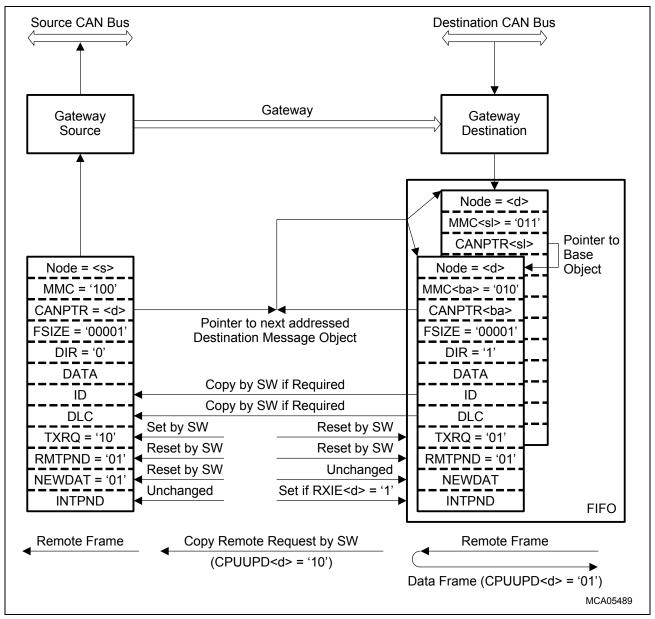

| 21.1.6.2 | Normal Gateway with FIFO Buffering        | 21-34 [2]  |

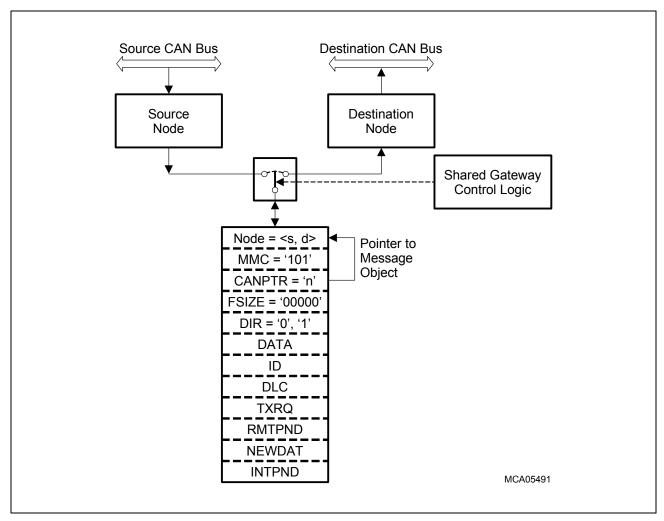

| 21.1.6.3 | Shared Gateway Mode                       | 21-37 [2]  |

| 21.1.7   | Programming the TwinCAN Module            | 21-41 [2]  |

| 21.1.7.1 | Configuration of CAN Node A/B             | 21-41 [2]  |

| 21.1.7.2 | Initialization of Message Objects         |            |

| 21.1.7.3 | Controlling a Message Transfer            |            |

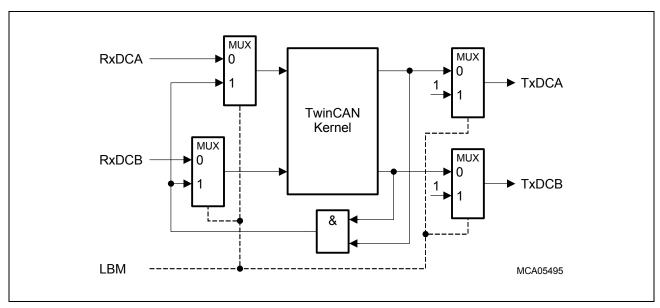

| 21.1.8   | Loop-Back Mode                            |            |

| 21.1.9   | Single Transmission Try Functionality     | 21-46 [2]  |

| 21.1.10  | Module Clock Requirements                 |            |

| 21.2     | TwinCAN Register Description              |            |

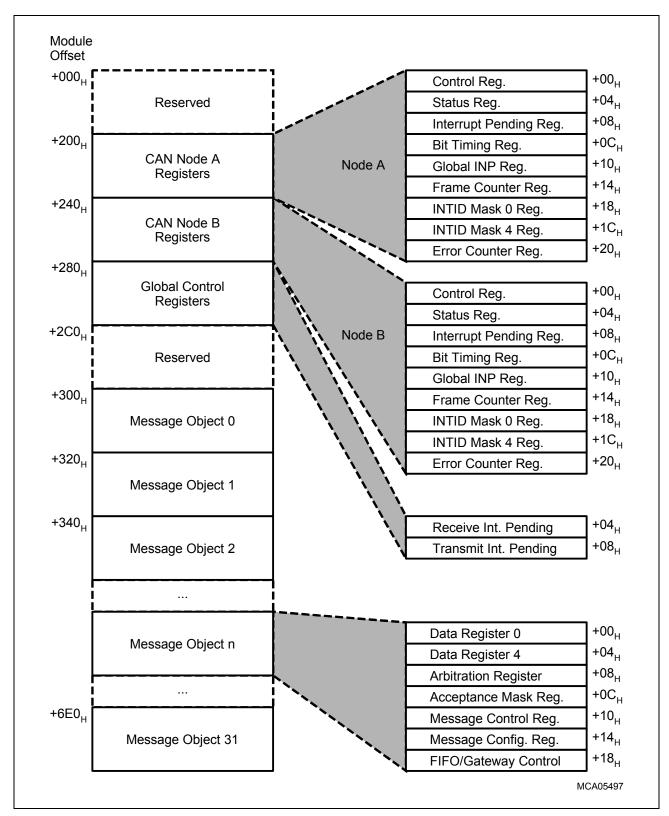

| 21.2.1   | Register Map                              |            |

| 21.2.2   | CAN Node A/B Registers                    |            |

| 21.2.3   | CAN Message Object Registers              |            |

| 21.2.4   | Global CAN Control/Status Registers       |            |

| 21.3     | XC164CM Module Implementation Details     |            |

| 21.3.1   | Interfaces of the TwinCAN Module          |            |

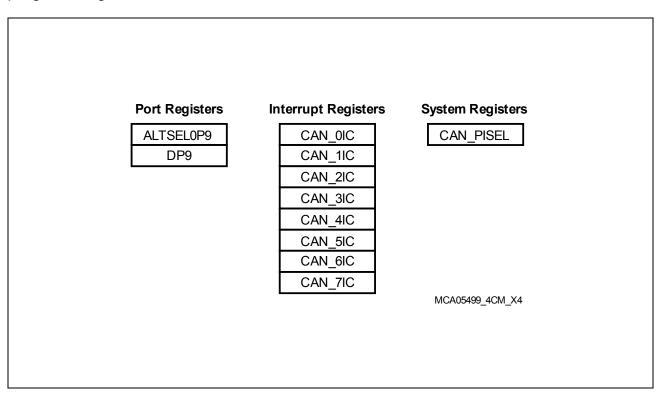

| 21.3.2   | TwinCAN Module Related External Registers |            |

| 21.3.2.1 | System Registers                          |            |

| 21.3.2.2 | Port Registers                            |            |

| 21.3.2.3 | Interrupt Registers                       |            |

| 21.3.3   | Register Table                            | 21-89 [2]  |

| 22       | Register Set                              | . 22-1 [2  |

| 22 1     | PD+RUS Perinherals                        |            |

# XC164CM Peripheral Units (Vol. 2 of 2)

|      |                   | Table of Contents |

|------|-------------------|-------------------|

| 22.2 | LXBUS Peripherals |                   |

|      | Keyword Index     | L-1 [1+2          |

# 14 The General Purpose Timer Units

The General Purpose Timer Unit blocks GPT1 and GPT2 have very flexible multifunctional timer structures which may be used for timing, event counting, pulse width measurement, pulse generation, frequency multiplication, and other purposes. They incorporate five 16-bit timers that are grouped into the two timer blocks GPT1 and GPT2. Each timer in each block may operate independently in a number of different modes such as gated timer or counter mode, or may be concatenated with another timer of the same block. Each block has alternate input/output functions and specific interrupts associated with it.

**Block GPT1** contains three timers/counters: The core timer T3 and the two auxiliary timers T2 and T4. The maximum resolution is  $f_{\rm GPT}/4$ . The auxiliary timers of GPT1 may optionally be configured as reload or capture registers for the core timer. These registers are listed in **Section 14.1.6**.

- $f_{GPT}/4$  maximum resolution

- 3 independent timers/counters

- Timers/counters can be concatenated

- 4 operating modes:

- Timer Mode

- Gated Timer Mode

- Counter Mode

- Incremental Interface Mode

- Reload and Capture functionality

- Separate interrupt lines

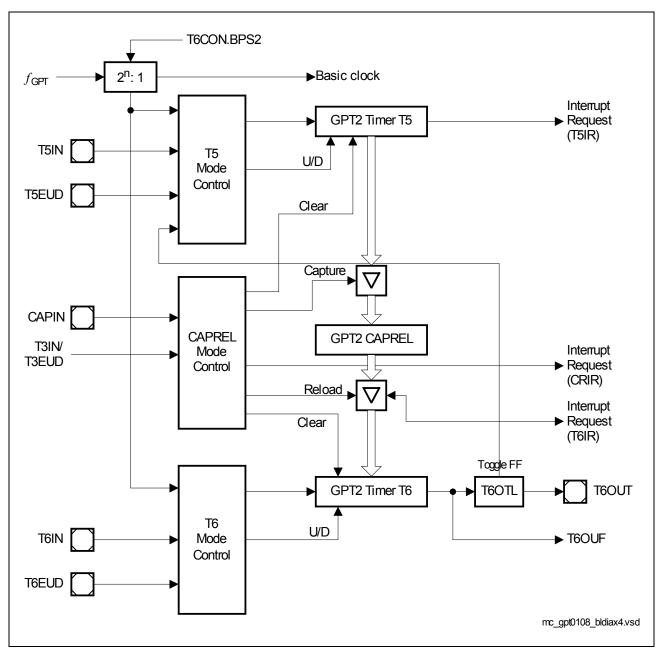

**Block GPT2** contains two timers/counters: The core timer T6 and the auxiliary timer T5. The maximum resolution is  $f_{\rm GPT}/2$ . An additional Capture/Reload register (CAPREL) supports capture and reload operation with extended functionality. These registers are listed in **Section 14.2.7**. The core timer T6 may be concatenated with timers of the CAPCOM unit (T7 and T8).

The following list summarizes the features which are supported:

- $f_{GPT}/2$  maximum resolution

- 2 independent timers/counters

- Timers/counters can be concatenated

- 3 operating modes:

- Timer Mode

- Gated Timer Mode

- Counter Mode

- Extended capture/reload functions via 16-bit capture/reload register CAPREL

- Separate interrupt lines

# 14.1 Timer Block GPT1

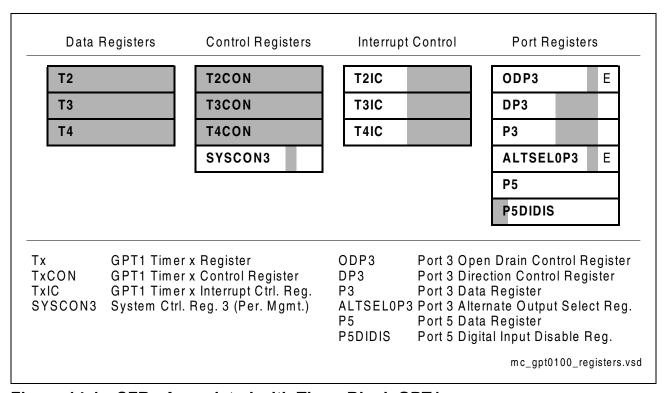

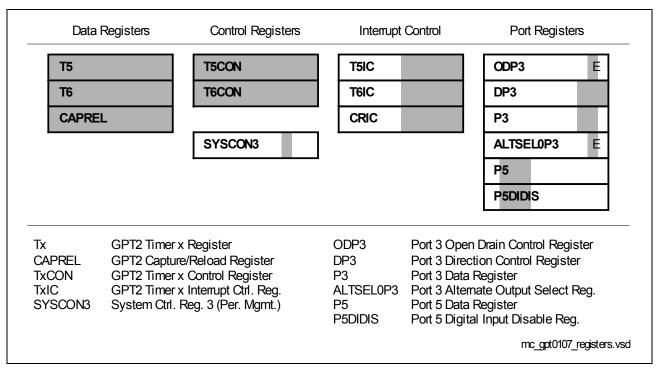

From a programmer's point of view, the GPT1 block is composed of a set of SFRs as summarized below. Those portions of port and direction registers which are used for alternate functions by the GPT1 block are shaded.

Figure 14-1 SFRs Associated with Timer Block GPT1

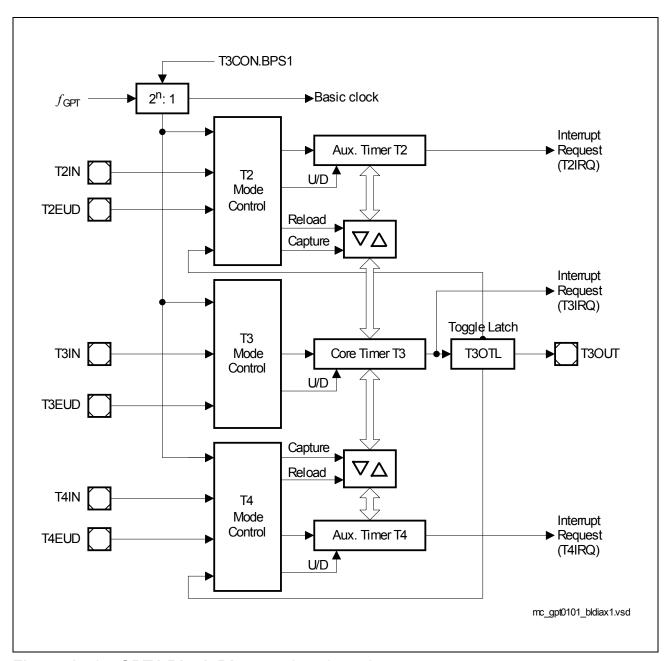

All three timers of block GPT1 (T2, T3, T4) can run in one of 4 basic modes: Timer Mode, Gated Timer Mode, Counter Mode, or Incremental Interface Mode. All timers can count up or down. Each timer of GPT1 is controlled by a separate control register TxCON.

Each timer has an input pin TxIN (alternate pin function) associated with it, which serves as the gate control in gated timer mode, or as the count input in counter mode. The count direction (up/down) may be programmed via software or may be dynamically altered by a signal at the External Up/Down control input TxEUD (alternate pin function). An overflow/underflow of core timer T3 is indicated by the Output Toggle Latch T3OTL, whose state may be output on the associated pin T3OUT (alternate pin function). The auxiliary timers T2 and T4 may additionally be concatenated with the core timer T3 (through T3OTL) or may be used as capture or reload registers for the core timer T3.

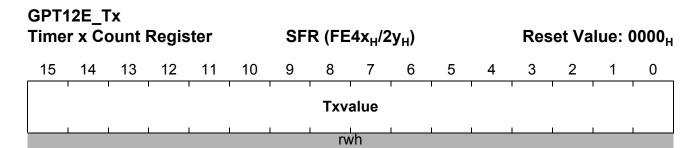

The current contents of each timer can be read or modified by the CPU by accessing the corresponding timer count registers T2, T3, or T4, located in the non-bitaddressable SFR space (see Section 14.1.6). When any of the timer registers is written to by the CPU in the state immediately preceding a timer increment, decrement, reload, or capture operation, the CPU write operation has priority in order to guarantee correct results.

The interrupts of GPT1 are controlled through the Interrupt Control Registers TxIC. These registers are not part of the GPT1 block. The input and output lines of GPT1 are connected to pins of ports P3 and P5. The control registers for the port functions are located in the respective port modules.

Note: The timing requirements for external input signals can be found in **Section 14.1.5**, **Section 14.3** summarizes the module interface signals, including pins.

Figure 14-2 GPT1 Block Diagram (n =  $2 \dots 5$ )

----

# **The General Purpose Timer Units**

## 14.1.1 GPT1 Core Timer T3 Control

The current contents of the core timer T3 are reflected by its count register T3. This register can also be written to by the CPU, for example, to set the initial start value.

The core timer T3 is configured and controlled via its bitaddressable control register T3CON.

| GPT12E_T3CON Timer 3 Control Register |                |                 |                |    |    | SF        | R (FF    | 42 <sub>H</sub> /A | 1 <sub>H</sub> ) |     |   | Res | et Va | lue: ( | 0000 <sub>H</sub> |   |

|---------------------------------------|----------------|-----------------|----------------|----|----|-----------|----------|--------------------|------------------|-----|---|-----|-------|--------|-------------------|---|

|                                       | 15             | 14              | 13             | 12 | 11 | 10        | 9        | 8                  | 7                | 6   | 5 | 4   | 3     | 2      | 1                 | 0 |

|                                       | T3<br>R<br>DIR | T3<br>CH<br>DIR | T3<br>ED<br>GE | ВР | S1 | T3<br>OTL | T3<br>OE | T3<br>UDE          | T3<br>UD         | T3R |   | T3M |       |        | T3I               |   |

|                                       | rh             | rwh             | rwh            | r۱ | N  | rwh       | rw       | rw                 | rw               | rw  |   | rw  |       |        | rw                |   |

| Field   | Bits    | Туре | Description                                                                                                                                                                                                                    |

|---------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T3RDIR  | 15      | rh   | Timer T3 Rotation Direction Flag  0 Timer T3 counts up  1 Timer T3 counts down                                                                                                                                                 |

| T3CHDIR | 14      | rwh  | Timer T3 Count Direction Change Flag This bit is set each time the count direction of timer T3 changes. T3CHDIR must be cleared by SW.  O No change of count direction was detected 1 A change of count direction was detected |

| T3EDGE  | 13      | rwh  | Timer T3 Edge Detection Flag The bit is set each time a count edge is detected. T3EDGE must be cleared by SW.  O No count edge was detected  1 A count edge was detected                                                       |

| BPS1    | [12:11] | rw   | GPT1 Block Prescaler Control Selects the basic clock for block GPT1 (see also Section 14.1.5) $00  f_{\rm GPT}/8$ $01  f_{\rm GPT}/4$ $10  f_{\rm GPT}/32$ $11  f_{\rm GPT}/16$                                                |

| T3OTL   | 10      | rwh  | Timer T3 Overflow Toggle Latch Toggles on each overflow/underflow of T3. Can be set or reset by software (see separate description)                                                                                            |

| Field | Bits  | Type | Description                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|-------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| T3OE  | 9     | rw   | Overflow/Underflow Output Enable  O Alternate Output Function Disabled  State of T3 toggle latch is output on pin T3OUT                                                                                                                                                                                                                                                       |  |  |  |  |

| T3UDE | 8     | rw   | Timer T3 External Up/Down Enable <sup>1)</sup> 0 Input T3EUD is disconnected 1 Direction influenced by input T3EUD                                                                                                                                                                                                                                                            |  |  |  |  |

| T3UD  | 7     | rw   | Timer T3 Up/Down Control <sup>1)</sup> 0 Timer T3 counts up 1 Timer T3 counts down                                                                                                                                                                                                                                                                                            |  |  |  |  |

| T3R   | 6     | rw   | Timer T3 Run Bit 0 Timer T3 stops 1 Timer T3 runs                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| ТЗМ   | [5:3] | rw   | Timer T3 Mode Control (Basic Operating Mode)  000 Timer Mode  001 Counter Mode  010 Gated Timer Mode with gate active low  011 Gated Timer Mode with gate active high  100 Reserved. Do not use this combination  101 Reserved. Do not use this combination  110 Incremental Interface Mode  (Rotation Detection Mode)  111 Incremental Interface Mode  (Edge Detection Mode) |  |  |  |  |

| T3I   | [2:0] | rw   | Timer T3 Input Parameter Selection Depends on the operating mode, see respective sections for encoding: Table 14-7 for Timer Mode and Gated Timer Mode Table 14-2 for Counter Mode Table 14-3 for Incremental Interface Mode                                                                                                                                                  |  |  |  |  |

<sup>1)</sup> See Table 14-1 for encoding of bits T3UD and T3UDE.

#### **Timer T3 Run Control**

The core timer T3 can be started or stopped by software through bit T3R (Timer T3 Run Bit). This bit is relevant in all operating modes of T3. Setting bit T3R will start the timer, clearing bit T3R stops the timer.

In gated timer mode, the timer will only run if T3R = 1 and the gate is active (high or low, as programmed).

Note: When bit T2RC or T4RC in timer control register T2CON or T4CON is set, bit T3R will also control (start and stop) the auxiliary timer(s) T2 and/or T4.

#### **Count Direction Control**

The count direction of the GPT1 timers (core timer and auxiliary timers) can be controlled either by software or by the external input pin TxEUD (Timer Tx External Up/Down Control Input). These options are selected by bits TxUD and TxUDE in the respective control register TxCON. When the up/down control is provided by software (bit TxUDE = 0), the count direction can be altered by setting or clearing bit TxUD. When bit TxUDE = 1, pin TxEUD is selected to be the controlling source of the count direction. However, bit TxUD can still be used to reverse the actual count direction, as shown in Table 14-1. The count direction can be changed regardless of whether or not the timer is running.

Note: When pin TxEUD is used as external count direction control input, it must be configured as input (its corresponding direction control bit must be cleared).

Table 14-1 GPT1 Timer Count Direction Control

| Pin TxEUD | Bit TxUDE | Bit TxUD | <b>Count Direction</b> | Bit TxRDIR |

|-----------|-----------|----------|------------------------|------------|

| X         | 0         | 0        | Count Up               | 0          |

| X         | 0         | 1        | Count Down             | 1          |

| 0         | 1         | 0        | Count Up               | 0          |

| 1         | 1         | 0        | Count Down             | 1          |

| 0         | 1         | 1        | Count Down             | 1          |

| 1         | 1         | 1        | Count Up               | 0          |

## **Timer 3 Output Toggle Latch**

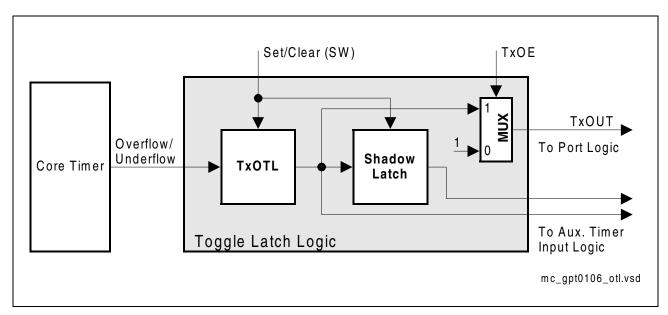

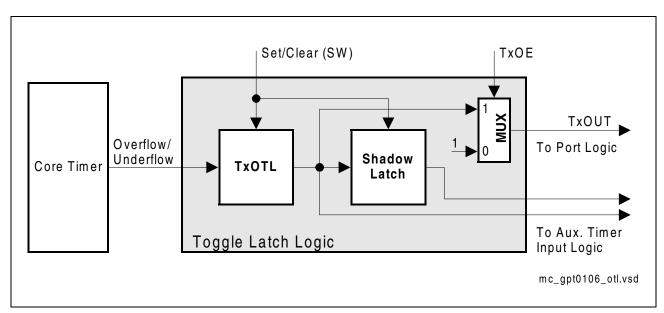

The overflow/underflow signal of timer T3 is connected to a block named 'Toggle Latch', shown in the timer mode diagrams. Figure 14-3 illustrates the details of this block. An overflow or underflow of T3 will clock two latches: The first latch represents bit T3OTL in control register T3CON. The second latch is an internal latch toggled by T3OTL's output. Both latch outputs are connected to the input control blocks of the auxiliary timers T2 and T4. The output level of the shadow latch will match the output level of T3OTL, but is delayed by one clock cycle. When the T3OTL value changes, this will result in a temporarily different output level from T3OTL and the shadow latch, which can trigger the selected count event in T2 and/or T4.

When software writes to T3OTL, both latches are set or cleared simultaneously. In this case, both signals to the auxiliary timers carry the same level and no edge will be detected. Bit T3OE (overflow/underflow output enable) in register T3CON enables the state of T3OTL to be monitored via an external pin T3OUT. When T3OTL is linked to an external port pin (must be configured as output), T3OUT can be used to control external HW. If T3OE = 1, pin T3OUT outputs the state of T3OTL. If T3OE = 0, pin T3OUT outputs a high level (as long as the T3OUT alternate function is selected for the port pin).

The trigger signals can serve as an input for the counter function or as a trigger source for the reload function of the auxiliary timers T2 and T4.

As can be seen from **Figure 14-3**, when latch T3OTL is modified by software to determine the state of the output line, also the internal shadow latch is set or cleared accordingly. Therefore, no trigger condition is detected by T2/T4 in this case.

Figure 14-3 Block Diagram of the Toggle Latch Logic of Core Timer T3

# 14.1.2 GPT1 Core Timer T3 Operating Modes

#### **Timer 3 in Timer Mode**

Timer mode for the core timer T3 is selected by setting bitfield T3M in register T3CON to  $000_{\rm B}$ . In timer mode, T3 is clocked with the module's input clock  $f_{\rm GPT}$  divided by two programmable prescalers controlled by bitfields BPS1 and T3I in register T3CON. Please see Section 14.1.5 for details on the input clock options.

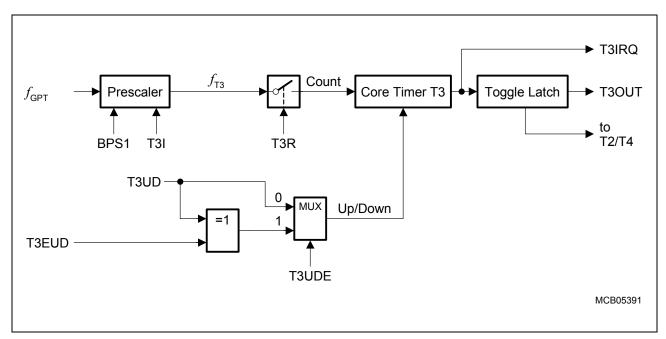

Figure 14-4 Block Diagram of Core Timer T3 in Timer Mode

#### **Gated Timer Mode**

Gated timer mode for the core timer T3 is selected by setting bitfield T3M in register T3CON to 010<sub>B</sub> or 011<sub>B</sub>. Bit T3M.0 (T3CON.3) selects the active level of the gate input. The same options for the input frequency are available in gated timer mode as in timer mode (see **Section 14.1.5**). However, the input clock to the timer in this mode is gated by the external input pin T3IN (Timer T3 External Input).

To enable this operation, the associated pin T3IN must be configured as input, that is, the corresponding direction control bit must contain 0.

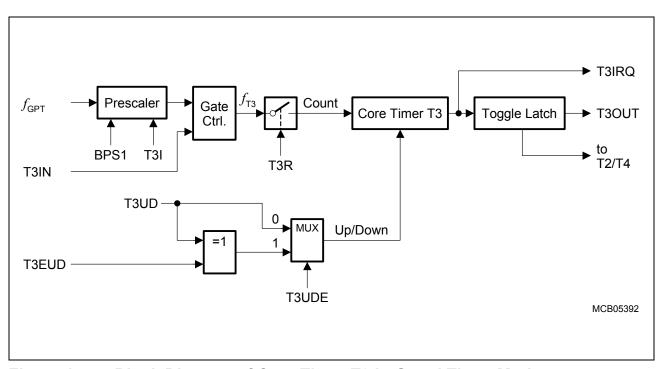

Figure 14-5 Block Diagram of Core Timer T3 in Gated Timer Mode

If  $T3M = 010_B$ , the timer is enabled when T3IN shows a low level. A high level at this line stops the timer. If  $T3M = 011_B$ , line T3IN must have a high level in order to enable the timer. Additionally, the timer can be turned on or off by software using bit T3R. The timer will only run if T3R is 1 and the gate is active. It will stop if either T3R is 0 or the gate is inactive.

Note: A transition of the gate signal at pin T3IN does not cause an interrupt request.

#### **Counter Mode**

Counter Mode for the core timer T3 is selected by setting bitfield T3M in register T3CON to 001<sub>B</sub>. In counter mode, timer T3 is clocked by a transition at the external input pin T3IN. The event causing an increment or decrement of the timer can be a positive, a negative, or both a positive and a negative transition at this line. Bitfield T3I in control register T3CON selects the triggering transition (see **Table 14-2**).

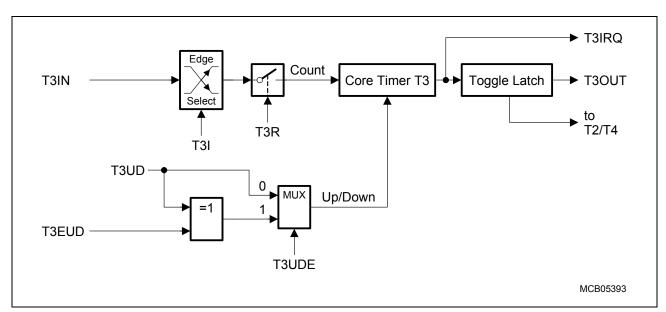

Figure 14-6 Block Diagram of Core Timer T3 in Counter Mode

Table 14-2 GPT1 Core Timer T3 (Counter Mode) Input Edge Selection

| T3I   | Triggering Edge for Counter Increment/Decrement |  |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|--|

| 000   | None. Counter T3 is disabled                    |  |  |  |  |  |  |  |

| 0 0 1 | Positive transition (rising edge) on T3IN       |  |  |  |  |  |  |  |

| 0 1 0 | Negative transition (falling edge) on T3IN      |  |  |  |  |  |  |  |

| 0 1 1 | Any transition (rising or falling edge) on T3IN |  |  |  |  |  |  |  |

| 1 X X | Reserved. Do not use this combination           |  |  |  |  |  |  |  |

For counter mode operation, pin T3IN must be configured as input (the respective direction control bit DPx.y must be 0). The maximum input frequency allowed in counter mode depends on the selected prescaler value. To ensure that a transition of the count input signal applied to T3IN is recognized correctly, its level must be held high or low for a minimum number of module clock cycles before it changes. This information can be found in **Section 14.1.5**.

#### **Incremental Interface Mode**

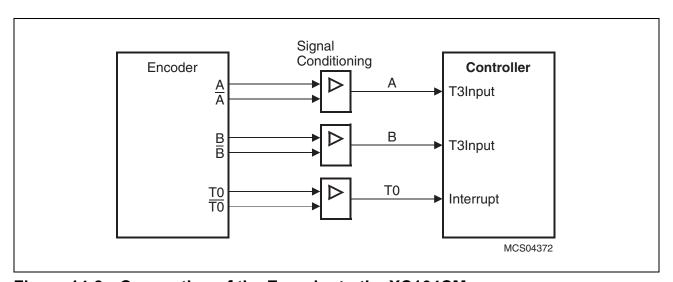

Incremental interface mode for the core timer T3 is selected by setting bitfield T3M in register T3CON to  $110_{\rm B}$  or  $111_{\rm B}$ . In incremental interface mode, the two inputs associated with core timer T3 (T3IN, T3EUD) are used to interface to an incremental encoder. T3 is clocked by each transition on one or both of the external input pins to provide 2-fold or 4-fold resolution of the encoder input.

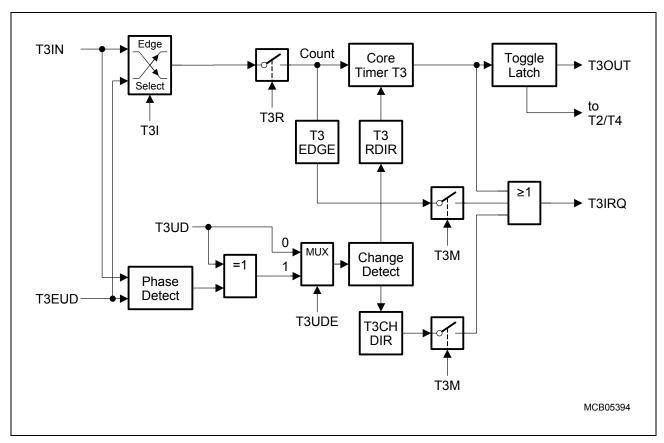

Figure 14-7 Block Diagram of Core Timer T3 in Incremental Interface Mode

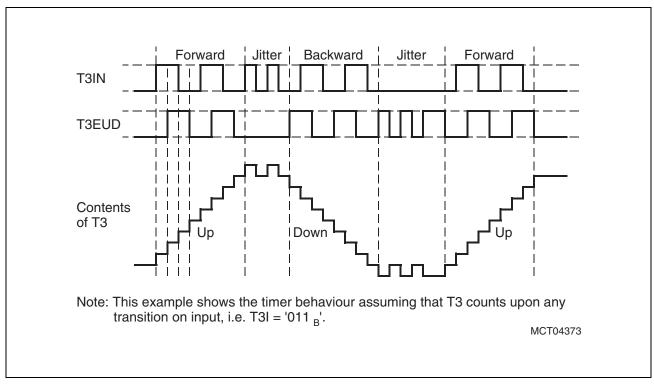

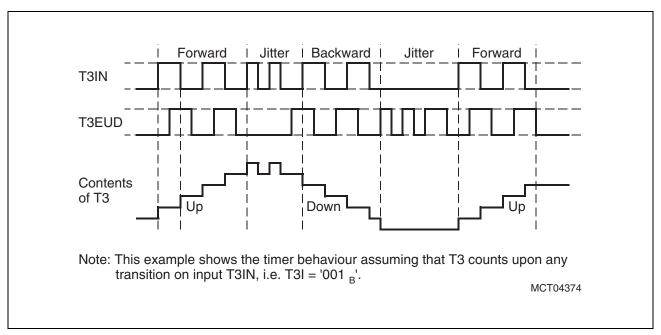

Bitfield T3I in control register T3CON selects the triggering transitions (see **Table 14-3**). The sequence of the transitions of the two input signals is evaluated and generates count pulses as well as the direction signal. So T3 is modified automatically according to the speed and the direction of the incremental encoder and, therefore, its contents always represent the encoder's current position.

The interrupt request (T3IRQ) generation mode can be selected: In Rotation Detection Mode (T3M =  $110_B$ ), an interrupt request is generated each time the count direction of T3 changes. In Edge Detection Mode (T3M =  $111_B$ ), an interrupt request is generated each time a count edge for T3 is detected. Count direction, changes in the count direction, and count requests are monitored by status bits T3RDIR, T3CHDIR, and T3EDGE in register T3CON.

Table 14-3 Core Timer T3 (Incremental Interface Mode) Input Edge Selection

| T3I   | Triggering Edge for Counter Increment/Decrement                          |

|-------|--------------------------------------------------------------------------|

| 0 0 0 | None. Counter T3 stops.                                                  |

| 0 0 1 | Any transition (rising or falling edge) on T3IN.                         |

| 0 1 0 | Any transition (rising or falling edge) on T3EUD.                        |

| 0 1 1 | Any transition (rising or falling edge) on any T3 input (T3IN or T3EUD). |

| 1 X X | Reserved. Do not use this combination.                                   |

The incremental encoder can be connected directly to the XC164CM without external interface logic. In a standard system, however, comparators will be employed to convert the encoder's differential outputs (such as A,  $\overline{A}$ ) to digital signals (such as A). This greatly increases noise immunity.

Note: The third encoder output T0, which indicates the mechanical zero position, may be connected to an external interrupt input and trigger a reset of timer T3 (for example via PEC transfer from ZEROS).

Figure 14-8 Connection of the Encoder to the XC164CM

For incremental interface operation, the following conditions must be met:

- Bitfield T3M must be 110<sub>B</sub> or 111<sub>B</sub>.

- Both pins T3IN and T3EUD must be configured as input, i.e. the respective direction control bits must be 0.

- Bit T3UDE must be 1 to enable automatic external direction control.

The maximum count frequency allowed in incremental interface mode depends on the selected prescaler value. To ensure that a transition of any input signal is recognized correctly, its level must be held high or low for a minimum number of module clock cycles before it changes. This information can be found in **Section 14.1.5**.

As in incremental interface mode two input signals with a 90° phase shift are evaluated, their maximum input frequency can be half the maximum count frequency.

In incremental interface mode, the count direction is automatically derived from the sequence in which the input signals change, which corresponds to the rotation direction of the connected sensor. **Table 14-4** summarizes the possible combinations.

Table 14-4 GPT1 Core Timer T3 (Incremental Interface Mode) Count Direction

| Level on Respective | T3IN      | Input                   | T3EUD Input     |                         |  |  |

|---------------------|-----------|-------------------------|-----------------|-------------------------|--|--|

| other Input         | Rising _r | Falling <b>\(\cdot\</b> | Rising <i>√</i> | Falling \(\frac{1}{2}\) |  |  |

| High                | Down      | Up                      | Up              | Down                    |  |  |

| Low                 | Up        | Down                    | Down            | Up                      |  |  |

**Figure 14-9** and **Figure 14-10** give examples of T3's operation, visualizing count signal generation and direction control. They also show how input jitter is compensated, which might occur if the sensor rests near to one of its switching points.

Figure 14-9 Evaluation of Incremental Encoder Signals, 2 Count Inputs

Figure 14-10 Evaluation of Incremental Encoder Signals, 1 Count Input

Note: Timer T3 operating in incremental interface mode automatically provides information on the sensor's current position. Dynamic information (speed, acceleration, deceleration) may be obtained by measuring the incoming signal periods. This is facilitated by an additional special capture mode for timer T5 (see Section 14.2.5).

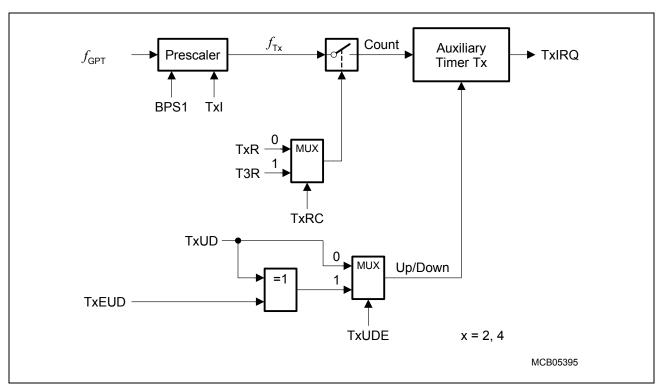

#### 14.1.3 **GPT1 Auxiliary Timers T2/T4 Control**

Auxiliary timers T2 and T4 have exactly the same functionality. They can be configured for timer mode, gated timer mode, counter mode, or incremental interface mode with the same options for the timer frequencies and the count signal as the core timer T3. In addition to these 4 counting modes, the auxiliary timers can be concatenated with the core timer, or they may be used as reload or capture registers in conjunction with the core timer. The start/stop function of the auxiliary timers can be remotely controlled by the T3 run control bit. Several timers may thus be controlled synchronously.

The current contents of an auxiliary timer are reflected by its count register T2 or T4, respectively. These registers can also be written to by the CPU, for example, to set the initial start value.

The individual configurations for timers T2 and T4 are determined by their bitaddressable control registers T2CON and T4CON, which are organized identically. Note that functions which are present in all 3 timers of block GPT1 are controlled in the same bit positions and in the same manner in each of the specific control registers.

Note: The auxiliary timers have no output toggle latch and no alternate output function.

|                | 12E_1<br>r 2 C  |                | N<br>I Reg      | ister |    | SF       | R (FF     | 40 <sub>H</sub> /A | ( <sub>H</sub> ) |   |     | Res | et Va | ılue: ( | 0000 <sub>H</sub> |

|----------------|-----------------|----------------|-----------------|-------|----|----------|-----------|--------------------|------------------|---|-----|-----|-------|---------|-------------------|

| 15             | 14              | 13             | 12              | 11    | 10 | 9        | 8         | 7                  | 6                | 5 | 4   | 3   | 2     | 1       | 0                 |

| T2<br>R<br>DIR | T2<br>CH<br>DIR | T2<br>ED<br>GE | T2<br>IR<br>DIS | -     | -  | T2<br>RC | T2<br>UDE | T2<br>UD           | T2R              |   | T2M | ı   |       | T2I     |                   |

| rh             | rwh             | rwh            | rw              | _     | -  | rw       | rw        | rw                 | rw               |   | rw  | •   | •     | rw      |                   |

| GPT'           | 12E_1<br>r 4 Co |                |                 | ister | SFR (FF44 <sub>H</sub> /A2 <sub>H</sub> ) Reset Value: 0000 <sub>H</sub> |          |           |          |     |   | )000 <sub>H</sub> |   |   |     |   |

|----------------|-----------------|----------------|-----------------|-------|--------------------------------------------------------------------------|----------|-----------|----------|-----|---|-------------------|---|---|-----|---|

| 15             | 14              | 13             | 12              | 11    | 10                                                                       | 9        | 8         | 7        | 6   | 5 | 4                 | 3 | 2 | 1   | 0 |

| T4<br>R<br>DIR | T4<br>CH<br>DIR | T4<br>ED<br>GE | T4<br>IR<br>DIS | -     | -                                                                        | T4<br>RC | T4<br>UDE | T4<br>UD | T4R |   | T4M               |   |   | T4I |   |

| rh             | rwh             | rwh            | rw              | -     | -                                                                        | rw       | rw        | rw       | rw  |   | rw                |   |   | rw  |   |

| Field  | Bits | Туре | Description                                                             |  |  |  |  |

|--------|------|------|-------------------------------------------------------------------------|--|--|--|--|

| TxRDIR | 15   | rh   | Timer Tx Rotation Direction  O Timer x counts up  1 Timer x counts down |  |  |  |  |

| Field   | Bits | Type | Description                                                                                                                                                                                                                             |

|---------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxCHDIR | 14   | rwh  | Timer Tx Count Direction Change This bit is set each time the count direction of timer Tx changes. TxCHDIR must be cleared by SW.  O No change in count direction was detected  A change in count direction was detected                |

| TxEDGE  | 13   | rwh  | Timer Tx Edge Detection The bit is set each time a count edge is detected. TxEDGE must be cleared by SW.  O No count edge was detected  1 A count edge was detected                                                                     |

| TxIRDIS | 12   | rw   | Timer Tx Interrupt Request Disable  O Interrupt generation for TxCHDIR and TxEDGE interrupts in Incremental Interface Mode is enabled  Interrupt generation for TxCHDIR and TxEDGE interrupts in Incremental Interface Mode is disabled |

| TxRC    | 9    | rw   | Timer Tx Remote Control  Timer Tx is controlled by its own run bit TxR  Timer Tx is controlled by the run bit T3R of core timer 3, not by bit TxR                                                                                       |

| TxUDE   | 8    | rw   | Timer Tx External Up/Down Enable <sup>1)</sup> 0 Input TxEUD is disconnected 1 Direction influenced by input TxEUD                                                                                                                      |

| TxUD    | 7    | rw   | Timer Tx Up/Down Control <sup>1)</sup> 0 Timer Tx counts up 1 Timer Tx counts down                                                                                                                                                      |

| TxR     | 6    | rw   | Timer Tx Run Bit  0 Timer Tx stops  1 Timer Tx runs  Note: This bit only controls timer Tx if bit TxRC = 0.                                                                                                                             |

| Field | Bits  | Туре | Description                                                                                                                                                                                                                                                                                          |  |  |  |

|-------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TxM   | [5:3] | rw   | Timer Tx Mode Control (Basic Operating Mode) 000 Timer Mode 001 Counter Mode 010 Gated Timer Mode with gate active low 011 Gated Timer Mode with gate active high 100 Reload Mode 101 Capture Mode 110 Incremental Interface Mode (Rotation Detect.) 111 Incremental Interface Mode (Edge Detection) |  |  |  |

| Txl   | [2:0] | rw   | Timer Tx Input Parameter Selection Depends on the operating mode, see respective sections for encoding: Table 14-7 for Timer Mode and Gated Timer Mode Table 14-2 for Counter Mode Table 14-3 for Incremental Interface Mode                                                                         |  |  |  |

<sup>1)</sup> See Table 14-1 for encoding of bits TxUD and TxUDE.

#### **Timer T2/T4 Run Control**

Each of the auxiliary timers T2 and T4 can be started or stopped by software in two different ways:

- Through the associated timer run bit (T2R or T4R). In this case it is required that the respective control bit TxRC = 0.

- Through the core timer's run bit (T3R). In this case the respective remote control bit must be set (TxRC = 1).

The selected run bit is relevant in all operating modes of T2/T4. Setting the bit will start the timer, clearing the bit stops the timer.

In gated timer mode, the timer will only run if the selected run bit is set and the gate is active (high or low, as programmed).

Note: If remote control is selected T3R will start/stop timer T3 and the selected auxiliary timer(s) synchronously.

#### **Count Direction Control**

The count direction of the GPT1 timers (core timer and auxiliary timers) is controlled in the same way, either by software or by the external input pin TxEUD. Please refer to the description in **Table 14-1**.

Note: When pin TxEUD is used as external count direction control input, it must be configured as input (its corresponding direction control bit must be cleared).

# 14.1.4 GPT1 Auxiliary Timers T2/T4 Operating Modes

The operation of the auxiliary timers in the basic operating modes is almost identical with the core timer's operation, with very few exceptions. Additionally, some combined operating modes can be selected.

#### Timers T2 and T4 in Timer Mode

Timer mode for an auxiliary timer Tx is selected by setting its bitfield TxM in register TxCON to  $000_B$ .

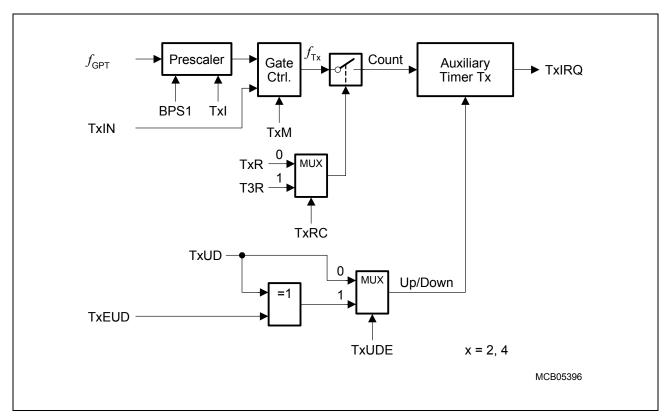

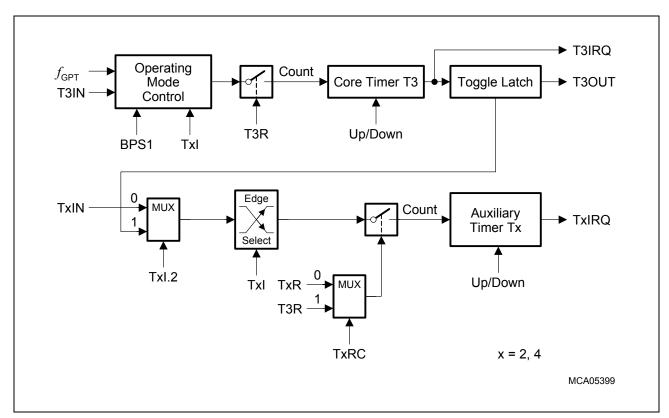

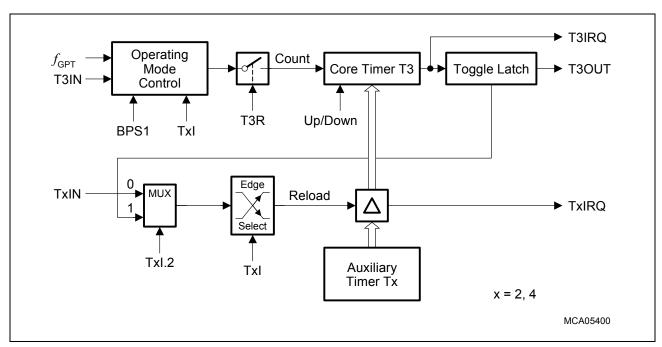

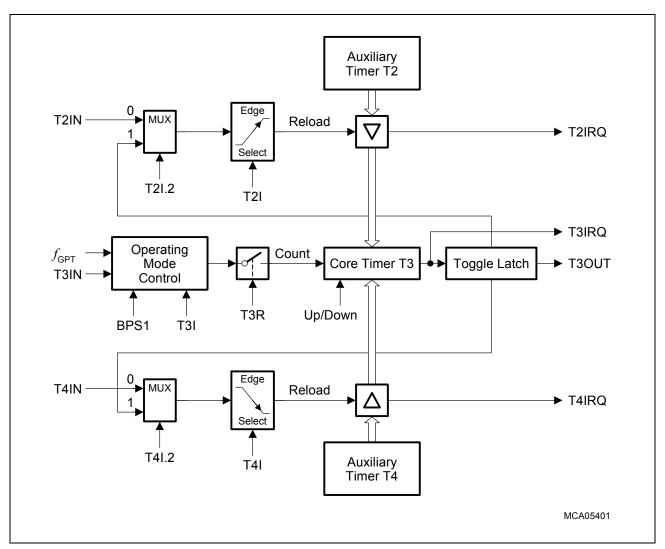

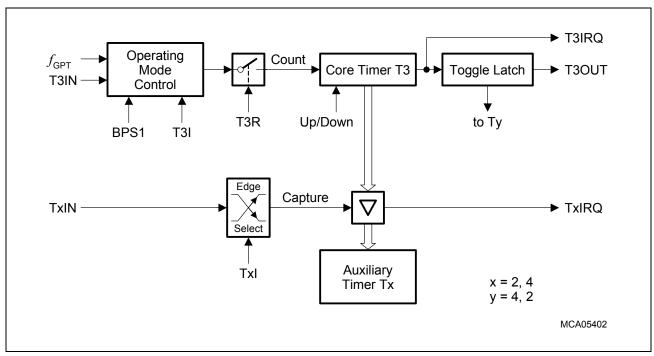

Figure 14-11 Block Diagram of an Auxiliary Timer in Timer Mode

#### **Timers T2 and T4 in Gated Timer Mode**

Gated timer mode for an auxiliary timer Tx is selected by setting bitfield TxM in register TxCON to  $010_B$  or  $011_B$ . Bit TxM.0 (TxCON.3) selects the active level of the gate input.

Note: A transition of the gate signal at line TxIN does not cause an interrupt request.

Figure 14-12 Block Diagram of an Auxiliary Timer in Gated Timer Mode

Note: There is no output toggle latch for T2 and T4.

Start/stop of an auxiliary timer can be controlled locally or remotely.

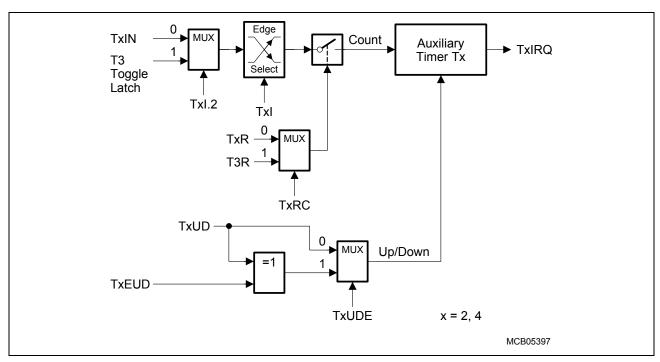

#### **Timers T2 and T4 in Counter Mode**

Counter mode for an auxiliary timer Tx is selected by setting bitfield TxM in register TxCON to 001<sub>B</sub>. In counter mode, an auxiliary timer can be clocked either by a transition at its external input line TxIN, or by a transition of timer T3's toggle latch T3OTL. The event causing an increment or decrement of a timer can be a positive, a negative, or both a positive and a negative transition at either the respective input pin or at the toggle latch. Bitfield TxI in control register TxCON selects the triggering transition (see **Table 14-5**).

Figure 14-13 Block Diagram of an Auxiliary Timer in Counter Mode

Table 14-5 GPT1 Auxiliary Timer (Counter Mode) Input Edge Selection

| T2I/T4I | Triggering Edge for Counter Increment/Decrement                  |

|---------|------------------------------------------------------------------|

| X 0 0   | None. Counter Tx is disabled                                     |

| 0 0 1   | Positive transition (rising edge) on TxIN                        |

| 0 1 0   | Negative transition (falling edge) on TxIN                       |

| 0 1 1   | Any transition (rising or falling edge) on TxIN                  |

| 101     | Positive transition (rising edge) of T3 toggle latch T3OTL       |

| 110     | Negative transition (falling edge) of T3 toggle latch T3OTL      |

| 111     | Any transition (rising or falling edge) of T3 toggle latch T3OTL |

Note: Only state transitions of T3OTL which are caused by the overflows/underflows of T3 will trigger the counter function of T2/T4. Modifications of T3OTL via software will NOT trigger the counter function of T2/T4.

For counter operation, pin TxIN must be configured as input (the respective direction control bit DPx.y must be 0). The maximum input frequency allowed in counter mode depends on the selected prescaler value. To ensure that a transition of the count input signal applied to TxIN is recognized correctly, its level must be held high or low for a minimum number of module clock cycles before it changes. This information can be found in Section 14.1.5.

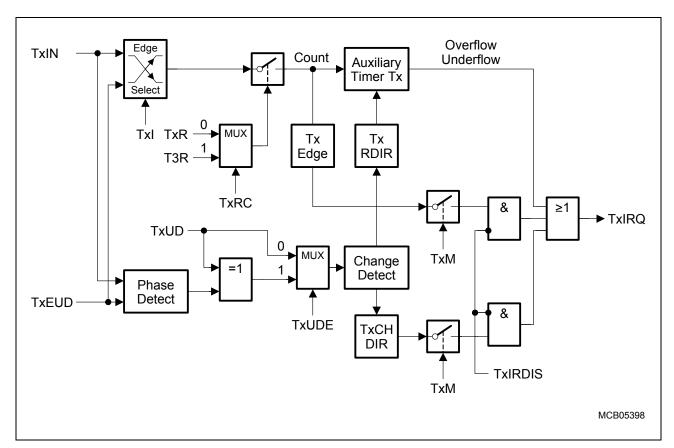

#### Timers T2 and T4 in Incremental Interface Mode

Incremental interface mode for an auxiliary timer Tx is selected by setting bitfield TxM in the respective register TxCON to  $110_B$  or  $111_B$ . In incremental interface mode, the two inputs associated with an auxiliary timer Tx (TxIN, TxEUD) are used to interface to an incremental encoder. Tx is clocked by each transition on one or both of the external input pins to provide 2-fold or 4-fold resolution of the encoder input.

Figure 14-14 Block Diagram of an Auxiliary Timer in Incremental Interface Mode

The operation of the auxiliary timers T2 and T4 in incremental interface mode and the interrupt generation are the same as described for the core timer T3. The descriptions, figures and tables apply accordingly.

#### **Timer Concatenation**

Using the toggle bit T3OTL as a clock source for an auxiliary timer in counter mode concatenates the core timer T3 with the respective auxiliary timer. This concatenation forms either a 32-bit or a 33-bit timer/counter, depending on which transition of T3OTL is selected to clock the auxiliary timer.

- **32-bit Timer/Counter:** If both a positive and a negative transition of T3OTL are used to clock the auxiliary timer, this timer is clocked on every overflow/underflow of the core timer T3. Thus, the two timers form a 32-bit timer.

- **33-bit Timer/Counter:** If either a positive or a negative transition of T3OTL is selected to clock the auxiliary timer, this timer is clocked on every second overflow/underflow of the core timer T3. This configuration forms a 33-bit timer (16-bit core timer + T3OTL + 16-bit auxiliary timer).

- As long as bit T3OTL is not modified by software, it represents the state of the internal toggle latch, and can be regarded as part of the 33-bit timer.

The count directions of the two concatenated timers are not required to be the same. This offers a wide variety of different configurations.

T3, which represents the low-order part of the concatenated timer, can operate in timer mode, gated timer mode or counter mode in this case.

Figure 14-15 Concatenation of Core Timer T3 and an Auxiliary Timer

## **Auxiliary Timer in Reload Mode**

Reload Mode for an auxiliary timer Tx is selected by setting bitfield TxM in the respective register TxCON to 100<sub>B</sub>. In reload mode, the core timer T3 is reloaded with the contents of an auxiliary timer register, triggered by one of two different signals. The trigger signal is selected the same way as the clock source for counter mode (see **Table 14-5**), i.e. a transition of the auxiliary timer's input TxIN or the toggle latch T3OTL may trigger the reload.

Note: When programmed for reload mode, the respective auxiliary timer (T2 or T4) stops independently of its run flag T2R or T4R.

The timer input pin TxIN must be configured as input if it shall trigger a reload operation.

Figure 14-16 GPT1 Auxiliary Timer in Reload Mode

Upon a trigger signal, T3 is loaded with the contents of the respective timer register (T2 or T4) and the respective interrupt request flag (T2IR or T4IR) is set.

Note: When a T3OTL transition is selected for the trigger signal, the interrupt request flag T3IR will also be set upon a trigger, indicating T3's overflow or underflow. Modifications of T3OTL via software will NOT trigger the counter function of T2/T4.

To ensure that a transition of the reload input signal applied to TxIN is recognized correctly, its level must be held high or low for a minimum number of module clock cycles, detailed in **Section 14.1.5**.

The reload mode triggered by the T3 toggle latch can be used in a number of different configurations. The following functions can be performed, depending on the selected active transition:

- If both a positive and a negative transition of T3OTL are selected to trigger a reload, the core timer will be reloaded with the contents of the auxiliary timer each time it overflows or underflows. This is the standard reload mode (reload on overflow/underflow).

- If either a positive or a negative transition of T3OTL is selected to trigger a reload, the core timer will be reloaded with the contents of the auxiliary timer on every second overflow or underflow.

- Using this "single-transition" mode for both auxiliary timers allows to perform very flexible Pulse Width Modulation (PWM). One of the auxiliary timers is programmed to reload the core timer on a positive transition of T3OTL, the other is programmed for a reload on a negative transition of T3OTL. With this combination the core timer is alternately reloaded from the two auxiliary timers.

**Figure 14-17** shows an example for the generation of a PWM signal using the "single-transition" reload mechanism. T2 defines the high time of the PWM signal (reloaded on positive transitions) and T4 defines the low time of the PWM signal (reloaded on negative transitions). The PWM signal can be output on pin T3OUT if T3OE = 1. With this method, the high and low time of the PWM signal can be varied in a wide range.

Note: The output toggle latch T3OTL is accessible via software and may be changed, if required, to modify the PWM signal.

However, this will NOT trigger the reloading of T3.

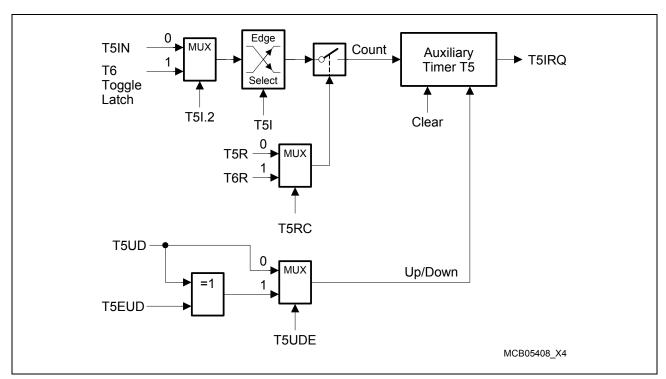

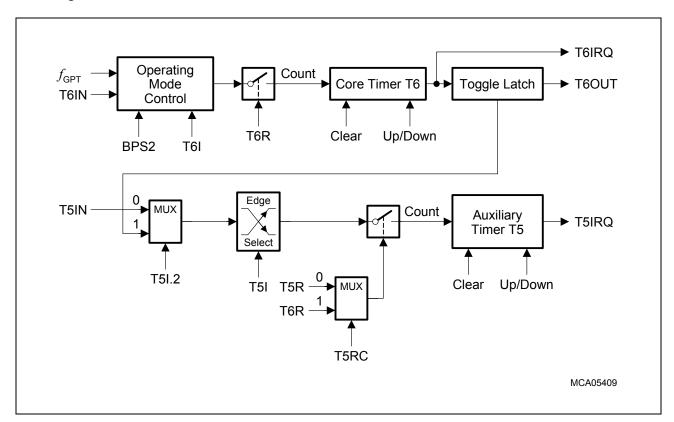

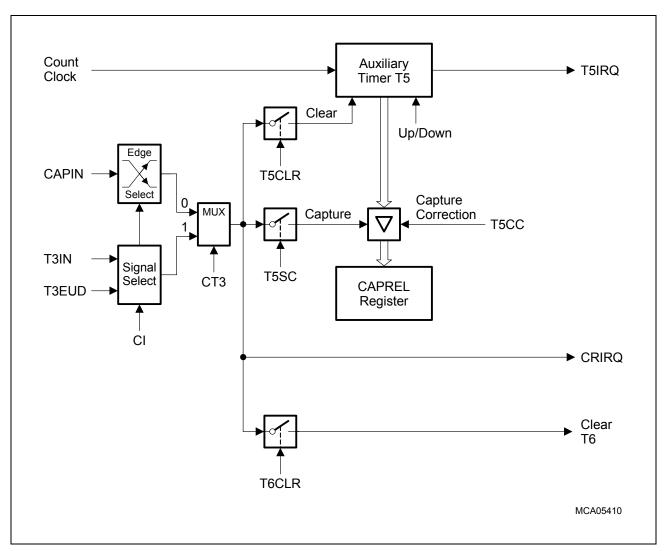

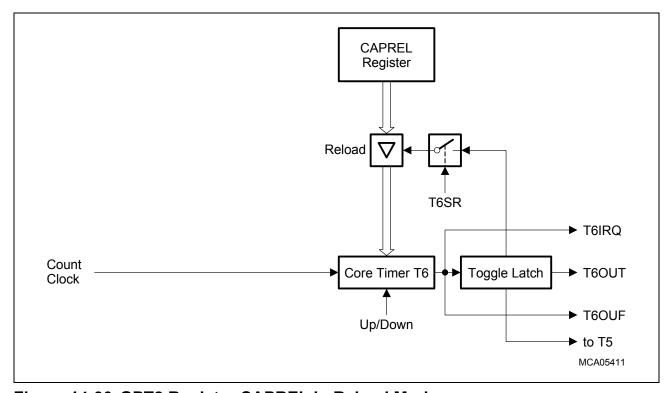

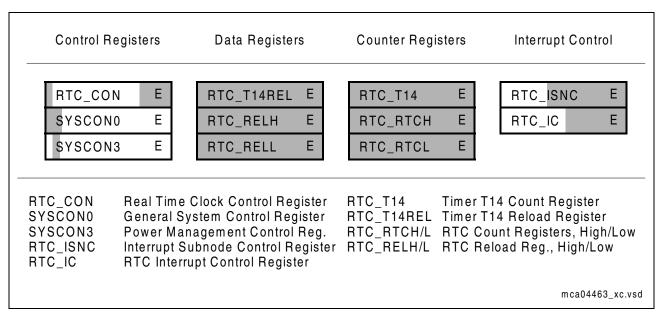

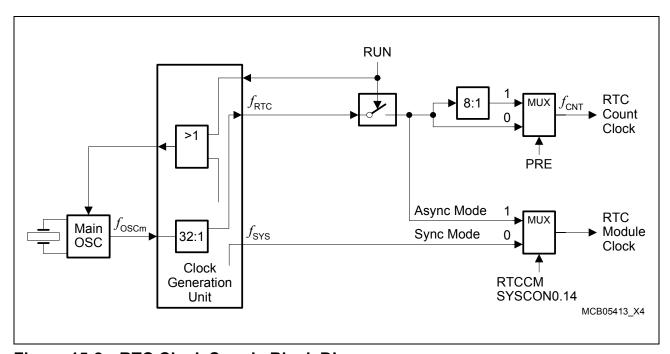

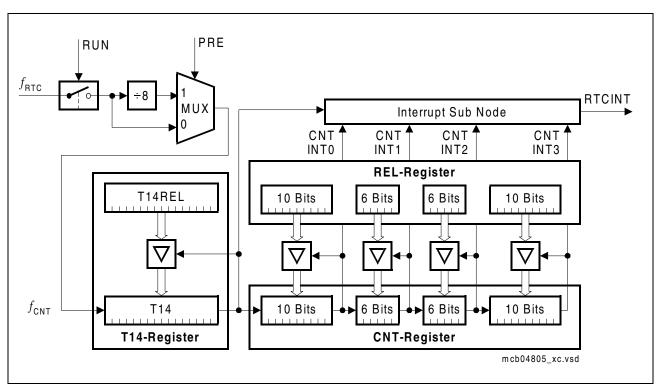

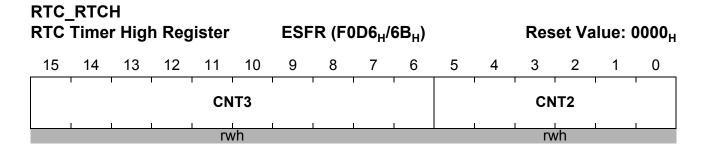

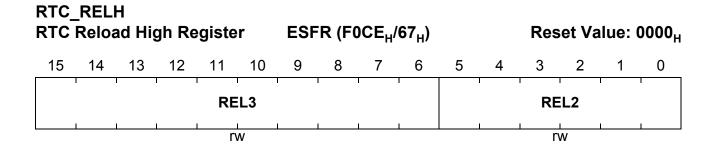

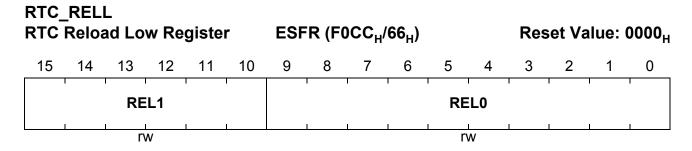

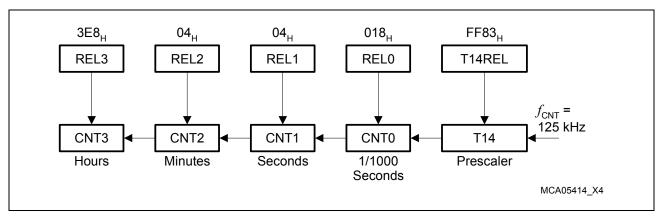

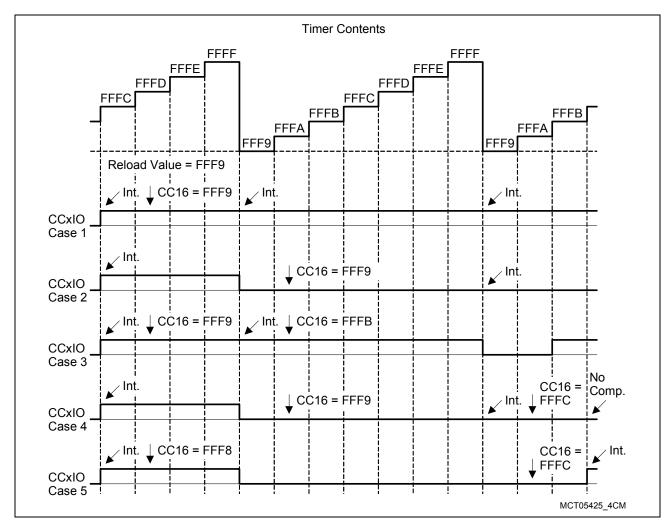

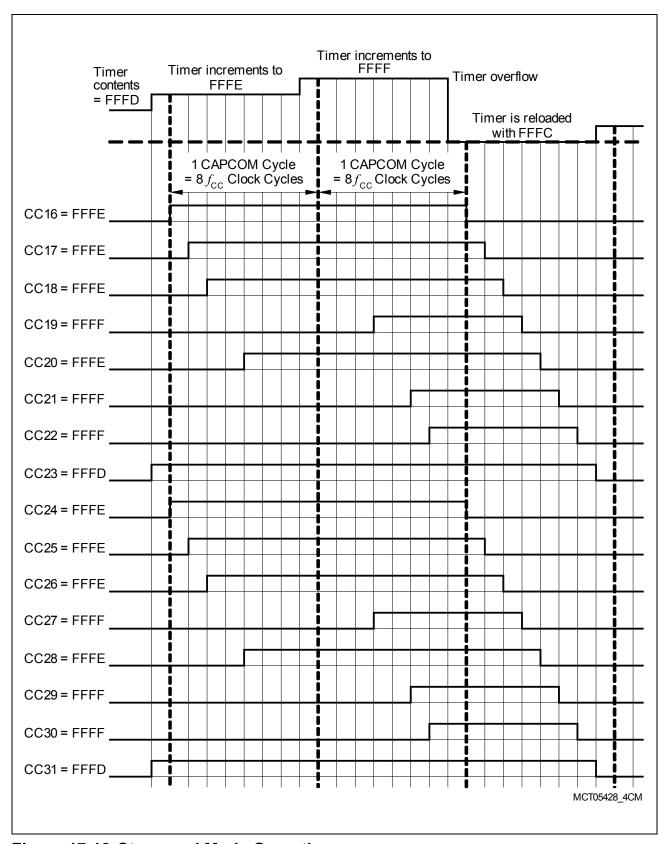

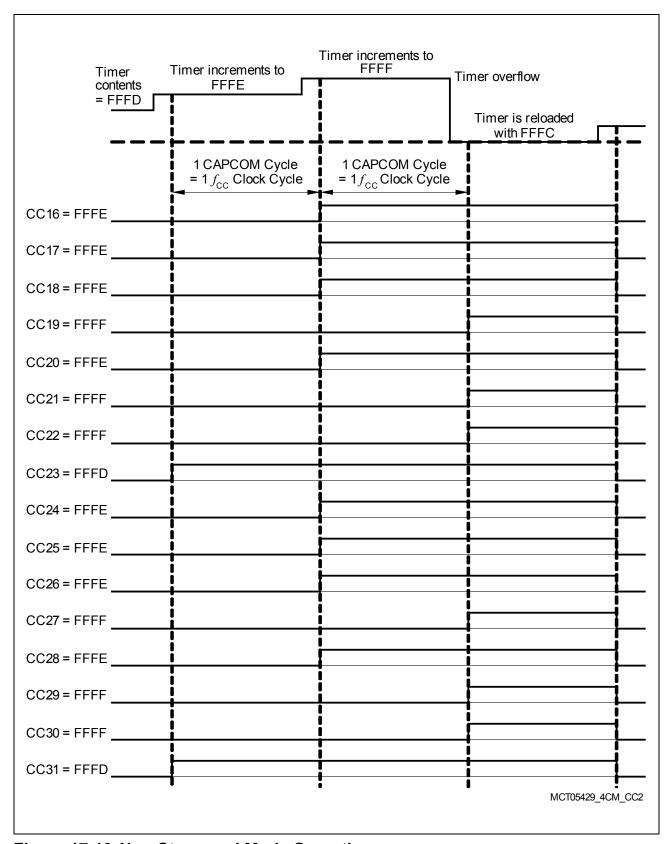

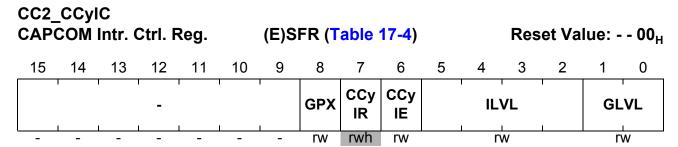

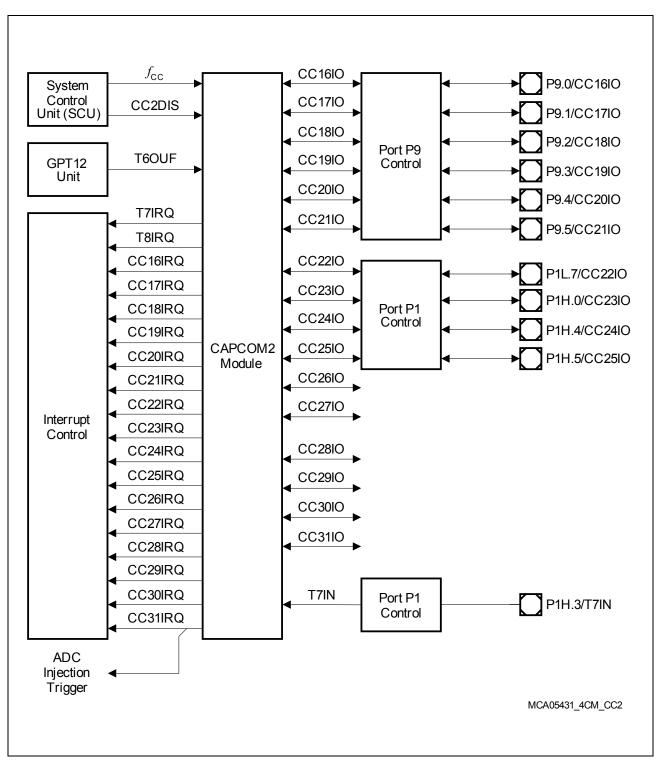

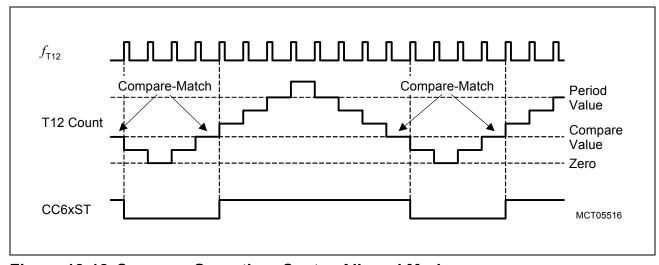

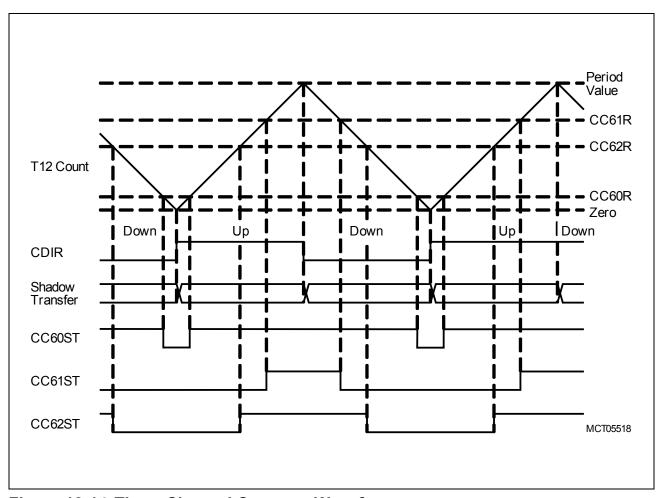

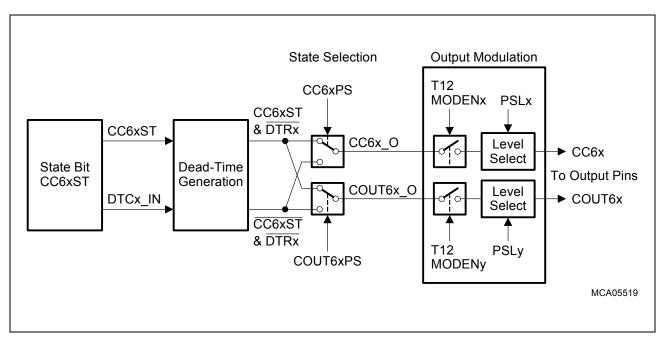

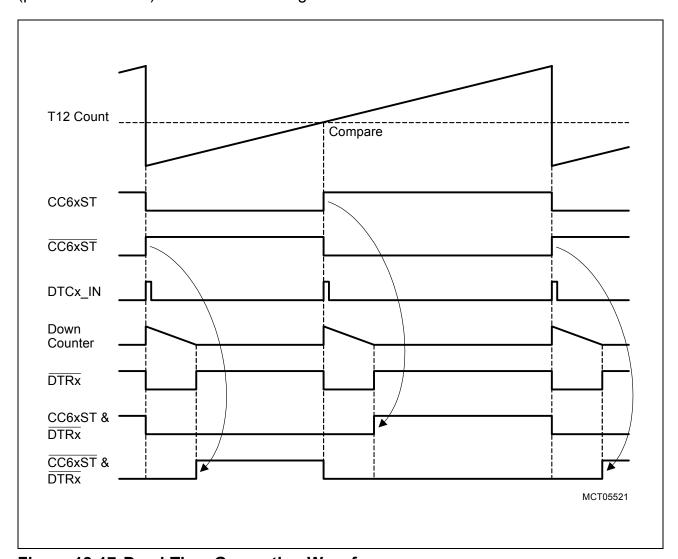

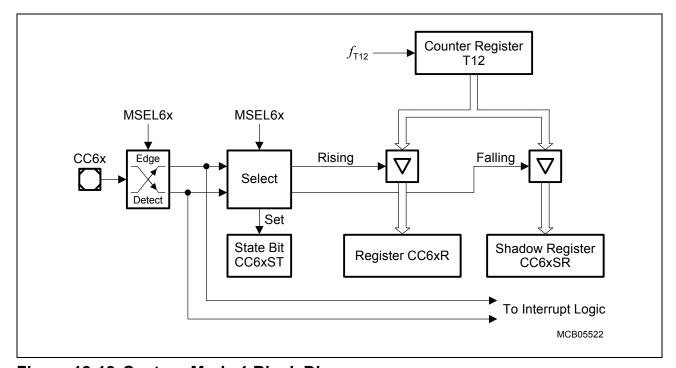

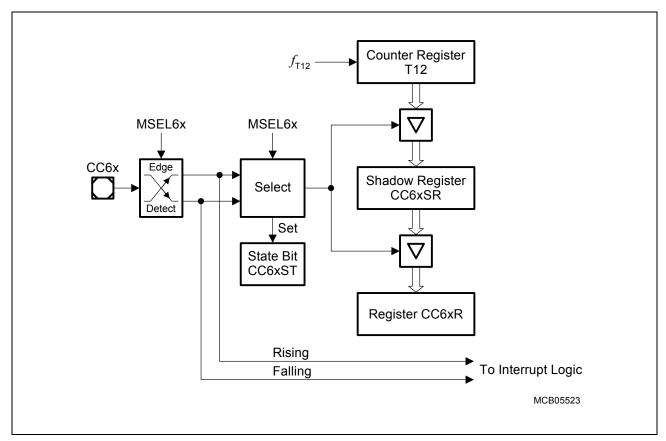

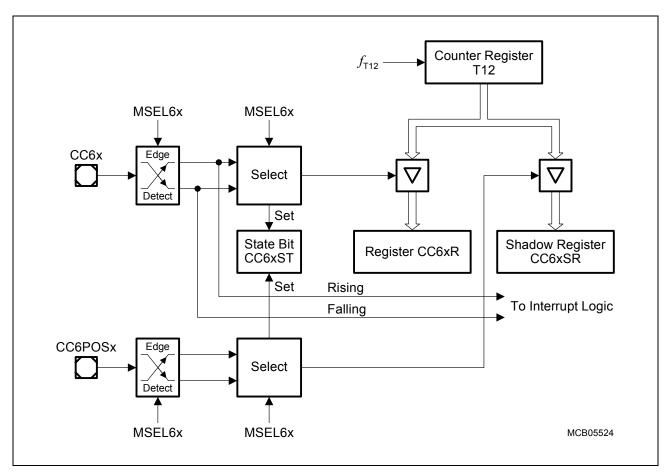

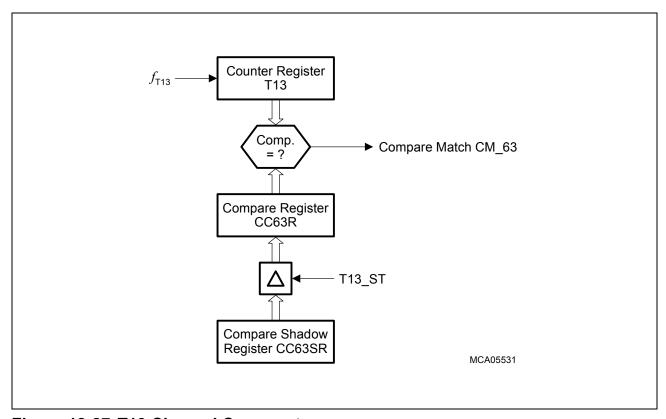

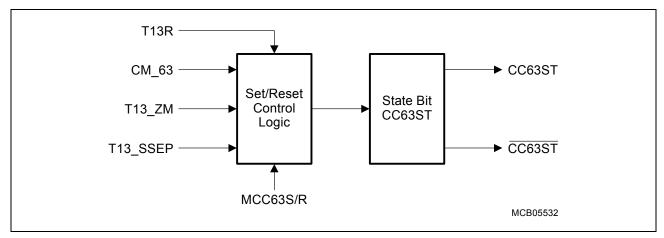

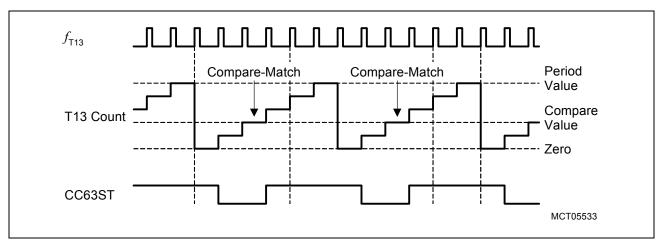

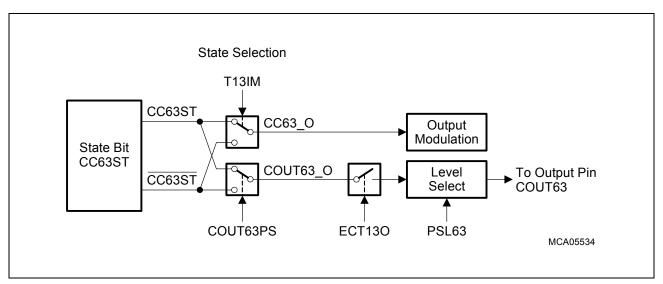

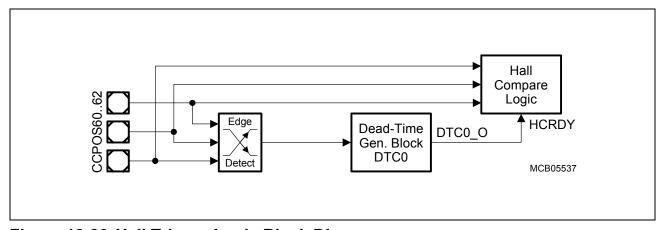

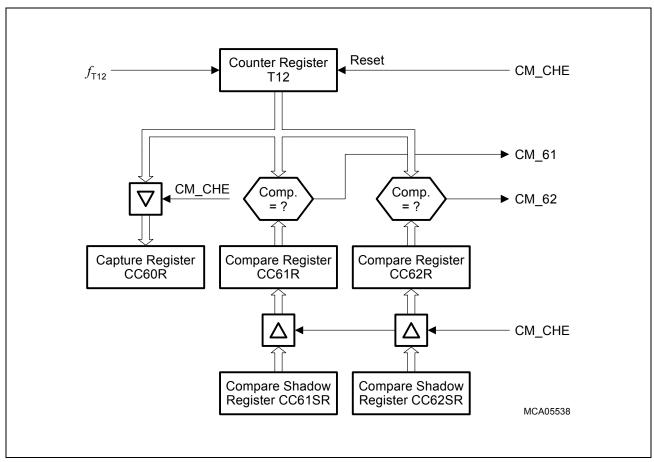

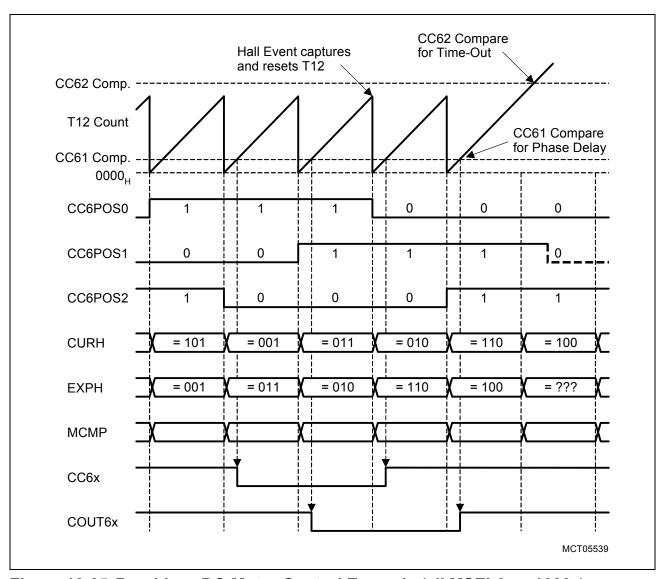

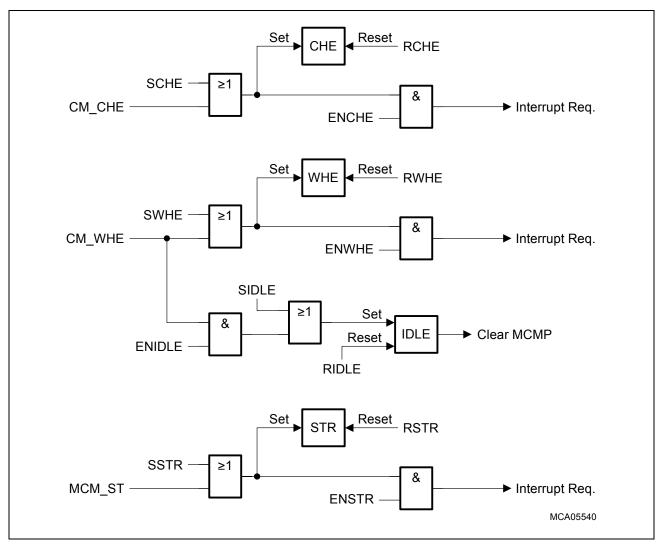

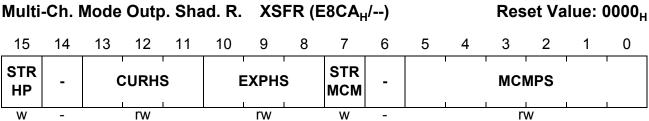

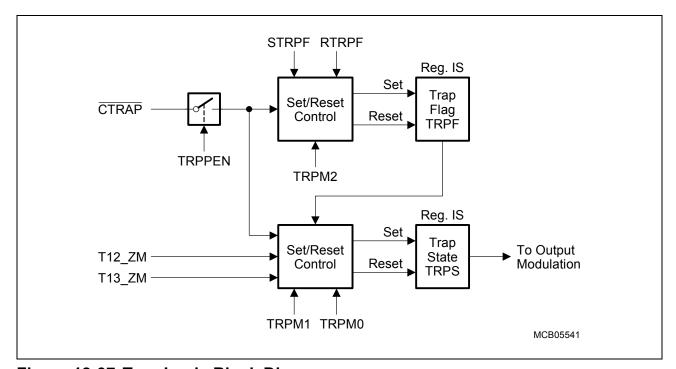

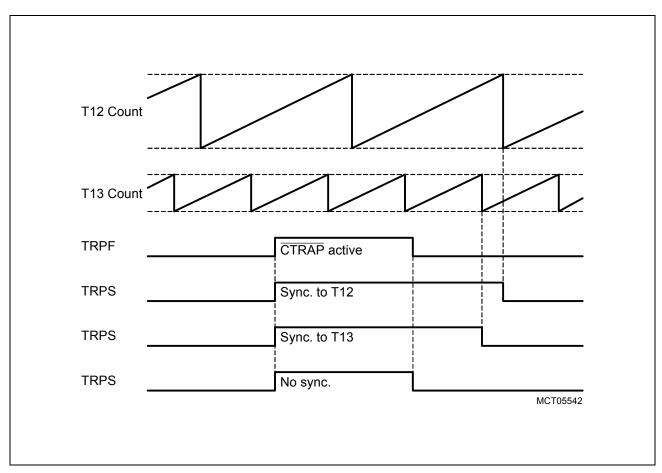

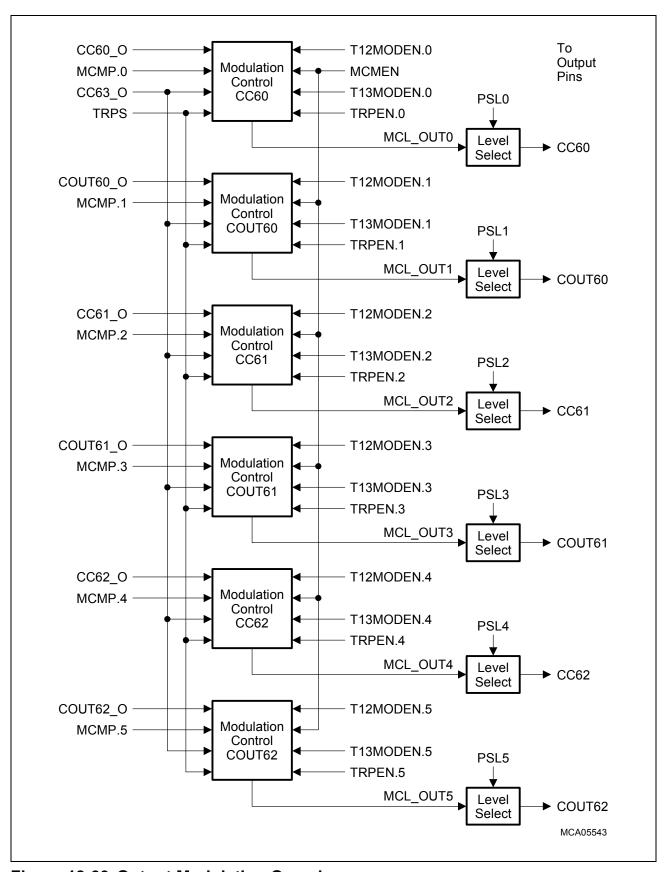

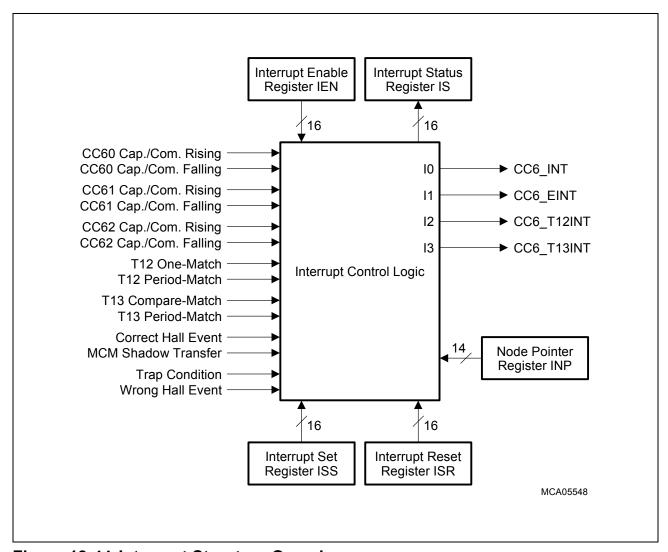

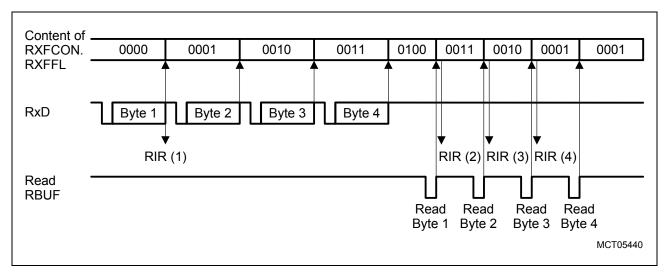

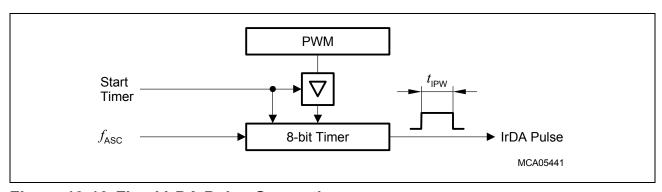

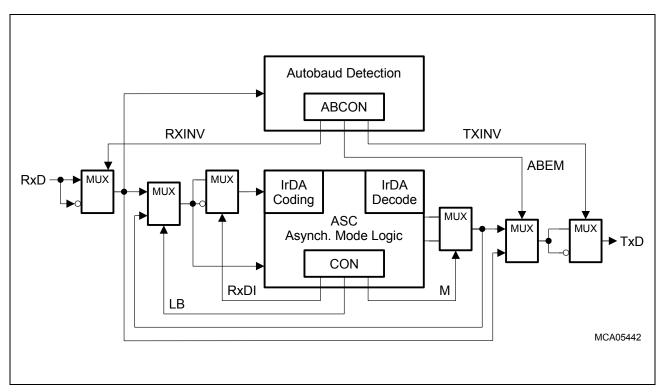

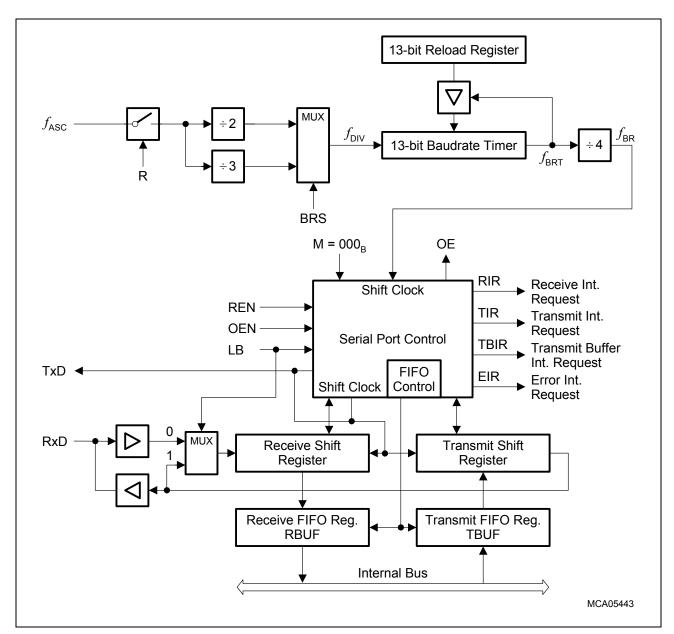

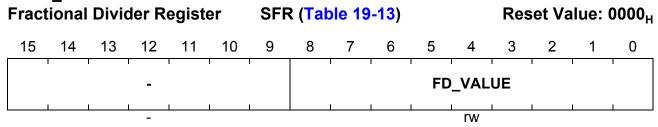

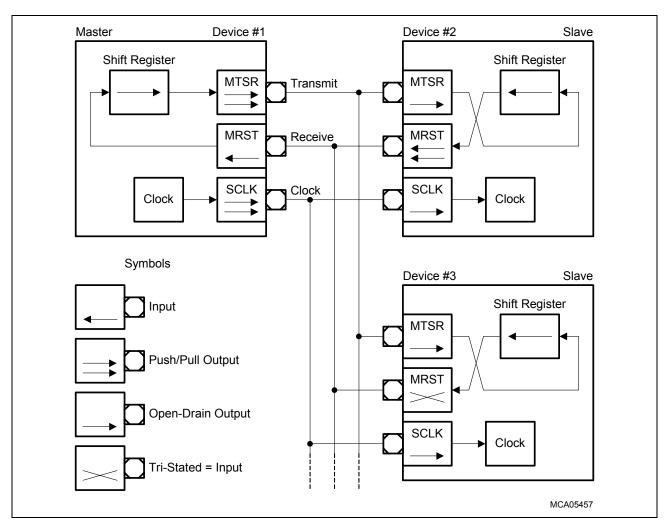

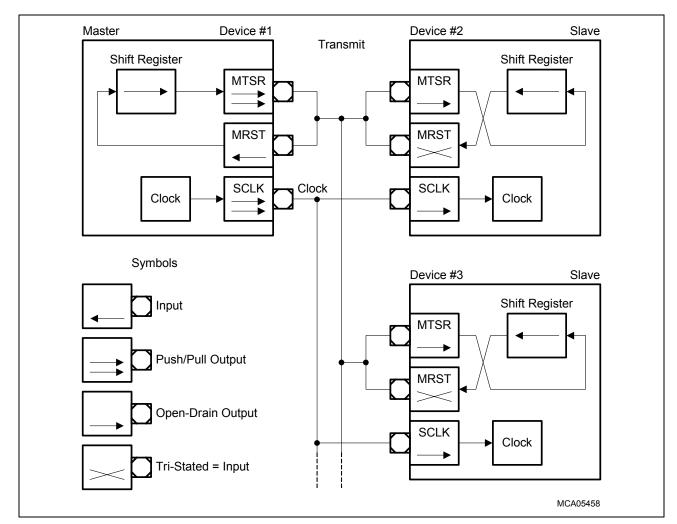

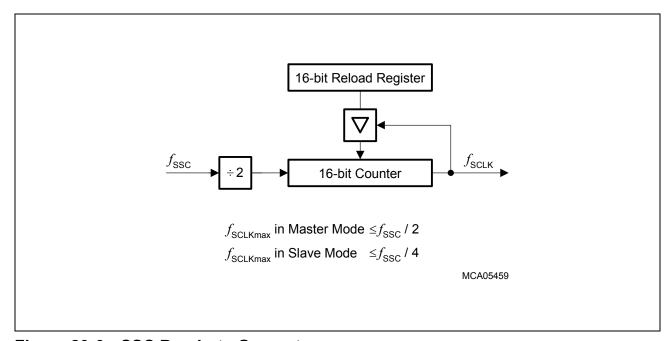

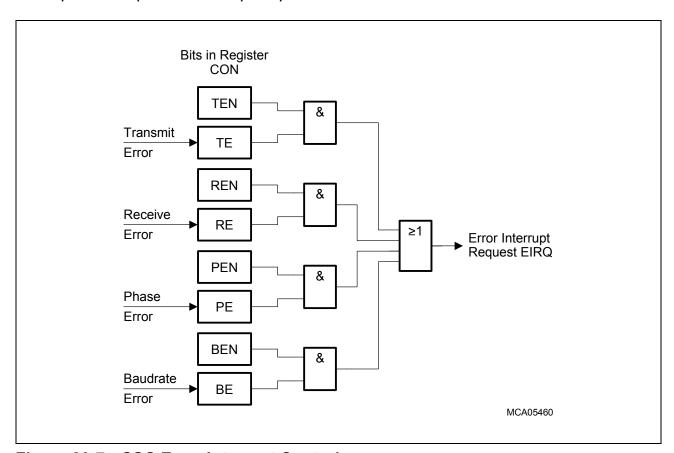

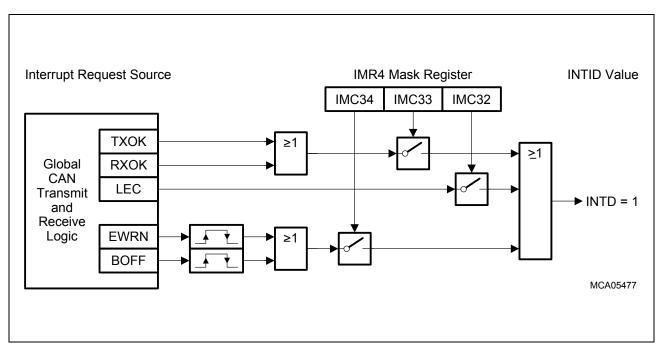

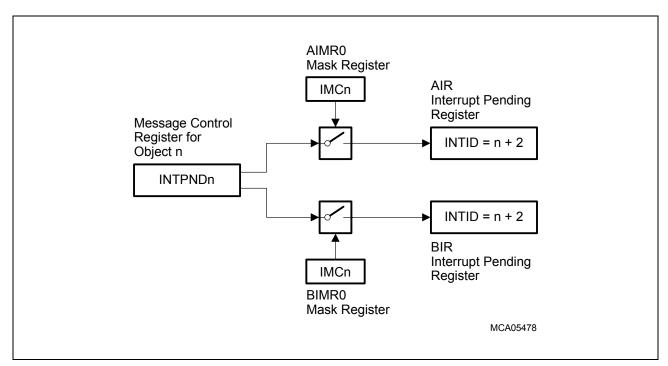

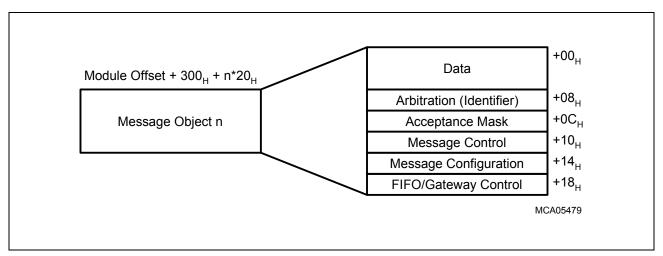

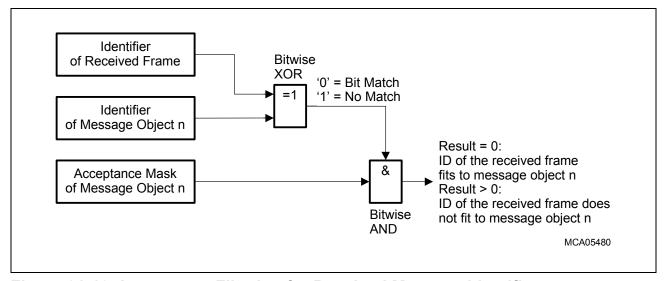

Figure 14-17 GPT1 Timer Reload Configuration for PWM Generation