Errata Sheet, Rel. 1.5, Aug. 2008

**MARKEN**

# XC2300 Derivatives 16/32-Bit Single-Chip Microcontroller with 32-Bit Performance

Microcontrollers

Never stop thinking

Edition 22.08.2008 Published by Infineon Technologies AG 81726 Munich, Germany © 2008 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XC2300 Derivatives 16/32-Bit Single-Chip Microcontroller with 32-Bit Performance

# Microcontrollers

Never stop thinking

# **Table of Contents**

| 1                                    | History List / Change Summary                         | 6                                                                                                              |

|--------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 2                                    | General                                               | 7                                                                                                              |

| 3                                    | Current Documentation                                 | 8                                                                                                              |

| <b>4</b><br>4.1<br>4.2<br>4.3        | Errata Device Overview                                | 9<br>12                                                                                                        |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.4 |                                                       | 18                                                                                                             |

| <b>6</b><br>6.1                      | MultiCAN_AI.040<br>MultiCAN_AI.041<br>MultiCAN_AI.042 | $\begin{array}{c} 20\\ 20\\ 21\\ 23\\ 24\\ 25\\ 26\\ 27\\ 28\\ 30\\ 31\\ 32\\ 33\\ 34\\ 35\\ 35\\ \end{array}$ |

| MultiCAN_TC.029 | 37                                                                                                                                      |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| MultiCAN_TC.030 | 38                                                                                                                                      |

| MultiCAN_TC.031 | 38                                                                                                                                      |

| MultiCAN_TC.032 | 39                                                                                                                                      |

| MultiCAN_TC.035 | 39                                                                                                                                      |

| MultiCAN_TC.037 |                                                                                                                                         |

| MultiCAN_TC.038 | 42                                                                                                                                      |

| OCDS_X.003      |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

| -               |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

| •               |                                                                                                                                         |

|                 |                                                                                                                                         |

| -               |                                                                                                                                         |

| -               |                                                                                                                                         |

| -               |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

| -               |                                                                                                                                         |

|                 |                                                                                                                                         |

| —               |                                                                                                                                         |

|                 | -                                                                                                                                       |

| —               |                                                                                                                                         |

|                 |                                                                                                                                         |

|                 |                                                                                                                                         |

| WDT_X.H001      | 55                                                                                                                                      |

|                 | MultiCAN_TC.030         MultiCAN_TC.031         MultiCAN_TC.032         MultiCAN_TC.035         MultiCAN_TC.037         MultiCAN_TC.038 |

History List / Change Summary

# 1 History List / Change Summary

| l able 1 | History List |                                     |

|----------|--------------|-------------------------------------|

| Version  | Date         | Remark                              |

| 1.0      | 13.07.2007   |                                     |

| 1.1      | 27.07.2007   |                                     |

| 1.2      | 19.10.2007   |                                     |

| 1.3      | 11.04.2008   | Errata Sheet for all product steps. |

| 1.4      | 20.08.2008   | Cancelled release due missing note. |

| 1.5      | 22.08.2008   |                                     |

Table 1 History List

#### General

# 2 General

This Errata Sheet describes the deviations of the XC2300 Derivatives from the current user documentation.

Each erratum identifier follows the pattern Module\_Arch.TypeNumber:

- Module: subsystem, peripheral, or function affected by the erratum

- Arch: microcontroller architecture where the erratum was firstly detected.

- AI: Architecture Independent

- CIC: Companion ICs

- TC: TriCore

- X: XC166 / XE166 / XC2000 Family

- XC8: XC800 Family

- [none]: C166 Family

- **Type**: category of deviation

- [none]: Functional Deviation

- P: Parametric Deviation

- H: Application Hint

- **D**: Documentation Update

- **Number**: ascending sequential number within the three previous fields. As this sequence is used over several derivatives, including already solved deviations, gaps inside this enumeration can occur.

This Errata Sheet applies to all temperature and frequency versions and to all memory size variants of this device, unless explicitly noted otherwise.

Note: This device is equipped with a C166S V2 core. Some of the errata have a workaround which is possibly supported by the compiler tool vendor. Some corresponding compiler switches need possibly to be set. Please see the respective documentation of your compiler.

Some errata of this Errata Sheet do not refer to all of the XC2300 Derivatives, please look to the overview:

- Table 2

for Functional Deviations,

- Table 3

for Deviations from Electrical and Timing Specification and

- Table 4

for Application Hints.

#### **Current Documentation**

## 3 Current Documentation

The Infineon XC2000 Family comprises device types from the XC2200 group, the XC2300 group and the XC2700 group. The XC23xx device types belong to the XC2300 group.

| Device       | XC23xx                                       |

|--------------|----------------------------------------------|

| Marking/Step | EES-AA, EES-AB, ES-AB, AB, EES-AC, ES-AC, AC |

| Package      | PG-LQFP-100, PG-LQFP-144                     |

This Errata Sheet refers to the following documentation:

- XC2300 Derivatives User's Manual Volume 1 System Units

- XC2300 Derivatives User's Manual Volume 2 Peripheral Units

- XC2365 Data Sheet

- XC2387 Data Sheet

- Documentation Addendum (if applicable)

Make sure you always use the corresponding documentation for this device available in category 'Documents' at www.infineon.com/xc2300.

The specific test conditions for EES and ES are documented in a separate Status Sheet.

Note: Devices marked with EES or ES are engineering samples which may not be completely tested in all functional and electrical characteristics, therefore they should be used for evaluation only.

## 4 Errata Device Overview

This chapter gives an overview of the dependencies of individual errata to devices and steps. An X in the column of the sales codes shows that this erratum is valid.

## 4.1 Functional Deviations

Table 2 shows the dependencies of functional deviations in the derivatives.

| Functio                 | onal De                 | viatio           | ns               |  |

|-------------------------|-------------------------|------------------|------------------|--|

| Functional<br>Deviation |                         | XC23xx           |                  |  |

|                         | <b>AA</b> <sup>1)</sup> | AB <sup>2)</sup> | AC <sup>3)</sup> |  |

| ADC_AI.001              | X                       | X                | X                |  |

| BSL_X.003               | X                       |                  |                  |  |

| BSL_X.004               | X                       | X                | X                |  |

| CPU_X.004               | X                       |                  |                  |  |

| DPRAM_X.001             | X                       | X                | X                |  |

| FLASH_X.007             | X                       |                  |                  |  |

| FLASH_X.008             | X                       | X                | X                |  |

| GPT12E_X.001            | X                       | X                | X                |  |

| GSC_X.001               | X                       | X                | X                |  |

| INT_X.007               | X                       | X                | X                |  |

| INT_X.008               | X                       | X                | X                |  |

| INT_X.009               | X                       | X                | X                |  |

| INT_X.010               | X                       | X                | X                |  |

| MultiCAN_AI.040         | X                       | X                | X                |  |

| MultiCAN_AI.041         | X                       | X                | X                |  |

| MultiCAN_AI.042         | X                       | X                | X                |  |

| MultiCAN_AI.043         | X                       | X                | X                |  |

# Table 2Errata Device Overview:Functional Deviations

# Table 2Errata Device Overview:Functional Deviations (cont'd)

|                         |                         |                  | 10 (00)          |  |

|-------------------------|-------------------------|------------------|------------------|--|

| Functional<br>Deviation |                         | XC23xx           |                  |  |

|                         | <b>AA</b> <sup>1)</sup> | AB <sup>2)</sup> | AC <sup>3)</sup> |  |

| MultiCAN_AI.044         | X                       | X                | X                |  |

| MultiCAN_AI.045         | X                       | X                | X                |  |

| MultiCAN_AI.046         | X                       | X                | X                |  |

| MultiCAN_TC.025         | X                       | X                | X                |  |

| MultiCAN_TC.026         | X                       | X                | X                |  |

| MultiCAN_TC.027         | X                       | X                | X                |  |

| MultiCAN_TC.028         | X                       | X                | X                |  |

| MultiCAN_TC.029         | X                       | X                | X                |  |

| MultiCAN_TC.030         | X                       | X                | X                |  |

| MultiCAN_TC.031         | X                       | X                | X                |  |

| MultiCAN_TC.032         | X                       | X                | X                |  |

| MultiCAN_TC.035         | X                       | X                | X                |  |

| MultiCAN_TC.037         | X                       | X                | X                |  |

| MultiCAN_TC.038         | X                       | X                | X                |  |

| OCDS_X.003              | X                       | X                | X                |  |

| POWER_X.003             | X                       |                  |                  |  |

| POWER_X.005             | X                       |                  |                  |  |

| RESET_X.002             | X                       | X                | X                |  |

| RESET_X.003             | X                       | X                | X                |  |

| RTC_X.003               | X                       | X                | X                |  |

| USIC_AI.003             | X                       | X                | X                |  |

| USIC_AI.004             | X                       | X                | X                |  |

1) Valid for EES-AA.

2) Valid for EES-AB, ES-AB and AB.

3) Valid for EES-AC, ES-AC and AC. No errata fixing was done for these steps. The only purpose was yield optimization.

### 4.2 Deviations from Electrical and Timing Specification

Table 3 shows the dependencies of deviations from the electrical and timing specification in the derivatives.

# Table 3Product Overview:Deviations from Electrical and Timing Specification

| Functional<br>Deviation | XC23xx                  |                         |                  |  |

|-------------------------|-------------------------|-------------------------|------------------|--|

|                         | <b>AA</b> <sup>1)</sup> | <b>AB</b> <sup>2)</sup> | AC <sup>3)</sup> |  |

- none -

1) Valid for EES-AA.

2) Valid for EES-AB, ES-AB and AB.

3) Valid for EES-AC, ES-AC and AC. No errata fixing was done for these steps. The only purpose was yield optimization.

## 4.3 Application Hints

Table 4 shows the dependencies of application hints in the derivatives.

# Table 4Product Overview:Application Hints

|                         | 1                       |                  |                  |

|-------------------------|-------------------------|------------------|------------------|

| Functional<br>Deviation |                         | XC23xx           |                  |

|                         | <b>AA</b> <sup>1)</sup> | AB <sup>2)</sup> | AC <sup>3)</sup> |

| CAPCOM12_X.H001         | X                       | X                | X                |

| CC6_X.H001              | X                       | X                | X                |

| INT_X.H002              | X                       | X                | X                |

| JTAG_X.H001             | X                       | X                | X                |

| MultiCAN_AI.H005        | X                       | X                | X                |

| MultiCAN_AI.H006        | X                       | X                | X                |

| MultiCAN_TC.H002        | X                       | X                | X                |

| MultiCAN_TC.H003        | X                       | X                | X                |

| MultiCAN_TC.H004        | X                       | X                | X                |

| OCDS_X.H002             | X                       | X                | X                |

| RESET_X.H002            | X                       |                  |                  |

| RESET_X.H003            | X                       | X                | X                |

| RTC_X.H003              | X                       | X                | X                |

| StartUp_X.H002          | X                       | X                | X                |

| USIC_AI.H001            | X                       | X                | X                |

| WDT_X.H001              | X                       |                  |                  |

1) Valid for EES-AA.

2) Valid for EES-AB, ES-AB and AB.

3) Valid for EES-AC, ES-AC and AC. No errata fixing was done for these steps. The only purpose was yield optimization.

# 5 Short Errata Description

This chapter gives an overview over the description and shows changes to the last Errata Sheet.

## 5.1 Errata removed in this Errata Sheet

Table 5 shows an overview of removed errata in this Errata Sheet. In column

Change was described why it can remove.

| Errata         | Short Description                                                                           | Change                           |

|----------------|---------------------------------------------------------------------------------------------|----------------------------------|

| INT_X.H001     | Software Modifications of Interrupt<br>Enable (xx_IE) or Interrupt Request<br>(xx_IR) Flags | User's Manual <sup>1)</sup>      |

| Leakage_X.D002 | Pin Leakage Calculation Formula                                                             | Data Sheet <sup>1)</sup>         |

| POWER_X.001    | Wake-up Trigger during Power<br>Transfers                                                   | Programmer's Guide <sup>1)</sup> |

| RESET_X.001    | System Reset                                                                                | User's Manual <sup>1)</sup>      |

| RESET_X.H001   | Register RSTSTAT0 after Power-on<br>Reset for Domain DMP_1                                  | User's Manual <sup>1)</sup>      |

#### Table 5 Errata removed in this Errata Sheet

1) An update in the documentation is done.

## 5.2 Functional Deviations

Table 6 shows a short description of the functional deviations.

| Functional<br>Deviation | Short Description                                                                          | Chg | Pg |

|-------------------------|--------------------------------------------------------------------------------------------|-----|----|

| ADC_AI.001              | Conversions requested in Slot 0 started twice                                              |     | 20 |

| BSL_X.003               | Single Wire Support for UART Bootstrap<br>Loader                                           |     | 20 |

| BSL_X.004               | Evaluation of UART Bootstrap Loader<br>Identification Byte in Single Wire<br>Configuration |     | 21 |

| CPU_X.004               | Write requests to PSRAM, to IMB SFRs, or as part of Flash Command Sequences                |     | 21 |

| DPRAM_X.001             | Parity Error Flag for DPRAM                                                                |     | 23 |

| FLASH_X.007             | Flash Erase Command "Erase Sector"                                                         |     | 24 |

| FLASH_X.008             | Flash Read after Flash Erase Command                                                       |     | 24 |

| GPT12E_X.001            | T5/T6 in Counter Mode with BPS2 = 1X <sub>B</sub>                                          |     | 25 |

| GSC_X.001               | Clearing of Request Triggers by the GSC                                                    |     | 25 |

| INT_X.007               | Interrupt using a Local Register Bank during execution of IDLE                             |     | 26 |

| INT_X.008               | HW Trap during Context Switch in Routine using a Local Bank                                |     | 27 |

| INT_X.009               | Delayed Interrupt Service of Requests using a Global Bank                                  |     | 28 |

| INT_X.010               | HW Traps and Interrupts may get postponed                                                  |     | 30 |

| MultiCAN_AI.040         | Remote frame transmit acceptance filtering error                                           |     | 31 |

| MultiCAN_AI.041         | Dealloc Last Obj                                                                           |     | 31 |

Table 6Functional Deviations

| Table 6 Functi          | onal Deviations (cont'd)                                           |     |    |

|-------------------------|--------------------------------------------------------------------|-----|----|

| Functional<br>Deviation | Short Description                                                  | Chg | Pg |

| MultiCAN_AI.042         | Clear MSGVAL during transmit<br>acceptance filtering               |     | 32 |

| MultiCAN_AI.043         | Dealloc Previous Obj                                               |     | 32 |

| MultiCAN AI.044         | RxFIFO Base SDT                                                    |     | 33 |

| MultiCAN AI.045         | OVIE Unexpected Interrupt                                          |     | 33 |

| MultiCAN AI.046         | Transmit FIFO base Object position                                 |     | 34 |

| MultiCAN_TC.025         | RXUPD behavior                                                     |     | 34 |

| MultiCAN TC.026         | MultiCAN Timestamp Function                                        |     | 35 |

| MultiCAN_TC.027         | MultiCAN Tx Filter Data Remote                                     |     | 35 |

| MultiCAN TC.028         | SDT behavior                                                       |     | 35 |

| MultiCAN_TC.029         | Tx FIFO overflow interrupt not generated                           |     | 37 |

| <br>MultiCAN_TC.030     | Wrong transmit order when CAN error at start of CRC transmission   |     | 38 |

| MultiCAN_TC.031         | List Object Error wrongly triggered                                |     | 38 |

| MultiCAN TC.032         | MSGVAL wrongly cleared in SDT mode                                 |     | 39 |

| MultiCAN_TC.035         | Different bit timing modes                                         |     | 39 |

| MultiCAN_TC.037         | Clear MSGVAL                                                       |     | 41 |

| MultiCAN_TC.038         | Cancel TXRQ                                                        |     | 42 |

| OCDS_X.003              | Peripheral Debug Mode Settings cleared by Reset                    |     | 42 |

| POWER_X.003             | External Supply of Digital Core Supply<br>Voltage V <sub>DDI</sub> |     | 43 |

| POWER_X.005             | Start-up of DMP_1 at low temperature                               |     | 43 |

| RESET_X.002             | Startup Mode Selection is not Valid in SCU_STSTAT.HWCFG            |     | 44 |

| RESET_X.003             | P2.[2:0] and P10.[12:0] Switch to Input                            | New | 44 |

| RTC_X.003               | Interrupt Generation in Asynchronous<br>Mode                       |     | 44 |

| Table 6 | Functional | Deviations | (cont'd) | ) |

|---------|------------|------------|----------|---|

|---------|------------|------------|----------|---|

| Functional<br>Deviation | Short Description                                                   | Chg | Pg |

|-------------------------|---------------------------------------------------------------------|-----|----|

| USIC_AI.003             | TCSRL.SOF and TCSRL.EOF not cleared after a transmission is started |     | 45 |

| USIC_AI.004             | Receive shifter baudrate limitation                                 |     | 45 |

## 5.3 Deviations from Electrical and Timing Specification

Table 7 shows a short description of the electrical- and timing deviations from the specification.

#### Table 7 Deviations from Electrical and Timing Specification

| AC/DC/ADC<br>Deviation | Short Description | Chg | Pg |

|------------------------|-------------------|-----|----|

| - none -               |                   |     |    |

## 5.4 Application Hints

The Table 8 shows a short description of the application hints.

| Hint             | Short Description                                                              | Chg        | D~        |  |

|------------------|--------------------------------------------------------------------------------|------------|-----------|--|

|                  | Short Description                                                              |            | Pg        |  |

| CAPCOM12_X.H001  | Enabling Single Event Operation                                                | New        | 47        |  |

| CC6_X.H001       | Modifications of Bit MODEN in Register<br>CCU6x_KSCFG                          |            | 48        |  |

| INT_X.H002       | Increased Latency for Hardware Traps                                           |            | <b>48</b> |  |

| JTAG_X.H001      | JTAG Pin Routing                                                               |            | <b>49</b> |  |

| MultiCAN_AI.H005 | TxD Pulse upon short disable request                                           | Upd<br>ate | 50        |  |

| MultiCAN_AI.H006 | Time stamp influenced by resynchronization                                     | New        | 50        |  |

| MultiCAN_TC.H002 | Double Synchronization of receive input                                        |            | 50        |  |

| MultiCAN_TC.H003 | Message may be discarded before transmission in STT mode                       |            | 51        |  |

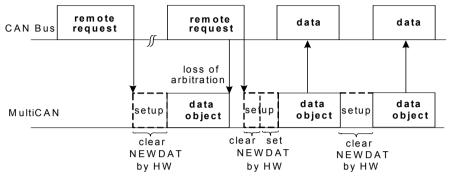

| MultiCAN_TC.H004 | Double remote request                                                          | Upd<br>ate | 51        |  |

| OCDS_X.H002      | Suspend Mode Behavior for MultiCAN                                             |            | 52        |  |

| RESET_X.H002     | Oscillator fail detection active by default                                    | New        | 53        |  |

| RESET_X.H003     | How to Trigger a PORST after an Internal Failure                               | New        | 54        |  |

| RTC_X.H003       | Changing the RTC Configuration                                                 |            | 54        |  |

| StartUp_X.H002   | FCONCS0FCONCS4 Registers are<br>Always Configured in External Start-Up<br>Mode |            |           |  |

| USIC_AI.H001     | FIFO RAM Parity Error Handling                                                 |            | 55        |  |

| WDT_X.H001       | Watchdog Timer Reset Functionality not enabled by Default                      |            | 55        |  |

## 6 Detailed Errata Description

This chapter shows a detailed description of the erratum.

## 6.1 Functional Deviations

#### ADC\_AI.001 Conversions requested in Slot 0 started twice

A conversion n+1 requested in arbiter slot 0 will be started twice if all configuration and timing conditions of the following sequence are met:

- 1. A conversion n of a channel is currently running.

- 2. Slot 0 has won the arbitration while conversion n is in progress.

- Conversion n ends one f<sub>ADCD</sub> clock cycle before the end of an arbitration cycle.

- 4. The conversion n+1 initiated in slot 0 is started exactly in the last f<sub>ADCD</sub> clock cycle of this arbitration-cycle (see 3.).

- 5. The conversion time of conversion n+1 is shorter than 2 arbitration cycles.

If all these conditions are met, then the request of slot 0 cannot be cleared in time by the arbiter, and conversion n+1 is requested a second time.

#### Workaround

The conversion time for channels requested in slot 0 must not be shorter than two arbitration cycles.

#### BSL\_X.003 Single Wire Support for UART Bootstrap Loader

In the current implementation, if the UART bootloader is used in a single wire configuration (RxD/TxD externally connected, e.g. K-line environment), the following restriction must be considered:

The identification byte  $D5_H$  that is sent by the microcontroller is also received and interpreted as first (of 32) opcode byte(s).  $D5_H$  represents the opcode of the 4-byte instruction 'MOVBS mem, reg'.

#### Workaround

The host program must only send 31 (instead of 32) bytes. The first 3 bytes should complement  $D5_H$  to a useful (or at least harmless) instruction, e.g.

(D5) 8E 1E FF results in MOVBS ONES, ZEROS.

In case the secondary bootstrap loader described in the 'System Units' Manual is used, the final JMPS SEG Code\_Start, SOF Code\_Start instruction can be omitted to compensate for the initial  $D5_H$  + 3 'fill bytes'. In this case the start address of the secondary loader must be 0xE00020.

# <u>BSL\_X.004</u> Evaluation of UART Bootstrap Loader Identification Byte in Single Wire Configuration

In the current implementation, transmission of the start bit of the identification byte ( $D5_H$ ) partially overlaps with the stop bit time slot of the zero byte sent by the host. This does not present any problem in a duplex (2-wire) configuration.

If the UART bootstrap loader is used in a single wire configuration (RxD/TxD externally connected, e.g. K-line environment), depending on the baudrate, the start bit of the identification byte may not be correctly recognized by the host. At 9600 Baud, the host typically interprets the identification byte as  $F5_{H}$ .

#### Workaround

The host software either should not evaluate the received identification byte, or should also tolerate values other than  $D5_{H}$ .

# <u>CPU\_X.004</u> Write requests to PSRAM, to IMB SFRs, or as part of Flash Command Sequences

Under exceptional pipeline conditions, write requests to specific memory areas are not executed if they coincide within one clock cycle with read requests from specific address ranges.

Write requests to the following memory areas can get lost:

Writes to variables located in the Program SRAM (PSRAM) in segment E0<sub>H</sub> (minimum access time) or in segment E8<sub>H</sub> (with Flash access timing)

- Writes to IMB SFRs (IMB\_..., see table in chapter about Program Memory Control in User's Manual), located in the last 256 bytes of segment FF<sub>H</sub>

- Writes to the internal Program Flash address range (mapped in segments C0<sub>H</sub> and higher), i.e. Flash Command Sequences may either not be executed at all (single cycle commands), or may be executed incorrectly (potentially resulting in a sequence error)

A necessary condition for losing a write request is that the write request is followed by a particular read request that gets cancelled (e.g. operand read after mispredicted conditional jump, etc.).

Read requests that potentially can cause this critical scenario are the following:

- Operand reads from the internal Program Flash

- Operand reads from the PSRAM in segment E8<sub>H</sub> (with Flash access timing)

- Operand reads from the External Memory Area via the EBC in the lower 32 Kbytes of segment 0<sub>H</sub>, in segments 1<sub>H</sub>...1F<sub>H</sub>, and in segments 40<sub>H</sub>...BF<sub>H</sub>, excluding the I/O area (segments 20<sub>H</sub>...3F<sub>H</sub>)

Instruction fetches from internal Program Flash or PSRAM, or operand reads from the I/O area (segments  $20_{H}...3F_{H}$ , including USIC and CAN modules) can not trigger the problematic condition.

#### Example

```

1 MOV [-R1], R12 ; write operand to PSRAM

; assumed: R1 points to PSRAM

2 JMPA+ cc_NN, label1 ; jump predicted taken but not taken

; assumed: R12 is negative

3 ...

1 abel1:

n MOV R3, [R0] ; read operand from Flash

; assumed: R0 points to Flash

```

When instruction n is cancelled due to the mispredicted jump 2 this will erroneously suppress the write to PSRAM by instruction 1. Note that other functions (besides the write) of this instruction 1 will be performed, e.g. the predecrement of R1 due to the addressing mode [-R1].

#### Workarounds

Because the timing conditions under which this problem occurs are quite complex the proposed workarounds are more restrictive than absolutely necessary. Depending on whether operand write or read accesses are more performance relevant (or easier to control, respectively), one of the following workarounds may be chosen:

#### Workaround1:

This workaround limits write requests to the critical memory areas:

Do not enable the PSRAM as RAM in the compiler (locator options), use PSRAM as ROM only. The only software routines that write to the critical memory areas are then the driver to perform the Flash Command Sequences, and the routine that copies (constant) data and code from Flash to PSRAM. These pieces of software must be carefully examined for the error conditions and must be verified (including writes to IMB SFRs in the initialization code).

#### Workaround2:

This workaround allows to use the PSRAM as RAM for variable storage while controlling problematic operand reads:

Perform operand reads from critical memory areas (see list for operand reads above) in a controlled way e.g. in a separate function. This function may read the required operands when no write access to the PSRAM has been performed by the last 4 instructions. Interrupts should be disabled in case PEC transfers to the PSRAM are used.

Note: In case a debugger is used, the 'window refresh' feature for windows covering an internal flash section containing (constant) operands that are also read by the program should be disabled while the program is running

#### **DPRAM\_X.001** Parity Error Flag for DPRAM

The parity error flag for the dual port memory (DPRAM) does not work correctly. Under certain conditions bit PECON.PEFDP is set, although there is no error in the DPRAM.

#### Workaround

Do not enable the parity error trap for the dual port memory, i.e. leave bit **PECON.PEENDP = 0** (default after power-on reset).

#### FLASH X.007 Flash Erase Command "Erase Sector"

Do not use the "Erase Sector" command.

#### Workaround

When programming a device for the first time (after delivery from Infineon) it is recommended to program it without erasing. When later data shall be replaced use only the "Erase Page" command before programming the new data.

#### FLASH\_X.008 Flash Read after Flash Erase Command

Under certain conditions all Flash erase commands do not work correctly. After erasing, all erased bits must be programmed with new data or with all-zero data before reading any data from the addressed sector is allowed.

#### Workarounds

- Erase a range of Flash memory and program it completely with new data before reading. This is the fastest solution. Additional hint: A Flash driver could implement a programming function that performs first an "Erase Page" and uses directly thereafter "Program Page" to program the data of this page. The Flash driver wouldn't need any separate erase function.

- 2. Erase a range of Flash memory and program it completely with all-zero data. Only after this the range may be read. Data can be programmed later<sup>1)</sup>.

<sup>1)</sup> Please note: only in order to implement this workaround for the noted device steps it is allowed to execute two program commands before erasing it.

#### <u>GPT12E\_X.001</u> T5/T6 in Counter Mode with BPS2 = 1X<sub>B</sub>

When T5 and/or T6 are configured for counter mode (bit field  $TxM = 001_B$  in register GPT12E\_TxCON, x = 5, 6), and bit field **BPS2 = 1X**<sub>B</sub> in register GPT12E\_T6CON, then edge detection for the following count input and control signals does not work correctly:

#### **T5IN, T6IN, T5EUD, T6EUD**.

Note: The configuration where T5 counts the overflow/underflow events of T6 is not affected by this problem.

#### Workaround

Do not set bit field BPS2 =  $1X_B$  in register GPT12E\_T6CON when T5 and/or T6 are configured for counter mode. Use only settings BPS2 =  $0X_B$  when T5 and/or T6 are configured for counter mode.

#### GSC X.001 Clearing of Request Triggers by the GSC

After a request from sources with priority 5..10 ( $\overline{\text{ESR0}}$ ...GPT12E, see table in Chapter "Global State Controller (GSC)" of the current User's Manual), the following problem will occur:

A trigger for a command request (Wake-up, Clock-off, Suspend Mode) that is enabled in register GSCEN remains pending in the GSC after the arbitration has been finished and the command has been requested. As a consequence, further request triggers with the same or a lower priority will be ignored (14 = lowest priority).

#### Example

A request from the OCDS to enter Suspend Mode (request source OCDS entry, priority 14) will be ignored if (at any time before) an interrupt request has occurred (request source ITC, priority 9), and the ITC request trigger is enabled in register GSCEN. In this case, modules that are programmed to stop in Suspend Mode (selected in bit field SUMCFG) will continue to run.

#### Workaround

Disable triggers from request sources that are not used by the application in register GSCEN.

For other sources that shall trigger the GSC, clear and then set again the respective trigger enable bits in register GSCEN each time the GSC logic shall be armed.

#### INT\_X.007 Interrupt using a Local Register Bank during execution of IDLE

During the execution of the IDLE instruction, if an interrupt which uses a local register bank is acknowledged, the CPU may stall, preventing further code execution. Recovery from this condition can only be made through a hardware or watchdog reset.

All of the following conditions must be present for the problem to occur:

- The IDLE instruction is executed while the global register bank is selected (bit field BANK = 00<sub>B</sub> in register PSW),

- The interrupting routine is using one of the **local** register banks (BANK = 10<sub>B</sub> or 11<sub>B</sub>), and the local register bank is selected automatically via the bank selection registers BNKSEL0...3, (i.e. the interrupting routine has a priority level ≥12),

- The system stack is located in the internal dual-ported RAM (DPRAM, locations 0F600<sub>H</sub> ... 0FDFF<sub>H</sub>),

- The interrupt is acknowledged during the first 8 clock cycles of the IDLE instruction execution.

#### Workaround 1

Disable interrupts (either globally, or only interrupts using a local register bank) before execution of IDLE:

| BCLR | IEN | ; | Disable interrupts globally |

|------|-----|---|-----------------------------|

| IDLE |     | ; | CPU enters idle mode        |

| BSET | IEN | ; | After exit from idle mode   |

|      |     | ; | re-enable interrupts        |

If an interrupt request is generated during this sequence, the CPU leaves idle mode and acknowledges the interrupt after BSET IEN.

#### Workaround 2

Do not use local register banks, use only global register banks.

#### Workaround 3

Locate the system stack in a memory other than the DPRAM, e.g. in DSRAM.

### INT\_X.008 HW Trap during Context Switch in Routine using a Local Bank

When a hardware trap occurs under specific conditions in a routine using a local register bank, the CPU may stall, preventing further code execution. Recovery from this condition can only be made through a hardware or watchdog reset.

All of the following conditions must be present for this problem to occur:

- The routine that is interrupted by the hardware trap is using one of the local register banks (bit field PSW.BANK = 10<sub>B</sub> or 11<sub>B</sub>)

- The system stack is located in the internal dual-ported RAM (DPRAM, locations 0F600<sub>H</sub> ... 0FDFF<sub>H</sub>)

- The hardware trap occurs in the second half (load phase) of a context switch operation triggered by one of the following actions:

- a) Execution of the IDLE instruction, or

- b) Execution of an instruction writing to the Context Pointer register CP (untypical case, because this would mean that the routine using one of the local banks modifies the CP contents of a global bank)

#### Workaround 1

Locate the system stack in a memory other than the DPRAM, e.g. in DSRAM.

#### Workaround 2

Do not use local register banks, use only global register banks.

#### Workaround 3

Condition b) (writing to CP while a local register bank context is selected) is not typical for most applications. If the application implementation already eliminates the possibility for condition b), then only a workaround for condition

a) is required.

The workaround for condition a) is to make sure that the IDLE instruction is executed within a code sequence that uses a global register bank context.

### INT\_X.009 Delayed Interrupt Service of Requests using a Global Bank

Service of an interrupt request using a global register bank is delayed - regardless of its priority - if it would interrupt a routine using one of the local register banks in the following situations:

Case 1:

- The Context Pointer CP is written to (e.g. by POP, MOV, SCXT ... instructions) within a routine that uses one of the **local** register banks (bit field PSW.BANK = 10<sub>B</sub> or 11<sub>B</sub>),

- Then an interrupt request occurs which is programmed (with GPRSELx = 00<sub>B</sub>) to automatically use the global bank via the bank selection registers BNKSEL0...3 (i.e. the interrupting routine has a priority level ≥12).

Note that this scenario is regarded as untypical case, because this would mean that the routine using one of the local banks modifies the CP contents of a global bank.

In this case service of the interrupt request is delayed until bit field PSW.BANK becomes  $00_B$ , e.g. by explicitly writing to the PSW, or by an implicit update from the stack when executing the RETI instruction at the end of the routine using the local bank.

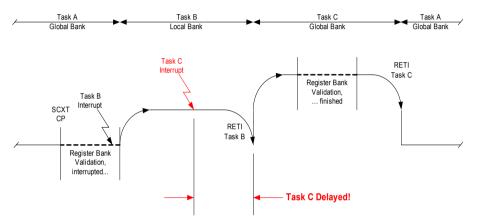

Case 2 (see also Figure 1):

- The Context Pointer CP is written to (e.g. by POP, MOV, SCXT ... instructions) within a routine (Task A) that uses a global register bank (bit field PSW.BANK = 00<sub>R</sub>), i.e. the context for this routine will be modified,

- This context switch procedure (19 cycles) is interrupted by an interrupt request (Task B) which is programmed (with GPRSELx = 1X<sub>B</sub>) to automatically use one of the **local** banks via the bank selection registers BNKSEL0...3 (i.e. the interrupting routine has a priority level ≥12),

- Before the corresponding interrupt service routine is finished, another interrupt request (Task C) occurs which is programmed (with GPRSELx =

$00_B$ ) to automatically use the **global** bank via the bank selection registers BNKSEL0...3 (i.e. the interrupting routine has a priority level  $\geq$ 13)

In this case service of this interrupt request (for Task C) is delayed until bit field PSW.BANK becomes  $00_B$  after executing the RETI instruction at the end of the routine (Task B) using the local bank.

### Figure 1 Example for Case 2: Interrupt Service for Task C delayed

#### Workaround for Case 1

Do not write to the CP register (i.e. modify the context of a global bank) while a local register bank context is selected.

#### Workaround for Case 2

When using both local and global register banks via the bank selection registers BNKSEL0...3 for interrupts on levels  $\geq$ 12, ensure that there is no interrupt using a global register bank that has a higher priority than an interrupt using a local register bank.

Example 1:

Local bank interrupts are used on levels 14 and 15, no local bank interrupts on level 12 and 13. In this case, global bank interrupts on level 15 must not be used.

Example 2:

Local bank interrupts are used on level 12. In this case, no global bank interrupts must be used on levels 13, 14, 15.

### INT\_X.010 HW Traps and Interrupts may get postponed

Under the special conditions described below, a hardware trap (HWTx) and subsequent interrupts, PEC transfers, OCDS service requests (on priority level <  $11_{\rm H}$ ) or class B and class A traps (if HWTx also was class A) may get postponed until the next RETI instruction is executed. If no RETI is executed, these requests may get postponed infinitely.

Both of the following conditions must be fulfilled at the same time when the trigger for the hardware trap HWTx occurs in order to cause the problem:

- 1. The pipeline is cancelled due to one of the following reasons:

- a) a multiply or divide instruction is followed by a mispredicted conditional (zero-cycle) jump.

- b) a class A hardware trap is triggered quasi-simultaneously with the request for a class B trap (= HWTx), i.e. the trigger for the class A trap arrives before the previously injected TRAP instruction for the class B trap has reached the Execute stage of the pipeline. In this case, the class A trap is entered, but when the RETI instruction at

the end of the class A trap routine is executed, the pending class B trap (HWTx) is **not** entered, and subsequent interrupts/PECs/class B traps are postponed until the next RETI.

- c) a break is requested by the debugger.

- 2. The pipeline is stalled in the Execute or Write Back stage due to consecutive writes, or due to a multi-cycle write that is performed to a memory area with wait states (PSRAM, external memory).

### Workaround

Disable overrun of pipeline bubbles by setting bit OVRUN (CPUCON2.4) = 0.

#### MultiCAN\_AI.040 Remote frame transmit acceptance filtering error

Correct behaviour:

Assume the MultiCAN message object receives a remote frame that leads to a valid transmit request in the same message object (request of remote answer), then the MultiCAN module prepares for an immediate answer of the remote request. The answer message is arbitrated against the winner of transmit acceptance filtering (without the remote answer) with a respect to the priority class (MOARn.PRI).

#### Wrong behaviour:

Assume the MultiCAN message object receives a remote frame that leads to a valid transmit request in the same message object (request of remote answer), then the MultiCAN module prepares for an immediate answer of the remote request. The answer message is arbitrated against the winner of transmit acceptance filtering (without the remote answer) with a respect to the CAN arbitration rules and not taking the PRI values into account.

If the remote answer is not sent out immediately, then it is subject to further transmit acceptance filtering runs, which are performed correctly.

#### Workaround

Set  $MOFCRn.FRREN=1_B$  and MOFGPRn.CUR to this message object to disable the immediate remote answering.

#### MultiCAN\_AI.041 Dealloc Last Obj

When the last message object is deallocated from a list, then a false list object error can be indicated.

#### Workaround

Ignore the list object error indication that occurs after the deallocation of the last message object.

or

• Avoid deallocating the last message object of a list.

#### MultiCAN AI.042 Clear MSGVAL during transmit acceptance filtering

Assume all CAN nodes are idle and no writes to MOCTRn of any other message object are performed. When bit MOCTRn.MSGVAL of a message object with valid transmit request is cleared by software, then MultiCAN may not start transmitting even if there are other message objects with valid request pending in the same list.

#### Workaround

• Do not clear MOCTRn.MSGVAL of any message object during CAN operation. Use bits MOCTRn.RXEN, MOCTRn.TXEN0 instead to disable/reenable reception and transmission of message objects.

or

• Take a dummy message object, that is not allocated to any CAN node. Whenever a transmit request is cleared, set MOCTRm.TXRQ of the dummy message object thereafter. This retriggers the transmit acceptance filtering process.

#### MultiCAN AI.043 Dealloc Previous Obj

Assume two message objects m and n (message object n = MOCTRm.PNEXT, i.e. n is the successor of object m in the list) are allocated. If message m is reallocated to another list or to another position while the transmit or receive acceptance filtering run is performed on the list, then message object n may not be taken into account during this acceptance filtering run. For the frame reception message object n may not receive the message because n is not taken into account for receive acceptance filtering. The message is then received by the second priority message object (in case of any other acceptance filtering match) or is lost when there is no other message object n may not be selected for transmission, whereas the second highest priority message object in the list

with valid transmit request, then no transmission is scheduled in this filtering round. If in addition the CAN bus is idle, then no further transmit acceptance filtering is issued unless another CAN node starts a transfer or one of the bits MSGVAL, TXRQ, TXEN0, TXEN1 is set in the message object control register of any message object.

#### Workaround

- After reallocating message object m, write the value one to one of the bits MSGVAL, TXRQ, TXEN0, TXEN1 of the message object control register of any message object in order to retrigger transmit acceptance filtering.

- For frame reception, make sure that there is another message object in the list that can receive the message targeted to n in order to avoid data loss (e.g. a message object with an acceptance mask=0<sub>D</sub> and PRI=3<sub>D</sub> as last object of the list).

#### MultiCAN\_AI.044 RxFIFO Base SDT

If a receive FIFO base object is located in that part of the list, that is used for the FIFO storage container (defined by the top and bottom pointer of this base object) and bit SDT is set in the base object (CUR pointer points to the base object), then MSGVAL of the base object is cleared after storage of a received frame in the base object without taking the setting of MOFGPRn.SEL into account.

#### Workaround

Take the FIFO base object out of the list segment of the FIFO slave objects, when using Single Data Transfer.

#### MultiCAN AI.045 OVIE Unexpected Interrupt

When a gateway source object or a receive FIFO base object with MOFCRn.OVIE set transmits a CAN frame, then after the transmission an unexpected interrupt is generated on the interrupt line as given by MOIPRm.RXINP of the message object referenced by m=MOFGPRn.CUR.

#### Workaround

Do not transmit any CAN message by receive FIFO base objects or gateway source objects with bit MOFCRn.OVIE set.

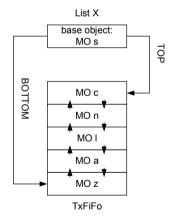

#### MultiCAN AI.046 Transmit FIFO base Object position

If a message object n is configured as transmit FIFO base object and is located in the list segment that is used for the FIFO storage container (defined by MOFGPRn.BOT and MOFGPRn.TOP) but not at the list position given by MOFGPRn.BOT, then the MultiCAN uses incorrect pointer values for this transmit FIFO.

#### Workaround

The transmit FIFO works properly when the transmit FIFO base object is either at the bottom position within the list segment of the FIFO (MOFGPRn.BOT=n) or outside of the list segment as described above.

#### MultiCAN\_TC.025 RXUPD behavior

When a CAN frame is stored in a message object, either directly from the CAN node or indirectly via receive FIFO or from a gateway source object, then bit MOCTR.RXUPD is set in the message object before the storage process and is automatically cleared after the storage process.

#### Problem description

When a standard message object (MOFCR.MMC) receives a CAN frame from a CAN node, then it processes its own RXUPD as described above (correct).

In addition to that, it also sets and clears bit RXUPD in the message object referenced by pointer MOFGPR.CUR (wrong behavior).

#### Workaround

The "foreign" RXUPD pulse can be avoided by initializing MOFGPR.CUR with the message number of the object itself instead of another object (which would be

message object 0 by default, because MOFGPR.CUR points to message object 0 after reset initialization of MultiCAN).

#### MultiCAN TC.026 MultiCAN Timestamp Function

The timestamp functionality does not work correctly.

#### Workaround

Do not use timestamp.

#### MultiCAN\_TC.027 MultiCAN Tx Filter Data Remote

Message objects of priority class 2 (MOAR. PRI = 2) are transmitted in the order as given by the CAN arbitration rules. This implies that for 2 message objects which have the same CAN identifier, but different DIR bit, the one with DIR = 1 (send data frame) shall be transmitted before the message object with DIR = 0, which sends a remote frame. The transmit filtering logic of the MultiCAN leads to a reverse order, i.e the remote frame is transmitted first. Message objects with different identifiers are handled correctly.

#### Workaround

None.

#### MultiCAN\_TC.028 SDT behavior

#### Correct behavior

Standard message objects:

MultiCAN clears bit MOCTR.MSGVAL after the successful reception/transmission of a CAN frame if bit MOFCR.SDT is set.

Transmit Fifo slave object:

MultiCAN clears bit MOCTR.MSGVAL after the successful reception/transmission of a CAN frame if bit MOFCR.SDT is set. After a

transmission, MultiCAN also looks at the respective transmit FIFO base object and clears bit MSGVAL in the base object if bit SDT is set in the base object and pointer MOFGPR.CUR points to MOFGPR.SEL (after the pointer update).

Gateway Destination/Fifo slave object:

MultiCAN clears bit MOCTR.MSGVAL after the storage of a CAN frame into the object (gateway/FIFO action) or after the successful transmission of a CAN frame if bit MOFCR.SDT is set. After a reception, MultiCAN also looks at the respective FIFO base/Gateway source object and clears bit MSGVAL in the base object if bit SDT is set in the base object and pointer MOFGPR.CUR points to MOFGPR.SEL (after the pointer update).

#### Problem description

Standard message objects:

After the successful transmission/reception of a CAN frame, MultiCAN also looks at message object given by MOFGPR.CUR. If bit SDT is set in the referenced message object, then bit MSGVAL is cleared in the message object CUR is pointing to.

Transmit FIFO slave object:

Same wrong behaviour as for standard message object. As for transmit FIFO slave objects CUR always points to the base object, the whole transmit FIFO is set invalid after the transmission of the first element instead after the base object CUR pointer has reached the predefined SEL limit value.

Gateway Destination/Fifo slave object:

Correct operation of the SDT feature.

#### Workaround

Standard message object:

Set pointer MOFGPR.CUR to the message number of the object itself.

Transmit FIFO:

Do not set bit MOFCR.SDT in the transmit FIFO base object. Then SDT works correctly with the slaves, but the FIFO deactivation feature by CUR reaching a predefined limit SEL is lost.

## MultiCAN\_TC.029 Tx FIFO overflow interrupt not generated

### Specified behaviour

After the successful transmission of a Tx FIFO element, a Tx overflow interrupt is generated if the FIFO base object fulfils these conditions:

- Bit MOFCR.OVIE=1, AND

- MOFGPR.CUR becomes equal to MOFGPR.SEL

### Real behaviour

A Tx FIFO overflow interrupt will not be generated after the transmission of the Tx FIFO base object.

### Workaround

If Tx FIFO overflow interrupt needed, take the FIFO base object out of the circular list of the Tx message objects. That is to say, just use the FIFO base object for FIFO control, but not to store a Tx message.

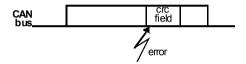

# <u>MultiCAN\_TC.030</u> Wrong transmit order when CAN error at start of CRC transmission

The priority order defined by acceptance filtering, specified in the message objects, define the sequential order in which these messages are sent on the CAN bus. If an error occurs on the CAN bus, the transmissions are delayed due to the destruction of the message on the bus, but the transmission order is kept. However, if a CAN error occurs when starting to transmit the CRC field, the arbitration order for the corresponding CAN node is disturbed, because the faulty message is not retransmitted directly, but after the next transmission of the CAN node.

Figure 3

## Workaround

None.

# <u>MultiCAN\_TC.031</u> List Object Error wrongly triggered

If the first list object in a list belonging to an active CAN node is deallocated from that list position during transmit/receive acceptance filtering (happening during message transfer on the bus), then a "list object" error may occur ( $NSRx.LOE=1_B$ ), which will cause that effectively no acceptance filtering is performed for this message by the affected CAN node.

As a result:

• for the affected CAN node, the CAN message during which the error occurs will not be stored in a message object. This means that although the message is acknowledged on the CAN bus, its content will be ignored.

- the message handling of an ongoing transmission is not disturbed, but the transmission of the subsequent message will be delayed, because transmit acceptance filtering has to be started again.

- message objects with pending transmit request might not be transmitted at all due to failed transmit acceptance filtering.

### Workaround

EITHER:

- Avoid deallocation of the first element on active CAN nodes. Dynamic reallocations on message objects behind the first element are allowed, OR

- Avoid list operations on a running node. Only perform list operations, if CAN node is not in use (e.g. when NCRX.INIT=1<sub>B</sub>)

## MultiCAN\_TC.032 MSGVAL wrongly cleared in SDT mode

When Single Data Transfer Mode is enabled ( $MOFCRn.SDT=1_B$ ), the bit MOCTRn.MSGVAL is cleared after the reception of a CAN frame, no matter if it is a data frame or a remote frame.

In case of a remote frame reception and with MOFCR.FRREN =  $0_B$ , the answer to the remote frame (data frame) is transmitted despite clearing of MOCTRn.MSGVAL (incorrect behaviour). If, however, the answer (data frame) does not win transmit acceptance filtering or fails on the CAN bus, then no further transmission attempt is made due to cleared MSGVAL (correct behaviour).

### Workaround

To avoid a single trial of a remote answer in this case, set MOFCR.FRREN =

1<sub>B</sub> and MOFGPR.CUR = this object.

## MultiCAN\_TC.035 Different bit timing modes

Bit timing modes ( $NFCRx.CFMOD=10_B$ ) do not conform to the specification.

When the modes  $001_B-100_B$  are set in register NFCRx.CFSEL, the actual configured mode and behaviour is different than expected.

| Table 9                                                 |                                                     |                                                                                                                                                                                                                          |  |  |

|---------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit timing mode<br>(NFCR.CFSEL)<br>according to<br>spec | Value to be written<br>to NFCR.CFSEL<br>instead     | Measurement                                                                                                                                                                                                              |  |  |

| 001 <sub>B</sub>                                        | Mode is missing (not<br>implemented) in<br>MultiCAN | Whenever a recessive edge<br>(transition from 0 to 1) is monitored<br>on the receive input the time<br>(measured in clock cycles)<br>between this edge and the most<br>recent dominant edge is stored in<br>CFC.         |  |  |

| 010 <sub>B</sub>                                        | 011 <sub>B</sub>                                    | Whenever a dominant edge is<br>received as a result of a<br>transmitted dominant edge the<br>time (clock cycles) between both<br>edges is stored in CFC.                                                                 |  |  |

| 011 <sub>B</sub>                                        | 100 <sub>B</sub>                                    | Whenever a recessive edge is<br>received as a result of a<br>transmitted recessive edge the<br>time (clock cycles) between both<br>edges is stored in CFC.                                                               |  |  |

| 100 <sub>B</sub>                                        | 001 <sub>B</sub>                                    | Whenever a dominant edge that<br>qualifies for synchronization is<br>monitored on the receive input the<br>time (measured in clock cycles)<br>between this edge and the most<br>recent sample point is stored in<br>CFC. |  |  |

# Workaround

None.

### MultiCAN\_TC.037 Clear MSGVAL

Correct behaviour:

When MSGVAL is cleared for a message object in any list, then this should not affect the other message objects in any way.

Message reception (wrong behaviour):

Assume that a received CAN message is about to be stored in a message object A, which can be a standard message object, FIFO base, FIFO slave, gateway source or gateway destination object.

If during of the storage action the user clears MOCTR.MSGVAL of message object B in any list, then the MultiCAN module may wrongly interpret this temporarily also as a clearing of MSGVAL of message object A. The result of this is that the message is not stored in message object A and is lost. Also no status update is performed on message object A (setting of NEWDAT, MSGLST, RXPND) and no message object receive interrupt is generated. Clearing of MOCTR.MSGVAL of message object B is performed correctly.

Message transmission (wrong behaviour):

Assume that MultiCAN is about to copy the message content of a message object A into the internal transmit buffer of the CAN node for transmission.

If during of the copy action the user clears MOCTR.MSGVAL of message object B in any list, then the MultiCAN module may wrongly interpret this also as a clearing of MSGVAL of message object A. The result of this is that the copy action for message A is not performed, bit NEWDAT is not cleared and no transmission takes place (clearing MOCTR.MSGVAL of message object B is performed correctly). In case of idle CAN bus and the user does not actively set the transmit request of any message object, this may lead to not transmitting any further message object, even if they have a valid transmit request set.

Single data transfer feature:

When the MultiCAN module clears MSGVAL as a result of a single data transfer (MOFCR.SDT = 1 in the message object), then the problem does not occur. The problem only occurs if MSGVAL of a message object is cleared via CPU.

### Workaround

Do not clear MOCTR.MSGVAL of any message object during CAN operation. Use bits MOCTR.RXEN, MOCTR.TXEN0 instead to disable/reenable reception and transmission of message objects.

# MultiCAN\_TC.038 Cancel TXRQ

When the transmit request of a message object that has won transmit acceptance filtering is cancelled (by clearing MSGVAL, TXRQ, TXEN0 or TXEN1), the CAN bus is idle and no writes to MOCTR of any message object are performed, then MultiCAN does not start the transmission even if there are message objects with valid transmit request pending.

### Workaround

To avoid that the CAN node ignores the transmission:

take a dummy message object, that is not allocated to any CAN node.

Whenever a transmit request is cleared, set TXRQ of the dummy message object thereafter. This retriggers the transmit acceptance filtering process.

or:

• whenever a transmit request is cleared, set one of the bits TXRQ, TXEN0 or TXEN1, which is already set, again in the message object for which the transmit request is cleared or in any other message object. This retriggers the transmit acceptance filtering process.

## OCDS\_X.003 Peripheral Debug Mode Settings cleared by Reset

The behavior (run/stop) of the peripheral modules in debug mode is defined in bitfield SUMCFG in the KSCCFG registers. The intended behavior is, that after an application reset has occurred during a debug session, a peripheral reenters the mode defined for debug mode.

For some peripherals, the debug mode setting in SUMCFG is erroneously set to normal mode upon any reset (instead upon a debug reset only). It remains in this state until SUMCFG is written by software or the debug system.

Some peripherals will **not** re-enter the state defined for debug mode after an application reset:

**GPT12, CAPCOM2, and MultiCAN** will resume normal operation like after reset, i.e. they are inactive until they are initialized by software.

In case the **RTC** has been running before entry into debug mode, and it was configured in SUMCFG to stop in debug mode, it will resume operation as before entry into debug mode instead.

All other peripheral modules, i.e. ADC0, ADC1, CC60...CC63, USIC0...USIC2, will correctly re-enter the state defined for debug mode after an application reset in debug mode.

For **Flash** and **CPU**, bitfield SUMCFG must be configured to normal mode anyway, since they are required for debugging.

### Workaround

None.

# POWER\_X.003 External Supply of Digital Core Supply Voltage V<sub>DDI</sub>

The digital core supply voltage  $V_{DDI}$  must not be supplied externally. The device may only be supplied by the on-chip voltage regulators, which is achieved by connecting pin TRef to  $V_{DDPB}$ .

### Workaround

None

## <u>POWER\_X.005</u> Start-up of DMP\_1 at low temperature

The start-up delay of the core power domain DMP\_1 upon power-up or a Power-on Reset (via pin PORST) increases with decreasing temperature. At temperatures below room temperature, the delay may increase by up to ~13 ms compared to temperatures above room temperature.

This increased delay does not occur for transitions between Power States.

### Workaround

None.

# RESET\_X.002 Startup Mode Selection is not Valid in SCU\_STSTAT.HWCFG

Reading from SCU\_STSTAT.HWCFG-bitfield returns all zeros instead of the information which startup mode has been entered after the last reset.

### Workaround

Read the initial value from VECSEG register to evaluate where from the user code is started:

- VECSEG[7:0] =  $00_{H}$  start from an off-chip memory, external startup mode

- VECSEG[7:0] =C0<sub>H</sub> start from on-chip flash, internal startup mode

- VECSEG[7:0]=E0<sub>H</sub> start from on-chip PSRAM, bootstrap loader mode (UART, CAN or SSC)

## RESET X.003 P2. [2:0] and P10. [12:0] Switch to Input

During a User Reset the port pins P2. [2:0] and P10. [12:0] are switch to input. The user has to check his application to this behaviour.

### Workaround

None.

## <u>RTC\_X.003</u> Interrupt Generation in Asynchronous Mode

Asynchronous Mode must be selected (bit RTCCM =  $1_B$  in register RTCCLKCON) whenever the system clock is less than 4 times faster than the RTC count input clock ( $f_{SYS} < f_{RTC} \times 4$ ). While in Asynchronous Mode, generation of the RTC interrupt via flag RTCIR in register RTC IC does not work correctly.

### Workaround 1

Select the system clock such that it is at least 4 times faster than the RTC count input clock ( $f_{SYS} \ge f_{RTC} \times 4$ ) and operate the RTC in Synchronous Mode.

### Workaround 2

Before switching from Synchronous to Asynchronous Mode, clear the individual interrupt enable bits (CNTxIE, T14IE) in register RTC\_ISNC. After returning to Synchronous Mode, set the individual interrupt enable bits as required by the application. Then flag RTCIR will get set if at least one of the individual interrupt requests (flags CNTxIR, T14IR) was pending.

# USIC\_AI.003 TCSRL.SOF and TCSRL.EOF not cleared after a transmission is started

The Start of Frame (SOF) and End of Frame (EOF) bit in the Transmit Control/Status Register (TCSRL) will not be cleared by hardware when the data is transfered from the transmit buffers (TBUFx) to the transmit shift register, i.e. the transmission of a new word starts.

### Workaround

Clear TCSRL.SOF and TCSRL.EOF by software.

### <u>USIC AI.004</u> Receive shifter baudrate limitation

If the frame length of <code>SCTRH.FLE</code> does not match the frame length of the master, then the baudrate of the SSC slave receiver is limited to  $f_{sys}/2$  instead of  $f_{svs}$ .

### Workaround

None.

**Errata Sheet**

**Detailed Errata Description**

# 6.2 Deviations from Electrical and Timing Specification

- none -

# 6.3 Application Hints

# CAPCOM12 X.H001 Enabling Single Event Operation

The single event operation mode of the CAPCOM1/2 unit eliminates the need for software to react after the first compare match when only one event is required within a certain time frame. The enable bit SEEy for a channel CCy is cleared by hardware after the compare event, thus disabling further events for this channel.

### One Channel in Single Event Operation

As the Single Event Enable registers CC1\_SEE, CC2\_SEE are not located in the bit-addressable SFR address range, they can only be modified by instructions operating on data type WORD. This is no problem when only one channel of a CAPCOM unit is used in single event mode.

### Two or more Channels in Single Event Operation

When two or more channels of a CAPCOM unit are independently operating in single event mode, usually an OR instruction is used to enable one or more compare events in register  $CCx\_SEE$ . In this case, the timing relation of the channels must be considered, otherwise the following typical problem may occur:

- In the Memory stage, software reads register CCx\_SEE with bit SEEy = 1<sub>B</sub> (event for channel CCy has not yet occurred)

- Meanwhile, event for CCy occurs, and bit SEEy is cleared to 0<sub>B</sub> by hardware

- In the Write-Back stage, software writes CCx\_SEE with bit SEEx = 1<sub>B</sub> (intended event for CCx enabled) and bit SEEy = 1<sub>B</sub>

In this case, another unintended event for channel CCy is enabled.

To avoid this effect, one of the following solutions - depending on the characteristics of the application - is recommended to enable further compare events for CAPCOM channels concurrently operating in single event mode:

• Modify register CCx\_SEE only when it is ensured that no compare event in single event mode can occur, i.e. when CCx\_SEE = 0x0000, or

- Modify register CCx\_SEE only when it is ensured that there is a sufficient time distance to the events of all channels operating in single event mode, such that none of the bits in CCx\_SEE can change in the meantime, or

- Use single event operation for one channel only (i.e. only one bit SEMz may be = 1<sub>B</sub>), and/or

- Use one of the standard compare modes, and emulate single event operation for a channel CCs by disabling further compare events in bit field MODs (in register CCx\_My) in the corresponding interrupt service routine. Writing to register CCx\_My is uncritical, as this register is not modified by hardware.

# CC6\_X.H001 Modifications of Bit MODEN in Register CCU6x\_KSCFG

For each module, setting bit MODEN = 0 immediately switches off the module clock. Care must be taken that the module clock is only switched off when the module is in a defined state (e.g. stop mode) in order to avoid undesired effects in an application.

In addition, for a CCU6 module in particular, if bit MODEN is changed to 0 while the internal functional blocks have not reached their defined stop conditions, and later MODEN is set to 1 and the mode is not set to run mode, this leads to a lock situation where the module clock is not switched on again.

## INT\_X.H002 Increased Latency for Hardware Traps

When a condition for a HW trap occurs (i.e. one of the bits in register TFR is set to  $1_B$ ), the next valid instruction that reaches the Memory stage is replaced with the corresponding TRAP instruction. In some special situations described in the following, a valid instruction may not immediately be available at the Memory stage, resulting in an increased delay in the reaction to the trap request:

When the CPU is in break mode, e.g. single-stepping over such instructions as SBRK or BSET TFR.x (where x = one of the trap flags in register TFR)

will have no (immediate) effect until the next instruction enters the Memory stage of the pipeline (i.e. until a further single-step is performed).

2. When the pipeline is running empty due to (mispredicted) branches and a relatively slow program memory (with many wait states), servicing of the trap is delayed by the time for the next access to this program memory, even if vector table and trap handler are located in a faster memory. However, the situation when the pipeline/prefetcher are completely empty is quite rare due to the advanced prefetch mechanism of the C166S V2 core.

# JTAG\_X.H001 JTAG Pin Routing

In the current device, the pins connected to the JTAG interface can be selected by software (write to register DBGPRR). After a reset, the JTAG interface is connected to position A (see **Table 10**). If connected to these pins, the debugger will work without any restrictions.