User's Manual, V 0.2, Jan 2005

# XC866 8-Bit Single Chip Microcontroller

Microcontrollers

Never stop thinking.

Edition 2005-01 Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany © Infineon Technologies AG 2005. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

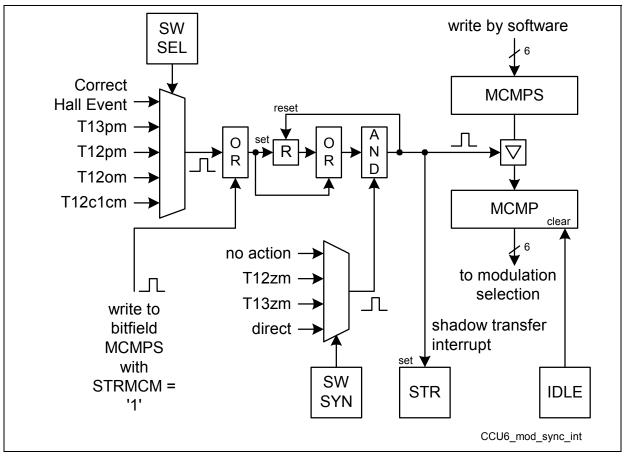

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# XC866 8-Bit Single Chip Microcontroller

# Microcontrollers

Never stop thinking.

# XC866

#### Revision History: 2005-01

Previous Version:

# We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: mcdocu.comments@infineon.com

| Table of ( | Contents<br>Introduction                          | Page<br>. 1-1 |

|------------|---------------------------------------------------|---------------|

| 1.1        | Feature Summary                                   | . 1-3         |

| 1.2        | Pin Configuration                                 |               |

| 1.3        | Pin Definitions and Functions                     | . 1-6         |

| 1.4        | Textual Convention                                | 1-12          |

| 1.5        | Reserved, Undefined and Unimplemented Terminology | 1-13          |

| 1.6        | Acronyms                                          | 1-14          |

| 2          | Processor Architecture                            | . 2-1         |

| 2.1        | Functional Description                            | . 2-2         |

| 2.2        | CPU Register Description                          | . 2-4         |

| 2.2.1      | Stack Pointer (SP)                                |               |

| 2.2.2      | Data Pointer (DPTR)                               | . 2-4         |

| 2.2.3      | Accumulator (ACC)                                 | . 2-4         |

| 2.2.4      | B Register                                        | . 2-4         |

| 2.2.5      | Program Status Word                               |               |

| 2.2.6      | Extended Operation Register (EO)                  | . 2-6         |

| 2.2.7      | Power Control Register (PCON)                     |               |

| 2.3        | Instruction Timing                                |               |

| 3          | Memory Organization                               | . 3-1         |

| 3.1        | Program Memory                                    | . 3-3         |

| 3.2        | Data Memory                                       | . 3-3         |

| 3.2.1      | Internal Data Memory                              | . 3-3         |

| 3.2.2      | External Data Memory                              | . 3-3         |

| 3.3        | Special Function Registers                        | . 3-4         |

| 3.3.1      | Address Extension by Mapping                      | . 3-4         |

| 3.3.2      | Address Extension by Paging                       |               |

| 3.3.3      | Bit-Addressing                                    | . 3-9         |

| 3.3.4      | System Control Registers                          | 3-10          |

| 3.3.4.1    | Bit Protection Scheme                             | 3-12          |

| 3.3.5      | XC866 Register Overview                           | 3-13          |

| 3.3.5.1    | CPU Registers                                     | 3-13          |

| 3.3.5.2    | System Control Registers                          | 3-14          |

| 3.3.5.3    | WDT Registers                                     | 3-16          |

| 3.3.5.4    | Port Registers                                    | 3-16          |

| 3.3.5.5    | ADC Registers                                     | 3-17          |

| 3.3.5.6    | Timer 2 Registers                                 | 3-20          |

| 3.3.5.7    | CCU6 Registers                                    | 3-20          |

| 3.3.5.8    | SSC Registers                                     | 3-24          |

| 3.3.5.9    | OCDS Registers                                    | 3-25          |

| 3.4        | Boot ROM Operating Mode                           | 3-26          |

| 3.4.1      | User Mode                                         | 3-26          |

| Table of (      | Contents                          | Page  |

|-----------------|-----------------------------------|-------|

| 3.4.2           | BootStrap Loader Mode             | 3-27  |

| 3.4.3           | OCDS Mode                         | 3-27  |

| 4               | Flach Momony                      | . 4-1 |

| <b>4</b><br>4.1 | Flash Memory                      |       |

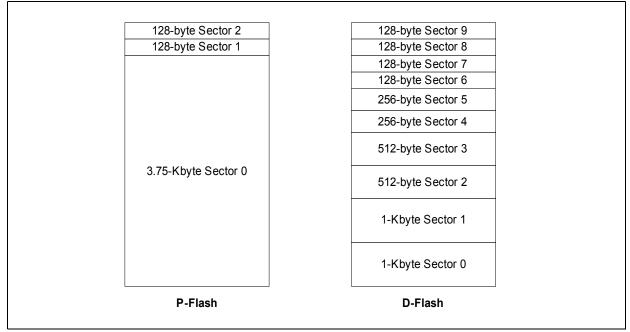

| 4.1             | Flash Memory Map                  |       |

| 4.2<br>4.3      | Flash Bank Sectorization          | -     |

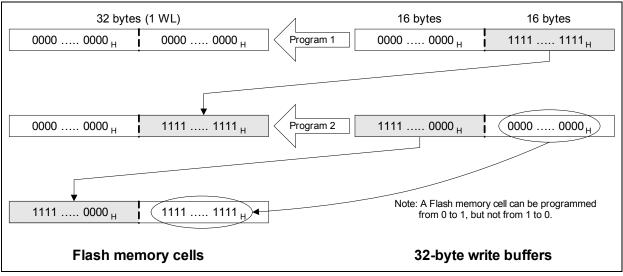

| -               | Wordline Address                  | -     |

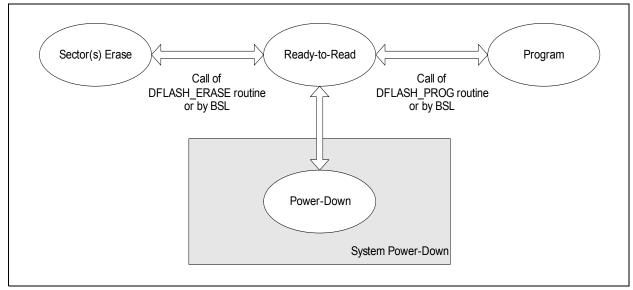

| 4.4             | Operating Modes                   |       |

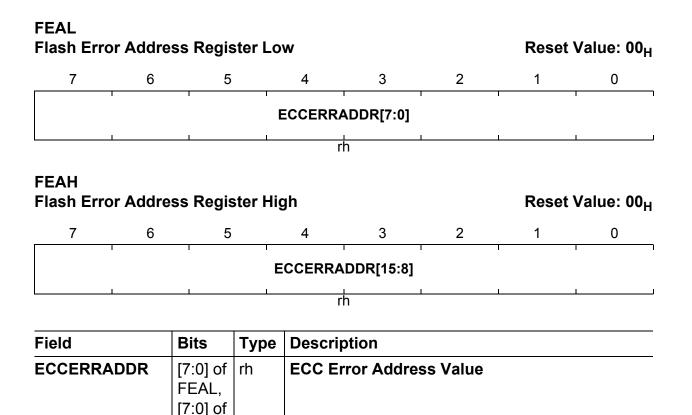

| 4.5             | Error Detection and Correction    |       |

| 4.6             |                                   |       |

| 4.7             | In-Application Programming        |       |

| 4.7.1           | D-Flash Programming               |       |

| 4.7.2           | D-Flash Erasing                   | 4-13  |

| 5               | Interrupt System                  | . 5-1 |

| 5.1             | Non-maskable Interrupt            |       |

| 5.2             | Maskable Interrupts               |       |

| 5.2.1           | Internal Interrupts               |       |

| 5.2.2           | External Interrupts               |       |

| 5.2.3           | Extended Interrupts               |       |

| 5.3             | Interrupt Source and Vector       | -     |

| 5.4             | Interrupt Register Description    |       |

| 5.4.1           | Interrupt Enable Registers        |       |

| 5.4.2           | Interrupt Request Flags           |       |

| 5.4.3           | Interrupt Priority Registers      |       |

| 5.4.4           |                                   |       |

| 5.4.5           | Interrupt Request Flags           |       |

| 5.5             | Interrupt Handling                |       |

| 5.6             | Interrupt Response Time           |       |

|                 |                                   |       |

| 6               | Parallel Ports                    |       |

| 6.1             | General Port Operation            | . 6-2 |

| 6.1.1           | General Register Description      | . 6-5 |

| 6.1.1.1         | Data Register                     | . 6-6 |

| 6.1.1.2         | Direction Register                | . 6-7 |

| 6.1.1.3         | Open Drain Control Register       | . 6-7 |

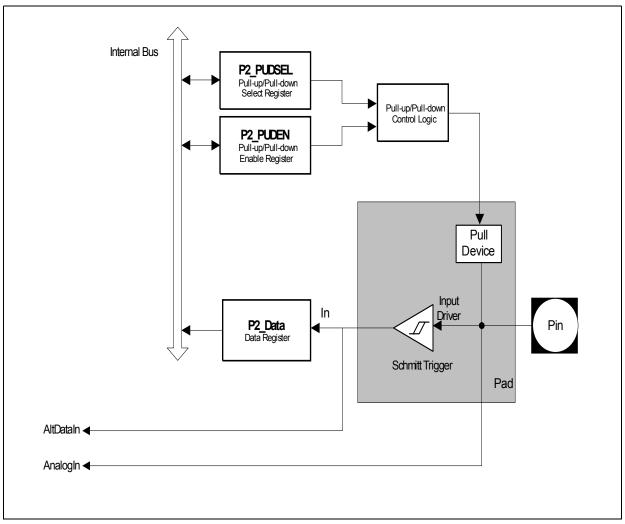

| 6.1.1.4         | Pull-Up/Pull-Down Device Register | . 6-8 |

| 6.1.1.5         | Alternate Input Functions         | 6-10  |

| 6.1.1.6         | Alternate Output Functions        |       |

| 6.2             | Register Map                      | 6-11  |

| 6.3             | Port 0                            | 6-14  |

| 6.3.1           | Functions                         | 6-14  |

| 6.3.2           | Register Description              | 6-16  |

| Table of ( | Contents Port 1                                     | <b>Page</b><br>6-19 |

|------------|-----------------------------------------------------|---------------------|

| 6.4.1      | Functions                                           |                     |

| 6.4.2      | Register Description                                | 6-21                |

| 6.5        | Port 2                                              | 6-24                |

| 6.5.1      | Functions                                           | 6-24                |

| 6.5.2      | Register Description                                | 6-26                |

| 6.6        | Port 3                                              | 6-28                |

| 6.6.1      | Functions                                           | 6-28                |

| 6.6.2      | Register Description                                | 6-31                |

| 7          | Power Supply, Reset and Clock Management            | . 7-1               |

| 7.1        | Power Supply System with Embedded Voltage Regulator |                     |

| 7.2        | Reset Control                                       |                     |

| 7.2.1      | Types of Reset                                      | . 7-3               |

| 7.2.1.1    | Power-On Reset                                      | . 7-3               |

| 7.2.1.2    | Hardware Reset                                      | . 7-4               |

| 7.2.1.3    | Watchdog Timer Reset                                | . 7-4               |

| 7.2.1.4    | Power-Down Wake-Up Reset                            | . 7-4               |

| 7.2.1.5    | Brownout Reset                                      | . 7-5               |

| 7.2.2      | Module Reset Behavior                               | . 7-6               |

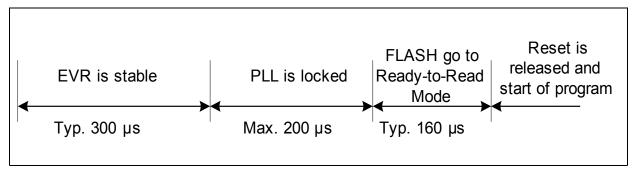

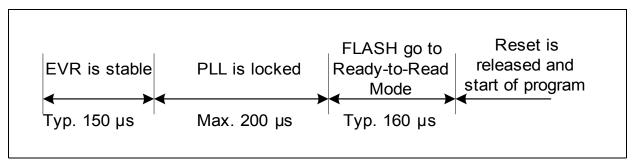

| 7.2.3      | Booting Scheme                                      |                     |

| 7.2.4      | Register Description                                |                     |

| 7.3        | Clock System                                        |                     |

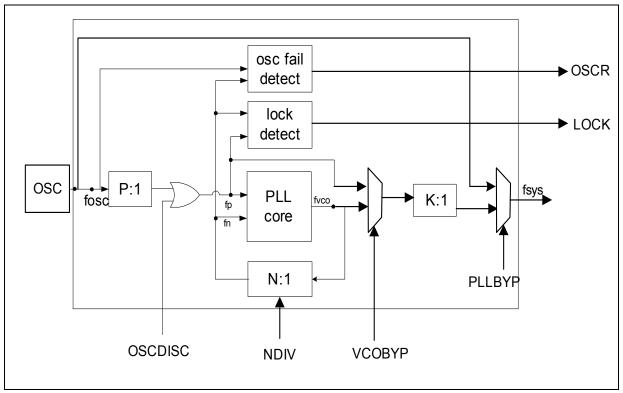

| 7.3.1      | Clock Generation Unit                               |                     |

| 7.3.1.1    | Functional Description                              |                     |

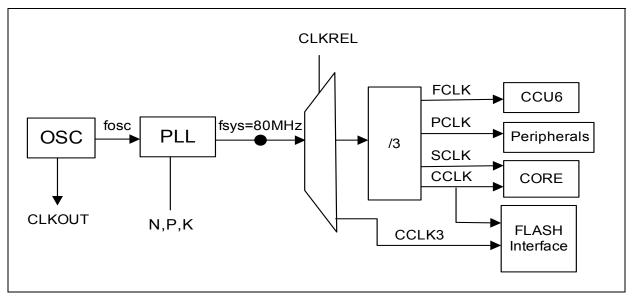

| 7.3.2      | Clock Source Control                                | 7-11                |

| 7.3.3      |                                                     | 7-13                |

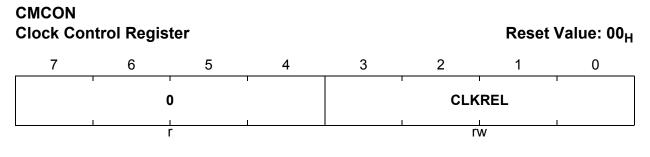

| 7.3.4      | Register Description                                | 7-14                |

| 8          | Power Saving Modes                                  | . 8-1               |

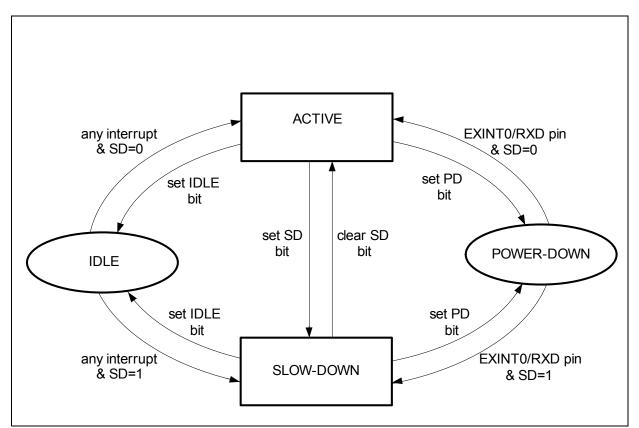

| 8.1        | Functional Description                              | . 02                |

| 8.1.1      | Idle Mode                                           |                     |

| 8.1.2      | Slow-Down Mode                                      |                     |

| 8.1.3      | Power-down Mode                                     |                     |

| 8.1.4      | Peripheral Clock Management                         |                     |

| 8.2        | Register Description                                | . 8-6               |

| 9          | Watchdog Timer                                      | . 9-1               |

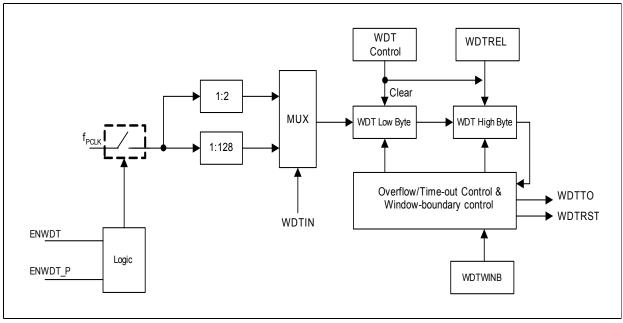

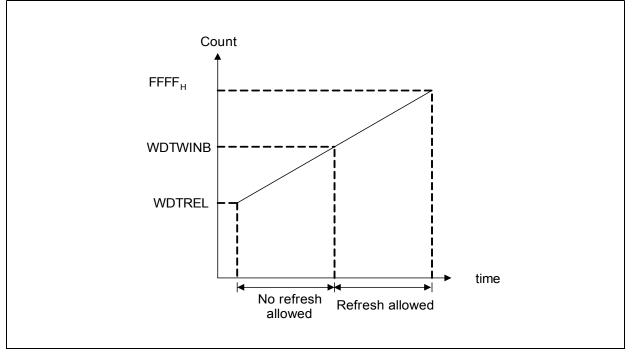

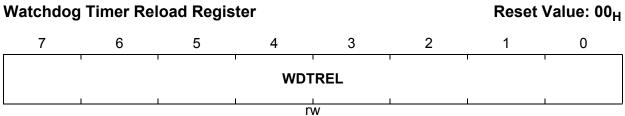

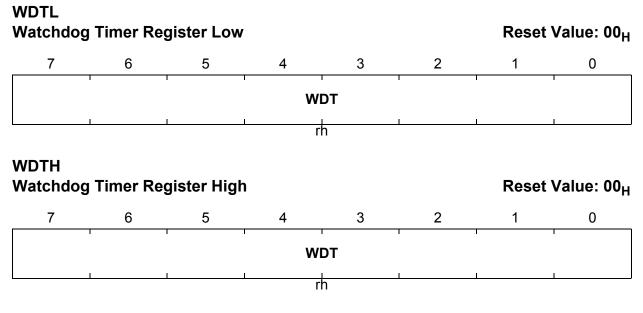

| 9.1        | Functional Description                              | . 9-2               |

| 9.2        | Register Map                                        | . 9-5               |

| 9.3        | Register Description                                | . 9-5               |

| 10         | Serial Interfaces                                   | 10-1                |

| 10.1       | UART                                                | 10-2                |

| Table of | Contents                                | Page  |

|----------|-----------------------------------------|-------|

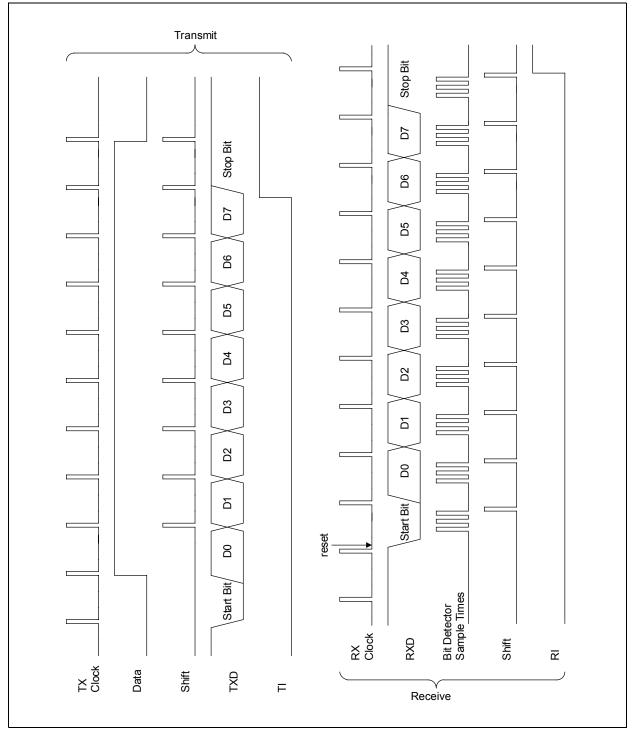

| 10.1.1   | UART Modes                              | 10-2  |

| 10.1.1.1 | Mode 1, 8-Bit UART, Variable Baud Rate  | 10-2  |

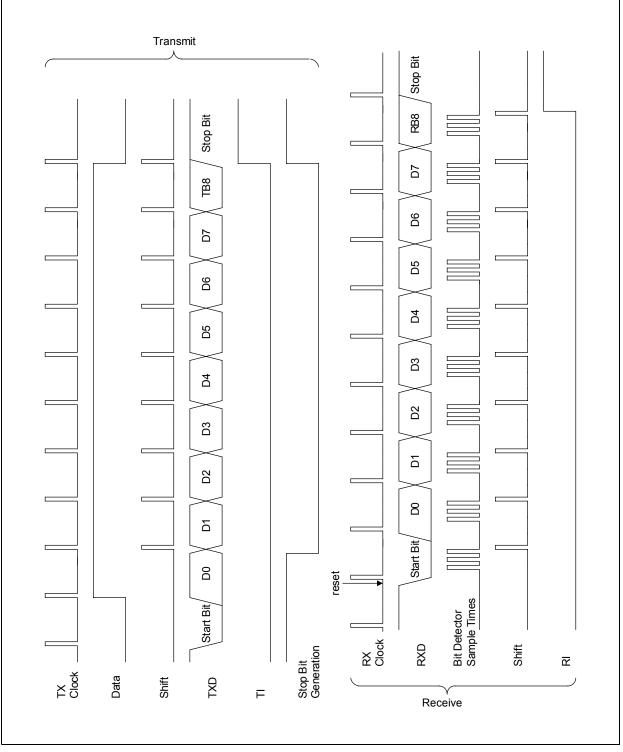

| 10.1.1.2 | Mode 2, 9-Bit UART, Fixed Baud Rate     | 10-5  |

| 10.1.1.3 | Mode 3, 9-Bit UART, Variable Baud Rate  | 10-5  |

| 10.1.2   | Multiprocessor Communication            | 10-7  |

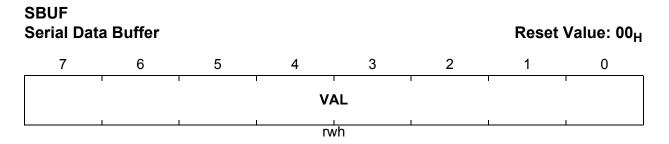

| 10.1.3   | Register Description                    | 10-7  |

| 10.1.4   | Baud Rate Generation                    | 10-9  |

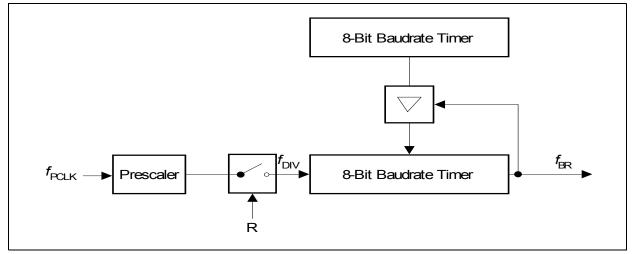

| 10.1.4.1 | Baud-rate Generator                     | 10-10 |

| 10.1.5   | Interfaces of UART                      | 10-13 |

| 10.2     | LIN                                     | 10-14 |

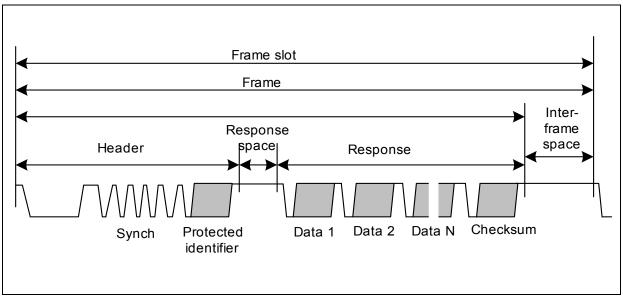

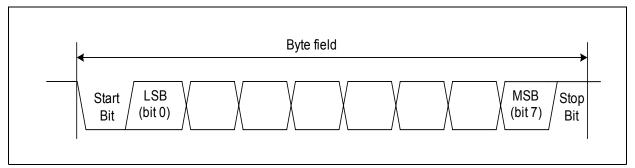

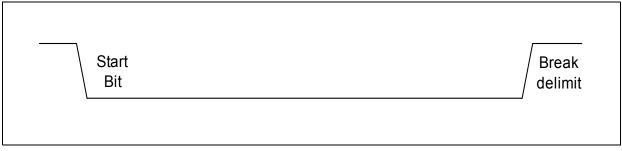

| 10.2.1   | LIN Protocol                            | 10-14 |

| 10.2.2   | LIN Header Transmission                 | 10-16 |

| 10.2.3   | Baud Rate Detection of LIN              | 10-17 |

| 10.3     | High-Speed Synchronous Serial Interface | 10-19 |

| 10.3.1   |                                         | 10-20 |

| 10.3.1.1 |                                         | 10-20 |

| 10.3.1.2 |                                         | 10-21 |

| 10.3.1.3 |                                         | 10-24 |

| 10.3.1.4 |                                         | 10-25 |

| 10.3.1.5 | Port Control                            | 10-25 |

| 10.3.1.6 | Baud Rate Generation                    | 10-26 |

| 10.3.1.7 | Error Detection Mechanisms              | 10-27 |

| 10.3.2   |                                         | 10-30 |

| 10.3.3   | •                                       | 10-31 |

| 10.3.4   |                                         | 10-32 |

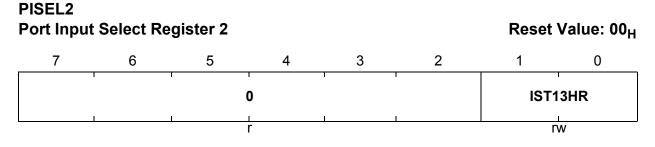

| 10.3.4.1 | Port Input Select Register              | 10-32 |

| 10.3.4.2 |                                         | 10-33 |

| 10.3.4.3 | Baud Rate Timer Reload Register         | 10-37 |

| 10.3.4.4 |                                         | 10-38 |

|          |                                         |       |

| 11       | Timers                                  | 11-1  |

| 11.1     | Timer 0 and Timer 1                     | 11-1  |

| 11.1.1   | Basic Timer Operations                  | 11-1  |

| 11.1.2   | Timer Modes                             | 11-2  |

| 11.1.2.1 | Mode 0                                  | 11-3  |

| 11.1.2.2 | Mode 1                                  | 11-4  |

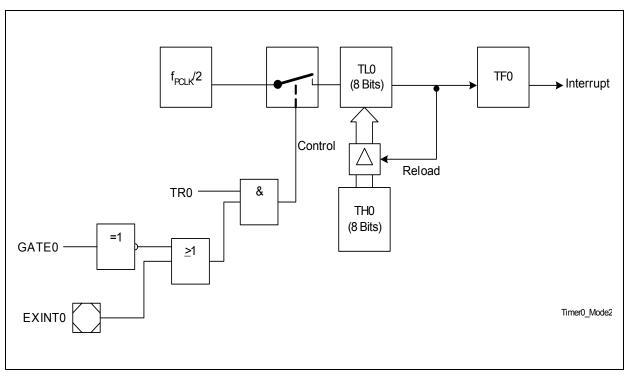

| 11.1.2.3 | Mode 2                                  | 11-5  |

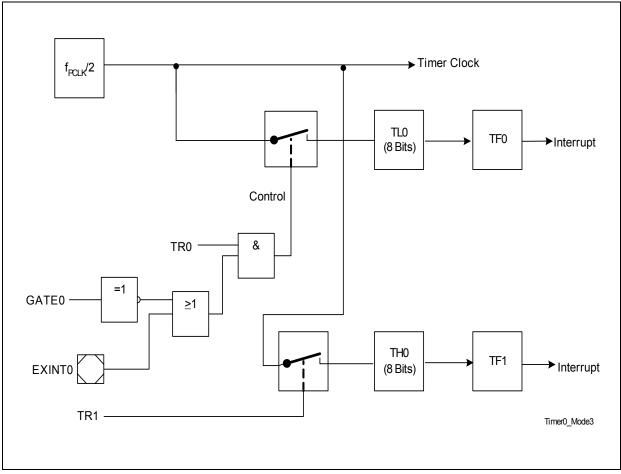

| 11.1.2.4 | Mode 3                                  | 11-6  |

| 11.1.3   | Register Map                            | 11-7  |

| 11.1.4   |                                         | 11-8  |

| 11.2     |                                         | 11-13 |

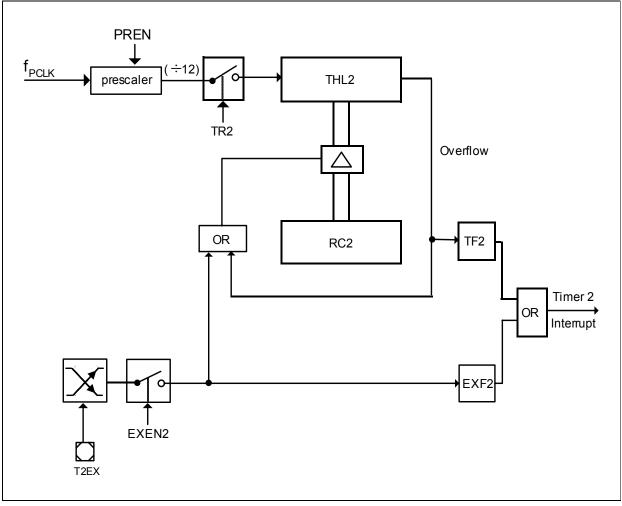

| 11.2.1   |                                         | 11-13 |

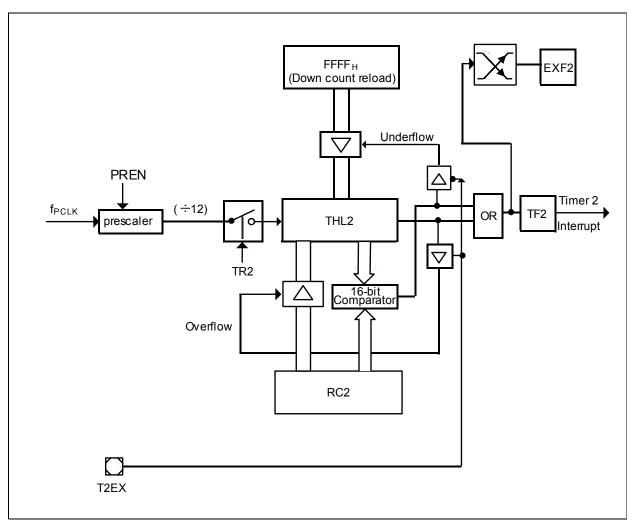

| 11.2.1.1 | Up/Down Count Disabled                  | 11-13 |

| Table of (11.2.1.2 |                                   | <b>Page</b><br>11-14 |

|--------------------|-----------------------------------|----------------------|

| 11.2.1.2           | Up/Down Count Enabled             | 11-14                |

| 11.2.2             | Capture Mode                      | 11-10                |

| 11.2.3             | Register Map                      |                      |

| 11.2.4             | Register Description              | 11-17                |

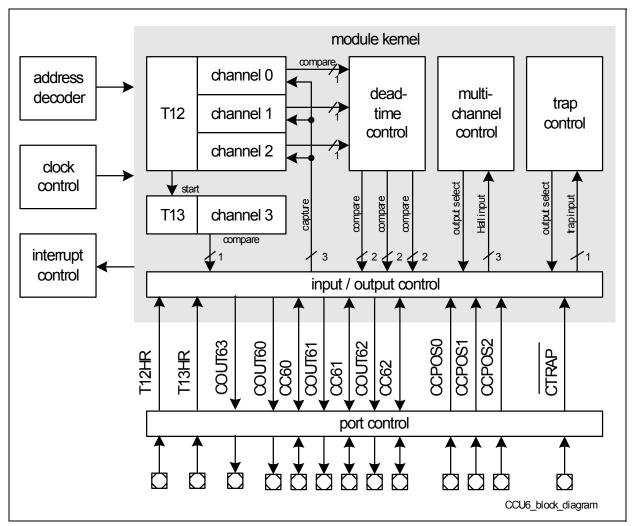

| 12                 | Capture/Compare Unit 6            | 12-1                 |

| 12.1               | Functional Description            | 12-3                 |

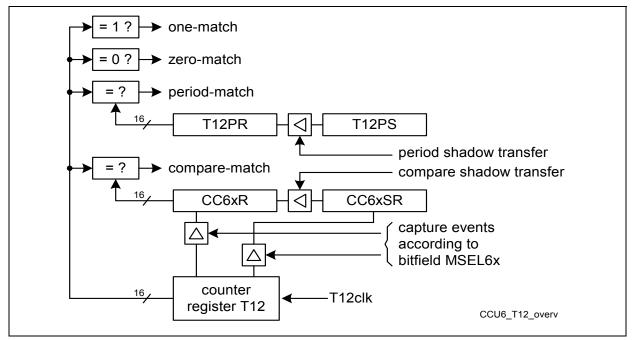

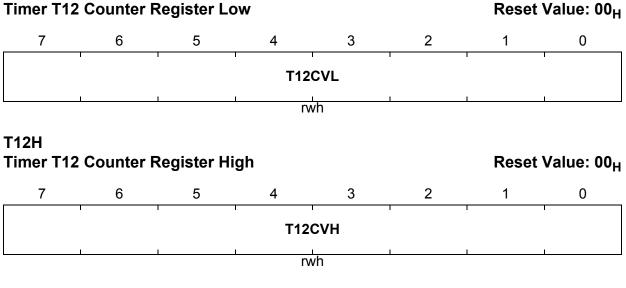

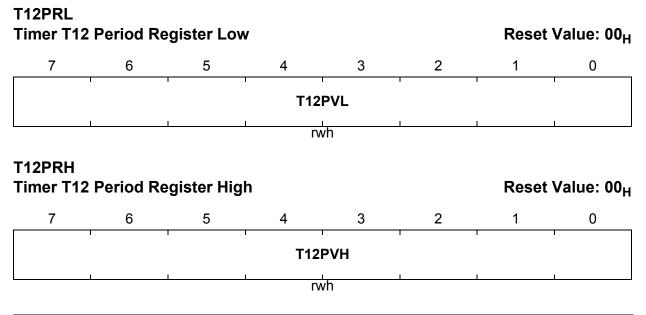

| 12.1.1             | Timer T12                         | 12-3                 |

| 12.1.1.1           | Timer Configuration               | 12-4                 |

| 12.1.1.2           | Counting Rules                    | 12-4                 |

| 12.1.1.3           | Switching Rules                   | 12-4                 |

| 12.1.1.4           | Compare Mode of T12               | 12-6                 |

| 12.1.1.5           | Duty Cycle of 0% and 100%         | 12-7                 |

| 12.1.1.6           | Dead-time Generation              |                      |

| 12.1.1.7           | Capture Mode                      |                      |

| 12.1.1.8           | Single-Shot Mode                  | 12-9                 |

| 12.1.1.9           | Hysteresis-Like Control Mode      | 12-10                |

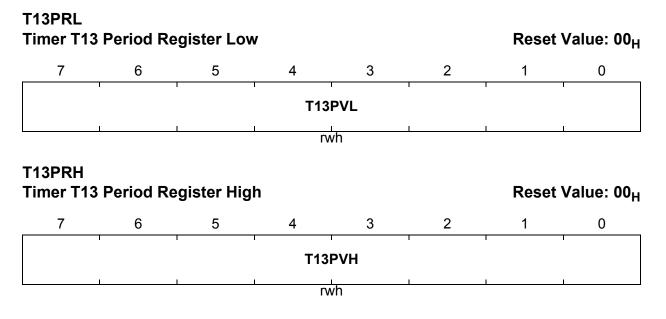

| 12.1.2             | Timer T13                         | 12-11                |

| 12.1.2.1           | Timer Configuration               | 12-11                |

| 12.1.2.2           | Compare Mode                      | 12-12                |

| 12.1.2.3           | Single-Shot Mode                  | 12-12                |

| 12.1.2.4           | Synchronization of T13 to T12     | 12-13                |

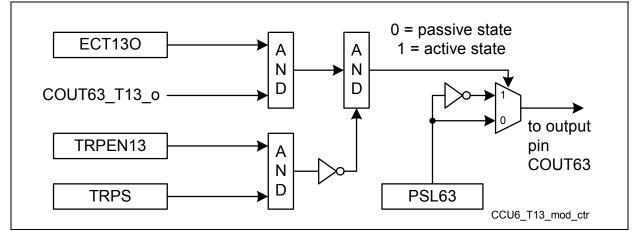

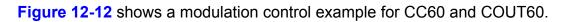

| 12.1.3             | Modulation Control                | 12-13                |

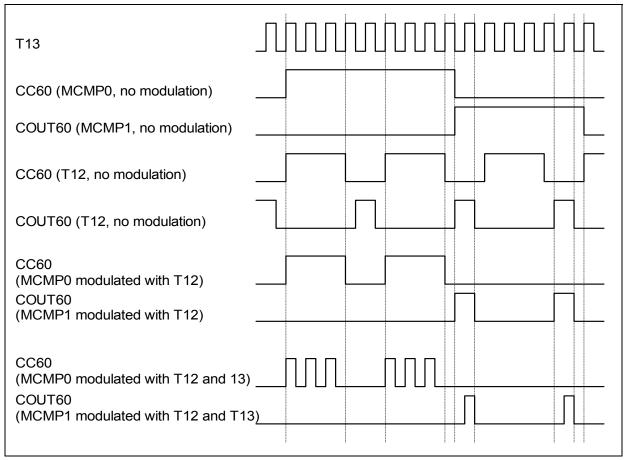

| 12.1.4             | Trap Handling                     | 12-16                |

| 12.1.5             | Multi-Channel Mode                | 12-17                |

| 12.1.6             | Hall Sensor Mode                  | 12-19                |

| 12.1.6.1           | Sampling of the Hall Pattern      | 12-19                |

| 12.1.6.2           | Brushless-DC Control              | 12-20                |

| 12.1.7             | Interrupt Generation              | 12-23                |

| 12.1.8             | Port Connection                   | 12-23                |

| 12.2               | Register Map                      | 12-26                |

| 12.3               | Register Description              | 12-29                |

| 12.3.1             | System Registers                  | 12-31                |

| 12.3.1.1           | Port Input Selection              | 12-31                |

| 12.3.2             | Timer T12 – Related Registers     | 12-35                |

| 12.3.3             | Timer T13 – Related Registers     | 12-41                |

| 12.3.4             | Capture/Compare Control Registers | 12-45                |

| 12.3.5             | Modulation Control Registers      | 12-57                |

| 12.3.5.1           | Global Module Control             | 12-57                |

| 12.3.5.2           | Multi-Channel Control             | 12-65                |

| 12.3.6             | Interrupt Control Registers       | 12-77                |

|                    |                                   |                      |

| 13                 | Analog-to-Digital Converter       | 13-1                 |

| Table of | Contents                           | Page  |

|----------|------------------------------------|-------|

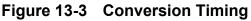

| 13.1     | Structure Overview                 | 13-2  |

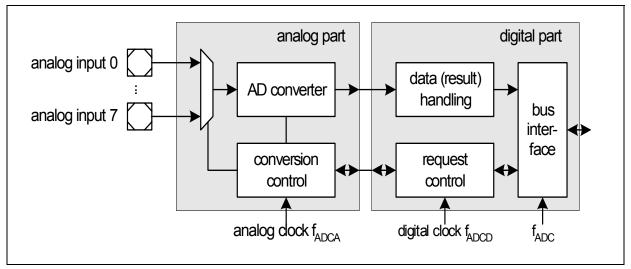

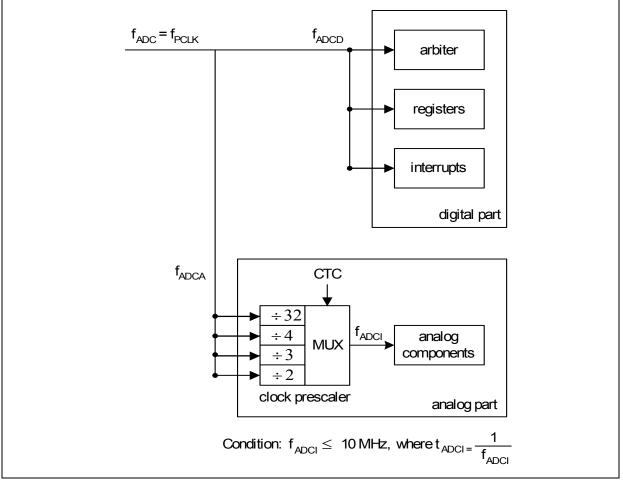

| 13.2     | Clocking Scheme                    | 13-3  |

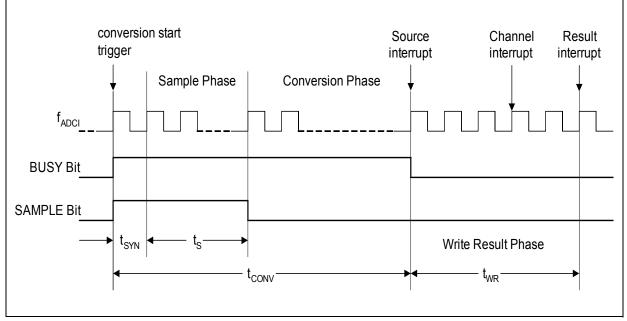

| 13.2.1   | Conversion Timing                  | 13-4  |

| 13.3     | Low Power Mode                     | 13-7  |

| 13.4     | Functional Description             | 13-8  |

| 13.4.1   | Request Source Arbiter             | 13-9  |

| 13.4.2   | Conversion Start Modes             | 13-10 |

| 13.4.3   | Channel Control                    | 13-10 |

| 13.4.4   | Sequential Request Source          | 13-11 |

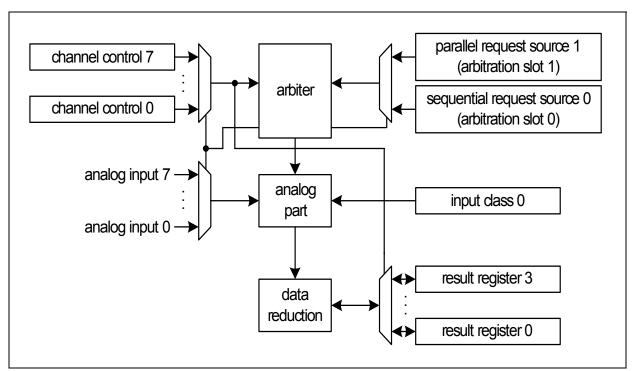

| 13.4.4.1 | Overview                           | 13-11 |

| 13.4.4.2 | Request Source Control             | 13-12 |

| 13.4.5   | Parallel Request Source            | 13-13 |

| 13.4.5.1 | Overview                           | 13-13 |

| 13.4.5.2 | Request Source Control             | 13-13 |

| 13.4.5.3 | External Trigger                   | 13-14 |

| 13.4.5.4 | Software Control                   | 13-14 |

| 13.4.5.5 | Autoscan                           | 13-15 |

| 13.4.6   | Wait-for-Read Mode                 | 13-15 |

| 13.4.7   | Result Generation                  | 13-16 |

| 13.4.7.1 | Overview                           | 13-16 |

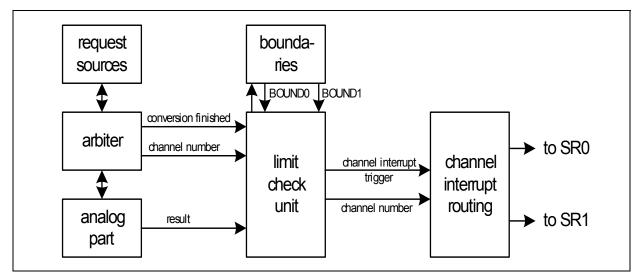

| 13.4.7.2 | Limit Checking                     | 13-17 |

| 13.4.7.3 | Data Reduction Filter              | 13-18 |

| 13.4.7.4 | Result FIFO Functionality          | 13-19 |

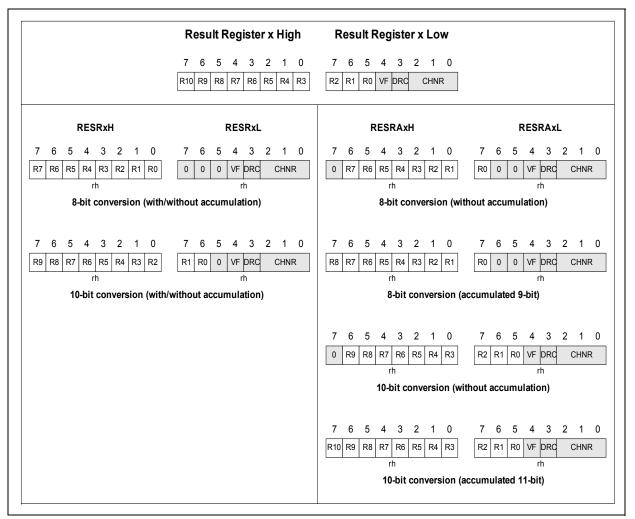

| 13.4.7.5 | Result Register View               | 13-19 |

| 13.4.8   |                                    | 13-21 |

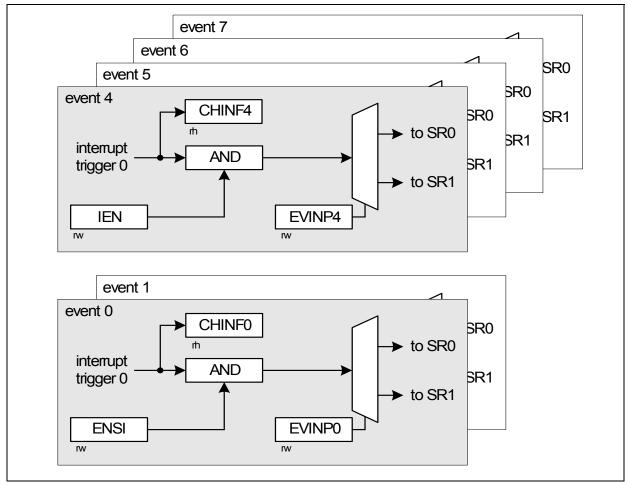

| 13.4.8.1 | Event Interrupts                   | 13-22 |

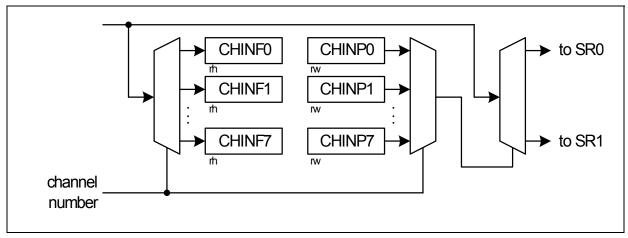

| 13.4.8.2 | Channel Interrupts                 | 13-23 |

| 13.4.9   | External Trigger Inputs            | 13-25 |

| 13.5     | ADC Module Initialization Sequence | 13-26 |

| 13.6     | Register Map                       | 13-28 |

| 13.7     | Register Description               | 13-31 |

| 13.7.1   | General Function Registers         | 13-31 |

| 13.7.2   | Priority and Arbitration Register  | 13-33 |

| 13.7.3   | External Trigger Control Register  | 13-35 |

| 13.7.4   | Channel Control Registers          | 13-36 |

| 13.7.5   | Input Class Register               | 13-37 |

| 13.7.6   | Sequential Source Registers        | 13-38 |

| 13.7.7   | Parallel Source Registers          | 13-44 |

| 13.7.8   | Result Registers                   | 13-48 |

| 13.7.9   | Interrupt Registers                | 13-52 |

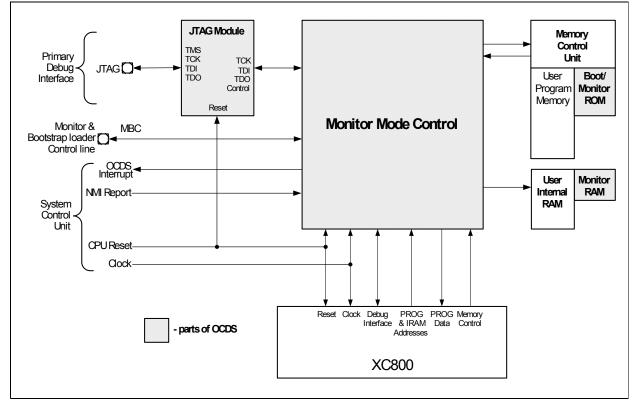

| 14       | On-Chip Debug Support              |       |

| 14.1     | Functional Description             | 14-2  |

| Table of ( | Contents<br>Debugging    | Page<br>14-3 |

|------------|--------------------------|--------------|

| 14.2.1     | Debug Events             |              |

| 14.2.1.1   | Hardware Breakpoints     |              |

| 14.2.1.2   | Software Breakpoints     | 14-5         |

| 14.2.1.3   | External Breaks          | 14-6         |

| 14.2.2     | Debug Actions            | 14-6         |

| 14.2.2.1   | Call the Monitor Program | 14-6         |

| 14.2.2.2   | Activate the MBC pin     | 14-6         |

| 14.3       | Register Description     | 14-7         |

| 14.3.1     | JTAG ID Register         | 14-9         |

| 15         | Index                    | 15-1         |

| 15.1       | Keyword Index            | 15-1         |

| 15.2       | Register Index           |              |

# 1 Introduction

The XC866 is a member of the high-performance XC800 family of 8-bit microcontrollers. It is based on the XC800 Core that is compatible with the industry standard 8051 processor. The XC866 features a great number of enhancements to enable new application technologies through its highly integrated on-chip components, such as on-chip oscillator or an integrated voltage regulator, allowing a single voltage supply of 3.0 to 5.5 V. In addition, the XC866 is equipped with either embedded Flash memory to offer high flexibility in development and ramp-up, or compatible ROM versions to provide cost-saving potential in high-volume production.

The multi-bank Flash architecture supports In-Application Programming (IAP), allowing user program to run from one bank, while programming or erasing another bank. In-System Programming (ISP) is available through the Boot ROM-based BootStrap Loader (BSL), enabling convenient programming and erasing of the embedded Flash via an external host (e.g., personal computer).

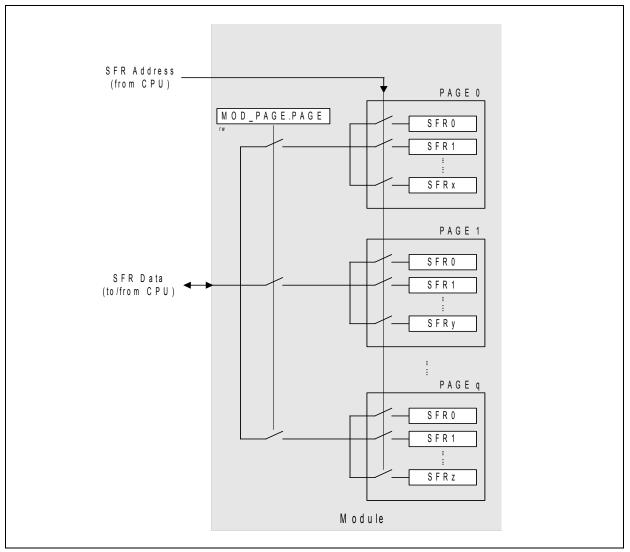

Other key features of the XC866 include a Capture/Compare Unit 6 (CCU6) for the generation of pulse width modulated signal with special modes for motor control, and a 10-bit Analog-to-Digital Converter (ADC) with extended functionalities like autoscan and result accumulation for anti-aliasing filtering or for averaging. Local Interconnect Network (LIN) applications are also supported through extended UART features and the provision of LIN low level drivers for most devices. For low power applications, various power saving modes are available for selection by the user. Control of the numerous on-chip peripheral functionalities is achieved by extending the Special Function Register (SFR) address range with an intelligent paging mechanism optimized for interrupt handling.

| Flash or ROM <sup>1)</sup><br>8K/16K x 8 On-Chip Debug Support |                                         | UART              | SSC               | Port 0                         | 6-bit Digital I/O          |        |                            |

|----------------------------------------------------------------|-----------------------------------------|-------------------|-------------------|--------------------------------|----------------------------|--------|----------------------------|

| Boot ROM<br>8K x 8                                             | XC800 Core                              |                   |                   | Capture/Compare Unit<br>16-bit |                            | Port 1 | 5-bit Digital I/O          |

| XRAM<br>512 x 8                                                |                                         | XC800 Cole        |                   | Compare Unit<br>16-bit         |                            | Port 2 | 8-bit Digital/Analog Input |

| RAM<br>256 x 8                                                 | Timer 0<br>16-bit                       | Timer 1<br>16-bit | Timer 2<br>16-bit | Watchdog<br>Timer              | ADC<br>10-bit<br>8-channel | Port 3 | 8-bit Digital I/O          |

|                                                                | 1) All ROM devices include 4K x 8 Flash |                   |                   |                                |                            |        | ,<br>h                     |

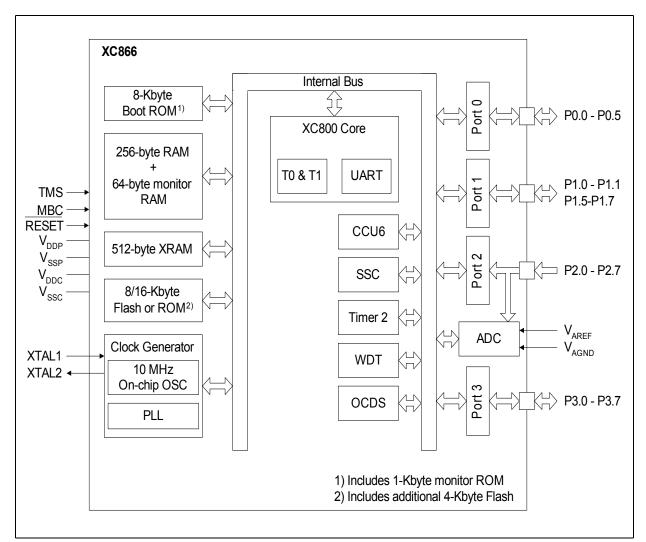

Figure 1-1 shows the functional units of the XC866.

# Figure 1-1 XC866 Functional Units

The XC866 product family features eight devices with different configurations and program memory sizes, offering cost-effective solution for different application requirements. In general, each device contains a non-volatile  $8K \times 8$  read-only program memory, a volatile  $768 \times 8$  read/write data memory, four ports, three 16-bit timers, a 16-bit capture/compare unit, a 16-bit compare timer, 14 interrupt vectors (and an NMI), four priority-level interrupt structure, two serial ports, versatile fail-safe mechanisms, on-chip debugging support logic and a 10-bit ADC.

The list of XC866 devices and their differences are summarized in Table 1-1.

| Device Type | Device Name | Flash Size | <b>ROM Size</b> | LIN Support |

|-------------|-------------|------------|-----------------|-------------|

| Flash       | XC866L-4FR  | 16 Kbytes  | _               | Yes         |

|             | XC866-4FR   | 16 Kbytes  | -               | No          |

|             | XC866L-2FR  | 8 Kbytes   | -               | Yes         |

|             | XC866-2FR   | 8 Kbytes   | -               | No          |

| ROM         | XC866L-4RR  | 4 Kbytes   | 16 Kbytes       | Yes         |

|             | XC866-4RR   | 4 Kbytes   | 16 Kbytes       | No          |

|             | XC866L-2RR  | 4 Kbytes   | 8 Kbytes        | Yes         |

|             | XC866-2RR   | 4 Kbytes   | 8 Kbytes        | No          |

# Table 1-1Device Summary

The term "XC866" in this document refers to all devices of the XC866 family unless otherwise stated.

# 1.1 Feature Summary

The following list summarizes the main features of the XC866:

- High-performance XC800 Core

- compatible with standard 8051 processor

- two clocks per machine cycle architecture (for memory access without wait state)

- two data pointers

- On-chip memory

- 8 Kbytes of Boot ROM

- 256 bytes of RAM

- 512 bytes of XRAM

- 8/16 Kbytes of Flash; or

8/16 Kbytes of ROM, with additional 4 Kbytes of Flash

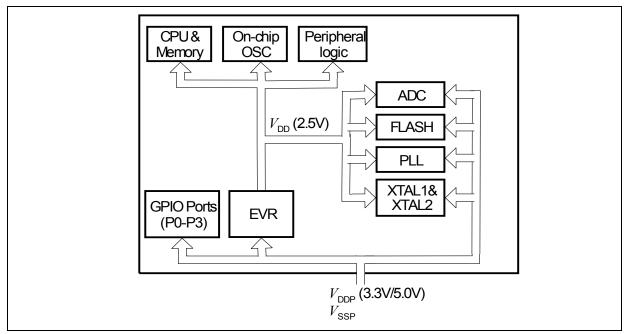

- I/O port supply at 3.0 to 5.5 V and core logic supply at 2.5 V (generated by embedded voltage regulator)

- Power-on reset generation

- Brownout detection for core logic supply

- On-chip OSC and PLL for clock generation

- PLL loss-of-lock detection

- Power saving modes

- slow-down mode

- idle mode

- power-down mode with wake-up capability via RXD or EXINT0

- clock gating control to each peripheral

- Programmable 16-bit Watchdog Timer (WDT)

- Four ports

- 19 pins as digital I/O

- 8 pins as digital/analog input

- 8-channel, 10-bit ADC

- Three 16-bit timers

- Timer 0 and Timer 1 (T0 and T1)

- Timer 2

- Capture/compare unit for PWM signal generation (CCU6)

- Full-duplex serial interface (UART)

- Synchronous serial channel (SSC)

- On-chip debug support

- 1 Kbyte of monitor ROM (part of the 8-Kbyte Boot ROM)

- 64 bytes of monitor RAM

- PG-TSSOP-38 pin package

- Temperature range T<sub>A</sub>:

- SAF (-40 to 85 °C)

- SAK (-40 to 125 °C)

# The block diagram of the XC866 is shown in Figure 1-2.

Figure 1-2 XC866 Block Diagram

# 1.2 Pin Configuration

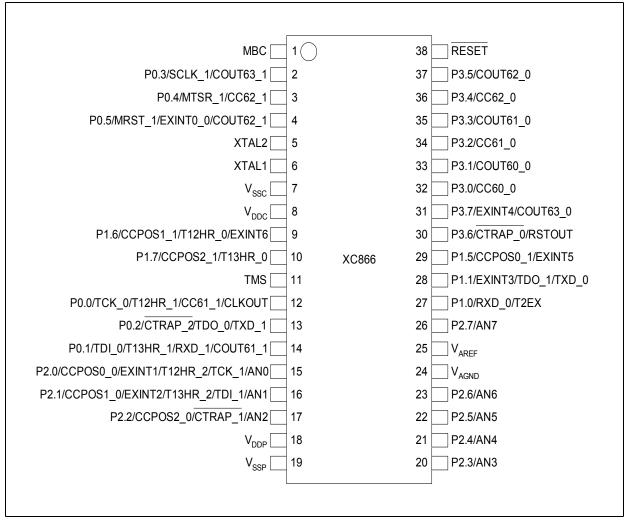

The pin configuration of the XC866, based on the PG-TSSOP-38 package, is shown in **Figure 1-3**.

Figure 1-3 XC866 Pin Configuration, PG-TSSOP-38 Package (top view)

# 1.3 Pin Definitions and Functions

After reset, all pins are configured as input with one of the following:

- Pull-up device enabled (PU)

- Pull-down device enabled (PD)

- High impedance with both pull-up and pull-down devices disabled (Hi-Z)

The functions and default states of the XC866 external pins are provided in Table 1-2.

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                                                                                                                                                |                                                                                                    |  |

|--------|---------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|

| P0     |               | I/O  |                | <b>Port 0</b><br>Port 0 is a 6-bit bidirectional general purpose I/O port. It can be used as alternate functions for the JTAG, CCU6, UART, and the SSC. |                                                                                                    |  |

| P0.0   | 12            |      | Hi-Z           | TCK_0<br>T12HR_1                                                                                                                                        | JTAG Clock Input<br>CCU6 Timer 12 Hardware Run<br>Input                                            |  |

|        |               |      |                | CC61_1<br>CLKOUT                                                                                                                                        | Input/Output of Capture/Compare<br>channel 1<br>10 MHz On-Chip OSC Clock<br>Output                 |  |

| P0.1   | 14            |      | Hi-Z           | TDI_0<br>T13HR_1                                                                                                                                        | JTAG Serial Data Input<br>CCU6 Timer 13 Hardware Run<br>Input                                      |  |

|        |               |      |                | RXD_1<br>COUT61_1                                                                                                                                       | UART Receive Input<br>Output of Capture/Compare<br>channel 1                                       |  |

| P0.2   | 13            |      | PU             | CTRAP_2<br>TDO_0<br>TXD_1                                                                                                                               | CCU6 Trap Input<br>JTAG Serial Data Output<br>UART Transmit Output                                 |  |

| P0.3   | 2             |      | Hi-Z           | SCK_1<br>COUT63_1                                                                                                                                       | SSC Clock Input/Output<br>Output of Capture/Compare<br>channel 3                                   |  |

| P0.4   | 3             |      | Hi-Z           | MTSR_1<br>CC62_1                                                                                                                                        | SSC Master Transmit Output/<br>Slave Receive Input<br>Input/Output of Capture/Compare<br>channel 2 |  |

Table 1-2

Pin Definitions and Functions

# Table 1-2Pin Definitions and Functions (cont'd)

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                       |                                                                                                                            |

|--------|---------------|------|----------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| P0.5   | 4             |      | Hi-Z           | MRST_1<br>EXINT0_0<br>COUT62_1 | SSC Master Receive Input/<br>Slave Transmit Output<br>External Interrupt Input 0<br>Output of Capture/Compare<br>channel 2 |

| Table 1-2 | Pin Definitions and Functions ( | (cont'd) | ) |

|-----------|---------------------------------|----------|---|

|-----------|---------------------------------|----------|---|

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                                                                                                                                                |                                                                                        |  |

|--------|---------------|------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| P1     |               | I/O  |                | <b>Port 1</b><br>Port 1 is a 5-bit bidirectional general purpose I/O port. It can be used as alternate functions for the JTAG, CCU6, UART, and the SSC. |                                                                                        |  |

| P1.0   | 27            |      | PU             | RXD_0<br>T2EX                                                                                                                                           | UART Receive Input<br>Timer 2 External Trigger Input                                   |  |

| P1.1   | 28            |      | PU             | EXINT3<br>TDO_1<br>TXD_0                                                                                                                                | External Interrupt Input 3<br>JTAG Serial Data Output<br>UART Transmit Output          |  |

| P1.5   | 29            |      | PU             | CCPOS0_1<br>EXINT5                                                                                                                                      | CCU6 Hall Input 0<br>External Interrupt Input 5                                        |  |

| P1.6   | 9             |      | PU             | CCPOS1_1<br>T12HR_0<br>EXINT6                                                                                                                           | CCU6 Hall Input 1<br>CCU6 Timer 12 Hardware Run<br>Input<br>External Interrupt Input 6 |  |

| P1.7   | 10            |      | PU             | CCPOS2_1<br>T13HR_0                                                                                                                                     | CCU6 Hall Input 2<br>CCU6 Timer 13 Hardware Run<br>Input                               |  |

|        |               |      |                | P1.5 and P1.6 can be used as a software chip select output for the SSC.                                                                                 |                                                                                        |  |

| Table 1-2 | Pin Definitions and Functions ( | (cont'd) |

|-----------|---------------------------------|----------|

|-----------|---------------------------------|----------|

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                                      |                                                                                                                                               |

|--------|---------------|------|----------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| P2     |               | I    |                | can be used inputs of the                     | -bit general purpose input-only port. It<br>as alternate functions for the digital<br>JTAG and CCU6. It is also used as the<br>s for the ADC. |

| P2.0   | 15            |      | Hi-Z           | CCPOS0_0<br>EXINT1<br>T12HR_2<br>TCK_1<br>AN0 | CCU6 Hall Input 0<br>External Interrupt Input 1<br>CCU6 Timer 12 Hardware Run<br>Input<br>JTAG Clock Input<br>Analog Input 0                  |

| P2.1   | 16            |      | Hi-Z           | CCPOS1_0<br>EXINT2<br>T13HR_2<br>TDI_1<br>AN1 | CCU6 Hall Input 1<br>External Interrupt Input 2<br>CCU6 Timer 13 Hardware Run<br>Input<br>JTAG Serial Data Input<br>Analog Input 1            |

| P2.2   | 17            |      | Hi-Z           | CCPOS2_0<br>CTRAP_1<br>AN2                    | CCU6 Hall Input 2<br>CCU6 Trap Input<br>Analog Input 2                                                                                        |

| P2.3   | 20            |      | Hi-Z           | AN3                                           | Analog Input 3                                                                                                                                |

| P2.4   | 21            |      | Hi-Z           | AN4                                           | Analog Input 4                                                                                                                                |

| P2.5   | 22            |      | Hi-Z           | AN5                                           | Analog Input 5                                                                                                                                |

| P2.6   | 23            |      | Hi-Z           | AN6                                           | Analog Input 6                                                                                                                                |

| P2.7   | 26            |      | Hi-Z           | AN7                                           | Analog Input 7                                                                                                                                |

| Symbol | Pin<br>Number | Туре | Reset<br>State | Function                                                                                                                 |                                                                                               |  |

|--------|---------------|------|----------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| P3     |               | 1    |                | <b>Port 3</b><br>Port 3 is a bidirectional general purpose I/O port. It can be used as alternate functions for the CCU6. |                                                                                               |  |

| P3.0   | 32            |      | Hi-Z           | CC60_0                                                                                                                   | Input/Output of Capture/Compare<br>channel 0                                                  |  |

| P3.1   | 33            |      | Hi-Z           | COUT60_0                                                                                                                 | Output of Capture/Compare<br>channel 0                                                        |  |

| P3.2   | 34            |      | Hi-Z           | CC61_0                                                                                                                   | Input/Output of Capture/Compare<br>channel 1                                                  |  |

| P3.3   | 35            |      | Hi-Z           | COUT61_0                                                                                                                 | Output of Capture/Compare<br>channel 1                                                        |  |

| P3.4   | 36            |      | Hi-Z           | CC62_0                                                                                                                   | Input/Output of Capture/Compare<br>channel 2                                                  |  |

| P3.5   | 37            |      | Hi-Z           | COUT62_0                                                                                                                 | Output of Capture/Compare<br>channel 2                                                        |  |

| P3.6   | 30            |      | PD             | CTRAP_0<br>RSTOUT                                                                                                        | CCU6 Trap Input<br>Reset output indication for internal<br>reset condition in microcontroller |  |

| P3.7   | 31            |      | Hi-Z           | EXINT4<br>COUT63_0                                                                                                       | External Interrupt Input 4<br>Output of Capture/Compare<br>channel 3                          |  |

# Table 1-2 Pin Definitions and Functions (cont'd)

| Symbol            | Pin<br>Number | Туре | Reset<br>State | Function                                                            |

|-------------------|---------------|------|----------------|---------------------------------------------------------------------|

| V <sub>DDP</sub>  | 18            | _    | -              | I/O Port Supply (3.0 - 5.5 V)                                       |

| V <sub>SSP</sub>  | 19            | _    | -              | I/O Port Ground                                                     |

|                   | 8             | _    | -              | Core Supply Output (2.5 V)                                          |

| V <sub>SSC</sub>  | 7             | _    | -              | Core Supply Ground                                                  |

| V <sub>AREF</sub> | 25            | _    | -              | ADC Reference Voltage                                               |

| V <sub>AGND</sub> | 24            | -    | -              | ADC Reference Ground                                                |

| XTAL1             | 6             | I    | Hi-Z           | External Oscillator Input<br>(backup for on-chip OSC, normally NC)  |

| XTAL2             | 5             | 0    | Hi-Z           | External Oscillator Output<br>(backup for on-chip OSC, normally NC) |

| TMS               | 11            | 1    | PD             | Test Mode Select                                                    |

| RESET             | 38            | 1    | PU             | Reset Input for PG-TSSOP-38 package                                 |

| МВС               | 1             | 1    | PU             | Monitor & BootStrap Loader Control                                  |

# Table 1-2 Pin Definitions and Functions (cont'd)

# 1.4 Textual Convention

This document uses the following textual conventions for named components of the XC866:

- Functional units of the XC866 are shown in upper case. For example: "The SSC can be used to communicate with shift registers."

- Pins using negative logic are indicated by an overbar. For example: "A reset input pin RESET is provided for the hardware reset."

- Bit fields and bits in registers are generally referenced as "Register name.Bit field" or "Register name.Bit". Most of the register names contain a module name prefix, separated by an underscore character "\_" from the actual register name. In the example of "SSC\_CON", "SSC" is the module name prefix, and "CON" is the actual register name).

- Variables that are used to represent sets of processing units or registers appear in mixed-case type. For example, the register name "CC6xR" refers to multiple "CC6xR" registers with the variable x (x = 0, 1, 2). The bounds of the variables are always specified where the register expression is first used (e.g., "x = 0 2"), and is repeated as needed.

- The default radix is decimal. Hexadecimal constants have a suffix with the subscript letter "H" (e.g., C0<sub>H</sub>). Binary constants have a suffix with the subscript letter "B" (e.g., 11<sub>B</sub>).

- When the extents of register fields, groups of signals, or groups of pins are collectively named in the body of the document, they are represented as "NAME[A:B]", which defines a range, from B to A, for the named group. Individual bits, signals, or pins are represented as "NAME[C]", with the range of the variable C provided in the text (e.g., CFG[2:0] and TOS[0]).

- Units are abbreviated as follows:

- **MHz** = Megahertz

- $\mu s$  = Microseconds

- **kBaud**, **kbit** = 1000 characters/bits per second

- **MBaud**, **Mbit** = 1,000,000 characters/bits per second

- **Kbyte** = 1024 bytes of memory

- **Mbyte** = 1,048,576 bytes of memory

In general, the *k* prefix scales a unit by 1000 whereas the *K* prefix scales a unit by 1024. Hence, the Kbyte unit scales the expression preceding it by 1024. The kBaud unit scales the expression preceding it by 1000. The *M* prefix scales by 1,000,000 or 1,048,576, and  $\mu$  scales by 0.000001. For example, 1 Kbyte is 1024 bytes, 1 Mbyte is 1024 × 1024 bytes, 1 kBaud/kbit are 1000 characters/bits per second, 1 MBaud/Mbit are 1,000,000 characters/bits per second, and 1 MHz is 1,000,000 Hz.

• Data format quantities are defined as follows:

byte = 8-bit quantity

# 1.5 Reserved, Undefined and Unimplemented Terminology

In tables where register bit fields are defined, the following conventions are used to indicate undefined and unimplemented function. Further, types of bits and bit fields are defined using the abbreviations shown in Table 1-3.

| Function of Bits | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Unimplemented    | <ul> <li>Register bit fields named "0" indicate unimplemented functions with the following behavior.</li> <li>Reading these bit fields returns 0.</li> <li>Writing to these bit fields has no effect.</li> <li>These bit fields are reserved. When writing, software should always set such bit fields to 0 in order to preserve compatibility with future products. Setting the bit fields to 1 may lead to unpredictable results.</li> </ul> |  |  |  |  |

| Undefined        | Certain bit combinations in a bit field can be labeled "Reserved<br>indicating that the behavior of the XC866 is undefined for that<br>combination of bits. Setting the register to undefined bit<br>combinations may lead to unpredictable results. Such bit<br>combinations are reserved. When writing, software must alway<br>set such bit fields to legal values as provided in the bit field<br>description tables.                       |  |  |  |  |

| rw               | The bit or bit field can be read and written.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| r                | The bit or bit field can only be read (read-only).                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| w                | The bit or bit field can only be written (write-only). Reading always return 0.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| h                | The bit or bit field can also be modified by hardware (such as a status bit). This attribute can be combined with 'rw' or 'r' bits to 'rwh' and 'rh' bits, respectively.                                                                                                                                                                                                                                                                       |  |  |  |  |

Table 1-3

Bit Function Terminology

# 1.6 Acronyms

Table 1-4 lists the acronyms used in this document.

| Table 1-4 | Acronyms                                    |  |  |  |  |

|-----------|---------------------------------------------|--|--|--|--|

| ADC       | Analog-to-Digital Converter                 |  |  |  |  |

| ALU       | Arithmetic/Logic Unit                       |  |  |  |  |

| BSL       | BootStrap Loader                            |  |  |  |  |

| CCU6      | Capture/Compare Unit 6                      |  |  |  |  |

| CGU       | Clock Generation Unit                       |  |  |  |  |

| CPU       | Central Processing Unit                     |  |  |  |  |

| ECC       | Error Correction Code                       |  |  |  |  |

| EVR       | Embedded Voltage Regulator                  |  |  |  |  |

| FIFO      | First-In First-Out                          |  |  |  |  |

| GPIO      | General Purpose I/O                         |  |  |  |  |

| IAP       | In-Application Programming                  |  |  |  |  |

| I/O       | Input/Output                                |  |  |  |  |

| ISP       | In-System Programming                       |  |  |  |  |

| JTAG      | Joint Test Action Group                     |  |  |  |  |

| LIN       | Local Interconnect Network                  |  |  |  |  |

| NMI       | Non-Maskable Interrupt                      |  |  |  |  |

| OCDS      | On-Chip Debug Support                       |  |  |  |  |

| PC        | Program Counter                             |  |  |  |  |

| POR       | Power-On Reset                              |  |  |  |  |

| PLL       | Phase-Locked Loop                           |  |  |  |  |

| PSW       | Program Status Word                         |  |  |  |  |

| PWM       | Pulse Width Modulation                      |  |  |  |  |

| RAM       | Random Access Memory                        |  |  |  |  |

| ROM       | Read-Only Memory                            |  |  |  |  |

| SFR       | Special Function Register                   |  |  |  |  |

| SPI       | Serial Peripheral Interface                 |  |  |  |  |

| SSC       | Synchronous Serial Controller               |  |  |  |  |

| UART      | Universal Asynchronous Receiver/Transmitter |  |  |  |  |

| WDT       | Watchdog Timer                              |  |  |  |  |

# 2 **Processor Architecture**

The XC866 is based on a high-performance 8-bit Central Processing Unit (CPU) that is compatible with the standard 8051 processor. While the standard 8051 processor is designed around a 12-clock machine cycle, the XC866 CPU uses a 2-clock machine cycle. This allows fast access to ROM or RAM memories without wait state. Access to the Flash memory, however, requires an additional wait state (one machine cycle). See **Section 2.3**. The instruction set consists of 45% one-byte, 41% two-byte and 14% three-byte instructions.

The XC866 CPU provides a range of debugging features, including basic stop/start, single-step execution, breakpoint support and read/write access to the data memory, program memory and SFRs.

# Features:

- Two clocks per machine cycle architecture (for memory access without wait state)

- Wait state support for Flash memory

- Program memory download option

- 15-source, 4-level interrupt controller

- Two data pointers

- Power saving modes

- Dedicated debug mode and debug signals

- Two 16-bit timers (Timer 0 and Timer 1)

- Full-duplex serial port (UART)

# XC866

#### **Processor Architecture**

# 2.1 Functional Description

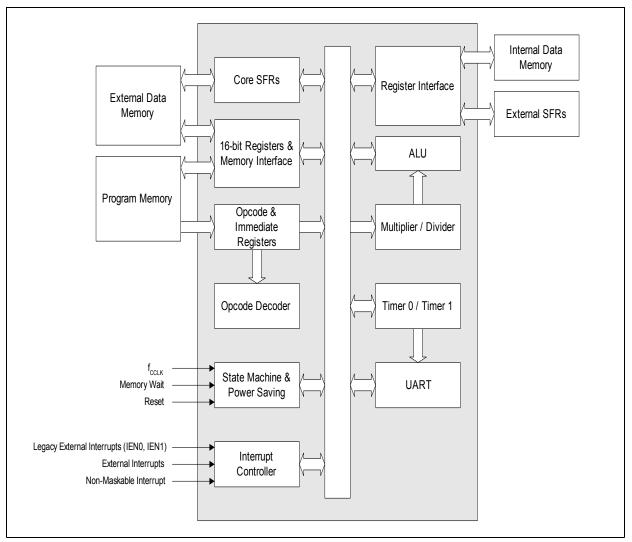

**Figure 2-1** shows the CPU functional blocks. The CPU consists of the instruction decoder, the arithmetic section, and the program control section. Each program instruction is decoded by the instruction decoder. This instruction decoder generates internal signals that control the functions of the individual units within the CPU. The internal signals have an effect on the source and destination of data transfers and control the arithmetic/logic unit (ALU) processing.

Figure 2-1 CPU Block Diagram

The arithmetic section of the processor performs extensive data manipulation and consists of the ALU, ACC register, B register, and PSW register.

The ALU accepts 8-bit data words from one or two sources, and generates an 8-bit result under the control of the instruction decoder. The ALU performs both arithmetic and logic operations. Arithmetic operations include add, subtract, multiply, divide, increment, decrement, BCD-decimal-add-adjust, and compare. Logic operations include AND, OR, Exclusive OR, complement, and rotate (right, left, or swap nibble (left four)). Also included is a Boolean processor performing the bit operations such as set, clear, complement, jump-if-set, jump-if-not-set, jump-if-set-and-clear, and move to/from carry. The ALU can perform the bit operations of logical AND or logical OR between any addressable bit (or its complement) and the carry flag, and place the new result in the carry flag.

The program control section controls the sequence in which the instructions stored in program memory are executed. The 16-bit Program Counter (PC) holds the address of the next instruction to be executed. The conditional branch logic enables internal and external events to the processor to cause a change in the program execution sequence.

# 2.2 CPU Register Description

The CPU registers occupy direct Internal Data Memory space locations in the range  $80_{\rm H}$  to  ${\rm FF}_{\rm H}.$

# 2.2.1 Stack Pointer (SP)

The SP register contains the Stack Pointer (SP). The SP is used to load the Program Counter (PC) into Internal Data Memory during LCALL and ACALL instructions, and to retrieve the PC from memory during RET and RETI instructions. Data may also be saved on or retrieved from the stack using PUSH and POP instructions, respectively. Instructions that use the stack automatically pre-increment or post-decrement the stack pointer so that the stack pointer always points to the last byte written to the stack, i.e., the top of the stack. On reset, the SP is reset to  $07_{\rm H}$ . This causes the stack to begin at a location =  $08_{\rm H}$  above register bank zero. The SP can be read or written under software control.

# 2.2.2 Data Pointer (DPTR)

The Data Pointer (DPTR) is stored in registers DPL (Data Pointer Low byte) and DPH (Data Pointer High byte) to form 16-bit addresses for External Data Memory accesses (MOVX A,@DPTR and MOVX @DPTR,A), for program byte moves (MOVC A,@A+DPTR), and for indirect program jumps (JMP @A+DPTR).

Two true 16-bit operations are allowed on the Data Pointer: load immediate (MOV DPTR,#data) and increment (INC DPTR).

# 2.2.3 Accumulator (ACC)

This register provides one of the operands for most ALU operations. While ACC is the symbol for the accumulator register, the mnemonics for accumulator-specific instructions refer to the accumulator simply as "A".

# 2.2.4 B Register

The B register is used during multiply and divide operations to provide the second operand. For other instructions, it can be treated as another scratch pad register.

# 2.2.5 Program Status Word

The Program Status Word (PSW) contains several status bits that reflect the current state of the CPU.

#### PSW

# **Program Status Word Register**

### Reset Value: 00<sub>H</sub>

| 7  | 6   | 5   | 4   | 3   | 2   | 1   | 0  |

|----|-----|-----|-----|-----|-----|-----|----|

| СҮ | AC  | F0  | RS1 | RS0 | ov  | F1  | Р  |

| rw | rwh | rwh | rw  | rw  | rwh | rwh | rh |

| Field      | Bits   | Туре | Desc                                                                                                                                                           | riptic                                           | on                                                             |  |

|------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------|--|

| P          | 0      | rh   | <b>Parity Flag</b><br>Set/cleared by hardware after each instruction to<br>indicate an odd/even number of "one" bits in the<br>accumulator, i.e., even parity. |                                                  |                                                                |  |

| F1         | 1      | rwh  | Gene                                                                                                                                                           | eral P                                           | urpose Flag                                                    |  |

| OV         | 2      | rwh  |                                                                                                                                                                | Overflow Flag<br>Used by arithmetic instructions |                                                                |  |

| RS0<br>RS1 | 3<br>4 | rw   | <b>Register Bank Select</b><br>These bits are used to select one of the four register<br>banks.                                                                |                                                  |                                                                |  |

|            |        |      | RS1                                                                                                                                                            | RS0                                              | Function                                                       |  |

|            |        |      | 0                                                                                                                                                              | 0                                                | Bank 0 selected, data address 00 <sub>H</sub> -07 <sub>H</sub> |  |

|            |        |      | 0                                                                                                                                                              | 1                                                | Bank 1 selected, data address 08 <sub>H</sub> -0F <sub>H</sub> |  |

|            |        |      | 1                                                                                                                                                              | 0                                                | Bank 2 selected, data address 10 <sub>H</sub> -17 <sub>H</sub> |  |

|            |        |      | 1                                                                                                                                                              | 1                                                | Bank 3 selected, data address 18 <sub>H</sub> -1F <sub>H</sub> |  |

| F0         | 5      | rwh  | General Purpose Flag                                                                                                                                           |                                                  |                                                                |  |

| AC         | 6      | rwh  | Auxiliary Carry Flag<br>Used by instructions that execute BCD operations                                                                                       |                                                  |                                                                |  |

| CY         | 7      | rw   | Carry Flag<br>Used by arithmetic instructions                                                                                                                  |                                                  |                                                                |  |

# 2.2.6 Extended Operation Register (EO)

The instruction set includes an additional instruction MOVC @(DPTR++),A which allows program memory to be written. This instruction may be used to download code into the program memory when the CPU is initialized and subsequently, also to provide software updates. The instruction copies the contents of the accumulator to the code memory at the location pointed to by the current data pointer, and then increments the data pointer.

The instruction uses the opcode  $A5_H$ , which is the same as the software break instruction TRAP (see **Table 2-1**). Register bit EO.TRAP\_EN is used to select the instruction executed by the opcode  $A5_H$ . When TRAP\_EN is 0 (default), the  $A5_H$  opcode executes the MOVC instruction. When TRAP\_EN is 1, the  $A5_H$  opcode executes the software break instruction TRAP, which switches the CPU to debug mode for breakpoint processing.

#### EO Extended Operation Register

Reset Value: 00<sub>H</sub>

| 7 | 6 | 5 | 4       | 3 | 2 | 1 | 0      |

|---|---|---|---------|---|---|---|--------|

|   | 0 | 1 | TRAP_EN |   | 0 | I | DPSEL0 |

|   | r |   | rw      |   | r |   | rw     |

| Field   | Bits            | Туре | Description                                                                  |  |

|---------|-----------------|------|------------------------------------------------------------------------------|--|

| DPSEL0  | 0               | rw   | Data Pointer Select0DPTR0 is selected.1DPTR1 is selected.                    |  |

| TRAP_EN | 4               | rw   | <b>TRAP Enable</b> 0Select MOVC @(DPTR++),A1Select software TRAP instruction |  |

| 0       | [3:1],<br>[7:5] | r    | Reserved<br>Returns 0 if read; should be written with 0.                     |  |

# 2.2.7 Power Control Register (PCON)

The CPU has two power-saving modes: idle mode and power-down mode. The idle mode can be entered via the PCON register. In idle mode, the clock to the CPU is stopped while the timers, serial port and interrupt controller continue to run using a half-speed clock. In power-down mode, the clock to the entire CPU is stopped.

### PCON Power Control Register

#### Reset Value: 00<sub>H</sub>

|        | 7  | 6 | 5   | 4   | 3  | 2    | 1 | 0  |  |

|--------|----|---|-----|-----|----|------|---|----|--|

| SMOD 0 |    |   | GF1 | GF0 | 0  | IDLE |   |    |  |

|        | rw |   | r   |     | rw | rw   | r | rw |  |

| Field | Bits | Туре | Description                                             |  |

|-------|------|------|---------------------------------------------------------|--|

| IDLE  | 0    | rw   | Idle Mode Enable0Do not enter idle mode1Enter idle mode |  |

| GF0   | 2    | rw   | General Purpose Flag Bit 0                              |  |

| GF1   | 3    | rw   | General Purpose Flag Bit 1                              |  |

# 2.3 Instruction Timing

For memory access without wait state, a CPU machine cycle comprises two input clock periods referred to as Phase 1 (P1) and Phase 2 (P2) that correspond to two different CPU states. A CPU state within an instruction is denoted by reference to the machine cycle and state number, e.g., C2P1 is the first clock period within machine cycle 2. Memory accesses take place during one or both phases of the machine cycle. SFR writes only occur at the end of P2. An instruction takes one, two or four machine cycles to execute. Registers are generally updated and the next opcode read at the end of P2 of the last machine cycle for the instruction.

With each access to the Flash memory, instruction execution times are extended by one machine cycle (one wait state), starting from either P1 or P2.

**Figure 2-2** shows the fetch/execute timing related to the internal states and phases. Execution of an instruction occurs at C1P1. For a 2-byte instruction, the second reading starts at C1P1.

**Figure 2-2** (a) shows two timing diagrams for a 1-byte, 1-cycle ( $1 \times$  machine cycle) instruction. The first diagram shows the instruction being executed within one machine cycle since the opcode (C1P2) is fetched from a memory without wait state. The second diagram shows the corresponding states of the same instruction being executed over two machine cycles (instruction time extended), with one wait state inserted for opcode fetching from the Flash memory.

**Figure 2-2** (b) shows two timing diagrams for a 2-byte, 1-cycle  $(1 \times \text{machine cycle})$  instruction. The first diagram shows the instruction being executed within one machine cycle since the second byte (C1P1) and the opcode (C1P2) are fetched from a memory without wait state. The second diagram shows the corresponding states of the same instruction being executed over three machine cycles (instruction time extended), with one wait state inserted for each access to the Flash memory (two wait states inserted in total).

**Figure 2-2** (c) shows two timing diagrams of a 1-byte, 2-cycle ( $2 \times$  machine cycle) instruction. The first diagram shows the instruction being executed over two machine cycles with the opcode (C2P2) fetched from a memory without wait state. The second diagram shows the corresponding states of the same instruction being executed over three machine cycles (instruction time extended), with one wait state inserted for opcode fetching from the Flash memory.

Figure 2-2 CPU Instruction Timing

Instructions are 1, 2 or 3 bytes long as indicated in the "Bytes" column of **Table 2-1**. For the XC866, the time taken for each instruction includes:

- · decoding/executing the fetched opcode

- fetching the operand/s (for instructions > 1 byte)

- fetching the first byte (opcode) of the next instruction (due to XC866 CPU pipeline)

*Note:* The XC866 CPU fetches the opcode of the next instruction while executing the current instruction.

**Table 2-1** provides a reference for the number of clock cycles required by each instruction. The first value applies to fetching operand(s) and opcode from fast program memory (e.g., Boot ROM and XRAM) without wait state. The second value applies to fetching operand(s) and opcode from slow program memory (e.g., Flash) with one wait state inserted. The instruction time for the standard 8051 processor is provided in the last column for performance comparison with the XC866 CPU. Even with one wait state inserted for each byte of operand/opcode fetched, the XC866 CPU executes instructions faster than the standard 8051 processor by a factor of between two (e.g., 2-byte, 1-cycle instructions) to six (e.g., 1-byte, 4-cycle instructions).

| Mnemonic     | Hex Code   | Bytes | Number of f <sub>CCLK</sub> Cycles |      |      |  |

|--------------|------------|-------|------------------------------------|------|------|--|

|              |            |       | XC866                              |      | 8051 |  |

|              |            |       | no ws                              | 1 ws | -    |  |

|              | ARITHMETIC | 2     | ·                                  |      |      |  |

| ADD A,Rn     | 28-2F      | 1     | 2                                  | 4    | 12   |  |

| ADD A,dir    | 25         | 2     | 2                                  | 6    | 12   |  |

| ADD A,@Ri    | 26-27      | 1     | 2                                  | 4    | 12   |  |

| ADD A,#data  | 24         | 2     | 2                                  | 6    | 12   |  |

| ADDC A,Rn    | 38-3F      | 1     | 2                                  | 4    | 12   |  |

| ADDC A,dir   | 35         | 2     | 2                                  | 6    | 12   |  |

| ADDC A,@Ri   | 36-37      | 1     | 2                                  | 4    | 12   |  |

| ADDC A,#data | 34         | 2     | 2                                  | 6    | 12   |  |

| SUBB A,Rn    | 98-9F      | 1     | 2                                  | 4    | 12   |  |

| SUBB A,dir   | 95         | 2     | 2                                  | 6    | 12   |  |

| SUBB A,@Ri   | 96-97      | 1     | 2                                  | 4    | 12   |  |

| SUBB A,#data | 94         | 2     | 2                                  | 6    | 12   |  |

| INC A        | 04         | 1     | 2                                  | 4    | 12   |  |

| INC Rn       | 08-0F      | 1     | 2                                  | 4    | 12   |  |

# Table 2-1 CPU Instruction Timing

# XC866

# **Processor Architecture**

# Table 2-1 CPU Instruction Timing (cont'd)

| Mnemonic      | Hex Code | Bytes | Number of f <sub>CCLK</sub> Cycles |      |      |

|---------------|----------|-------|------------------------------------|------|------|

|               |          |       | XC866                              |      | 8051 |

|               |          |       | no ws                              | 1 ws |      |

| INC dir       | 05       | 2     | 2                                  | 6    | 12   |

| INC @Ri       | 06-07    | 1     | 2                                  | 4    | 12   |

| DEC A         | 14       | 1     | 2                                  | 4    | 12   |

| DEC Rn        | 18-1F    | 1     | 2                                  | 4    | 12   |

| DEC dir       | 15       | 2     | 2                                  | 6    | 12   |

| DEC @Ri       | 16-17    | 1     | 2                                  | 4    | 12   |

| INC DPTR      | A3       | 1     | 4                                  | 4    | 24   |

| MUL AB        | A4       | 1     | 8                                  | 8    | 48   |

| DIV AB        | 84       | 1     | 8                                  | 8    | 48   |

| DA A          | D4       | 1     | 2                                  | 4    | 12   |

|               | LOGICAL  |       |                                    |      | •    |

| ANL A,Rn      | 58-5F    | 1     | 2                                  | 4    | 12   |

| ANL A,dir     | 55       | 2     | 2                                  | 6    | 12   |

| ANL A,@Ri     | 56-57    | 1     | 2                                  | 4    | 12   |

| ANL A,#data   | 54       | 2     | 2                                  | 6    | 12   |

| ANL dir,A     | 52       | 2     | 2                                  | 6    | 12   |

| ANL dir,#data | 53       | 3     | 4                                  | 10   | 24   |

| ORL A,Rn      | 48-4F    | 1     | 2                                  | 4    | 12   |

| ORL A,dir     | 45       | 2     | 2                                  | 6    | 12   |

| ORL A,@Ri     | 46-47    | 1     | 2                                  | 4    | 12   |

| ORL A,#data   | 44       | 2     | 2                                  | 6    | 12   |

| ORL dir,A     | 42       | 2     | 2                                  | 6    | 12   |

| ORL dir,#data | 43       | 3     | 4                                  | 10   | 24   |

| XRL A,Rn      | 68-6F    | 1     | 2                                  | 4    | 12   |

| XRL A,dir     | 65       | 2     | 2                                  | 6    | 12   |

| XRL A,@Ri     | 66-67    | 1     | 2                                  | 4    | 12   |

| XRL A,#data   | 64       | 2     | 2                                  | 6    | 12   |

| XRL dir,A     | 62       | 2     | 2                                  | 6    | 12   |

### **Processor Architecture**

### Table 2-1 CPU Instruction Timing (cont'd)

| Mnemonic       | Hex Code    | Bytes | Number of f <sub>CCLK</sub> Cycles |      |    |  |

|----------------|-------------|-------|------------------------------------|------|----|--|

|                |             |       | XC                                 | 8051 |    |  |

|                |             |       | no ws                              | 1 ws |    |  |

| XRL dir,#data  | 63          | 3     | 4                                  | 10   | 24 |  |

| CLR A          | E4          | 1     | 2                                  | 4    | 12 |  |

| CPL A          | F4          | 1     | 2                                  | 4    | 12 |  |

| SWAP A         | C4          | 1     | 2                                  | 4    | 12 |  |

| RL A           | 23          | 1     | 2                                  | 4    | 12 |  |

| RLC A          | 33          | 1     | 2                                  | 4    | 12 |  |

| RR A           | 03          | 1     | 2                                  | 4    | 12 |  |

| RRC A          | 13          | 1     | 2                                  | 4    | 12 |  |

|                | DATA TRANSF | ER    |                                    |      |    |  |

| MOV A,Rn       | E8-EF       | 1     | 2                                  | 4    | 12 |  |

| MOV A,dir      | E5          | 2     | 2                                  | 6    | 12 |  |

| MOV A,@Ri      | E6-E7       | 1     | 2                                  | 4    | 12 |  |

| MOV A,#data    | 74          | 2     | 2                                  | 6    | 12 |  |

| MOV Rn,A       | F8-FF       | 1     | 2                                  | 4    | 12 |  |

| MOV Rn,dir     | A8-AF       | 2     | 4                                  | 8    | 24 |  |

| MOV Rn,#data   | 78-7F       | 2     | 2                                  | 6    | 12 |  |

| MOV dir,A      | F5          | 2     | 2                                  | 6    | 12 |  |

| MOV dir,Rn     | 88-8F       | 2     | 4                                  | 8    | 24 |  |

| MOV dir,dir    | 85          | 3     | 4                                  | 10   | 24 |  |

| MOV dir,@Ri    | 86-87       | 2     | 4                                  | 8    | 24 |  |

| MOV dir,#data  | 75          | 3     | 4                                  | 10   | 24 |  |

| MOV @Ri,A      | F6-F7       | 1     | 2                                  | 4    | 12 |  |

| MOV @Ri,dir    | A6-A7       | 2     | 4                                  | 8    | 24 |  |

| MOV @Ri,#data  | 76-77       | 2     | 2                                  | 6    | 12 |  |

| MOV DPTR,#data | 90          | 3     | 4                                  | 10   | 24 |  |

| MOVC A,@A+DPTR | 93          | 1     | 4                                  | 6    | 24 |  |

| MOVC A,@A+PC   | 83          | 1     | 4                                  | 6    | 24 |  |

| MOVX A,@Ri     | E2-E3       | 1     | 4                                  | 6    | 24 |  |

### **Processor Architecture**

### Table 2-1 CPU Instruction Timing (cont'd)

| Mnemonic     | Hex Code  | Bytes | Number of f <sub>CCLK</sub> Cycles |      |    |  |

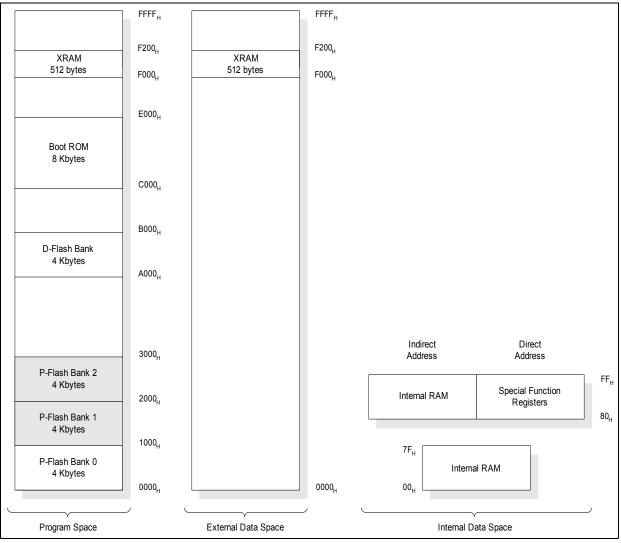

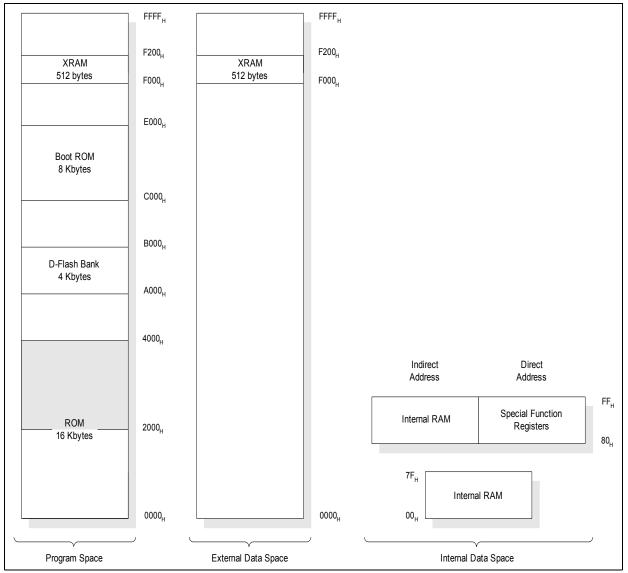

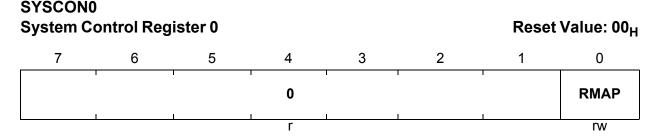

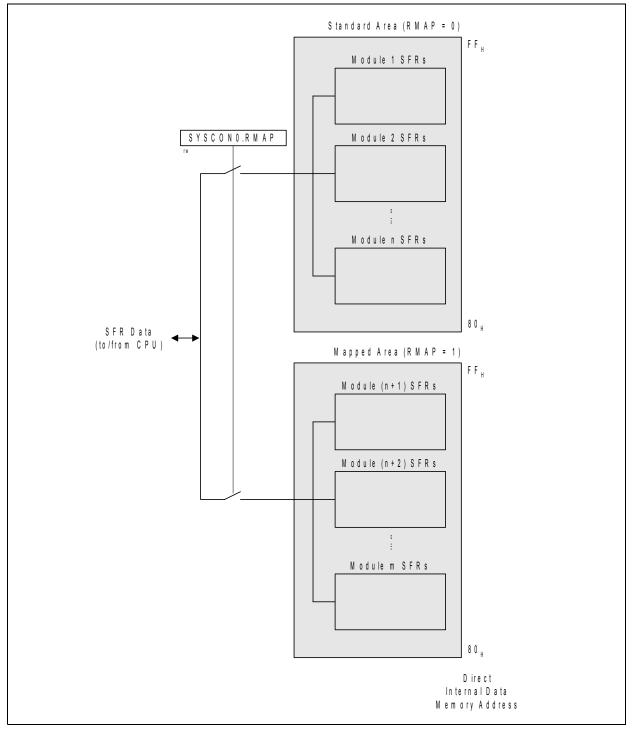

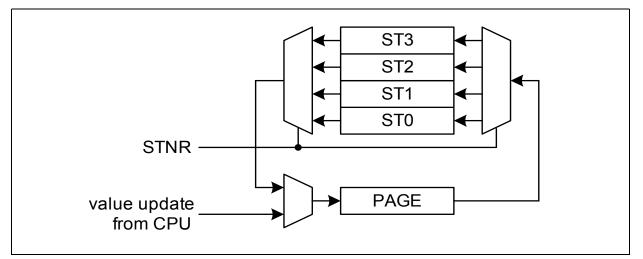

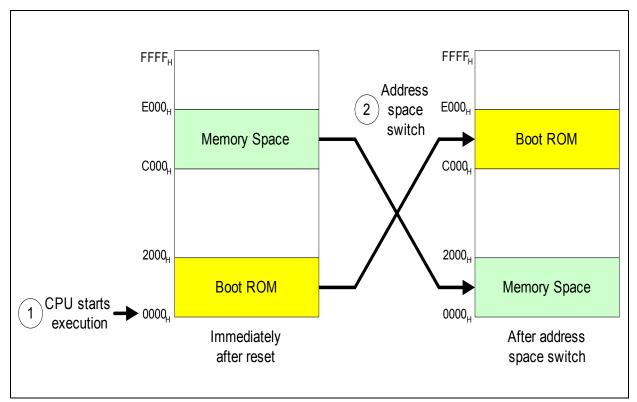

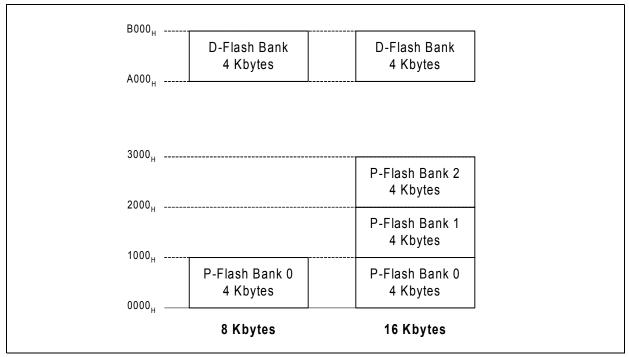

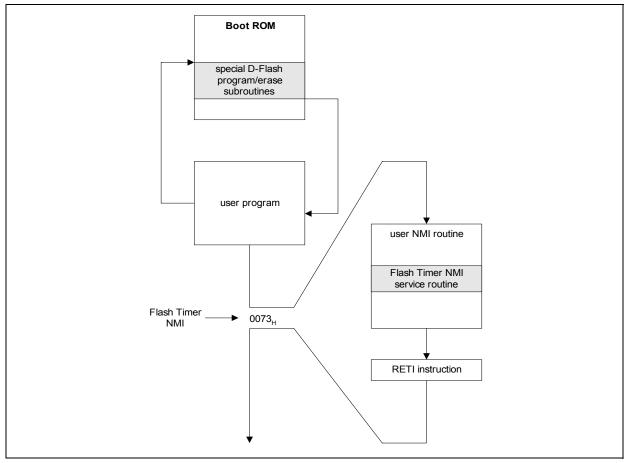

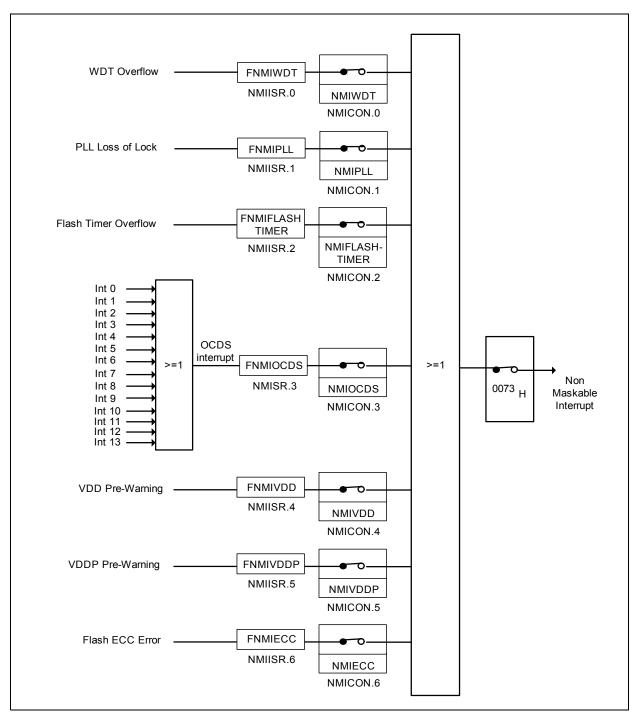

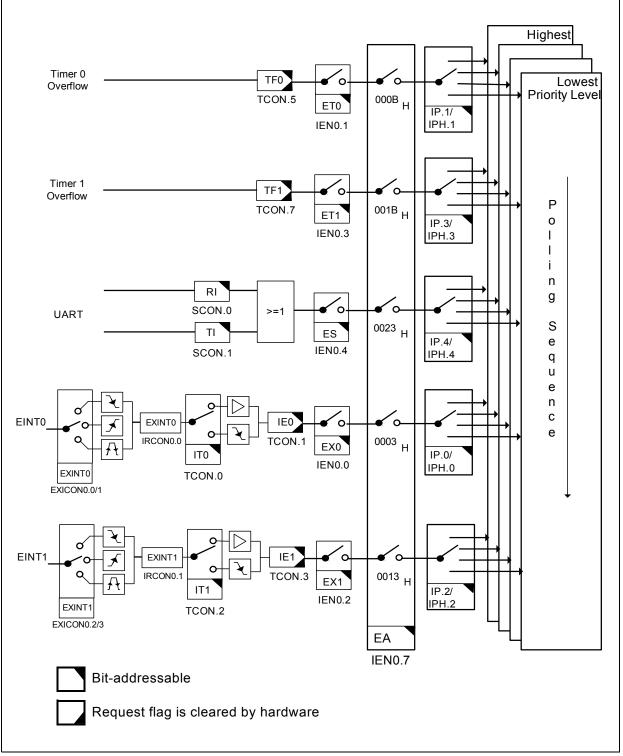

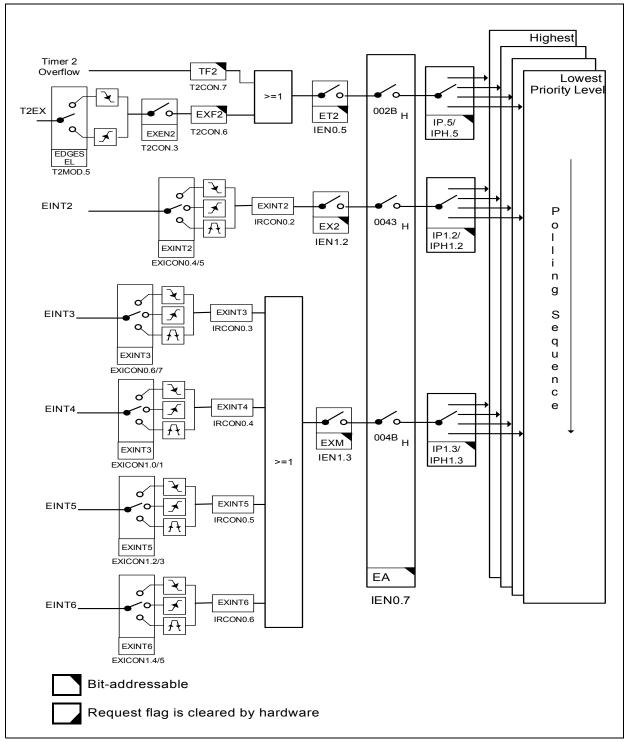

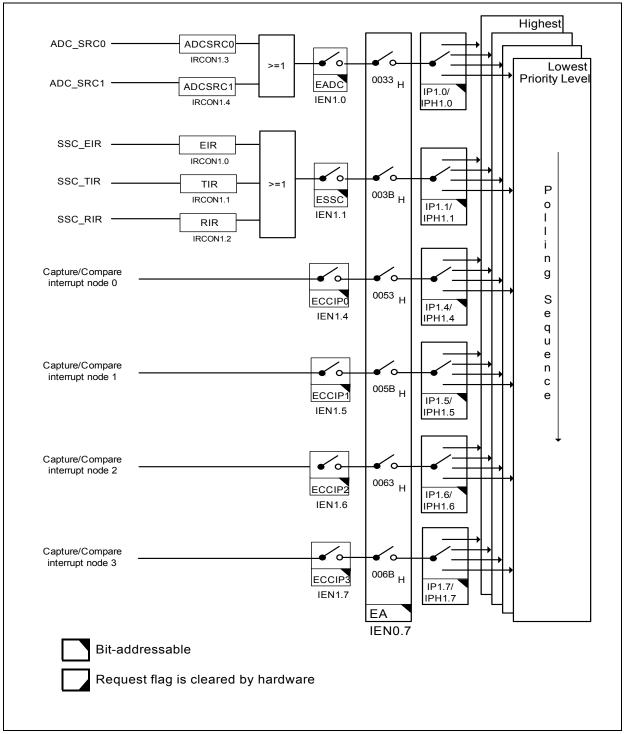

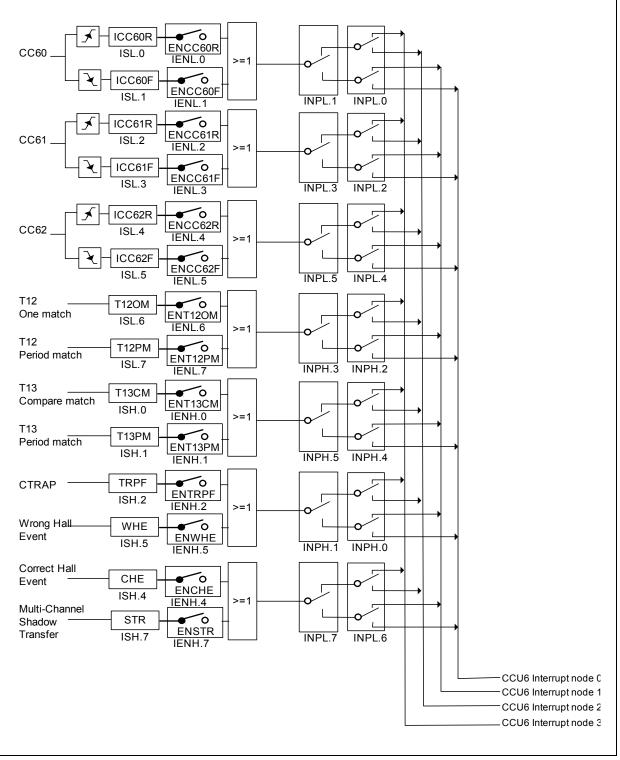

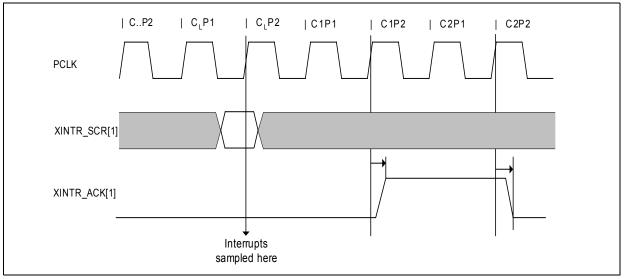

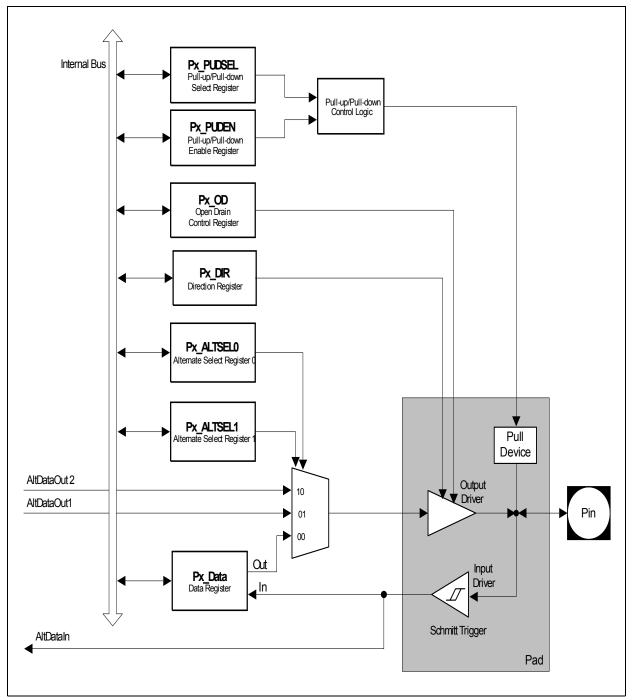

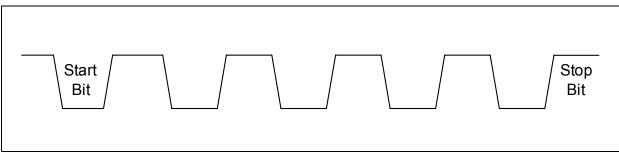

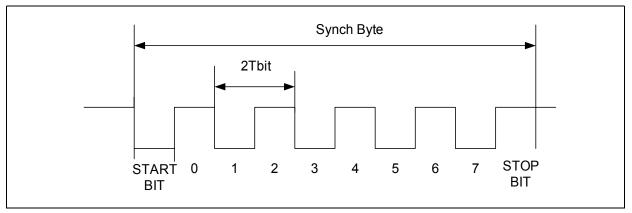

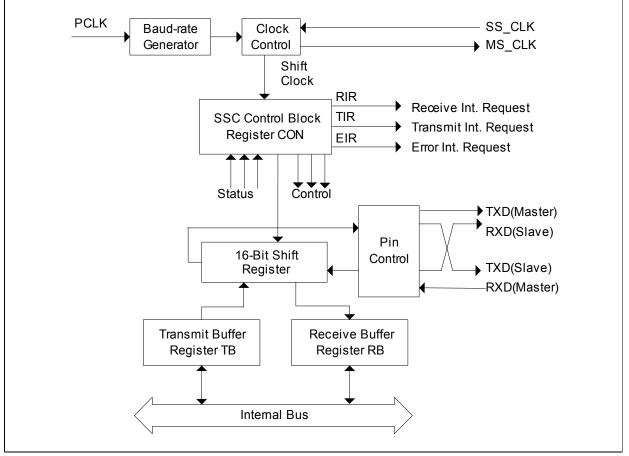

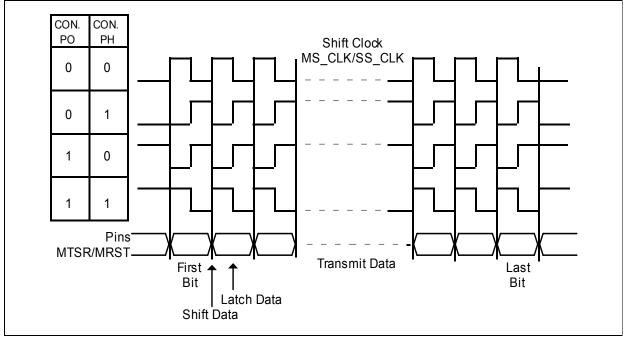

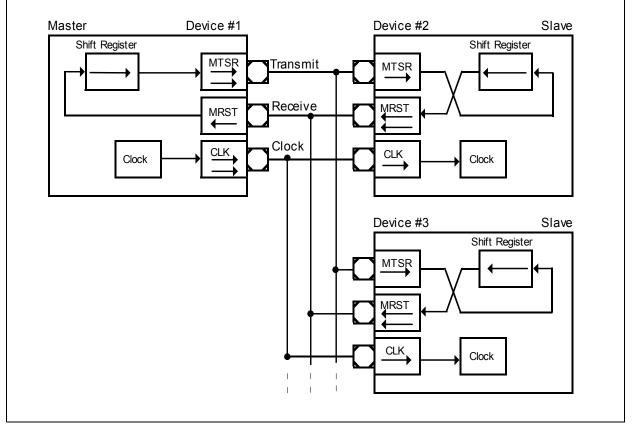

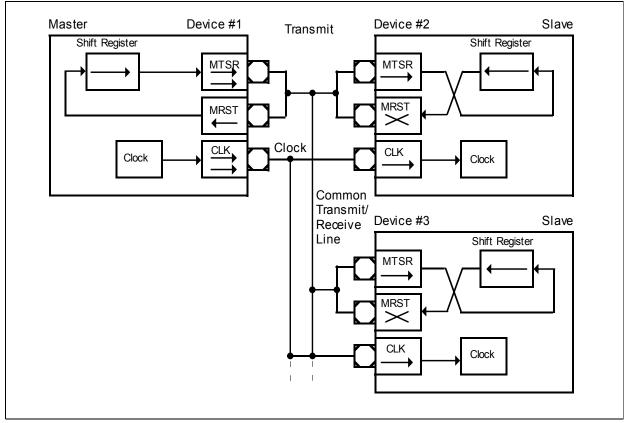

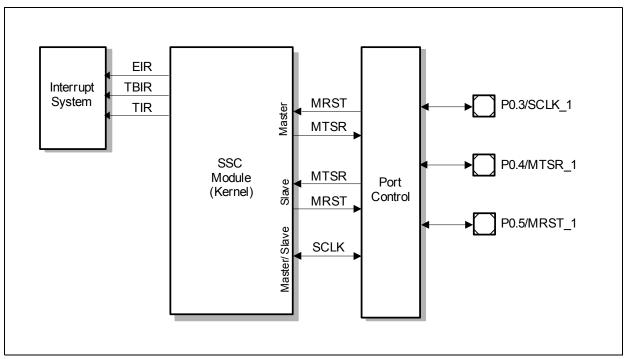

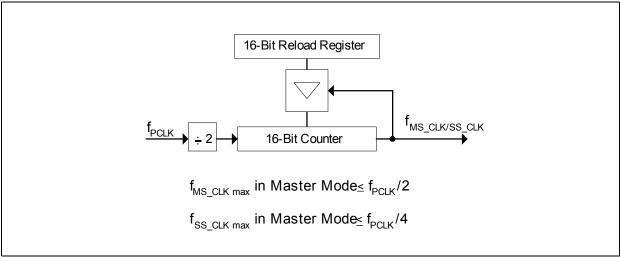

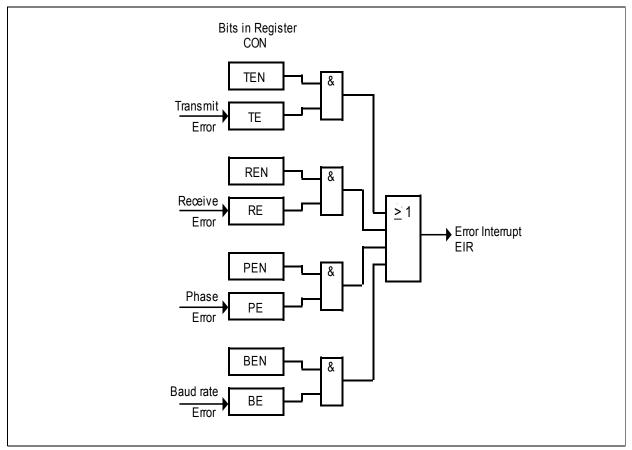

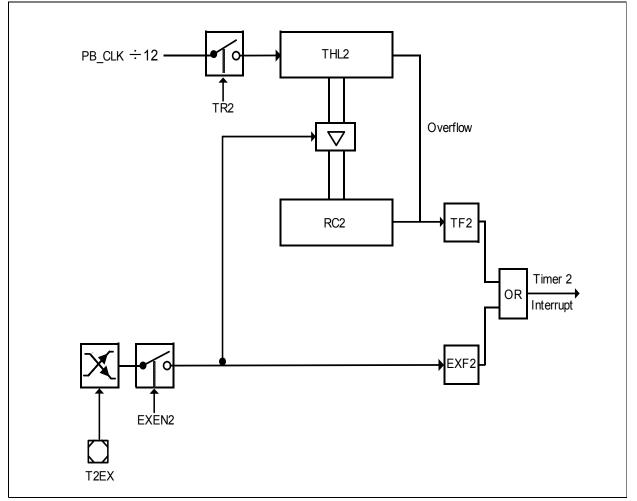

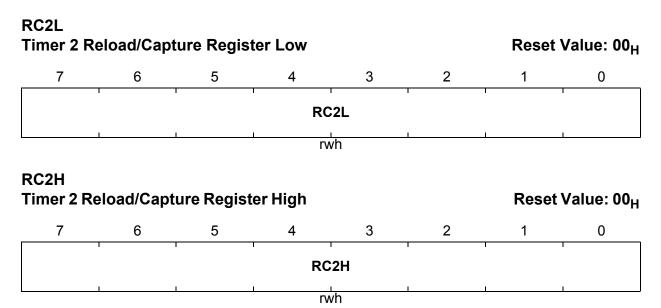

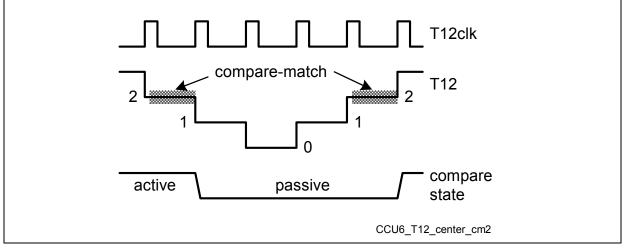

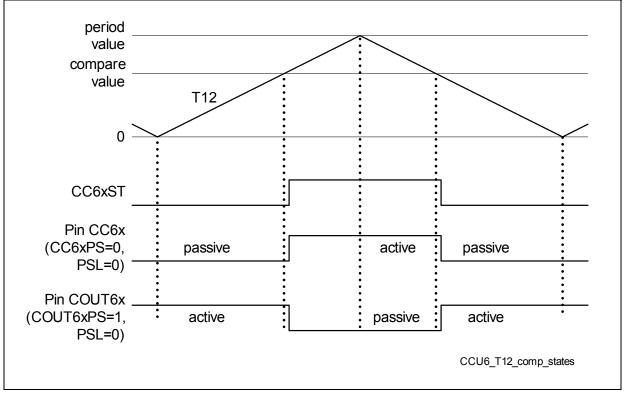

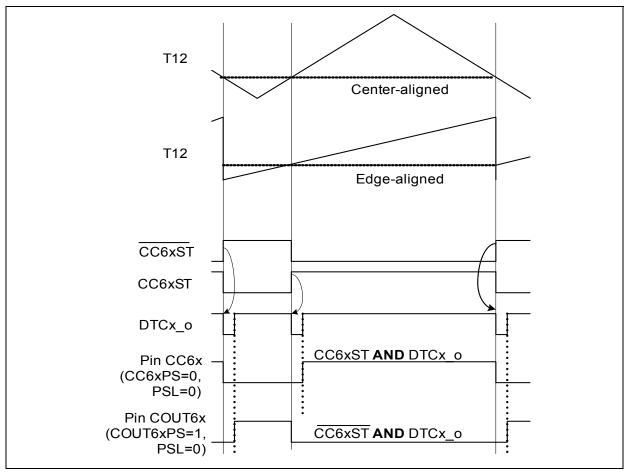

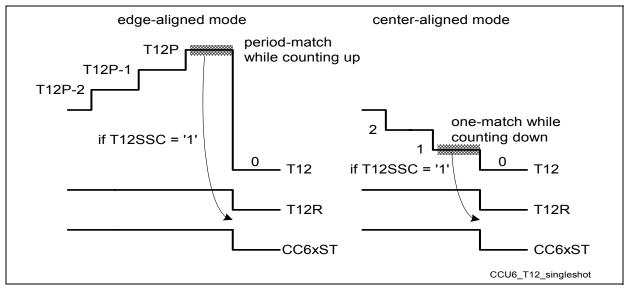

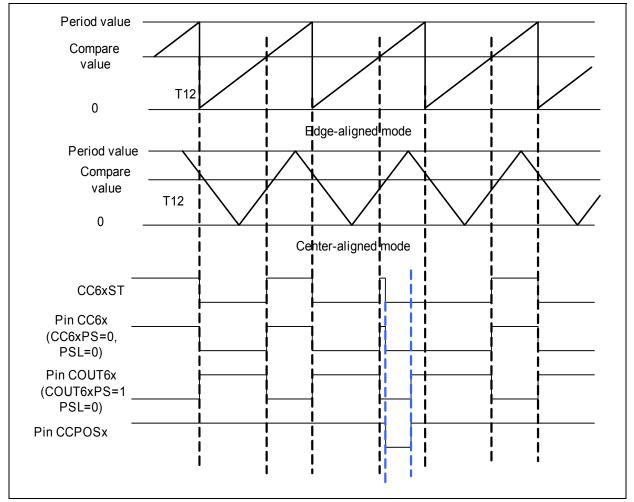

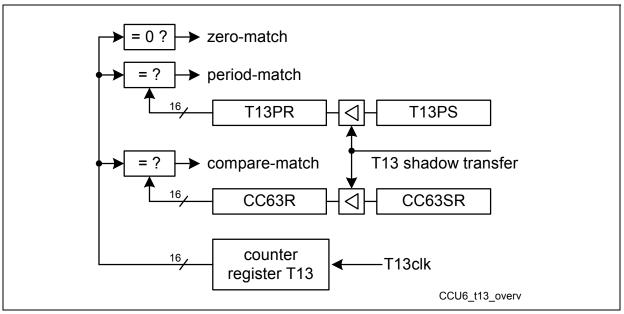

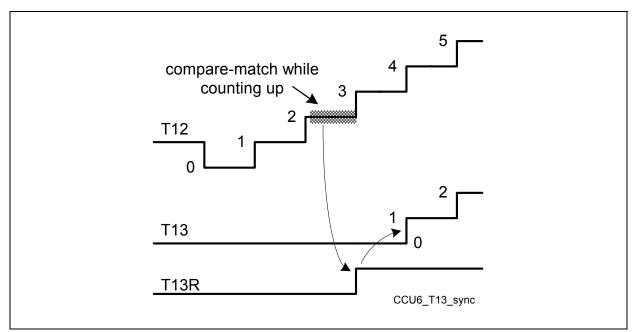

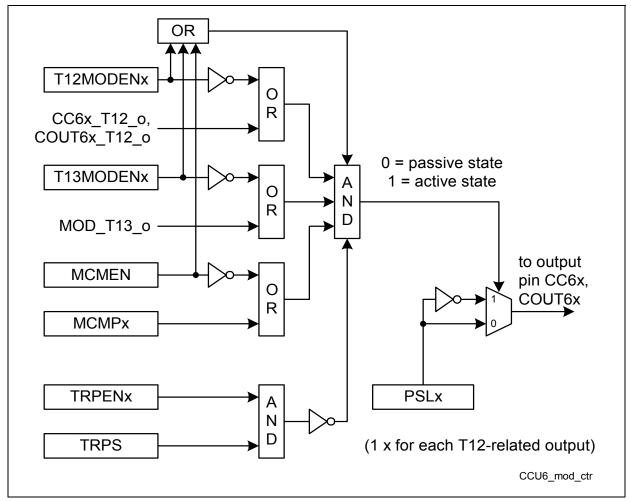

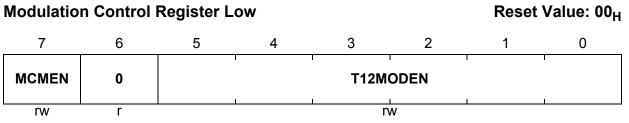

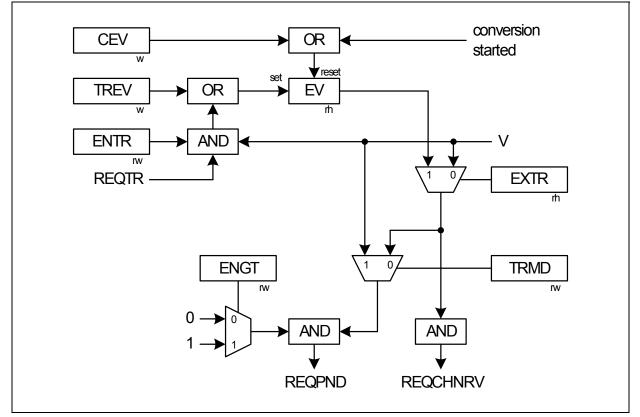

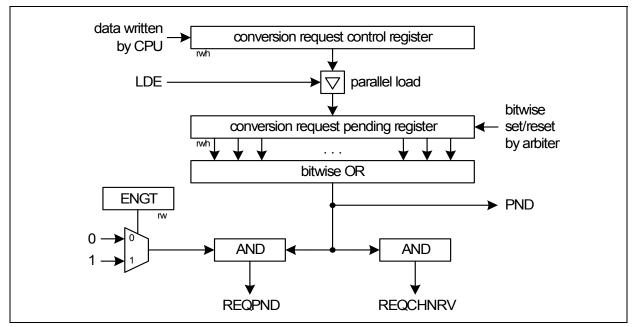

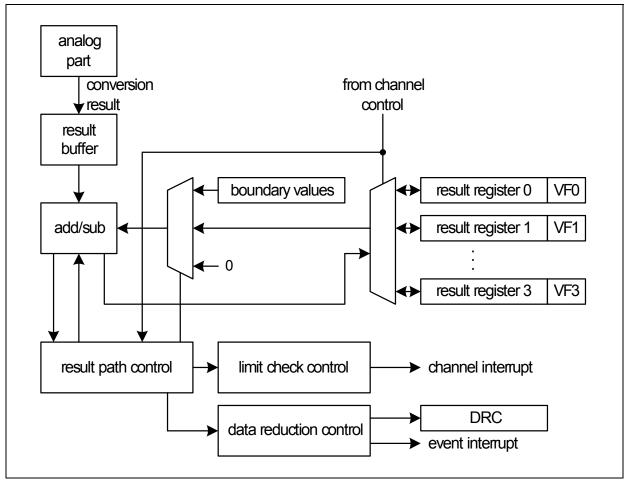

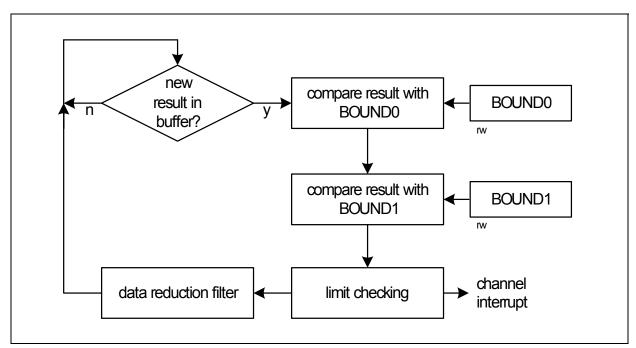

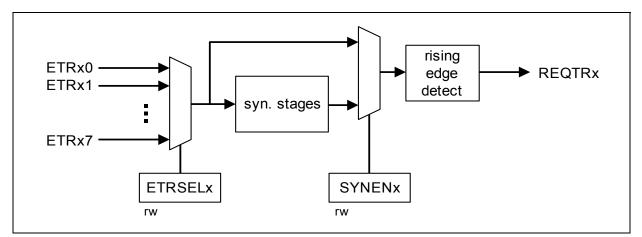

|--------------|-----------|-------|------------------------------------|------|----|--|