## 8XC51RA/RB/RC Hardware Description

February 1995

Order Number: 272668-001

Information in this document is provided in connection with Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel retains the right to make changes to these specifications at any time, without notice. Microcomputer Products may have minor variations to this specification known as errata.

\*Other brands and names are the property of their respective owners.

†Since publication of documents referenced in this document, registration of the Pentium, OverDrive and iCOMP trademarks has been issued to Intel Corporation.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 7641 Mt. Prospect, IL 60056-7641

or call 1-800-879-4683

COPYRIGHT © INTEL CORPORATION, 1996

## 8XC51RA/RB/RC HARDWARE DESCRIPTION

| CONTENTS PAGE                                                        |

|----------------------------------------------------------------------|

| 1.0 INTRODUCTION 1                                                   |

| 2.0 MEMORY ORGANIZATION 1   2.1 Program Memory 1   2.2 Data Memory 1 |

| 3.0 SPECIAL FUNCTION<br>REGISTERS 4                                  |

| 4.0 PORT STRUCTURES AND<br>OPERATION6                                |

| 4.1 I/O Configurations                                               |

| 4.2 Writing to a Port                                                |

| 4.3 Port Loading and Interfacing                                     |

| 4.4 Read-Modify-Write Feature                                        |

| 4.5 Accessing External Memory9                                       |

| 5.0 TIMERS/COUNTERS 11                                               |

| 5.1 Timer 0 and Timer 1 11                                           |

| 5.2 Timer 2 14                                                       |

| 6.0 SERIAL INTERFACE                                                 |

| 6.1 Framing Error Detection                                          |

| 6.2 Multiprocessor Communications 19                                 |

| 6.3 Automatic Address Recognition 19                                 |

| 6.4 Baud Rates 25                                                    |

| 6.5 Using Timer 1 to Generate Baud<br>Rates 25                       |

| 6.6 Using Timer 2 to Generate Baud<br>Rates 25                       |

## CONTENTS

| 7.0 HARDWARE WATCHDOG TIMER<br>(ONE-TIME ENABLED WITH RESET- |      |

|--------------------------------------------------------------|------|

| OUT)                                                         | . 23 |

| 7.1 Using the WDT                                            | . 23 |

| 7.2 WDT during Power Down and Idle                           | . 23 |

| 8.0 INTERRUPTS                                               | . 24 |

| 8.1 External Interrupts                                      | . 25 |

| 8.2 Timer Interrupts                                         | . 25 |

| 8.3 Serial Port Interrupt                                    | . 25 |

| 8.4 Interrupt Enable                                         | . 25 |

| 8.5 Priority Level Structure                                 | . 31 |

| 8.6 Response Time                                            | . 29 |

| 9.0 RESET                                                    | . 29 |

| 9.1 Power-On Reset                                           | . 30 |

| 10.0 POWER-SAVING MODES OF<br>OPERATION                      | . 30 |

| 10.1 Idle Mode                                               |      |

| 10.2 Power Down Mode                                         |      |

| 10.3 Power Off Flag                                          | . 32 |

| 11.0 ALE DISABLE                                             | . 32 |

| 12.0 EPROM VERSIONS                                          | . 32 |

| 13.0 PROGRAM MEMORY LOCK                                     | . 32 |

| 14.0 ONCE MODE                                               | . 33 |

| 15.0 ON-CHIP OSCILLATOR                                      | . 34 |

| 16.0 CPU TIMING                                              | . 35 |

Table 1. C51RX Family of Microcontrollers

## intel

## **1.0 INTRODUCTION**

The 8XC51RA/RB/RC is a highly integrated 8-bit microcontroller based on the MCS® 51 architecture. As a member of the MCS 51 family, the 8XC51RA/RB/RC is optimized for control applications. Its key features are 512 bytes on-chip RAM and watchdog timer. Also included are an enhanced serial port for multi-processor communications, an up/down timer/counter and enhanced program lock scheme for the on-chip program memory. Since the 8XC51RA/RB/RC products are CHMOS, they have two software selectable reduced power modes: Idle Mode and Power Down Mode.

The 8XC51RA/RB/RC uses the standard 8051 instruction set and is pin-for-pin compatible with the existing MCS 51 family of products.

This document presents a comprehensive description of the on-chip hardware features of the 8XC51RA/RB/ RC. It begins with a discussion of the on-chip memory and then discusses each of the peripherals listed below.

- 512 Bytes On-Chip RAM

- Hardware Watchdog Timer (One-Time Enabled with Reset-Out)

- ALE Disable/Enable

- Four 8-Bit Bidirectional Parallel Ports

- Three 16-Bit Timer/Counters with

- One Up/Down Timer/Counter

- Clock Out

- Full-Duplex Programmable Serial Port with

- Framing Error Detection

- Automatic Address Recognition

- Interrupt Structure with

- Seven Interrupt Sources

- Four Priority Levels

- Power-Saving Modes

- Idle Mode

- Power Down Mode

- Three-Level Program Lock System

Table 1 summarizes the product names and memory differences of the various 8XC51RA/RB/RC products currently available. Throughout this document, the products will generally be referred to as the C51RX.

| ROM<br>Device | EPROM<br>Version | ROMIess<br>Version | ROM/<br>EPROM<br>Bytes | RAM<br>Bytes |

|---------------|------------------|--------------------|------------------------|--------------|

| 83C51RA       | 87C51RA          | 80C51RA            | 8K                     | 512          |

| 83C51RB       | 87C51RB          | 80C51RA            | 16K                    | 512          |

| 83C51RC       | 87C51RC          | 80C51RA            | 32K                    | 512          |

### 2.0 MEMORY ORGANIZATION

All MCS-51 devices have a separate address space for Program and Data Memory. Up to 64 Kbytes each of external Program and Data Memory can be addressed.

### 2.1 Program Memory

If the  $\overline{EA}$  pin is connected to V<sub>SS</sub>, all program fetches are directed to external memory. On the 83C51RA (or 87C51RA), if the  $\overline{EA}$  pin is connected to V<sub>CC</sub>, then program fetches to addresses 0000H through 1FFFH are directed to internal ROM and fetches to addresses 2000H through FFFFH are to external memory.

On the 83C51RB (or 87C51RB) if  $\overline{EA}$  is connected to VCC, program fetches to addresses 0000H through 3FFFH are directed to internal ROM, and fetches to addresses 4000H through FFFFH are to external memory.

On the 83C51RC (or 87C51RC) if  $\overline{\text{EA}}$  is connected to V<sub>CC</sub>, program fetches to addresses 0000H through 7FFFH are directed to internal ROM or EPROM and fetches to addresses 8000H through FFFFH are to external memory.

### 2.2 Data Memory

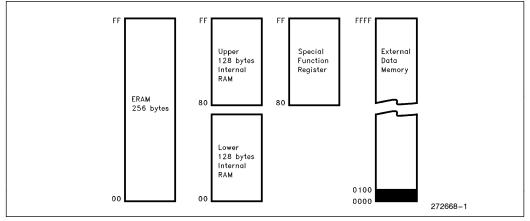

The C51RX has internal data memory that is mapped into four separate segments: the lower 128 bytes of RAM, upper 128 bytes of RAM, 128 bytes special function register (SFR) and 256 bytes expanded RAM (ERAM).

The four segments are:

- 1. The Lower 128 bytes of RAM (addresses 00H to 7FH) are directly and indirectly addressable.

- 2. The Upper 128 bytes of RAM (addresses 80H to FFH) are indirectly addressable only.

- 3. The Special Function Registers, SFRs, (addresses 80H to FFH) are directly addressable only.

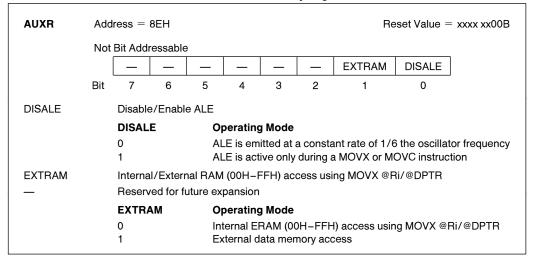

- 4. The 256-bytes expanded RAM (ERAM, 00H– FFH) are indirectly accessed by move external instruction, MOVX, and with the EXTRAM bit cleared.

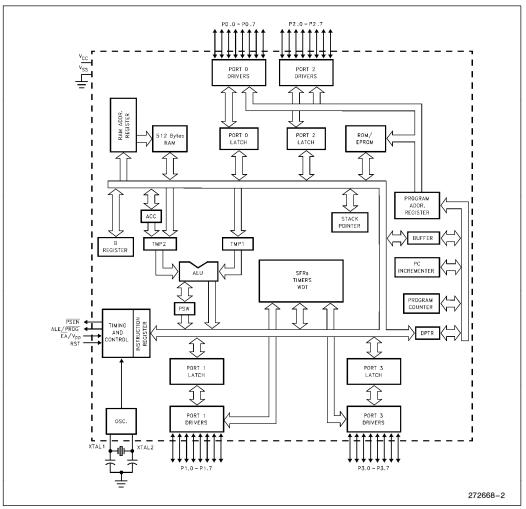

Figure 1. 8XC51RA/RB/RC Functional Block Diagram

The Lower 128 bytes can be accessed by either direct or indirect addressing. The Upper 128 bytes can be accessed by indirect addressing only. The Upper 128 bytes occupy the same address space as the SFR. That means they have the same address, but are physically separate from SFR space.

When an instruction accesses an internal location above address 7FH, the CPU knows whether the access is to the upper 128 bytes of data RAM or to SFR space by the addressing mode used in the instruction. Instructions that use direct addressing access SFR space. For example:

#### MOV 0A0H, #data

accesses the SFR at location 0A0H (which is P2). Instructions that use indirect addressing access the Upper 128 bytes of data RAM. For example:

#### MOV @R0, #data

where R0 contains 0A0H, accesses the data byte at address 0A0H, rather than P2 (whose address is 0A0H).

The 256 bytes ERAM can be accessed by indirect addressing, with EXTRAM bit cleared and MOVX instructions. This part of memory is physically located on-chip, logically occupies the first 256-bytes of external data memory.

Table 2. AUXR: Auxiliary Register

Figure 2. Internal and External Data Memory Address Space with EXTRAM = 0

With EXTRAM = 0, the ERAM is indirectly addressed, using the MOVX instruction in combination with any of the registers R0, R1 of the selected bank or DPTR. An access to ERAM will not affect ports P0, P2, P3.6 (WR#) and P3.7 (RD#). For example, with EXTRAM = 0,

#### MOVX @R0,#data

where R0 contains 0A0H, access the ERAM at address 0A0H rather than external memory. An access to external data memory locations higher than FFH (i.e. 0100H to FFFFH) will be performed with the MOVX DPTR instructions in the same way as in the standard MCS<sup>®</sup> 51, so with P0 and P2 as data/address bus, and P3.6 and P3.7 as write and read timing signals. Refer to Figure 2.

With EXTRAM = 1, MOVX @Ri and MOVX @DPTR will be similar to the standard MCS<sup>®</sup> 51. MOVX @Ri will provide an eight-bit address multiplexed with data on PortO and any output port pins can be used to output higher order address bits. This is to provide the external paging capability. MOVX @DPTR will generate a sixteen-bit address. Port2 outputs the high-order eight address bits (the contents of DPH) while PortO multiplexes the low-order eight address bits (DPL) with data. MOVX @Ri and MOVX @DPTR will generate either read or write signals on P3.6 (#WR) and P3.7 (#RD).

The stack pointer (SP) may be located anywhere in the 256 bytes RAM (lower and upper RAM) internal data memory. The stack may not be located in the ERAM.

### 3.0 SPECIAL FUNCTION REGISTERS

A map of the on-chip memory area called the SFR (Special Function Register) space is shown in Table 3.

Note that not all of the addresses are occupied. Unoccupied addresses are not implemented on the chip. Read accesses to these addresses will in general return random data, and write accesses will have no effect.

User software should not write 1s to these unimplemented locations, since they may be used in future MCS-51 products to invoke new features. In that case the reset or inactive values of the new bits will always be 0, and their active values will be 1. The functions of the SFRs are outlined below. More information on the use of specific SFRs for each peripheral is included in the description of that peripheral.

Accumulator: ACC is the Accumulator register. The mnemonics for Accumulator-Specific instructions, however, refer to the Accumulator simply as A.

| 0F8H |                   |                   |                    |                    |                 |                 |                    |                  | 0FFH |

|------|-------------------|-------------------|--------------------|--------------------|-----------------|-----------------|--------------------|------------------|------|

| 0F0H | B<br>00000000     |                   |                    |                    |                 |                 |                    |                  | 0F7H |

| 0E8H |                   |                   |                    |                    |                 |                 |                    |                  | 0EFH |

| 0E0H | ACC<br>00000000   |                   |                    |                    |                 |                 |                    |                  | 0E7H |

| 0D8H |                   |                   |                    |                    |                 |                 |                    |                  | 0DFH |

| 0D0H | PSW<br>00000000   |                   |                    |                    |                 |                 |                    |                  | 0D7H |

| 0C8H | T2CON<br>00000000 | T2MOD<br>XXXXXX00 | RCAP2L<br>00000000 | RCAP2H<br>00000000 | TL2<br>00000000 | TH2<br>00000000 |                    |                  | 0CFH |

| 0C0H |                   |                   |                    |                    |                 |                 |                    |                  | 0C7H |

| 0B8H | IP<br>XX000000    | SADEN<br>00000000 |                    |                    |                 |                 |                    |                  | 0BFH |

| 0B0H | P3<br>11111111    |                   |                    |                    |                 |                 |                    | IPH<br>XX000000  | 0B7H |

| 0A8H | IE<br>0X000000    | SADDR<br>00000000 |                    |                    |                 |                 |                    |                  | 0AFH |

| 0A0H | P2<br>11111111    |                   |                    |                    |                 |                 | WDTRST<br>XXXXXXXX |                  | 0A7H |

| 98H  | SCON<br>00000000  | SBUF<br>XXXXXXXX  |                    |                    |                 |                 |                    |                  | 9FH  |

| 90H  | P1<br>11111111    |                   |                    |                    |                 |                 |                    |                  | 97H  |

| 88H  | TCON<br>00000000  | TMOD<br>00000000  | TL0<br>00000000    | TL1<br>00000000    | TH0<br>00000000 | TH1<br>00000000 | AUXR<br>XXXXXX00   |                  | 8FH  |

| 80H  | P0<br>11111111    | SP<br>00000111    | DPL<br>00000000    | DPH<br>00000000    |                 |                 |                    | PCON<br>00000000 | 87H  |

#### Table 3. 8XC51RA/RB/RC SFR Map and Reset Values

| PSW        | Addre                          | ess = OC                       | 00H                                                   |          |                                                          |                   |       | Reset Value = 0000 0000B |          |       |

|------------|--------------------------------|--------------------------------|-------------------------------------------------------|----------|----------------------------------------------------------|-------------------|-------|--------------------------|----------|-------|

|            | Bit Ac                         | ddressab                       | le                                                    |          |                                                          |                   |       |                          |          |       |

|            |                                | CY                             | AC                                                    | F0       | RS1                                                      | RS0               | OV    | _                        | Р        | ]     |

|            | Bit                            | 7                              | 6                                                     | 5        | 4                                                        | 3                 | 2     | 1                        | 0        | -     |

| Symbol     | Funct                          | tion                           |                                                       |          |                                                          |                   |       |                          |          |       |

| CY         | Carry                          | flag.                          |                                                       |          |                                                          |                   |       |                          |          |       |

| AC         | Auxilia                        | ary Carry                      | flag. (For                                            | BCD Op   | erations)                                                |                   |       |                          |          |       |

| F0         | Flag 0                         | ). (Availa                     | ble to the                                            | user for | general p                                                | ourposes)         | ).    |                          |          |       |

| RS1<br>RS0 | •                              |                                | select bit<br>select bit                              |          |                                                          |                   |       |                          |          |       |

|            | <b>RS1</b><br>0<br>0<br>1<br>1 | <b>RS0</b><br>0<br>1<br>0<br>1 | <b>Workir</b><br>Bank 0<br>Bank 1<br>Bank 2<br>Bank 3 |          | t <b>er Bank</b><br>(00H–0<br>(08H–0<br>(10H–1<br>(18H–1 | 7H)<br>FH)<br>7H) | dress |                          |          |       |

| OV         | Overfl                         | low flag.                      |                                                       |          |                                                          |                   |       |                          |          |       |

| _          | User o                         | definable                      | flag.                                                 |          |                                                          |                   |       |                          |          |       |

| Ρ          |                                |                                | /cleared<br>e" bits in                                |          |                                                          |                   |       | to indicat               | e an odd | /even |

**B Register:** The B register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

**Stack Pointer:** The Stack Pointer Register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. The stack may reside anywhere in on-chip RAM. On reset, the Stack Pointer is initialized to 07H causing the stack to begin at location 08H.

**Data Pointer:** The Data Pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address, but it may be manipulated as a 16-bit register or as two independent 8-bit registers.

**Program Status Word:** The PSW register contains program status information as detailed in Table 4.

**Ports 0 to 3 Registers:** P0, P1, P2, and P3 are the SFR latches of Port 0, Port 1, Port 2, and Port 3 respectively.

**Timer Registers:** Register pairs (TH0, TL0), (TH1, TL1), and (TH2, TL2) are the 16-bit count registers for Timer/Counters 0, 1, and 2 respectively. Control and status bits are contained in registers TCON and TMOD

for Timers 0 and 1 and in registers T2CON and T2MOD for Timer 2. The register pair (RCAP2H, RCAP2L) are the capture/reload registers for Timer 2 in 16-bit capture mode or 16-bit auto-reload mode.

Serial Port Registers: The Serial Data Buffer, SBUF, is actually two separate registers: a transmit buffer and a receive buffer register. When data is moved to SBUF, it goes to the transmit buffer where it is held for serial transmission. (Moving a byte to SBUF initiates the transmission). When data is moved from SBUF, it comes from the receive buffer. Register SCON contains the control and status bits for the Serial Port. Registers SADDR and SADEN are used to define the Given and the Broadcast addresses for the Automatic Address Recognition feature.

**Interrupt Registers:** The individual interrupt enable bits are in the IE register. Two priorities can be set for each of the 7 interrupts in the IP register.

**Power Control Register:** PCON controls the Power Reduction Modes. Idle and Power Down Modes.

WatchDog Timer ReSet: (WDTRST) register is used to keep the watchdog timer from periodically resetting the part.

### 4.0 PORT STRUCTURES AND OPERATION

All four ports in the C51RX are bidirectional. Each consists of a latch (Special Function Registers P0 through P3), an output driver, and an input buffer.

The output drivers of Ports 0 and 2, and the input buffers of Port 0, are used in accesses to external memory. In this application, Port 0 outputs the low byte of the external memory address, time-multiplexed with the byte being written or read. Port 2 outputs the high byte of the external memory address when the address is 16 bits wide. Otherwise the Port 2 pins continue to emit the P2 SFR content.

All the Port 1 and Port 3 pins are multifunctional. They are not only port pins, but also serve the functions of various special features as listed in Table 5.

The alternate functions can only be activated if the corresponding bit latch in the port SFR contains a 1. Otherwise the port pin is stuck at 0.

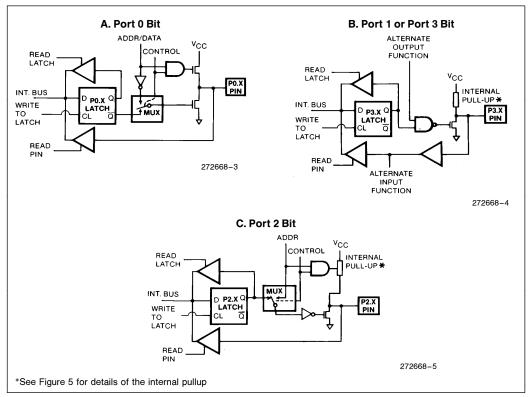

### 4.1 I/O Configurations

Figure 3 shows a functional diagram of a typical bit latch and I/O buffer in each of the four ports. The bit latch (one bit in the port's SFR) is represented as a Type D flip-flop, which clocks in a value from the internal bus in response to a "write to latch" signal from the CPU. The Q output of the flip-flop is placed on the internal bus in response to a "read latch" signal from the CPU. The level of the port pin itself is placed on the internal bus in response to a "read pin" signal from the CPU. Some instructions that read a port activate the "read latch" signal, and others activate the "read pin" signal. See the Read-Modify-Write Feature section. As shown in Figure 3, the output drivers of Ports 0 and 2 are switchable to an internal ADDRESS and AD-DRESS/DATA bus by an internal CONTROL signal for use in external memory accesses. During external memory accesses, the P2 SFR remains unchanged, but the P0 SFR gets 1s written to it.

#### **Table 5. Alternate Port Functions**

| Port Pin              | Alternate Function                                   |

|-----------------------|------------------------------------------------------|

| P0.0/AD0-<br>P0.7/AD7 | Multiplexed Byte of Address/Data for External Memory |

| P1.0/T2               | Timer 2 External Clock Input/Clock-<br>Out           |

| P1.1/T2EX             | Timer 2 Reload/Capture/Direction<br>Control          |

| P2.0/A8-              | High Byte of Address for External                    |

| P2.7/A15              | Memory                                               |

| P3.0/RXD              | Serial Port Input                                    |

| P3.1/TXD              | Serial Port Output                                   |

| P3.2/INTO             | External Interrupt 0                                 |

| P3.3/INT              | External Interrupt 1                                 |

| P3.4/T0               | Timer 0 External Clock Input                         |

| P3.5/T1               | Timer 1 External Clock Input                         |

| P3.6/WR               | Write Strobe for External Memory                     |

| P3.7/RD               | Read Strobe for External Memory                      |

Figure 3. C51RX Port Bit Latches and I/O Buffers

Also shown in Figure 3 is that if a P1 or P3 latch contains a 1, then the output level is controlled by the signal labeled "alternate output function." The actual pin level is always available to the pin's alternate input function, if any.

Ports 1, 2, and 3 have internal pullups. Port 0 has open drain outputs. Each I/O line can be independently used as an input or an output (Ports 0 and 2 may not be used as general purpose I/O when being used as the AD-DRESS/DATA BUS). To be used as an input, the port bit latch must contain a 1, which turns off the output driver FET. On Ports 1, 2, and 3, the pin is pulled high by the internal pullup, but can be pulled low by an external source.

Port 0 differs from the other ports in not having internal pullups. The pullup FET in the P0 output driver (see Figure 3) is used only when the Port is emitting 1s during external memory accesses. Otherwise the pullup FET is off. Consequently P0 lines that are being used as output port lines are open drain. Writing a 1 to the bit latch leaves both output FETs off, which floats the pin and allows it to be used as a high-impedance input. Because Ports 1 through 3 have fixed internal pullups they are sometimes call "quasi-bidirectional" ports. When configured as inputs they pull high and will source current (IIL in the data sheets) when externally pulled low. Port 0, on the other hand, is considered "true" bidirectional, because it floats when configured as an input.

All the port latches have 1s written to them by the reset function. If a 0 is subsequently written to a port latch, it can be reconfigured as an input by writing a 1 to it.

### 4.2 Writing to a Port

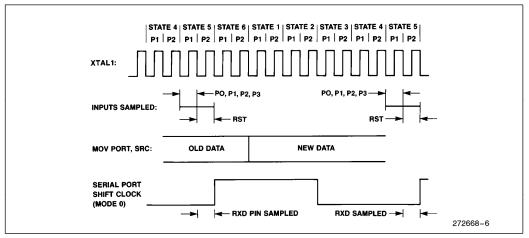

In the execution of an instruction that changes the value in a port latch, the new value arrives at the latch during State 6 Phase 2 of the final cycle of the instruction. However, port latches are in fact sampled by their output buffers only during Phase 1 of any clock period. (During Phase 2 the output buffer holds the value it saw during the previous Phase 1). Consequently, the new value in the port latch won't actually appear at the output pin until the next Phase 1, which will be at S1P1 of the next machine cycle. Refer to Figure 4. For more information on internal timings refer to the CPU Timing section.

Figure 4. Port Operation

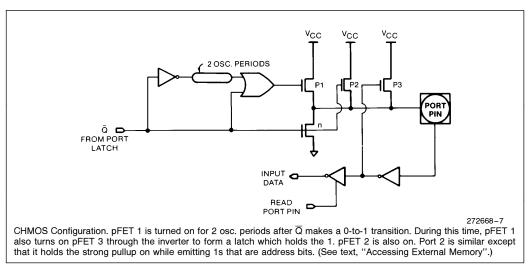

If the change requires a 0-to-1 transition in Ports 1, 2, and 3, an additional pullup is turned on during S1P1 and S1P2 of the cycle in which the transition occurs. This is done to increase the transition speed. The extra pullup can source about 100 times the current that the normal pullup can. The internal pullups are field-effect transistors, not linear resistors. The pull-up arrangements are shown in Figure 5.

The pullup consists of three pFETs. Note that an n-channel FET (nFET) is turned on when a logical 1 is applied to its gate, and is turned off when a logical 0 is applied to its gate. A p-channel FET (pFET) is the opposite: it is on when its gate sees a 0, and off when its gate sees a 1.

pFET 1 in is the transistor that is turned on for 2 oscillator periods after a 0-to-1 transition in the port latch. A 1 at the port pin turns on pFET3 (a weak pull-up), through the invertor. This invertor and pFET form a latch which hold the 1.

If the pin is emitting a 1, a negative glitch on the pin from some external source can turn off pFET3, causing the pin to go into a float state. pFET2 is a very weak pullup which is on whenever the nFET is off, in traditional CMOS style. It's only about  $\frac{1}{10}$  the strength of pFET3. Its function is to restore a 1 to the pin in the event the pin had a 1 and lost it to a glitch.

Figure 5. Ports 1 and 3 Internal Pullup Configurations

### 8XC51RA/RB/RC HARDWARE DESCRIPTION

## intel

## 4.3 Port Loading and Interfacing

The output buffers of Ports 1, 2, and 3 can each sink 1.6 mA at 0.45 V. These port pins can be driven by open-collector and open-drain outputs although 0-to-1 transitions will not be fast since there is little current pulling the pin up. An input 0 turns off pullup pFET3, leaving only the very weak pullup pFET2 to drive the transition.

In external bus mode, Port 0 output buffers can each sink 3.2 mA at 0.45 V. However, as port pins they require external pullups to be able to drive any inputs.

See the latest revision of the data sheet for design-in information.

### 4.4 Read-Modify-Write Feature

Some instructions that read a port read the latch and others read the pin. Which ones do which? The instructions that read the latch rather than the pin are the ones that read a value, possibly change it, and then rewrite it to the latch. These are called "read-modify-write" instructions. Listed below are the read-modify-write instructions. When the destination operand is a port, or a port bit, these instructions read the latch rather than the pin:

| ANL | (logical AND, e.g., ANL P1, A)                         |

|-----|--------------------------------------------------------|

| ORL | (logical OR, e.g., ORL P2, A)                          |

| XRL | (logical EX-OR, e.g., XRL P3, A)                       |

| JBC | (jump if bit = 1 and clear bit, e.g., JBC P1.1, LABEL) |

| CPL | (complement bit, e.g., CPL P3.0)                       |

| INC | (increment, e.g., INC P2)                              |

| DEC | (decrement, e.g., DEC P2)                              |

|     |                                                        |

| DJNZ         | (decrement and jump if not zero, e.g., DJNZ P3, LABEL) |

|--------------|--------------------------------------------------------|

| MOV, PX.Y, C | (move carry bit to bit Y of Port X)                    |

| CLR PX.Y     | (clear bit Y of Port X)                                |

| SETB PX.Y    | (set bit Y of Port X)                                  |

|              |                                                        |

It is not obvious that the last three instructions in this list are read-modify-write instructions, but they are. They read the port byte, all 8 bits, modify the addressed bit, then write the new byte back to the latch.

The reason that read-modify-write instructions are directed to the latch rather than the pin is to avoid a possible misinterpretation of the voltage level at the pin. For example, a port bit might be used to drive the base of a transistor. When a 1 is written to the bit, the transistor is turned on. If the CPU then reads the same port bit at the pin rather than the latch, it will read the base voltage of the transistor and interpret it as a 0. Reading the latch rather than the pin will return the correct value of 1.

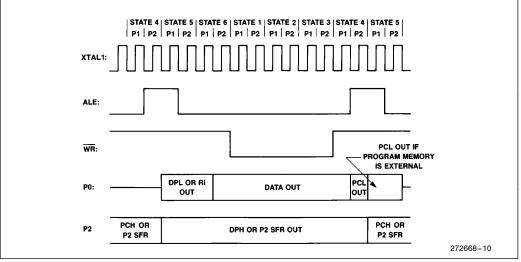

## 4.5 Accessing External Memory

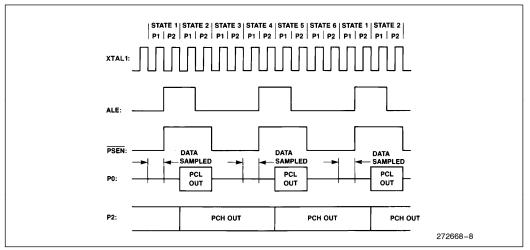

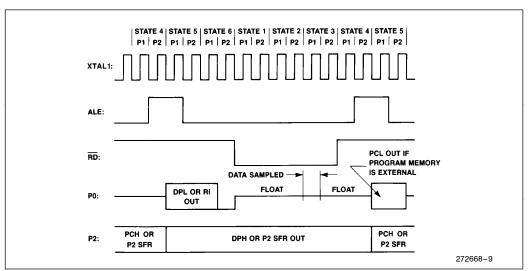

Accesses to external memory are of two types: accesses to external Program Memory and accesses to external Data Memory. Accesses to external Program Memory use signal PSEN (program store enable) as the read strobe. Accesses to external Data Memory use  $\overline{RD}$  or  $\overline{WR}$  (alternate functions of P3.7 and P3.6) to strobe the memory. Refer to Figures 6 through 8.

Fetches from external Program Memory always use a 16-bit address. Accesses to external Data Memory can use either a 16-bit address (MOVX @ DPTR) or an 8-bit address (MOVX @ Ri).

Figure 6. External Program Memory Fetches

Figure 7. External Data Memory Read Cycle

Figure 8. External Data Memory Write Cycle

When EXTRAM = 1, AUXR SFR bit 1 is set, and a 16-bit address is used, the high byte of the address comes out on Port 2, where it is held for the duration of the read or write cycle. The Port 2 drivers use the strong pullups during the entire time that they are emitting address bits that are 1s. This occurs when the MOVX @ DPTR instruction is executed. During this time the Port 2 latch (the Special Function Register) does not have to contain 1s, and the contents of the Port 2 SFR are not modified. If the external memory cycle, the undisturbed contents of the Port 2 SFR will reappear in the next cycle.

When EXTRAM = 1, AUXR SFR bit 1 is set, and an 8-bit address is being used (MOVX @ Ri), the contents of the Port 2 SFR remain at the Port 2 pins throughout the external memory cycle. In this case, Port 2 pins can be used to page the external data memory.

In either case, the low byte of the address is time-multiplexed with the data byte on Port 0. The ADDRESS/DATA signal drives both FETs in the Port 0 output buffers. Thus, in external bus mode the Port 0 pins are not open-drain outputs and do not require external pullups. The ALE (Address Latch Enable) signal should be used to capture the address byte into an external latch. The address byte is valid at the negative transition of ALE. Then, in a write cycle, the data byte to be written appears on Port 0 just before  $\overline{WR}$  is activated. In a read cycle, the incoming byte is accepted at Port 0 just before the read strobe (RD) is deactivated.

During any access to external memory, the CPU writes OFFH to the Port 0 latch (the Special Function Register), thus obliterating the information in the Port 0 SFR. Also, a MOV P0 instruction must not take place during external memory accesses. If the user writes to Port 0 during an external memory fetch, the incoming code byte is corrupted. Therefore, do not write to Port 0 if external program memory is used.

External Program Memory is accessed under two conditions:

- 1. Whenever signal  $\overline{EA}$  is active, or

- Whenever the program counter (PC) contains an address greater than 1FFFH (8K) for the 8XC51RA or 3FFFH (16K) for the 8XC51RB, or 7FFFH (32K) for the 87C51RC.

This requires that the ROMless versions have  $\overline{EA}$  wired to V<sub>SS</sub> enable the lower 8K, 16K, or 32K program bytes to be fetched from external memory.

When the CPU is executing out of external Program Memory, all 8 bits of Port 2 are dedicated to an output function and may not be used for general purpose I/O. During external program fetches they output the high byte of the PC with the Port 2 drivers using the strong pullups to emit bits that are 1s.

### 5.0 TIMERS/COUNTERS

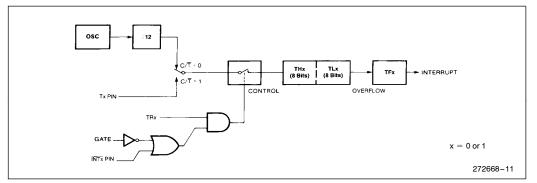

The C51RX has three 16-bit Timer/Counters: Timer 0, Timer 1, and Timer 2. Each consists of two 8-bit registers, THx and TLx, (x = 0, 1, and 2). All three can be configured to operate either as timers or event counters.

In the Timer function, the TLx register is incremented every machine cycle. Thus one can think of it as counting machine cycles. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

In the Counter function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin—T0, T1, or T2. In this function, the external input is sampled during S5P2 of every machine cycle. When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register during S3P1 of the cycle following the one in which the transition was detected. Since it takes 2 machine cycles (24 oscillator periods) to recognize a 1-to-0 transition, the maximum count rate is  $\frac{1}{24}$  of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.

In addition to the Timer or Counter selection, Timer 0 and Timer 1 have four operating modes from which to select: Modes 0 - 3. Timer 2 has three modes of operation: Capture, Auto-Reload, and Baud Rate Generator.

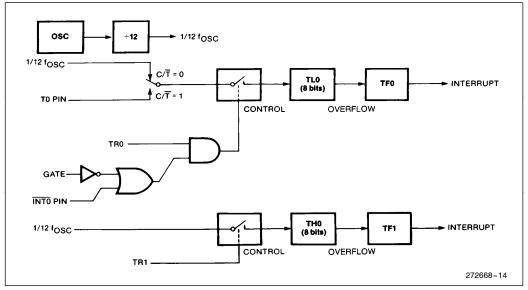

### 5.1 Timer 0 and Timer 1

The Timer or Counter function is selected by control bits  $C/\overline{T}$  in the Special Function Register TMOD (Table 5). These two Timer/Counters have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timer/Counters. Mode 3 operation is different for the two timers.

#### MODE 0

Either Timer 0 or Timer 1 in Mode 0 is an 8-bit Counter with a divide-by-32 prescaler. Figure 9 shows the Mode 0 operation for either timer.

In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFx. The counted input is enabled to the Timer when TRx = 1 and either GATE = 0 or  $\overline{INTx} = 1$ . (Setting GATE = 1 allows the Timer to be controlled by external input  $\overline{INTx}$ , to facilitate pulse width measurements). TRx and TFx are

control bits in SFR TCON (Table 7). The GATE bit is in TMOD. There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

The 13-bit register consists of all 8 bits of THx and the lower 5 bits of TLx. The upper 3 bits of TLx are indeterminate and should be ignored. Setting the run flag (TRx) does not clear these registers.

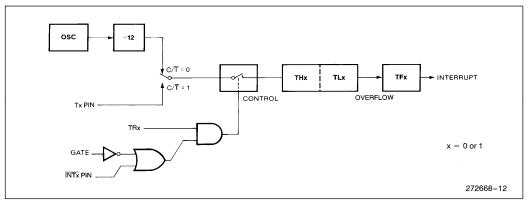

### MODE 1

Mode 1 is the same as Mode 0, except that the Timer register uses all 16 bits. Refer to Figure 10. In this mode, THx and TLx are cascaded; there is no prescaler.

### MODE 2

Mode 2 configures the Timer register as an 8-bit Counter (TLx) with automatic reload, as shown in Figure 11. Overflow from TLx not only sets TFx, but also reloads TLx with the contents of THx, which is preset by software. The reload leaves THx unchanged.

| MOD                 | )              | Add                                                       | lress =                                                                                                         | 89H                                                                                                     |                                                                                                 |                                                                                                                |                                                         |                                                                                                     | Reset                                                                      | Value =                                         | 0000 0000                |

|---------------------|----------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------|--------------------------|

|                     |                | Not                                                       | Bit Add                                                                                                         | ressable                                                                                                |                                                                                                 |                                                                                                                |                                                         |                                                                                                     |                                                                            |                                                 |                          |

|                     |                |                                                           |                                                                                                                 | TIM                                                                                                     | ER 1                                                                                            |                                                                                                                |                                                         | TIM                                                                                                 | ER 0                                                                       |                                                 |                          |

|                     |                |                                                           | GATE                                                                                                            | C/T                                                                                                     | M1                                                                                              | M0                                                                                                             | GATE                                                    | C/T                                                                                                 | M1                                                                         | M0                                              | ]                        |

|                     |                | Bit                                                       | 7                                                                                                               | 6                                                                                                       | 5                                                                                               | 4                                                                                                              | 3                                                       | 2                                                                                                   | 1                                                                          | 0                                               | -                        |

| Sym                 | bol            | Fur                                                       | oction                                                                                                          |                                                                                                         |                                                                                                 |                                                                                                                |                                                         |                                                                                                     |                                                                            |                                                 |                          |

| GAT                 | E              | Gat                                                       | ing cont                                                                                                        | rol when                                                                                                | set. Time                                                                                       | er/Counte                                                                                                      | er 0 or 1 is                                            | senabled                                                                                            | l only whi                                                                 | le INT0 o                                       | r INT1 pin               |

| C/T                 |                | whe<br>Tim                                                | enever T<br>er or Co                                                                                            | R0 or TF<br>unter Se                                                                                    | R1 control<br>1 control<br>lector. Cl                                                           | ol pin is se<br>l bit is set<br>ear for Ti                                                                     | et. When                                                | cleared, <sup>-</sup><br>ation (inp                                                                 | Timer 0 o<br>ut from in                                                    | r 1 is ena                                      | bled                     |

| C/⊤<br>M1           | MO             | whe<br>Tim<br>cloc                                        | enever T<br>er or Co                                                                                            | R0 or TF<br>unter Se<br>or Count                                                                        | R1 control<br>1 control<br>lector. Cl                                                           | ol pin is se<br>l bit is set<br>ear for Ti                                                                     | et. When o<br><br>mer opera                             | cleared, <sup>-</sup><br>ation (inp                                                                 | Timer 0 o<br>ut from in                                                    | r 1 is ena                                      | bled                     |

|                     | <b>M0</b><br>0 | whe<br>Tim<br>cloo<br><b>Op</b> e                         | enever T<br>er or Co<br>ck). Set f<br>erating l                                                                 | R0 or TF<br>unter Se<br>for Count                                                                       | R1 contro<br>1 control<br>lector. Cl<br>er operat                                               | bl pin is se<br>l bit is set<br>ear for Tii<br>ion (input                                                      | et. When o<br><br>mer opera                             | cleared, <sup>-</sup><br>ation (inp<br>or T1 inp                                                    | Timer 0 o<br>ut from in                                                    | r 1 is ena                                      | bled                     |

| M1                  |                | whe<br>Tim<br>cloo<br><b>Op</b> e<br>8-bi                 | enever T<br>er or Co<br>ck). Set f<br>erating I<br>t Timer/                                                     | R0 or TF<br>unter Se<br>or Count<br><b>Mode</b><br>Counter.                                             | R1 contro<br>1 control<br>lector. Cl<br>er operat<br>THx with                                   | bl pin is se<br>l bit is set<br>ear for Tin<br>ion (input<br>n TLx as 5                                        | et. When (<br><br>mer opera<br>t from T0 (              | cleared, <sup>-</sup><br>ation (inp<br>or T1 inp<br>caler.                                          | Timer 0 o<br>ut from in<br>ut pin).                                        | r 1 is ena<br>ternal sys                        | bled                     |

| <b>M1</b><br>0      | 0              | whe<br>Tim<br>cloc<br>8-bi<br>16-l<br>8-bi                | enever T<br>er or Co<br>ck). Set f<br>erating I<br>t Timer/<br>bit Timer<br>t auto-re                           | R0 or TF<br>unter Se<br>or Count<br><b>Mode</b><br>Counter.<br>r/Counte                                 | R1 contro<br>1 control<br>lector. Cle<br>er operat<br>THx with<br>r. THx an<br>ler/Coun         | ol pin is set<br>l bit is set<br>ear for Tin<br>ion (input<br>n TLx as 5<br>d TLx are                          | et. When o<br><br>mer opera<br>t from T0<br>5-bit presc | cleared, <sup>-</sup><br>ation (inp<br>or T1 inp<br>caler.<br>cd; there i                           | Timer 0 o<br>ut from in<br>ut pin).<br>s no pres                           | r 1 is ena<br>ternal sys<br>scaler.             | bled stem                |

| <b>M1</b><br>0<br>0 | 0<br>1         | whe<br>Tim<br>cloc<br>8-bi<br>16-l<br>8-bi<br>eac<br>(Tin | enever T<br>er or Co<br>ck). Set f<br>erating I<br>t Timer/<br>bit Timer<br>t auto-re<br>h time it<br>ner 0) TL | R0 or TF<br>unter Se<br>for Count<br>Mode<br>Counter.<br>r/Counte<br>eload Tim<br>overflow<br>0 is an 8 | R1 control<br>lector. Cl-<br>er operat<br>THx with<br>r. THx an<br>her/Coun<br>'s.<br>-bit Time | ol pin is se<br>l bit is set<br>ear for Tin<br>ion (input<br>n TLx as 5<br>d TLx are<br>ter. THx h<br>r/Counte | et. When o<br>mer opera<br>t from TO<br>5-bit presc     | cleared, <sup>-</sup><br>ation (inp<br>or T1 inp<br>caler.<br>cd; there i<br>lue which<br>ed by the | Timer 0 o<br>ut from in<br>ut pin).<br>s no pres<br>n is to be<br>standard | r 1 is ena<br>ternal sys<br>scaler.<br>reloaded | bled<br>stem<br>into TLx |

#### Table 6. TMOD: Timer/Counter Mode Control Register

Figure 9. Timer/Counter 0 or 1 in Mode 0: 13-Bit Counter

| TCON   | Addro | ess = 88        | ЗH                      |          |                         |            |            | Reset        | Value =   | 0000 0000B |  |

|--------|-------|-----------------|-------------------------|----------|-------------------------|------------|------------|--------------|-----------|------------|--|

|        | Bit A | Bit Addressable |                         |          |                         |            |            |              |           |            |  |

|        |       | TF1             | TR1                     | TF0      | TR0                     | IE1        | IT1        | IE0          | IT0       |            |  |

|        | Bit   | 7               | 6                       | 5        | 4                       | 3          | 2          | 1            | 0         |            |  |

| Symbol | Func  | tion            |                         |          |                         |            |            |              |           |            |  |

| TF1    |       |                 |                         |          | rdware o<br>rs to inter |            |            | overflow.    | Cleared   | by         |  |

| TR1    | Timer | 1 Run c         | ontrol bit.             | Set/clea | ared by so              | oftware to | o turn Tim | ner/Cour     | ter 1 on  | /off.      |  |

| TF0    |       |                 | 0                       | ,        | rdware o<br>rs to inter |            |            | ) overflow   | w. Cleare | ed by      |  |

| TR0    | Timer | 0 Run c         | ontrol bit.             | Set/clea | ared by so              | oftware to | o turn Tim | ner/Cour     | ter 0 on  | /off.      |  |

| IE1    |       | mitted of       |                         |          | when ex<br>Cleared w    |            |            |              |           | nsition-   |  |

| IT1    |       |                 | e control<br>nal interr |          | cleared b               | y softwa   | re to spe  | cify falling | g edge/lo | ow level   |  |

| IEO    |       | mitted of       | ,                       |          | when ext<br>Cleared w   |            | •          | 0            |           | nsition-   |  |

| IT0    |       |                 | e control<br>nal interr |          | cleared b               | y softwa   | re to spe  | cify falling | g edge/lo | ow level   |  |

Figure 10. Timer/Counter 0 or 1 in Mode 1: 16-Bit Counter

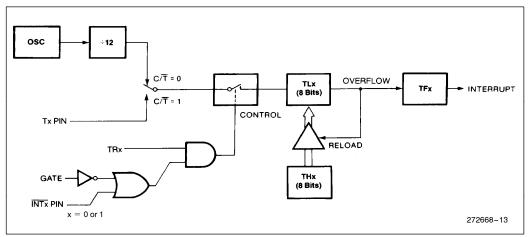

### MODE 3

Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. The logic for Mode 3 on Timer 0 is shown in Figure 12. TL0 uses the Timer 0 control bits:  $C/\overline{T}$ , GATE, TR0,  $\overline{INT0}$ , and TF0. TH0 is locked into

a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus TH0 now controls the Timer 1 interrupt.

Mode 3 is provided for applications requiring an extra 8-bit timer or counter. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in any application not requiring an interrupt.

Figure 11. Timer/Counter 1 Mode 2: 8-Bit Auto-Reload

Figure 12. Timer/Counter 0 Mode 3: Two 8-Bit Counters

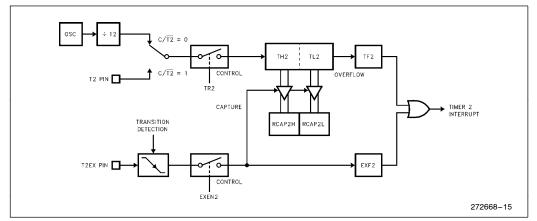

### 5.2 Timer 2

Timer 2 is a 16-bit Timer/Counter which can operate either as a timer or as an event counter. This is selected by bit  $C/\overline{T2}$  in the Special Function Register T2CON (Table 9). It has three operating modes: capture, autoreload (up or down counting), and baud rate generator. The modes are selected by bits in T2CON as shown in Table 8.

| Table 8 | . Timer 2 | Operati | ng M | odes |

|---------|-----------|---------|------|------|

|         |           |         |      |      |

| RCLK + TCLK | CP/RL2 | T2*OE | TR2 | Mode        |

|-------------|--------|-------|-----|-------------|

| 0           | 0      | 0     | 1   | 16-Bit      |

|             |        |       |     | Auto-Reload |

| 0           | 1      | 0     | 1   | 16-Bit      |

|             |        |       |     | Capture     |

| 1           | Х      | Х     | 1   | Baud_Rate   |

|             |        |       |     | Generator   |

| X           | 0      | 1     | 1   | Clock-Out   |

|             |        |       |     | on P1.0     |

| Х           | Х      | Х     | 0   | Timer Off   |

Table 9. T2CON: Timer/Counter 2 Control Register

| T2CON  | Address =                               | = 0C8H                                  |                                      |                                            |                                 |                         | Reset Va                | alue = 0000                                   | 0000B  |

|--------|-----------------------------------------|-----------------------------------------|--------------------------------------|--------------------------------------------|---------------------------------|-------------------------|-------------------------|-----------------------------------------------|--------|

|        | Bit Addres                              | sable                                   |                                      |                                            |                                 |                         |                         |                                               |        |

|        | TF2                                     | EXF2                                    | RCLK                                 | TCLK                                       | EXEN2                           | TR2                     | C/T2                    | CP/RL2                                        |        |

| В      | it 7                                    | 6                                       | 5                                    | 4                                          | 3                               | 2                       | 1                       | 0                                             |        |

| Symbol | Function                                |                                         |                                      |                                            |                                 |                         |                         |                                               |        |

| TF2    | Timer 2 ov                              |                                         |                                      |                                            |                                 | iust be cle             | eared by se             | oftware. TF2                                  | 2 will |

| EXF2   | Timer 2 ex<br>on T2EX a<br>to vector to | ternal flag<br>nd EXEN2<br>o the Time   | set when e<br>= 1. Whe<br>2 interrup | either a cap<br>n Timer 2<br>ot routine. E | pture or relo<br>interrupt is e | enabled E<br>be cleared | XF2 = 1                 | egative tran<br>will cause th<br>are. EXF2 do | e CPU  |

| RCLK   | Receive cl                              | ock flag. W<br>ock in seria             | /hen set, c                          | auses the                                  | serial port t                   | o use Tim               |                         | low pulses fo<br>erflow to be                 |        |

| TCLK   |                                         | ock in seria                            | al port Mod                          |                                            |                                 |                         |                         | flow pulses f<br>verflows to b                |        |

| EXEN2  |                                         | ansition or                             | 1 T2EX if T                          | imer 2 is n                                |                                 |                         |                         | ur as a resul<br>Il port. EXEN                |        |

| TR2    | Start/stop                              | control for                             | Timer 2. A                           | A logic 1 st                               | arts the time                   | ər.                     |                         |                                               |        |

| C/T2   |                                         | al timer (O                             | SC/12 or (                           | ÚSC/2 in b                                 | baud rate ge                    | enerator m              | node).                  |                                               |        |

| CP/RL2 | EXEN2 = negative tr                     | eload flag.<br>1. When c<br>ansitions a | When set<br>eared, aut<br>t T2EX wh  | , captures<br>to-reloads<br>ten EXEN2      | will occur o<br>will occur ei   | ther with<br>n either R | Timer 2 ov<br>CLK = 1 o | ns at T2EX if<br>verflows or<br>or TCLK = 1   |        |

### CAPTURE MODE

In the capture mode there are two options selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 is a

16-bit timer or counter which upon overflow sets bit TF2 in T2CON. This bit can then be used to generate an interrupt. If EXEN2 = 1, Timer 2 still does the above, but with the added feature that a 1-to-0 tran-

Figure 13. Timer 2 in Capture Mode

sition at external input T2EX causes the current value in the Timer 2 registers, TH2 and TL2, to be captured into registers RCAP2H and RCAP2L, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 bit, like TF2, can generate an interrupt. The capture mode is illustrated in Figure 13.

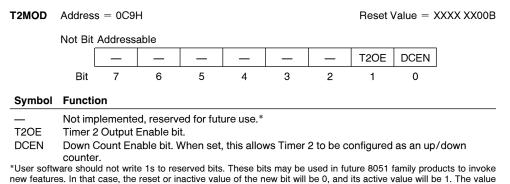

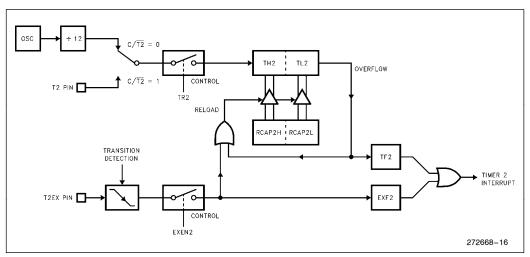

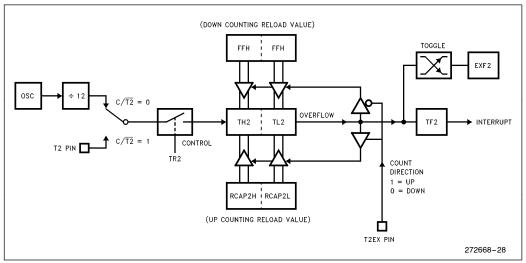

#### AUTO-RELOAD MODE (UP OR DOWN COUNTER)

Timer 2 can be programmed to count up or down when configured in its 16-bit auto-reload mode. This feature is invoked by a bit named DCEN (Down Counter Enable) located in the SFR T2MOD (see Table 10). Upon reset the DCEN bit is set to 0 so that Timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down depending on the value of the T2EX pin.

Figure 14 shows Timer 2 automatically counting up when DCEN = 0. In this mode there are two options selected by bit EXEN2 in T2CON. If EXEN2 = 0, Timer 2 counts up to 0FFFFH and then sets the TF2 bit upon overflow. The overflow also causes the timer registers to be reloaded with the 16-bit value in RCAP2H and RCAP2L. The values in RCAP2H and RCAP2L are preset by software. If EXEN2 = 1, a 16bit reload can be triggered either by an overflow or by a 1-to-0 transition at external input T2EX. This transition also sets the EXF2 bit. Either the TF2 or EXF2 bit can generate the Timer 2 interrupt if it is enabled.

#### Table 10. T2MOD: Timer 2 Mode Control Register

read from a reserved bit is indeterminate.

Figure 14. Timer 2 Auto Reload Mode (DCEN = 0)

Figure 15. Timer 2 Auto Reload Mode (DCEN = 1)

Setting the DCEN bit enables Timer 2 to count up or down as shown in Figure 15. In this mode the T2EX pin controls the direction of count. A logic 1 at T2EX makes Timer 2 count up. The timer will overflow at 0FFFFH and set the TF2 bit which can then generate an interrupt if it is enabled. This overflow also causes a the 16-bit value in RCAP2H and RCAP2L to be reloaded into the timer registers, TH2 and TL2, respectively.

A logic 0 at T2EX makes Timer 2 count down. Now the timer underflows when TH2 and TL2 equal the values stored in RCAP2H and RCAP2L. The underflow sets the TF2 bit and causes 0FFFFH to be reloaded into the timer registers.

The EXF2 bit toggles whenever Timer 2 overflows or underflows. This bit can be used as a 17th bit of resolution if desired. In this operating mode, EXF2 does not generate an interrupt.

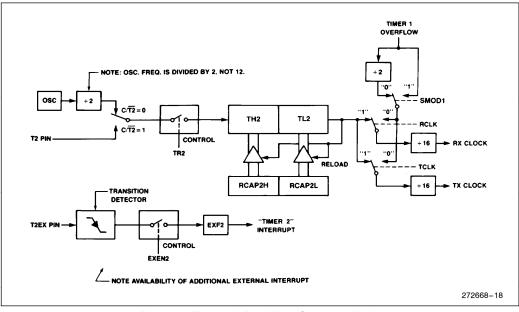

### BAUD RATE GENERATOR MODE

The baud rate generator mode is selected by setting the RCLK and/or TCLK bits in T2CON. Timer 2 in this mode will be described in conjunction with the serial port.

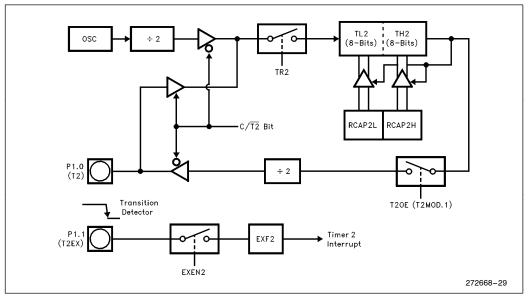

### PROGRAMMABLE CLOCK OUT

A 50% duty cycle clock can be programmed to come out on P1.0. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed (1) to input the external clock for Timer/Counter 2 or (2) to output a 50% duty cycle clock ranging from 61 Hz to 4 MHz at a 16 MHz operating frequency.

To configure the Timer/Counter 2 as a clock generator, bit C/T2 (in T2CON) must be cleared and bit T2OE in T2MOD must be set. Bit TR2 (T2CON.2) also must be set to start the timer (see Table 9 for operating modes).

The Clock-out frequency depends on the oscillator frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L) as shown in this equation:

Clock-out Frequency =

$\frac{\text{Oscillator Frequency}}{4 \times \text{(65536} - \text{RCAP2H, RCAP2L)}}$

In the Clock-Out mode Timer 2 roll-overs will not generate an interrupt. This is similar to when Timer 2 is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and Clock-out frequencies cannot be determined independently of one another since they both use the values in RCAP2H and RCAP2L.

Figure 16. Timer 2 in Clock-Out Mode

## 6.0 SERIAL INTERFACE

The serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the receive register. (However, if the first byte still hasn't been read by the time reception of the second byte is complete, one of the bytes will be lost). The serial port receive and transmit registers are both accessed through Special Function Register SBUF. Actually, SBUF is two separate registers, a transmit buffer and a receive buffer. Writing to SBUF loads the transmit register, and reading SBUF accesses a physically separate receive register.

The serial port control and status register is the Special Function Register SCON, shown in Table 11. This register contains the mode selection bits (SM0 and SM1); the SM2 bit for the multiprocessor modes (see Multiprocessor Communications section); the Receive Enable bit (REN); the 9th data bit for transmit and receive (TB8 and RB8); and the serial port interrupt bits (TI and RI). The serial port can operate in 4 modes:

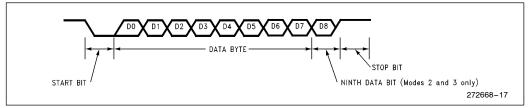

Mode 0: Serial data enters and exits through RXD. TXD outputs the shift clock. 8 bits are transmitted/received: 8 data bits (LSB first). The baud rate is fixed at 1/12 the oscillator frequency.

**Mode 1:** 10 bits are transmitted (through TXD) or received (through RXD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in Special Function Register SCON. The baud rate is variable.

Mode 2: 11 bits are transmitted (through TXD) or received (through RXD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). Refer to Figure 17. On Transmit, the 9th data bit (TB8 in SCON) can be assigned the value of 0 or 1. Or, for example, the parity bit (P in the PSW) could be moved into TB8. On receive, the 9th data bit goes into RB8 in SCON, while the stop bit is ignored. (The validity of the stop bit can be checked with Framing Error Detection.) The baud rate is programmable to either  $\frac{1}{32}$  or  $\frac{1}{64}$  the oscillator frequency.

Figure 17. Data Frame: Modes 1, 2 and 3

8XC51RA/RB/RC HARDWARE DESCRIPTION

**Mode 3:** 11 bits are transmitted (through TXD) or received (through RXD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit and a stop bit (1). In fact, Mode 3 is the same as Mode 2 in all respects except the baud rate. The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0and REN = 1. Reception is initiated in the other modes by the incoming start bit if REN = 1. For more detailed information on each serial port mode, refer to the "Hardware Description of the 8051, 8052, and 80C51."

### 6.1 Framing Error Detection

Framing Error Detection allows the serial port to check for valid stop bits in modes 1, 2, or 3. A missing stop bit can be caused, for example, by noise on the serial lines, or transmission by two CPUs simultaneously.

If a stop bit is missing, a Framing Error bit FE is set. The FE bit can be checked in software after each reception to detect communication errors. Once set, the FE bit must be cleared in software. A valid stop bit will not clear FE.

The FE bit is located in SCON and shares the same bit address as SM0. Control bit SMOD0 in the PCON register (location PCON.6) determines whether the SM0 or FE bit is accessed. If SMOD0 = 0, then accesses to SCON.7 are to SM0. If SMOD0 = 1, then accesses to SCON.7 are to FE.

### 6.2 Multiprocessor Communications

Modes 2 and 3 provide a 9-bit mode to facilitate multiprocessor comunication. The 9th bit allows the controller to distinguish between address and data bytes. The 9th bit is set to 1 for address bytes and set to 0 for data bytes. When receiving, the 9th bit goes into RB8 in SCON. When transmitting, TB8 is set or cleared in software.

The serial port can be programmed such that when the stop bit is received the serial port interrupt will be activated only if the received byte is an address byte (RB8 = 1). This feature is enabled by setting the SM2 bit in SCON. A way to use this feature in multiprocessor systems is as follows.

When the master processor wants to transmit a block of data to one of several slaves, it first sends out an address byte which identifies the target slave. Remember, an address byte has its 9th bit set to 1, whereas a data byte has its 9th bit set to 0. All the slave processors should have their SM2 bits set to 1 so they will only be interrupted by an address byte. In fact, the C51RX has an Automatic Address Recognition feature which allows only the addressed slave to be interrupted. That is, the address comparison occurs in hardware, not software. (On the 8051 serial port, an address byte interrupts all slaves for an address comparison.)

The addressed slave's software then clears its SM2 bit and prepares to receive the data bytes that will be coming. The other slaves are unaffected by these data bytes. They are still waiting to be addressed since their SM2 bits are all set.

### 6.3 Automatic Address Recognition

Automatic Address Recognition reduces the CPU time required to service the serial port. Since the CPU is only interrupted when it receives its own address, the software overhead to compare addresses is eliminated. With this feature enabled in one of the 9-bit modes, the Receive Interrupt (RI) flag will only get set when the received byte corresponds to either a Given or Broadcast address.

The feature works the same way in the 8-bit mode (Mode 1) as in the 9-bit modes, except that the stop bit takes the place of the 9th data bit. If SM2 is set, the RI flag is set only if the received byte matches the Given or Broadcast Address and is terminated by a valid stop bit. Setting the SM2 bit has no effect in Mode 0.

The master can selectively communicate with groups of slaves by using the Given Address. Addressing all slaves at once is possible with the Broadcast Address. These addresses are defined for each slave by two Special Function Registers: SADDR and SADEN.

A slave's individual address is specified in SADDR. SADEN is a mask byte that defines don't-cares to form the Given Address. These don't-cares allow flexibility in the user-defined protocol to address one or more slaves at a time. The following is an example of how the user could define Given Addresses to selectively address different slaves.

| Slave 1: |       |   |      |      |

|----------|-------|---|------|------|

|          | SADDR | = | 1111 | 0001 |

|          | SADEN | = | 1111 | 1010 |

|          | GIVEN | = | 1111 | 0X0X |

| Slave 2: |       |   |      |      |

|          | SADDR | = | 1111 | 0011 |

|          | SADEN | = | 1111 | 1001 |

|          | GIVEN | = | 1111 | 0XX1 |

Table 11. SCON: Serial Port Control Register

|        | Bit Addre                            | ecablo                                      |                                            |                                                                       |                                            |                              |                            |                             |       |

|--------|--------------------------------------|---------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------|------------------------------|----------------------------|-----------------------------|-------|

|        | SM0/FE                               | SM1                                         | SM2                                        | REN                                                                   | TB8                                        | RB8                          | ТІ                         | BI                          | 1     |

| Bit    |                                      | 6                                           | 5                                          | 4                                                                     | 3                                          | 2                            | 1                          | 0                           |       |

|        | (SMOD0 =                             | -                                           | 5                                          | -                                                                     | 0                                          | 2                            | I                          | 0                           |       |

| Symbol | Function                             |                                             |                                            |                                                                       |                                            |                              |                            |                             |       |

| FE     | bit is not o                         |                                             | valid frame                                | t by the rec<br>es but shou<br>FE bit.                                |                                            |                              |                            |                             |       |

| SM0    | Serial Po                            | rt Mode Bit                                 | 0, (SMOD                                   | 0  must = 0                                                           | to access                                  | bit SM0)                     |                            |                             |       |

| SM1    | Serial Po                            | rt Mode Bit                                 | 1                                          |                                                                       |                                            |                              |                            |                             |       |

|        | SM0                                  | SM1                                         | Mode                                       | Descrip                                                               |                                            | Baud F                       |                            |                             |       |

|        | 0                                    | 0                                           | 0                                          | shift reg                                                             |                                            | Fosc/                        |                            |                             |       |

|        | 0<br>1                               | 1<br>0                                      | 1<br>2                                     | 8-bit UA                                                              |                                            | variable                     | -                          | (00                         |       |

|        | 1                                    | 1                                           | 2                                          | 9-bit UA<br>9-bit UA                                                  |                                            | rosc/¢<br>variable           | 64 or F <sub>OSC</sub>     | /32                         |       |

| SM2    | will not be<br>received<br>activated | e set unless<br>byte is a Gi<br>unless a va | s the receiv<br>ven or Bro<br>alid stop bi | s Recogniti<br>ved 9th dat<br>adcast Ado<br>t was recei<br>, SM2 shou | a bit (RB8)<br>Iress. In Mo<br>ved, and th | is 1, indica<br>ode 1, if SN | ting an add<br>I2 = 1 thei | ress, and t<br>n RI will no | he    |

| REN    | Enables s<br>reception               | •                                           | tion. Set b                                | y software                                                            | to enable r                                | eception. C                  | lear by sof                | tware to di                 | sable |

| TB8    | The 9th d<br>desired.                | ata bit that                                | will be trai                               | nsmitted in                                                           | Modes 2 a                                  | nd 3. Set o                  | r clear by s               | oftware as                  |       |

| RB8    |                                      |                                             |                                            | bit that wa<br>lode 0, RB8                                            |                                            |                              | if SM2 =                   | 0, RB8 is th                | ne    |

| ΤI     |                                      |                                             |                                            | nardware at<br>other mode                                             |                                            |                              |                            |                             |       |

| RI     | through tl                           |                                             | time in the                                | ardware at<br>other mode                                              |                                            |                              |                            |                             |       |

|        | located at P<br>oscillator fre       |                                             |                                            |                                                                       |                                            |                              |                            |                             |       |

The SADEN byte are selected such that each slave can be addressed separately. Notice that bit 1 (LSB) is a don't-care for Slave 1's Given Address, but bit 1 = 1 for Slave 2. Thus, to selectively communicate with just Slave 1 the master must send an address with bit 1 = 0 (e.g. 1111 0000).

Similarly, bit 2 = 0 for Slave 1, but is a don't-care for Slave 2. Now to communicate with just Slave 2 an address with bit 2 = 1 must be used (e.g. 1111 0111).

Finally, for a master to communicate with both slaves at once the address must have bit 1 = 1 and bit 2 = 0.

Notice, however, that bit 3 is a don't-care for both slaves. This allows two different addresses to select both slaves (1111 0001 or 1111 0101). If a third slave was added that required its bit 3 = 0, then the latter address could be used to communicate with Slave 1 and 2 but not Slave 3.

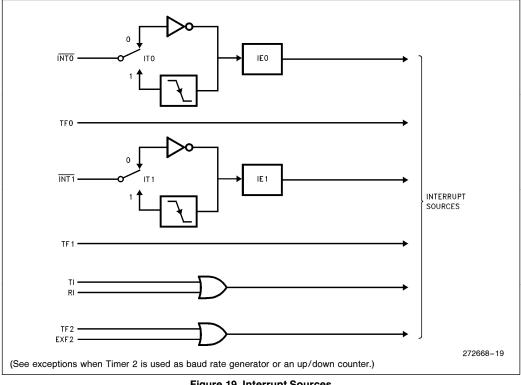

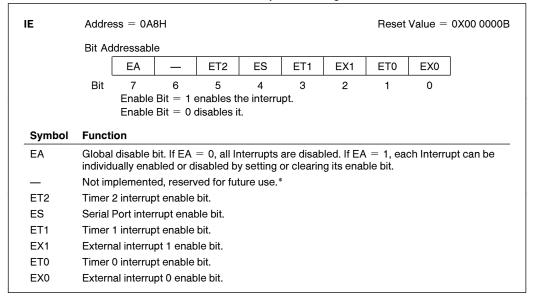

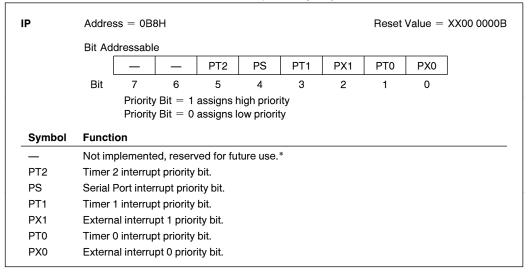

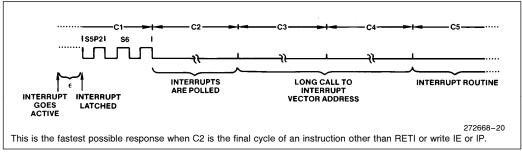

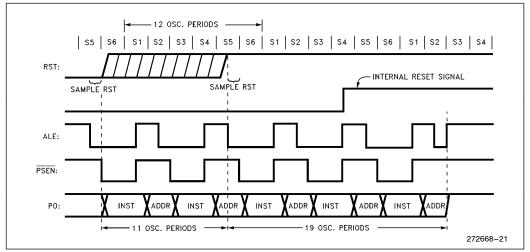

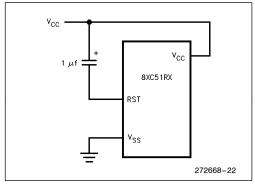

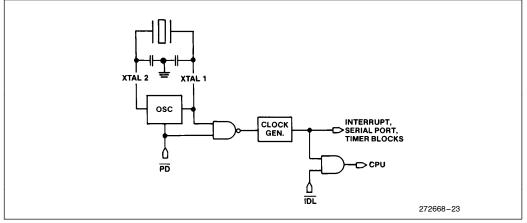

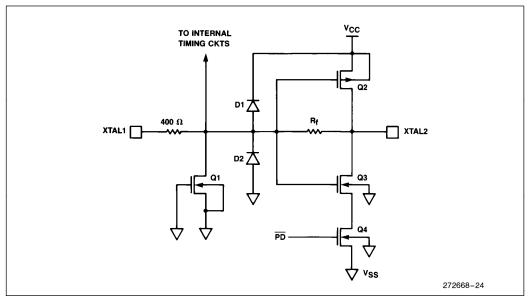

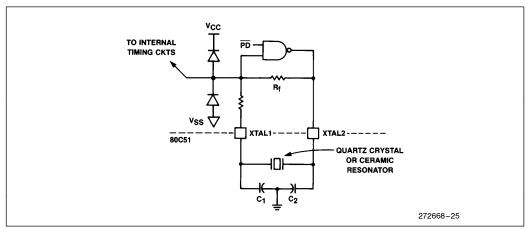

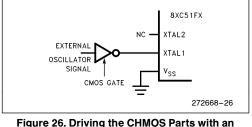

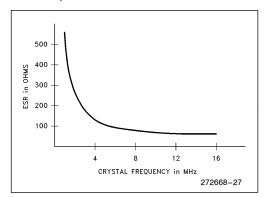

The master can also communicate with all slaves at once with the Broadcast Address. It is formed from the logical OR of the SADDR and SADEN registers with zeros defined as don't-cares. The don't-cares also allow