### FEATURES OF MX10F201FC (80C51 with MTP memory and LCD)

- -80C51 CPU core

- 4.5 ~ 5.5V voltage range

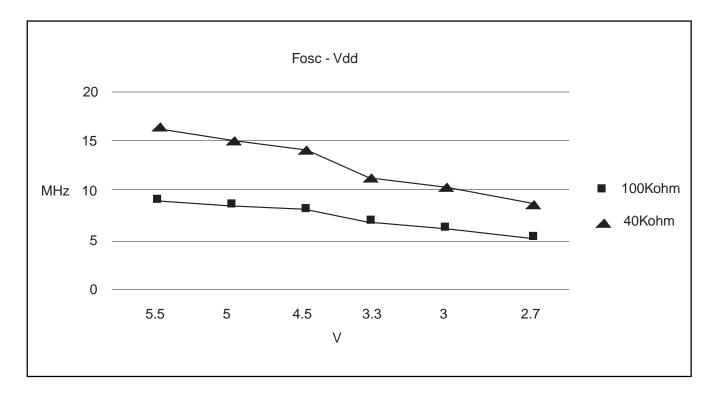

- 2 to 16MHz clock frequency

- 16K bytes MTP memory for code memory

- 512 bytes internal data RAM

- Low power consumption

- Up to 16 digits LCD driver/controller

- Four 8 bit general purpose I/O ports

- Two standard 16-bit Timers

- On-chip Watch Dog Timer

- Two channel PWM outputs

- UART

- 8 interrupt sources

- 100 pin PQFP package

- Single clock or dual clock

- EMI compatibility

#### **Features list**

- 80C51 CPU core

- 4.5 ~ 5.5V operation voltage range

- 2 to 16MHz clock frequency

- 16K bytes MTP memory for code memory

- More than 100 times program/erase cycles

- More than 10 years data retention

- 512 bytes internal data RAM

- Low operation current

- Power saving modes

- User friendly power control for active mode current

- Idle mode

- Sleep mode

- Power down mode, can be wake up by external interrupts or RESET

- LCD driver/controller

- Max. 16-digits display at 1/4 duty LCD

- 1:1(static), 1:2, 1:3 or 1:4 selectable LCD multiplexing rate

- 4 backplane driver, 32 segment driver

- LCD directly drive capability with display memory

- VLCD to control LCD driving voltage, (VLCD-VSS)

- 4x8 general purpose I/O ports

- Provide software I2C capability

- Two standard 16-bit Timers (Timer 0,1)

- On-chip Watch Dog Timer (WDT)

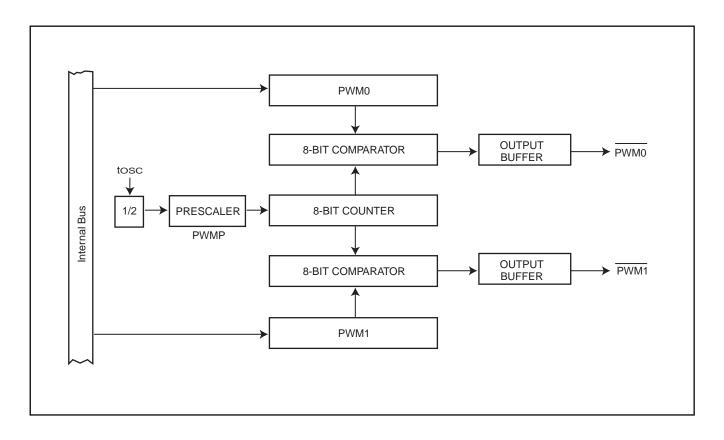

- Two channel PWM outputs

- UART

- Up to 8 interrupt sources and 8 interrupt vectors

- 4 external sources

- 4 internal sources(Timer0,Timer1,watch Timer and UART)

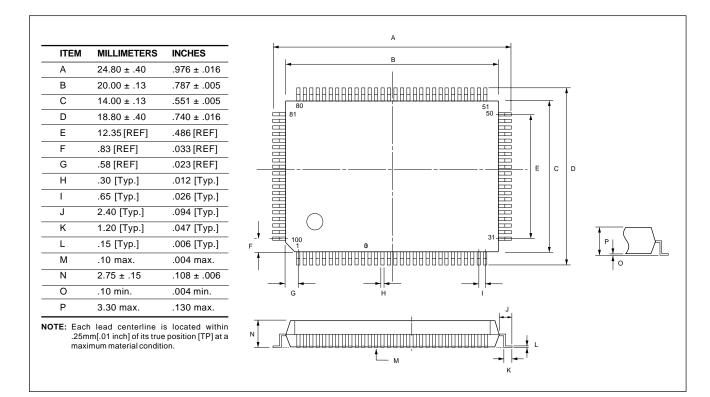

- 100 pin PQFP package

- Single clock or dual clock

- single clock mode: 2~16MHz system clock for CPU,Timer0/1,WDT,UART and LCD

- dual clock mode : 2~16MHz system clock for CPU, Timer0/1, WDT, UART; while 32.768KHz sub-system clock for LCD and watch timer.

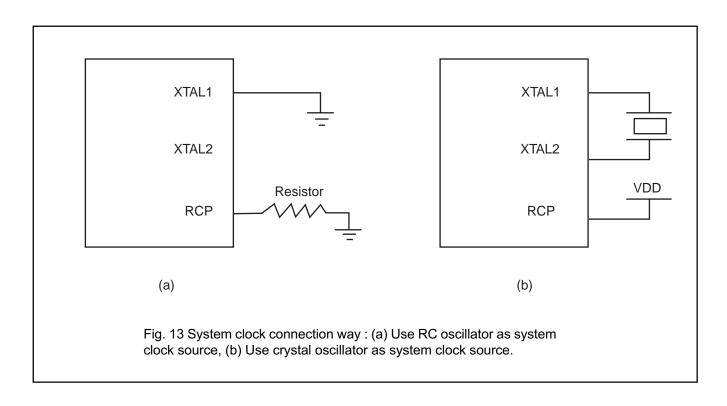

- system clock is either crystal or RC activated

- EMC(Electro-Magnetic Compatibility) improved

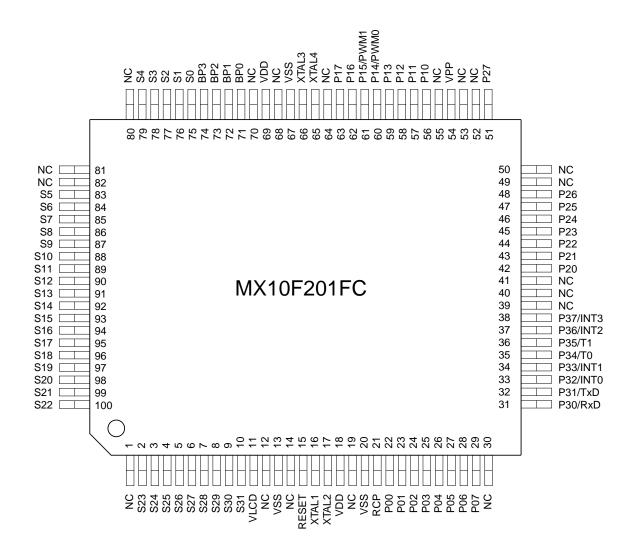

#### **PINNING**

Fig.1 Pinning

#### **Table. 1 Pin Description**

| I/O  | SYMBOL   | PIN \QFP 100  | DESCRIPTION                                   |

|------|----------|---------------|-----------------------------------------------|

| 0    | BP0-BP3  | 71~74         | Backplane drive output line 0 to 3.           |

| 0    | S00-S31  | 75-79,83-100, | Segment drive output line 0 to 31.            |

|      |          | 2-10          |                                               |

| I/O  | P00-P07  | 22-29         | Port:8-bit open drain bidirectional I/O Port  |

| I/O  | P20-P27  | 42-48,51      | Port: 8-bit quasi-bidirectional I/O Port with |

|      |          |               | internal pull-up                              |

| I/O  | P10-P17  | 56-63         | Quasi-bidirectional I/O lines                 |

|      | P14      |               | also for PWM channel 0                        |

|      | P15      |               | also for PWM channel 1                        |

| I/O  | P30-P37  | 31-38         | Quasi-bidirectional I/O lines                 |

|      | P30      | 31            | also for UART Receive                         |

|      | P31      | 32            | also for UART Transmit                        |

|      | P32-P33, |               | also for external interrupt 0-3               |

|      | P36-P37  |               |                                               |

|      | P34      |               | also for Timer0 external input                |

|      | P35      |               | also for Timer1 external input                |

|      |          |               |                                               |

| I    | RESET    | 15            | reset input                                   |

| I    | VDD      | 18,69         | Positive power supply                         |

|      | VSS      | 13,20,67      | Ground                                        |

|      | XTAL1    | 16            | XTAL connection input                         |

| 0    | XTAL2    | 17            | XTAL connection output                        |

| I    | XTAL3    | 66            | 32.768KHz, XTAL input                         |

| 0    | XTAL4    | 65            | 32.768KHz, XTAL output                        |

| ı    | RCP      | 21            | RC oscillator resistor connection input       |

| ı    | TEST/VPP | 54            | Supply 12V power for programming / erasing    |

| T    | VLCD     | 11            | LCD driver power supply                       |

| Note |          |               |                                               |

#### Note:

- 1. To avoid a 'Latch-up' effect at power-on , the voltage on any pin (at any time )must not be higher than  $V_{DD}$  +0.5 V or lower Vss-0.5V respectively

- 2. The generation or use of a Port 3 pin as an alternative function is carried out automatically by the associated Special Function Register (SFR) bit is properly written .

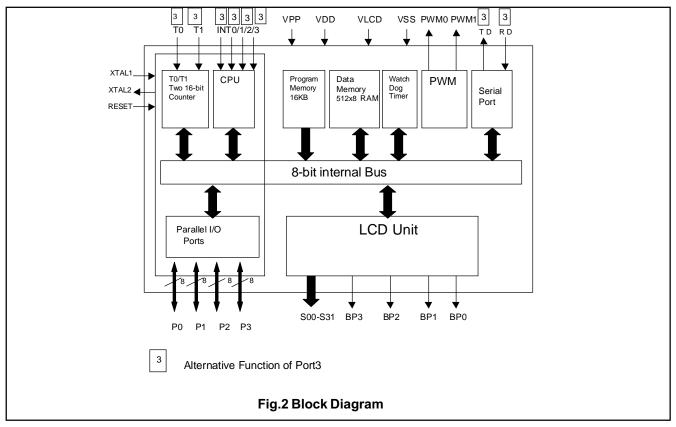

#### **FUNCTIONAL DESCTIPTION**

#### General

The MX10F201FC is a stand-alone high-performance and low power microcontroller designed for use in many applications which need code programmability.

The Flash EPROM offers customers to program the device themselves. This feature increases the flexibility in many applications, not only in development stage, but also in mass production stage.

In addition to the 80C51 standard functions, the MX10F201FC provides a number of dedicated hardware functions. MX10F201FC is a control-oriented CPU with on-chip program and data memory. It can execute program with internal memory up to 16k bytes. MX10F201FC has four software selectable modes of reduced activity for power reduction: active power control, idle, sleep, and Power-down. The idle mode freezes the CPU while allowing the RAM, Timers, serial ports, interrupt system and other peripherals to continue functioning. The Power-down mode saves the RAM contents but freezes the oscillator causing all other chip functions to be inoperative. Power-down mode can be terminated by an external reset ,and in addition, by either of the four external interrupts. The sleep mode behaves like power down mode, but with LCD and oscillator still turning on. And sleep mode can be terminated as the power down mode does.

#### **Instruction Set Execution**

The MX10F201FC uses the powerful instruction set of the 80C51. Additional SFRs are incorporated to control the on-chip peripherals. The instruction set consists of 49 single-byte, 46 two-bytes, and 16 three-bytes instructions. When using a 16MHz oscillator, 64 instructions execute in 750 ns and 45 instructions execute in 1.5 us. Multiply and divide instructions execute in 3 us.

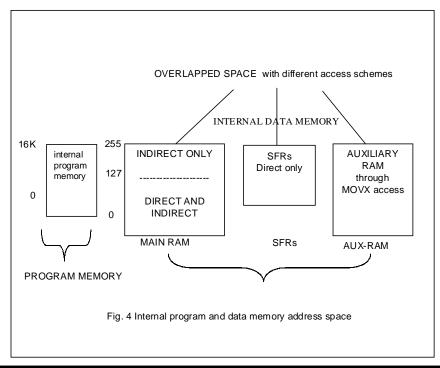

#### **MEMORY ORGANIZATION**

The Central Processing Unit (CPU) manipulates operands in three memory spaces; these are the 256 bytes internal data memory (RAM), 256 byte auxiliary data memory (AUX-RAM) and 16k byte internal MTP program memory (FEPROM).

#### **Program Memory**

The program memory address space of the MX10F201FC comprises an internal and an external memory space. The MX10F201FC has 16k byte of program memory on-chip.

#### **Program Protection**

If the user choose to set security lock in MTP memory, the program content is protected from reading out of chip.

#### **Internal Data Memory**

The internal data memory is divided into three physically separated parts: 256 byte of RAM, 256 bytes of AUX-RAM, and 128 bytes special function register area (SFR). These parts can be addressed as follows (see Fig.4 and Table. 2)

- RAM 0 to 127 can be addressed directly and indirectly as in the 80C51. Address pointers are R0 and R1 of the selected register bank.

- RAM 128 to 255 can only be addressed indirectly . Address pointers are R0 and R1 of the selected register bank.

- AUX-RAM 0 to 255 is indirectly addressable as the external data memory locations 0 to 255 with the MOVX instructions. Address pointers are R0 and R1 of the selected register bank and DPTR. When executing from internal program memory, an access to AUX\_RAM 0 to 255 will not affect the ports P0,P2,P3.6 and P3.7. SFRs can only be addressed directly in the address range from 128 to 255.

| LOCATION                                   | ADDRESSED               |

|--------------------------------------------|-------------------------|

| RAM 0 to 127                               | DIRECT and INDIRECT     |

| RAM 128 to 255                             | INDIRECT only           |

| AUX-RAM 0 to 255                           | INDIRECT only with MOVX |

| Special Function Register (SFR) 128 to 255 | DIRECT only             |

Fig. 4 shows the internal memory address space. Table 3 shows the Special Function Register (SFR) memory map. Location 0 to 31 at the lower RAM area can be devided into four 8-bit register banks. Only one of these banks may be enabled at a time. The next 16 bytes, locations 32 through 47, contain 128 directly addressable bit locations.

The stack can be located anywhere in the internal 256 byte RAM. The stack depth is only limited by the available internal RAM space of 256 bytes. All registers except the Program Counter and the four 8-byte register banks reside in the SFR address space.

- Register

- Direct

- Register-Indirect

- Immediate

- Base-Register plus Index-Register-Indirect.

The first three methods can be used for addressing destination operands. Most instructions have a 'destination / source' field that specifies the data type, addressing methods and operands involved. For operations other than MOVs, the destination operand is also a source operand.

Access to memory addresses is as follows:

- Register in one of the four 8-byte register banks through Direct or Register-Indirect addressing.

- 256 bytes of internal RAM through Direct or Register-Indirect addressing. Bytes 0-127 of internal RAM may be only be addressed indirectly as data RAM.

- SFR through direct addressing at address location 128-255.

### Table. 3 SFR Registers Map

| Symbol   | Direct Address(ex) | Reset Value |

|----------|--------------------|-------------|

| P0       | 80H                | 1111,1111   |

| SP       | 81                 | 0000,0111   |

| DPL      | 82                 | 0000,0000   |

| DPH      | 83                 | 0000,0000   |

| PCON     | 87                 | 0000,0000   |

| TCON     | 88                 | 0000,0000   |

| TMOD     | 89                 | 0000,0000   |

| TLO      | 8A                 | 0000,0000   |

| TL1      | 8B                 | 0000,0000   |

| TH0      | 8C                 | 0000,0000   |

| TH1      | 8D                 | 0000,0000   |

| P1       | 90                 | 1111,1111   |

| SCON     | 98                 | 0000,0000   |

| SBUF     | 99                 | xxxx,xxxx   |

| P2       | A0                 | 1111,1111   |

| IE       | A8                 | 0000,0000   |

| P3       | B0                 | 1111,1111   |

| IP       | B8                 | x000,0000   |

| LCON     | BA                 | x001,1100   |

| LCD0     | BB                 | 0000,0000   |

| LCD1     | BC                 | ,           |

|          |                    | 0000,0000   |

| LCD2     | BD                 | 0000,0000   |

| LCD3     | BE                 | 0000,0000   |

| LCD4     | BF                 | 0000,0000   |

| INTCON   | C0                 | 0000,0000   |

| LCD5     | C1                 | 0000,0000   |

| LCD6     | C2                 | 0000,0000   |

| LCD7     | C3                 | 0000,0000   |

| LCD8     | C4                 | 0000,0000   |

| LCD9     | C5                 | 0000,0000   |

| LCDA     | C6                 | 0000,0000   |

| LCDB     | C7                 | 0000,0000   |

| PSW      | D0                 | 0000,0000   |

| LCDC     | D1                 | 0000,0000   |

| LCDD     | D2                 | 0000,0000   |

| LCDE     | D3                 | 0000,0000   |

| LCDF     | D4                 | 0000,0000   |

| ACC      | E0                 | 0000,0000   |

| WTL      | E3                 | 0000,0000   |

| WTH      | E4                 | xx00,0000   |

| IEN1     | E8                 | xxxx,xx00   |

| EBTCON   | EB                 | xxxx,001x   |

| В        | F0                 | 0000,0000   |

| PCON1    | F1                 | x000,0100   |

| IP1      | F8                 | xxxx,xx00   |

| PWM0     | FC                 | 0000,0000   |

| PWM1     | FD                 | 0000,0000   |

| PWMP     | FE                 | 0000,0000   |

| T3 (WDT) | FF                 | 1111,1111   |

|          |                    | <del></del> |

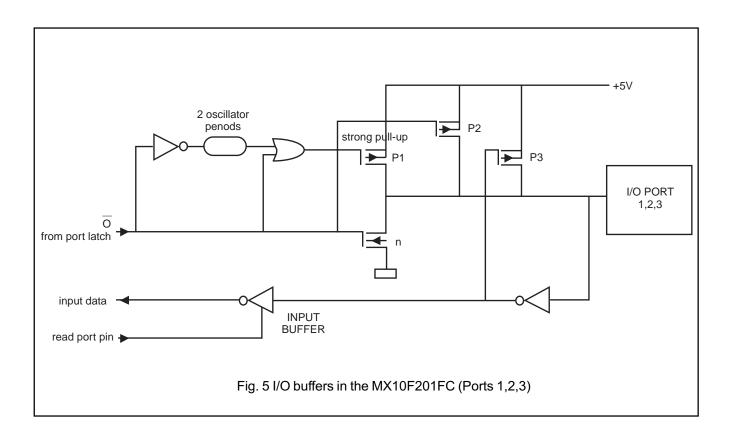

#### I/O facilities

MX10F201FC has one 8 bits port, port 0, which is open drain, and three 8 bits ports, port 1/2/3, which are quasi bidirectional ports. These four ports are fully compatible to standard 80C51's port 0/1/2/3.

- Port1: pins can be configured individually to provide 2 PWM outputs.

- Port3: pins can be configured individually to provide: external interrupt inputs (external interrupt 0/1/2/3); external inputs for Timer/ counter 0 and Timer/counter1, and UART receive / transmit.

Port pins which are not used for alternate functions may be used as normal bidirectional I/O pins. The generation or use of a Port 1 or Port 3 pin as an alternate function is carried out automatically by writing the associated SFR bit with proper value.

#### Timer/Counter

MX10F201FC's Timer/Counter 0 and 1 are fully compatible to standard 80C51's.

The MX10F201FC's contains two 16-bit Timer/counters, Timer 0 and Timer 1. Timer 0 and Timer 1 may be programmed to carry out the following functions:

- measure time intervals and pulse durations

- count events

- generate interrupt requests.

#### Timer 0 and Timer 1

Timers 0 and 1 each have a control bit in TMOD SFR that selects the Timer or counter function of the corresponding Timer. In the Timer function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of 12 oscillator periods, the count rate is 1/12 of the oscillator frequency.

In the counter function, the register is incremented in response to a HIGH-to-LOW transition at the corresponding samples, when the transition shows a HIGH in one cycle and a LOW in the next cycle, the counter is incremented. Thus, it takes two machine cycles (24 oscillator periods) to recognize a HIGH-to-LOW transition. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle.

Timer 0 and Timer 1 can be programmed independently to operate in one of four modes (refer to table 5):

- Mode 0: 8-bit Timer/counter with devided-by-32 prescaler

- Mode 1: 16-bit Timer/counter

- Mode 2: 8-bit Timer/counter with automatic reload

- Mode 3: Timer 0: one 8-bit Timer/counter and one 8-bits Timer. Timer 1: stopped.

When Timer 0 is in Mode 3, Timer 1 can be programmed to operate in Modes 0, 1 or 2 but cannot set an interrupt request flag and generate an interrupt. However, the overflow from Timer 1 can be used to pulse the Serial Port transmission-rgate generator. With a 16 MHz crystal, the counting frequency of these Timer/counters is as follows:

- in the Timer function, the Timer is incremented at a frequency of 1.33 MHz (oscillator frequency divided by 12).

- in the counter function, the frequency handling range for external inputs is 0 Hz to 0.66 MHz (oscillator frequency divided by 24).

Both internal and external inputs can be gated to the Timer by a second external source for directly measuring pulse duration.

The Timers are started and stopped under software control. Each one sets its interrupt request flag when it overflows from all logic 1's to all logic 0's (respectively, the automatic reload value), with the exception of Mode 3 as previously described.

#### TMOD: TIMER/COUNTER MODE CONTROL REGISTER

This register is located at address 89H.

#### Table. 4 TMOD SFR (89H)

| 7       | 6   | 5  | 4  | 3       | 2   | 1  | 0     |

|---------|-----|----|----|---------|-----|----|-------|

| GATE    | C/T | M1 | MO | GATE    | C/T | M1 | MO    |

| (MSB)   |     |    |    |         |     |    | (LSB) |

| TIMER 1 |     |    |    | TIMER 0 |     |    |       |

keep the above table with the following table

#### Table. 5 Description of TMOD bits

| MNEMONIC | POSITION | FUNCTION                                                                             |

|----------|----------|--------------------------------------------------------------------------------------|

| TIMER 1  |          |                                                                                      |

| GATE     | TMOD.7   | Timer 1 gating control: when set, Timer/counter'1' is enabled only while 'Int1'      |

|          |          | pin is high and 'tr1' control bit is set. when cleared, Timer/counter '1' is enabled |

|          |          | whenever 'tr1' control bit is set.                                                   |

| C/T      | TMOD.6   | Timer or counter selector: cleared for Timer operation (input from internal          |

|          |          | system clock). set for counter operation (input from 'T1' input pin).                |

| M1       | TMOD.5   | Operation mode: see table 6.                                                         |

| MO       | TMOD.4   | Operation mode: see table 6.                                                         |

| TIMER 0  |          |                                                                                      |

| GATE     | TMOD.3   | Timer 0 gating control: when set, Timer/Counter '0' is enabled only while 'Int0'     |

|          |          | pin is high and 'tr0' control bit is set. when cleared, Timer/counter '0' is enabled |

|          |          | whenever 'tr0' control bit is set.                                                   |

| C/T      | TMOD.2   | Timer or counter selector: cleared for Timer operation (input from internal          |

|          |          | system clock). set for counter operation (input from 'T0' input pin).                |

| M1       | TMOD.1   | Operation mode: see table 6.                                                         |

| MO       | TMOD.0   | Operation mode: see table 6.                                                         |

|          |          |                                                                                      |

#### Table. 6 TMOD M1 and M0 operating modes

| M1 | MO | FUNCTION                                                                                             |

|----|----|------------------------------------------------------------------------------------------------------|

| 0  | 0  | 8-bit Timer/counter: 'THx' with 5-bit prescaler.                                                     |

| 0  | 1  | 16-bit Timer/counter: 'THx' and 'TLx' are cascaded, there is no prescaler.                           |

| 1  | 0  | 8-bit autoload Timer/counter: 'THx' holds a value which is to be reloaded into 'TLx' each time it    |

|    |    | overflows.                                                                                           |

| 1  | 1  | Timer 0: TL0 is an 8-bit Timer/counter controlled by the standard Timer 0 control bits. TH0 is an 8- |

|    |    | bit Timer controlled by Timer 1 control bits.                                                        |

| 1  | 1  | Timer 1 : Timer/counter 1 stopped.                                                                   |

TCON: TIMER/COUNTER CONTROL REGISTER

This register is located at address 88H.

### Table. 7 TCON SFR (88H)

| 7     | 6   | 5   | 4   | 3   | 2   | 1   | 0     |

|-------|-----|-----|-----|-----|-----|-----|-------|

| TF1   | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0   |

| (MSB) |     |     |     |     |     |     | (LSB) |

keep the above table with the following table

### Table. 8 Description of TCON bits

| MNEMONIC | POSITION | FUNCTION                                                                            |

|----------|----------|-------------------------------------------------------------------------------------|

| TF1      | TCON.7   | Timer 1 overflow flag: set by hardware on Timer/Counter overflow. Cleared when      |

|          |          | interrupt is processed.                                                             |

| TR1      | TCON.6   | Timer 0 overflow flag: set by hardware on Timer/Counter overflow. Cleared when      |

|          |          | interrupt is processed.                                                             |

| TF0      | TCON.5   | Timer 0 overflow flag: set by hardware on Timer/Counter overflow. Cleared when      |

|          |          | interrupt is processed.                                                             |

| TR0      | TCON.4   | Timer 0 control bit : set/cleared by software to turn Timer/counter ON/OFF.         |

| IE1      | TCON.3   | Interrupt 1 edge flag: set by hardware when external interrupt is detected. Cleared |

|          |          | when interrupt is processed.                                                        |

| IT1      | TCON.2   | Interrupt 1 type control bit : set/cleared by software to specify falling edge/LOW  |

|          |          | level triggered external interrupt.                                                 |

| IE0      | TOCN.1   | Interrupt 0 edge flag: set by hardware when external interrupt is detected. Cleared |

|          |          | when interrupt is processed.                                                        |

| IT0      | TOCN.0   | Interrupt 0 type control bit: set/cleared by software tospecify falling edge/LOW    |

|          |          | level triggered external interrupt.                                                 |

|          |          |                                                                                     |

#### Interrupt system

The MX10F201FC contains a 8-source 4 external interrupts, Timer 0, Timer 1, watch timer and UART structures with two priority levels.

Each External interrupts INT0, INT1, INT2, and INT3 can be either level-activated or transition-activated depending on bits IT0 and IT1 in TCON SFR and IT2, IT3 in INTCON SFR. The flags that actually generate these interrupts are bits IE0, IE1 in TCON and IE2,IE3 in INTCON. When an external interrupt is generated, the corresponding request flag is cleared by the hardware when the service routine is vectored to, if the interrupt is transition-activated. If the interrupt is level-activated the external source has to hold the request active until the requested interrupt is actually generated. Then it has to deactive the request before the interrupt service routine is completed, otherwise another interrupt will be generated.

The Timer 0 and Timer 1 Interrupts are generated by TF0 and TF1, which are set by a rollover in their respective Timer/counter register (except for Timer 0 in Mode 3 of the serial interface). When a Timer interrupt is generated, the flag that generated it is cleared by the on-chip hardware when the service routine is vectored to.

#### IE: INTERRUPT ENABLE REGISTER

This register is located at address A8H.

#### Table. 9 IE SFR (A8H)

| _ |       | , , |     |    |     |     |     |       |

|---|-------|-----|-----|----|-----|-----|-----|-------|

|   | 7     | 6   | 5   | 4  | 3   | 2   | 1   | 0     |

| _ | EA    | EX3 | EX2 | ES | ET1 | EX1 | ET0 | EX0   |

| Ī | (MSB) | )   |     |    |     |     |     | (LSB) |

keep the above table with the following table

#### Table. 10 Description of IE bits

| EA IE.7 Disable all interrupt - Low, all disabled High, each interrupt source is individua clearing its enable bit.  EX3 IE.6 Enable / Disable External interrupt 3 Low, disabled | lly enabled or disabled by setting or |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| - High, each interrupt source is individual clearing its enable bit.  EX3 IE.6 Enable / Disable External interrupt 3.                                                             | lly enabled or disabled by setting or |

| clearing its enable bit.  EX3 IE.6 Enable / Disable External interrupt 3.                                                                                                         | lly enabled or disabled by setting or |

| EX3 IE.6 Enable / Disable External interrupt 3.                                                                                                                                   |                                       |

| •                                                                                                                                                                                 |                                       |

| - Low, disabled                                                                                                                                                                   |                                       |

| · , · · · · · ·                                                                                                                                                                   |                                       |

| - High, enabled                                                                                                                                                                   |                                       |

| EX2 IE.5 Enable / Disable External Interrupt 2.                                                                                                                                   |                                       |

| - Low, disabled                                                                                                                                                                   |                                       |

| - High, enabled                                                                                                                                                                   |                                       |

| ES IE.4 Enable / Disable UART interrupt.                                                                                                                                          |                                       |

| - Low, disabled                                                                                                                                                                   |                                       |

| - High, enabled                                                                                                                                                                   |                                       |

| ET1 IE.3 Enable / Disable Timer1 overflow interrup                                                                                                                                | ot.                                   |

| EX1 IE.2 Enable / Disable External interrupt 1.                                                                                                                                   |                                       |

| - Low, disabled                                                                                                                                                                   |                                       |

| - High, enabled                                                                                                                                                                   |                                       |

| ET0 IE.1 Enable / disable Timer0 overflow interrup                                                                                                                                | t.                                    |

| EX0 IE.0 Enable / Disable External interrupt 0.                                                                                                                                   |                                       |

| - Low, disabled                                                                                                                                                                   |                                       |

| - High, enabled                                                                                                                                                                   |                                       |

IEN1: INTERRUPT ENABLE REGISTER 2

Table. 11 IEN1 SFR (E8H)

| 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|---|---|---|---|---|---|-----|---|

| - | - | - | - | - | - | EWT | 0 |

EWT: Enable / Disable Watch Timer interrupt.

IP: INTERRUPT PRIORITY REGISTER

This register is located at address B8H.

Table. 12 IP SFR (B8H)

keep the above table with the following table

Table. 13 Description of IP bits

| MNEMONIC | POSITION | FUNCTION                                              |

|----------|----------|-------------------------------------------------------|

| _        | IP.7     | RESERVED                                              |

| PX3      | IP.6     | Define External interrupt 3 interrupt priority level. |

|          |          | - High, assign a high priority level.                 |

| PX2      | IP.5     | Define External interrupt 2 interrupt priority level. |

|          |          | - High, assign a high priority level.                 |

| PS1      | IP.4     | Define interrupt priority level of UART.              |

| PT1      | IP.3     | Define Timer1 overflow interrupt priority level.      |

| PX1      | IP.2     | Define External interrupt 1 interrupt priority level. |

|          |          | - High, assign a high priority level.                 |

| PT0      | IP.1     | Define Timer0 overflow interrupt priority level.      |

| PX0      | IP.0     | Define External interrupt 0 interrupt priority level. |

|          |          | - High, assign a high priority level.                 |

IP1: INTERRUPT PRIORITY REGISTER 2

Table. 14 IP1 SFR (F8H)

| 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|---|---|---|---|---|---|-----|---|

| - | - | - | - | - | - | PWT | 0 |

PWT: Define Watch Timer interrupt priority level.

#### Table. 15 INTCON SFR (C0H)

| 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|---|---|-----|-----|-----|-----|-----|-----|

| 0 | 0 | WTF | WTR | IE3 | IT3 | IE2 | IT2 |

#### **Table. 16 Description of INTCON bits**

IE3/2: External interrupt 3/2 edge flag. Set by H/W when exteranl interrupt is detected, and cleared when interrupt is processed.

IT3/2: External interrupt 3/2 type control bit. Set/cleared by S/W to specify falling edge/low level triggered external interrupt.

WTF: Watch timer overflow interrupt flog. Set by H/W when watch timer overflow occurred, and cleared by S/W or warm/cold reset.

WTR: Watch timer enable bit. Set/ cleared by S/W

#### Table. 17 INTERRUPT VECTORS & PRIORITY WITHIN LEVELS

| source               | name | Priority Within Level | Vector Address |

|----------------------|------|-----------------------|----------------|

| Ext. interrupt0      | IE0  | 1(Highest)            | 0003H          |

| Timer0 overflow      | TF0  | 2                     | 000BH          |

| Ext. interrupt1      | IE1  | 3                     | 0013H          |

| Timer1 overflow      | TF1  | 4                     | 001BH          |

| UART interrupt       | IS   | 5                     | 0023H          |

| Ext. interrupt2      | IE2  | 6                     | 002BH          |

| Ext. interrupt3      | IE3  | 7                     | 0033H          |

| Watch timer overflow | WTF  | 8                     | 003BH          |

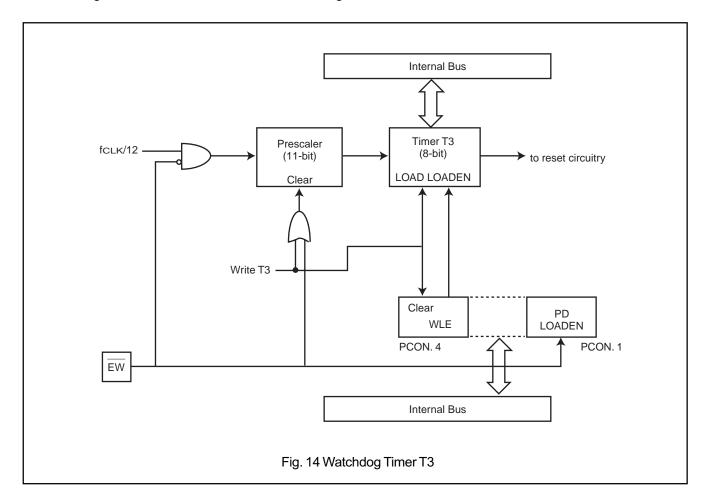

#### **Watch Timer**

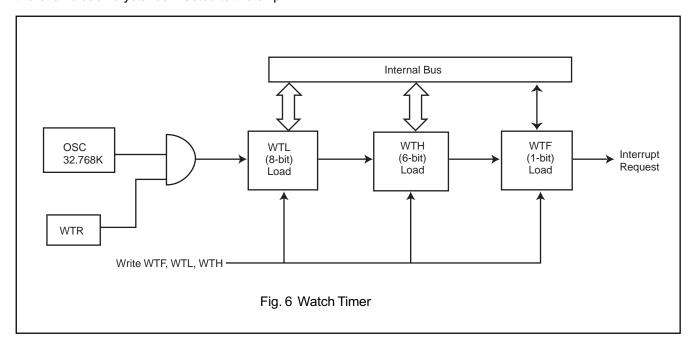

The watch timer module (see Fig. 6) is clocked by 32.768KHz external crystal, and generates interrupt request every 0.5 second. This value is derived from  $f_{timer} = f_{osc} / (256x64)$ . The watch timer consists of an 8-bit timer register WTL and a 6-bit timer registers WTH. The WTL register is triggered by the 32.768KHz external crystal, and the WTH register increases its value while WTL overflow occurs. When the overflow of WTH occurs, the WTF bit in SFR INTCON is set High automatically and an interrupt request is sent to the microcontroller.

Both of the timer registers WTL and WTH can be loaded values by software. Therefore the time interval of the watch timer interrupt request can be adjusted. This allows the watch timer to send interrupt request more frequently for some special application.

The WTF can be set both by hardware and software, but it can only be cleared by software. The 32.768KHz external oscillator is gated by the WTR bit in SFR INTCON. If WTR is cleared, the watch timer registers will hold their values.

In the idle and sleep states the watch timer remains active, and it wakes up the microcontroller while the watch timer overflow (i.e. WTF is set HIGH) occurs.

Since this module is clocked by the 32.768KHz external crystal, this module is disabled and consumes no power if there is no such crystal connected to the chip.

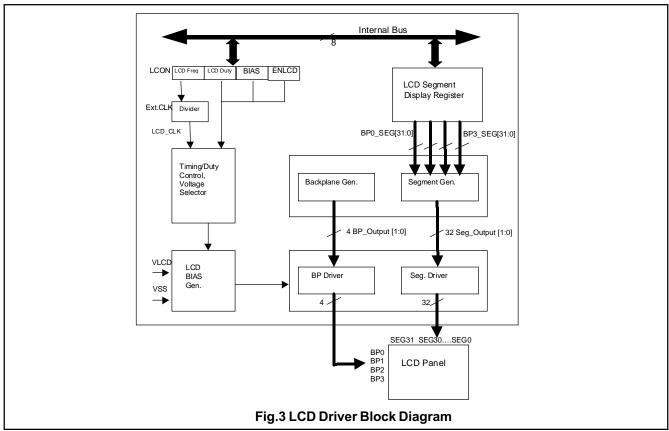

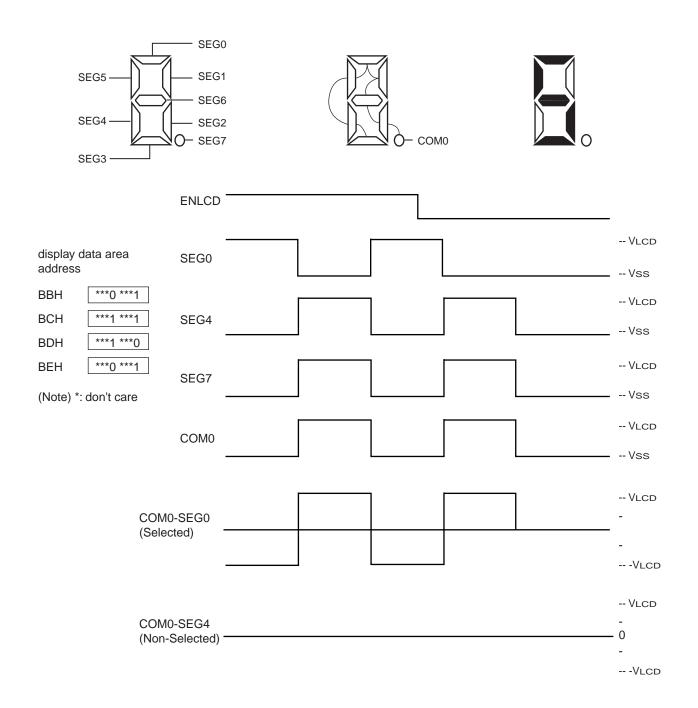

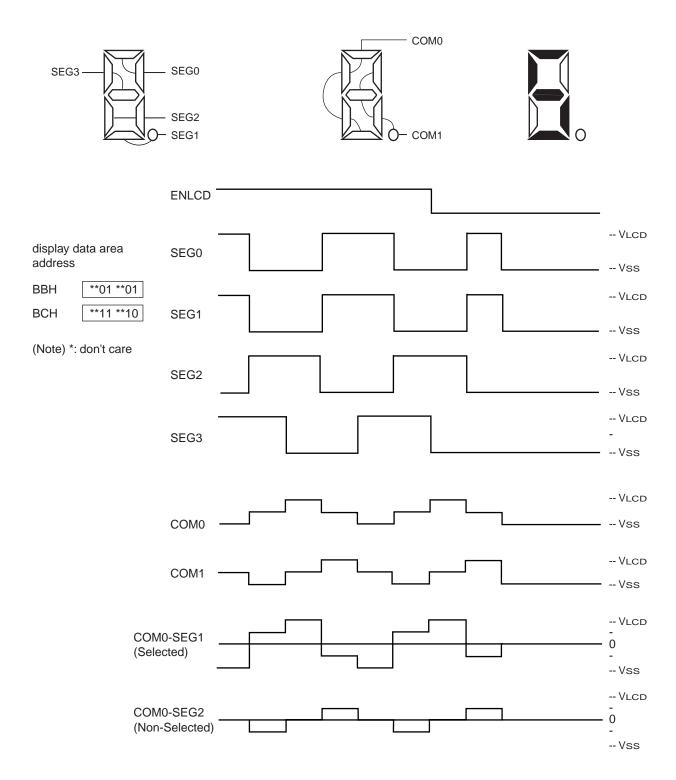

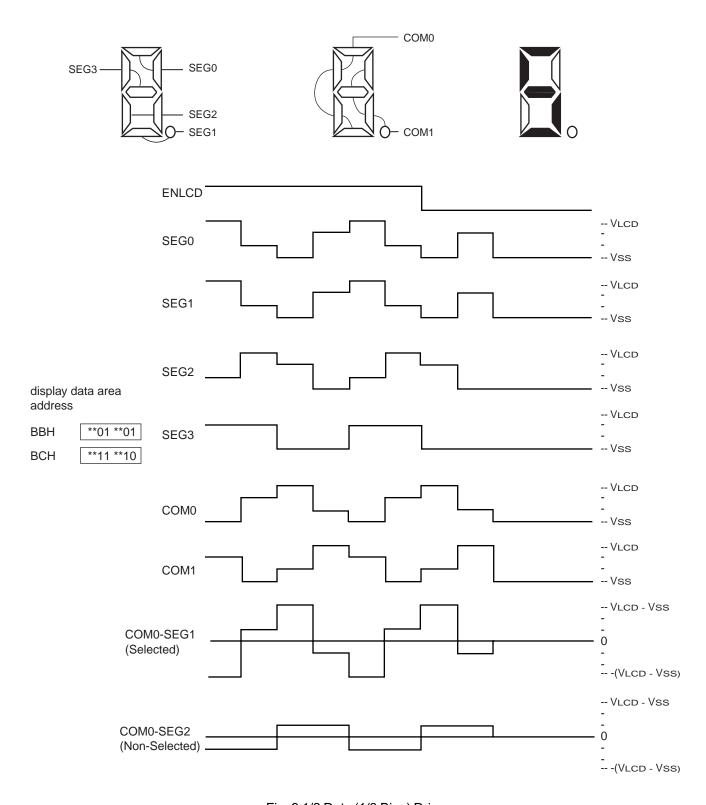

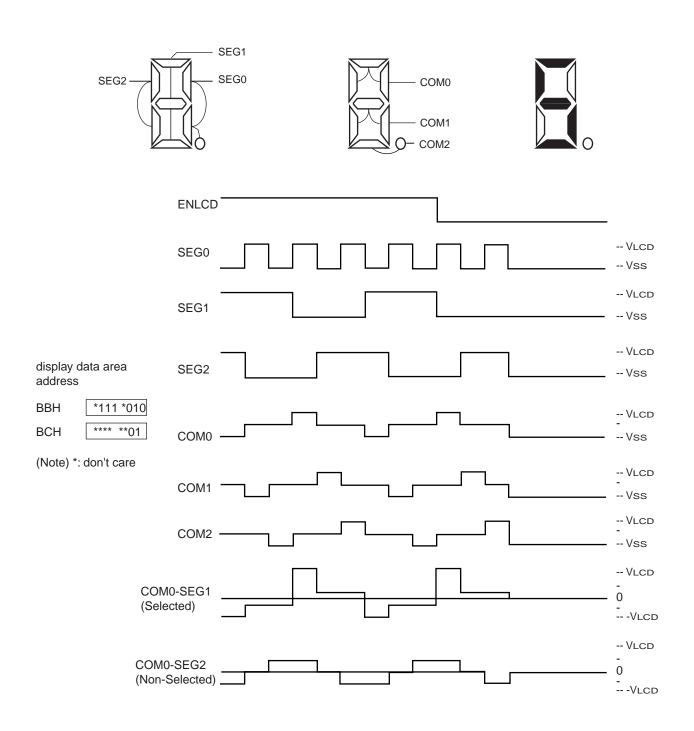

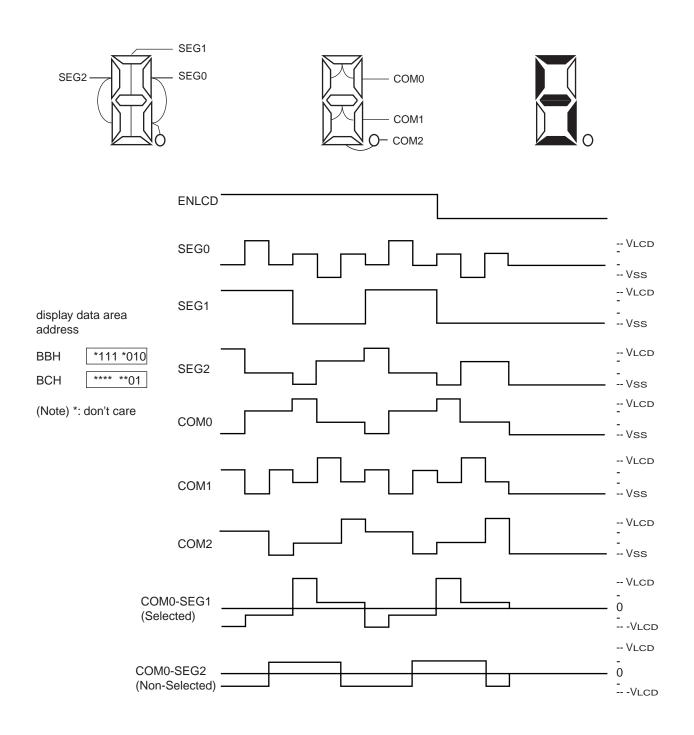

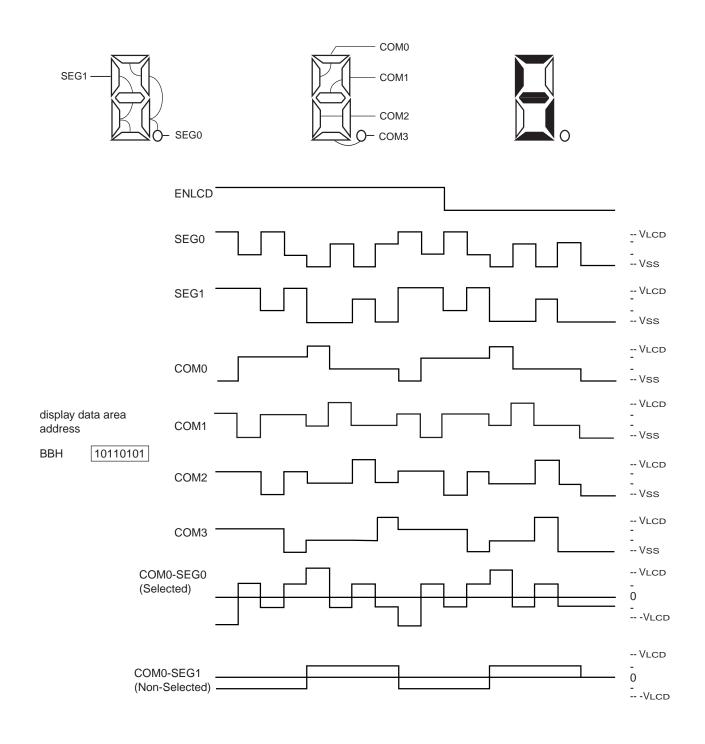

#### LCD drivers

The LCD module includes 4 by 32 pixel memory and can drive directly 4 backplanes and 32 segments outputs. Thus, for common digit-typed LCD, MX10F201FC can have maximum 16 digits display.

#### **LCD Control Register (LCON)**

Since MX10F201FC has several possible clocking alternatives: 2 to 16MHz system clock with possible second 32.768KHz sub-system clock, programmers need to set up this register to get proper LCD frame scan rate.

Table. 18 LCON SFR (BAH)

| 7 | 6     | 5     | 4     | 3   | 2   | 1    | 0     |

|---|-------|-------|-------|-----|-----|------|-------|

| - | LCDF2 | LCDF1 | LCDF0 | MD1 | MD0 | Bias | ENLCD |

. LCDF2,LCDF1,LCDF0: Selection of LCD frame scan frequency

Table. 19

|                 |                     |          | Frame scan | freq (Hz) |        |

|-----------------|---------------------|----------|------------|-----------|--------|

| Fclk            | Divider             |          |            |           |        |

| (ext. clk)      | Select              | 1/4 Duty | 1/3 Duty   | 1/2 Duty  | Static |

| - 000 : 16Mhz   | Fclk/2^18           | 61       | 81         | 61        | 61     |

| - 001 : 12Mhz   | Fclk/(2^16*3)       | 61       | 81         | 61        | 61     |

| -010:8Mhz       | Fclk/2^17           | 61       | 81         | 61        | 61     |

| - 011 : 4Mhz    | Fclk/2^16           | 61       | 81         | 61        | 61     |

| - 100 : 2Mhz    | Fclk/2^15           | 61       | 81         | 61        | 61     |

| - 101 : 1Mhz    | Fclk/2^14           | 61       | 81         | 61        | 61     |

| - 110 :0.5Mhz   | Fclk/2^13           | 61       | 81         | 61        | 61     |

| * - 111 : 32Khz | Fclk/2 <sup>9</sup> | 64       | 85         | 64        | 64     |

<sup>\*</sup> Note: Dual clock mode is set by writing as "111".

Table. 20

|               | No of Backplanes | Pixel | Digits |  |

|---------------|------------------|-------|--------|--|

| - 00 : static | 1 (BP0)          | 32    | 4      |  |

| - 01 : 1:2    | 2 (BP0,1)        | 64    | 8      |  |

| - 10 : 1:3    | 3 (BP0,1,2)      | 96    | 12     |  |

| - 11 : 1:4    | 4 (BP0,1,2,3)    | 128   | 16     |  |

<sup>.</sup> Bias: set LCD voltage bias generator.

- High, bias is 1/2(VLCD-VSS)

- Low, bias is 1/3(VLCD-VSS)

<sup>.</sup> MD1,MD0: Mode bits, determine the LCD multiplex rate.

Table, 21

| LCD Drive Mode | No of BPs | LCD Bias | Voff(rms) | Von(rms) | Contrast |

|----------------|-----------|----------|-----------|----------|----------|

| static         | 1         | static   | 0         | 1        | infinity |

| 1:2            | 2         | 1/2      | 0.354     | 0.791    | 2.236    |

| 1:2            | 2         | 1/3      | 0.333     | 0.745    | 2.236    |

| 1:3            | 3         | 1/3      | 0.333     | 0.638    | 1.915    |

| 1:4            | 4         | 1/3      | 0.333     | 0.577    | 1.732    |

. ENLCD: Enable/Disable LCD

- Low, all segment and backplanes drivers are set to the Vss level.

- High, the LCD is enable and digits display is possible.

# LCD segment display register : contain the on/off information of 4 by 32 segments of LCD Table. 22

| Address | Bit7                                                    | Bit6                                                            | Bit5                                                                                                                                                                                                                                                                                                                                                                                                  | Bit4                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit3                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit2                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Bit0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|---------|---------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BBH     |                                                         | SE                                                              | G1                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SE                                                                                                                                                                                                                                                                                                                                                                                                                                               | EG0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| BCH     |                                                         | SE                                                              | G3                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SEG2                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| BDH     |                                                         | SE                                                              | G5                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SE                                                                                                                                                                                                                                                                                                                                                                                                                                               | EG4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| BEH     |                                                         | SE                                                              | G7                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SE                                                                                                                                                                                                                                                                                                                                                                                                                                               | EG6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| BFH     |                                                         | SE                                                              | G9                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SE                                                                                                                                                                                                                                                                                                                                                                                                                                               | EG8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| C1H     |                                                         | SE                                                              | :G11                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SE                                                                                                                                                                                                                                                                                                                                                                                                                                               | EG10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| C2H     |                                                         | SE                                                              | :G13                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SEG12                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| СЗН     |                                                         | SE                                                              | G15                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SEG14                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| C4H     |                                                         | SE                                                              | :G17                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SEG16                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| C5H     |                                                         | SE                                                              | G19                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SEG18                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

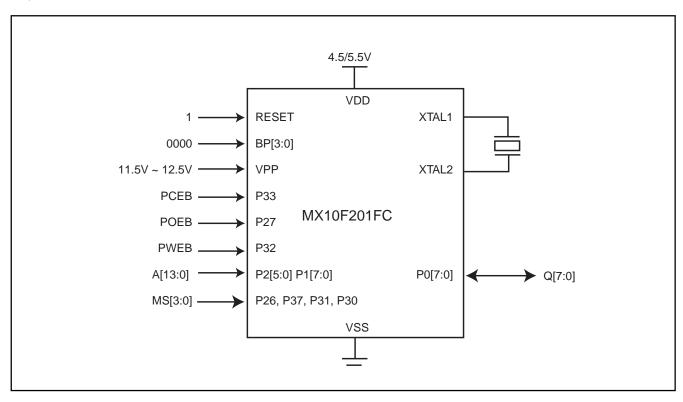

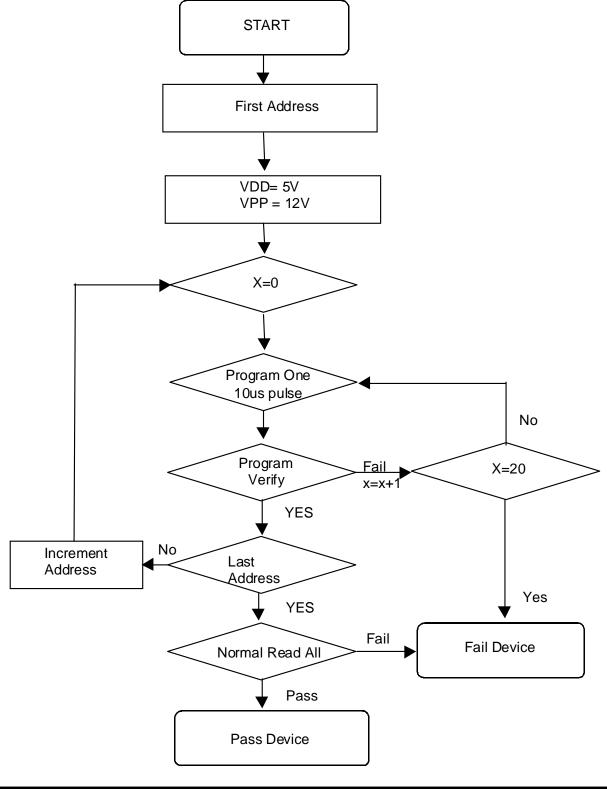

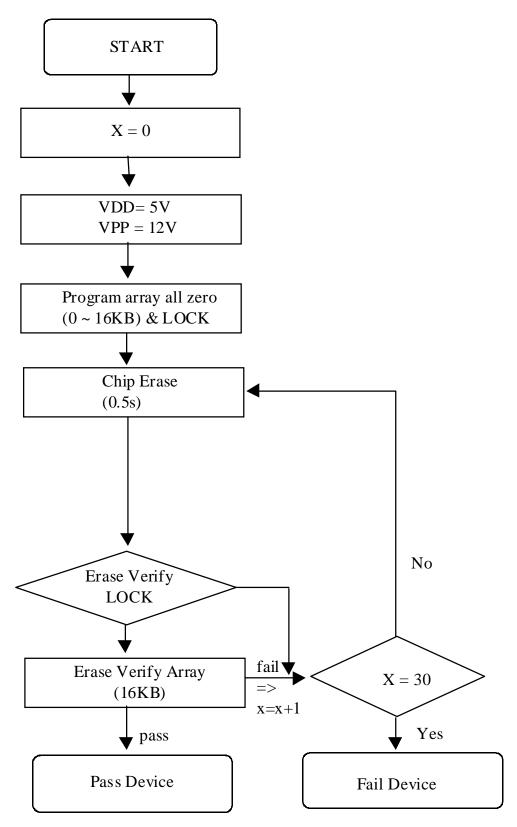

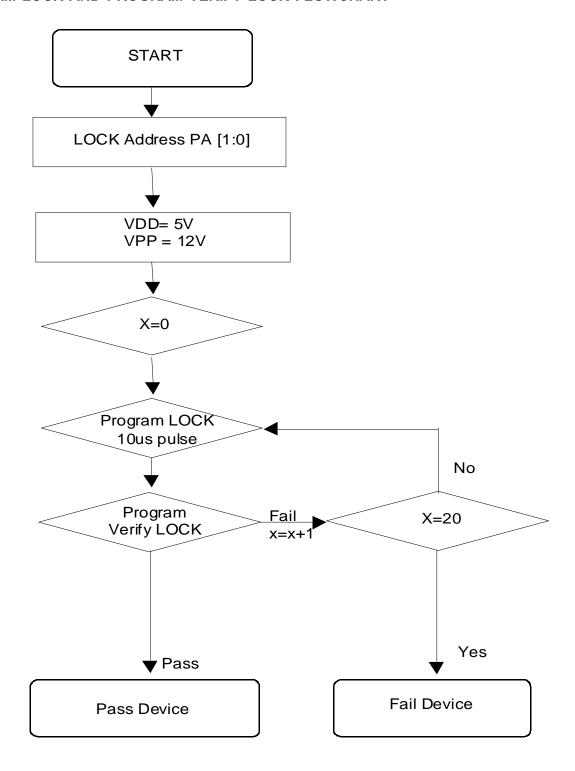

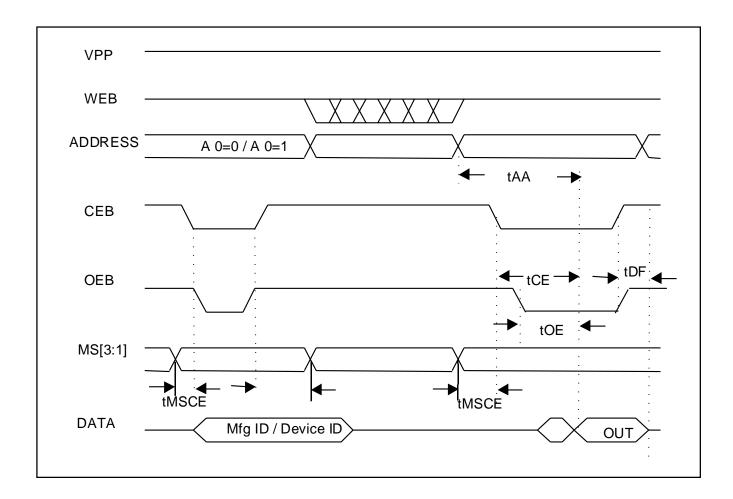

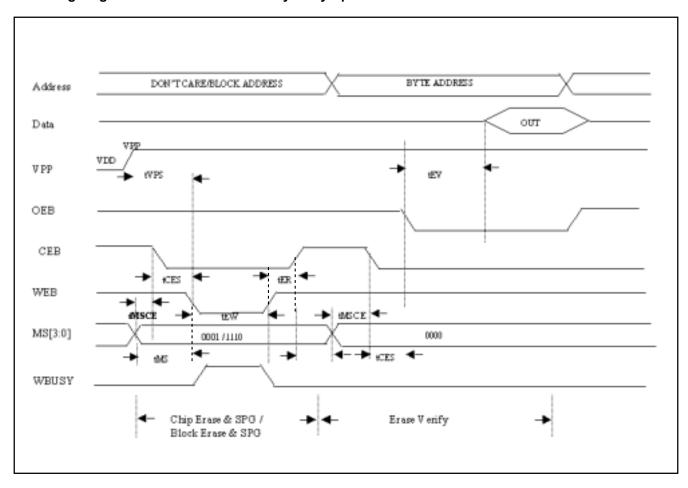

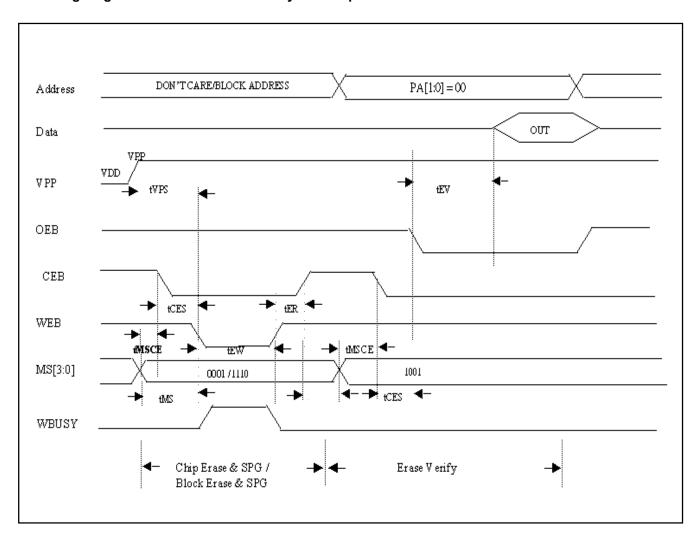

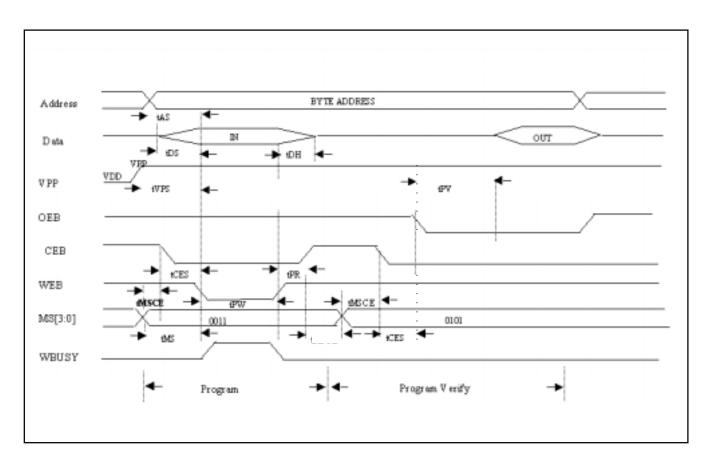

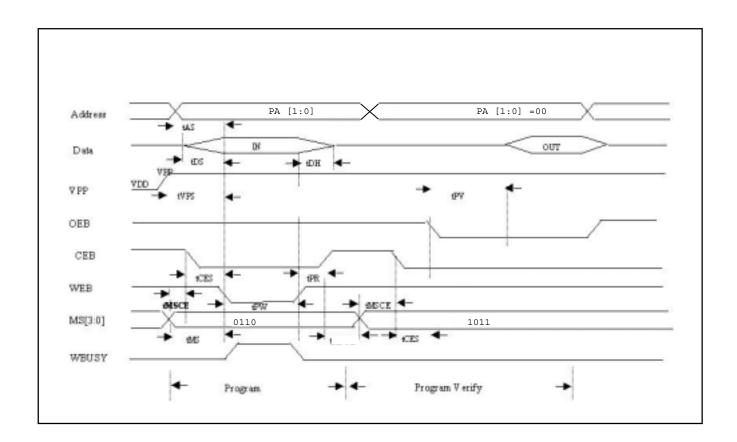

| C6H     |                                                         | SE                                                              | G21                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SEG20                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |