# NUC501 User's Manual

Publication Release Date: Nov. 2009

nuvoton

### Table of Contents

| 1 | Gen                     | neral Description                                         | 6  |  |  |  |  |  |  |  |  |

|---|-------------------------|-----------------------------------------------------------|----|--|--|--|--|--|--|--|--|

| 2 |                         | iture                                                     | 6  |  |  |  |  |  |  |  |  |

| 3 |                         | Pad and Pin Configuration 9                               |    |  |  |  |  |  |  |  |  |

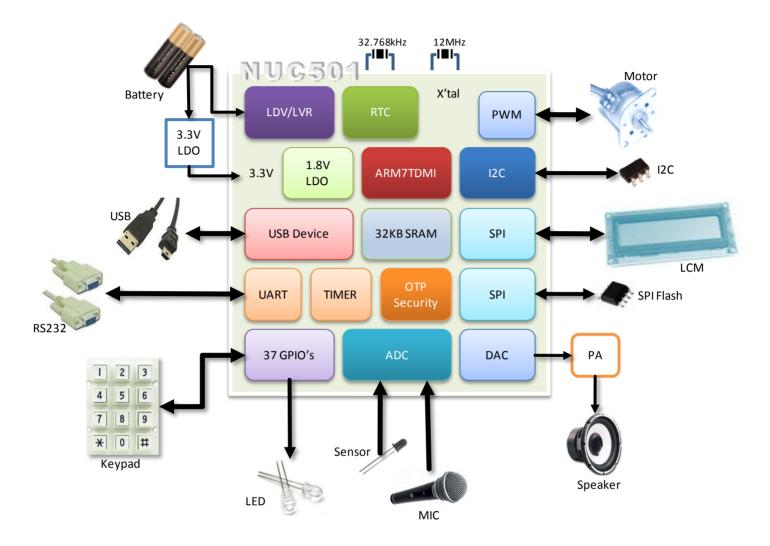

| 4 | System Diagram 19       |                                                           |    |  |  |  |  |  |  |  |  |

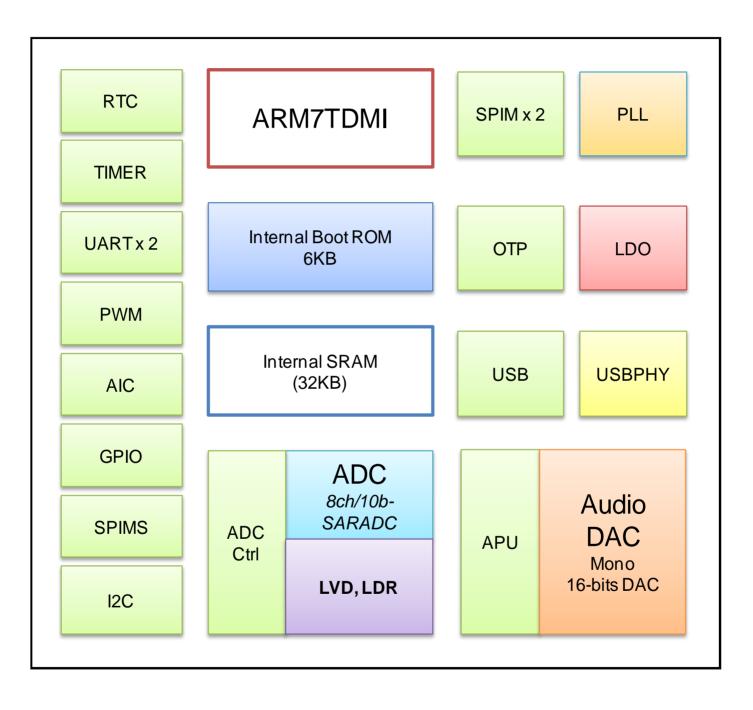

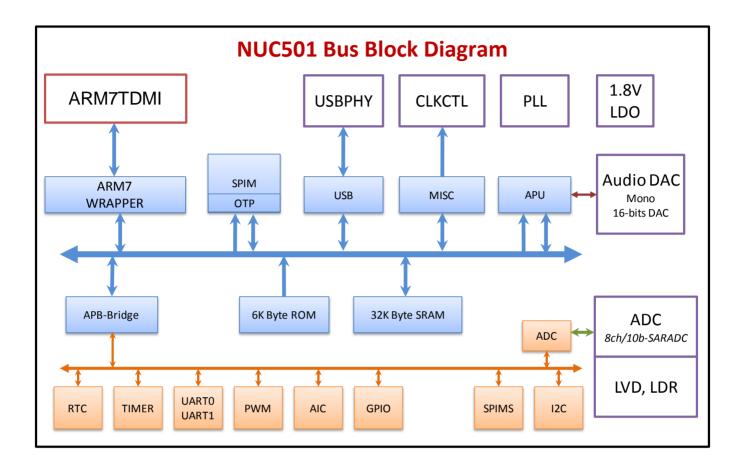

| 5 | -                       | ck Diagram                                                | 20 |  |  |  |  |  |  |  |  |

|   | 5.1                     | System block diagram                                      | 20 |  |  |  |  |  |  |  |  |

|   | 5.2                     | On-Chip Bus block diagram                                 | 21 |  |  |  |  |  |  |  |  |

| 6 | Fun                     | nctional Description                                      | 22 |  |  |  |  |  |  |  |  |

|   | 6.1                     | ARM7TDMI CPU Core                                         | 22 |  |  |  |  |  |  |  |  |

|   | 6.2                     | System Manager                                            | 23 |  |  |  |  |  |  |  |  |

|   | 6.2.1                   | 1 Overview                                                | 23 |  |  |  |  |  |  |  |  |

|   | 6.2.2                   | 2 System Memory Mapping                                   | 23 |  |  |  |  |  |  |  |  |

|   | 6.2.3                   | 3 AHB Bus Arbitration                                     | 25 |  |  |  |  |  |  |  |  |

|   | 6.2.4                   | 4 Fixed Priority Mode                                     | 25 |  |  |  |  |  |  |  |  |

|   | 6.2.5 Power-On Settings |                                                           |    |  |  |  |  |  |  |  |  |

|   | 6.2.6                   | 6 System Manager Control Registers                        | 27 |  |  |  |  |  |  |  |  |

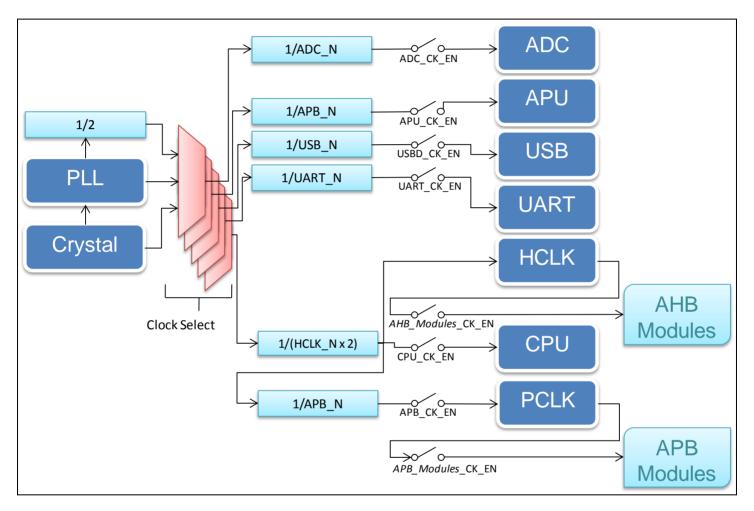

|   | 6.3                     | Clock Controller                                          | 45 |  |  |  |  |  |  |  |  |

|   | 6.3.1                   | 1 Function Description                                    | 45 |  |  |  |  |  |  |  |  |

|   | 6.3.2                   | 2 Clock Control Registers                                 | 45 |  |  |  |  |  |  |  |  |

|   | 6.4                     | SPI Synchronous Serial Interface Controller (Master Mode) | 58 |  |  |  |  |  |  |  |  |

|   | 6.4.1                   | 1 Overview                                                | 58 |  |  |  |  |  |  |  |  |

|   | 6.4.2                   | 2 Features                                                | 58 |  |  |  |  |  |  |  |  |

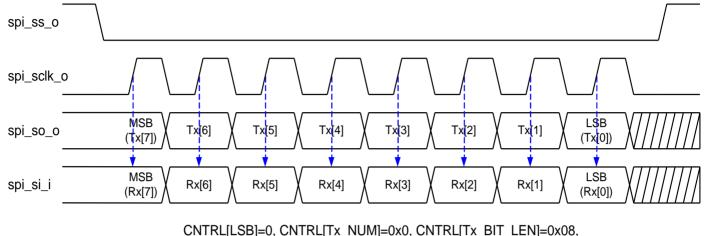

|   | 6.4.3                   | 3 SPIM Timing Diagram                                     | 59 |  |  |  |  |  |  |  |  |

|   | 6.4.4                   | 4 SPIM Programming Example without DMA                    | 59 |  |  |  |  |  |  |  |  |

|   | 6.4.5                   | 5 SPIM Programming Example with DMA                       | 60 |  |  |  |  |  |  |  |  |

|   | 6.4.6                   | 6 Direct memory mapping mode                              | 60 |  |  |  |  |  |  |  |  |

|   | 6.4.7                   | 7 SPIM Serial Interface Control Registers Mapping         | 62 |  |  |  |  |  |  |  |  |

|   | 6.5                     | Audio Processing Unit                                     | 76 |  |  |  |  |  |  |  |  |

|   | 6.5.1                   | 1 Overview and Features                                   | 76 |  |  |  |  |  |  |  |  |

|   | 6.5.2                   | 2 APU Functional Description                              | 76 |  |  |  |  |  |  |  |  |

|   | 6.5.3                   | 3 AUDIO DAC Clock                                         | 76 |  |  |  |  |  |  |  |  |

|   | 6.5.4                   | 4 APU Run Procedures                                      | 76 |  |  |  |  |  |  |  |  |

|   | 6.5.5                   | 5 APU Control Register Mapping                            | 78 |  |  |  |  |  |  |  |  |

| 6.5.6     APU Control Registers     79       6.6     SRAM Controller     87       6.6.1     Overview     87       6.6.2     Features     87       6.6.3     SRAM Block Diagram     88       6.6.4     SRAM System Diagram     89       6.6.5     SRAM Register Mapping     91       6.7     USB Device Controller     94       6.7.1     Overview     94       6.7.2     Features     94       6.7.3     Functional Descriptions     95       6.7.4     Memory Mapping     95       6.7.5     USB Control Registers Mapping     97       6.9.1     Overview     113       6.9.2     Features     113       6.9.3     Interrupt Controller     113       6.9.4     AIC Functional Descriptions     113       6.9.2     Features     113       6.9.3     Interrupt Sources     114       6.9.4     AIC Functional Descriptions     116       6.9.5     AIC Registers Mapping     118       6.9.6     AIC Control Registers     120       6.10     General Purpose I/O     134       6.10.1     Overview and Features     134       6.10.2     GPIO Control Register Mapping     135   <                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.6.1       Overview       87         6.6.2       Features       87         6.6.3       SRAM Block Diagram       88         6.6.4       SRAM System Diagram       89         6.6.5       SRAM Function Description       90         6.6.6       SRAM Register Mapping       91         6.7       USB Device Controller       94         6.7.1       Overview       94         6.7.2       Features       94         6.7.3       Functional Descriptions       95         6.7.4       Memory Mapping       96         6.7.5       USB Control Registers Mapping       97         6.9.1       Overview       113         6.9.1       Overview       113         6.9.2       Features       113         6.9.3       Interrupt Controller       113         6.9.4       AIC Functional Descriptions       116         6.9.5       AIC Registers Mapping       118         6.9.6       AIC Control Registers       120         6.10       General Purpose I/O       134         6.10.1       Overview and Features       134         6.10.2       GPIO Control Register Mapping       135                                      |

| 6.6.2       Features       87         6.6.3       SRAM Block Diagram       88         6.6.4       SRAM System Diagram       89         6.6.5       SRAM Function Description       90         6.6.6       SRAM Register Mapping       91         6.7       USB Device Controller       94         6.7.1       Overview       94         6.7.2       Features       94         6.7.3       Functional Descriptions       95         6.7.4       Memory Mapping       96         6.7.5       USB Control Registers Mapping       97         6.9       Advanced Interrupt Controller       113         6.9.1       Overview       113         6.9.2       Features       113         6.9.3       Interrupt Sources       114         6.9.4       AIC Functional Descriptions       116         6.9.5       AIC Registers Mapping       118         6.9.6       AIC Control Registers       120         6.10       General Purpose I/O       134         6.10.1       Overview and Features       134         6.10.2       GPIO Control Register Mapping       135         6.10.3       GPIO Control Register Description     |

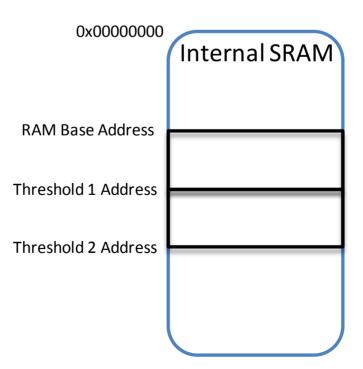

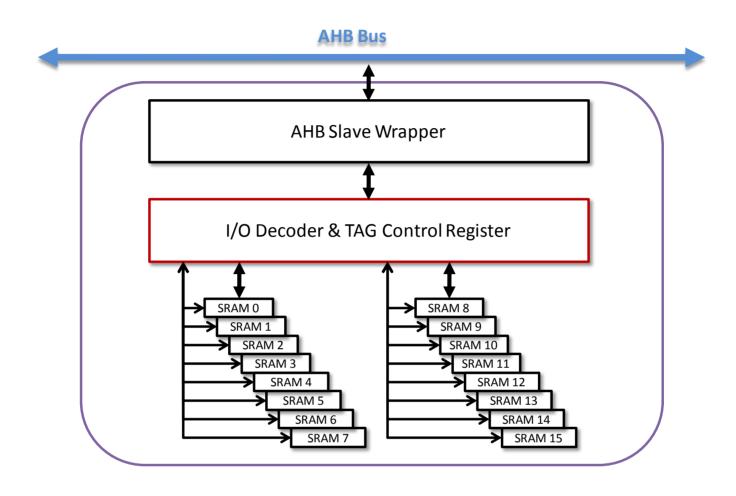

| 6.6.3       SRAM Block Diagram       88         6.6.4       SRAM System Diagram       89         6.6.5       SRAM Function Description       90         6.6.6       SRAM Register Mapping       91         6.7       USB Device Controller       94         6.7.1       Overview       94         6.7.2       Features       94         6.7.3       Functional Descriptions       95         6.7.4       Memory Mapping       96         6.7.5       USB Control Registers Mapping       97         6.9       Advanced Interrupt Controller       113         6.9.1       Overview       113         6.9.2       Features       113         6.9.3       Interrupt Sources       114         6.9.4       AIC Functional Descriptions       116         6.9.5       AIC Registers Mapping       118         6.9.6       AIC Control Registers       120         6.10       General Purpose I/O       134         6.10.1       Overview and Features       134         6.10.2       GPIO Control Register Mapping       135         6.10.3       GPIO Control Register Mapping       135         6.10.3       GPIO Control R |

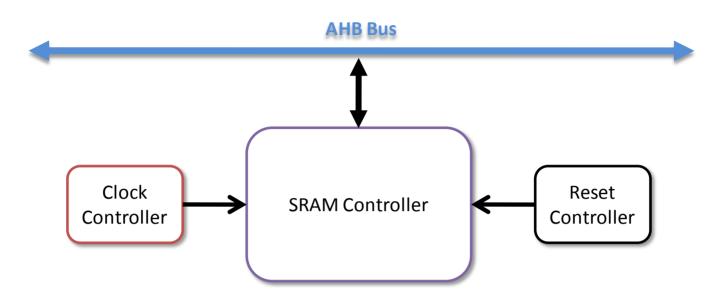

| 6.6.4       SRAM System Diagram       89         6.6.5       SRAM Function Description       90         6.6.6       SRAM Register Mapping       91         6.7       USB Device Controller       94         6.7.1       Overview       94         6.7.2       Features       94         6.7.3       Functional Descriptions       95         6.7.4       Memory Mapping       96         6.7.5       USB Control Registers Mapping       97         6.9       Advanced Interrupt Controller       113         6.9.1       Overview       113         6.9.2       Features       113         6.9.3       Interrupt Sources       114         6.9.4       AIC Functional Descriptions       116         6.9.5       AIC Registers Mapping       118         6.9.6       AIC Control Registers       120         6.10       General Purpose I/O       134         6.10.1       Overview and Features       134         6.10.2       GPIO Control Register Mapping       135         6.10.3       GPIO Control Register Description       136         6.11       I2C Synchronous Serial Interface       157                   |

| 6.6.5SRAM Function Description906.6.6SRAM Register Mapping916.7USB Device Controller946.7.1Overview946.7.2Features946.7.3Functional Descriptions956.7.4Memory Mapping966.7.5USB Control Registers Mapping976.9Advanced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.6.6SRAM Register Mapping916.7USB Device Controller946.7.1Overview946.7.2Features946.7.3Functional Descriptions956.7.4Memory Mapping966.7.5USB Control Registers Mapping976.9Advanced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1356.10.3GPIO Control Register Description1366.10.1I2C Synchronous Serial Interface137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6.7USB Device Controller946.7.1Overview946.7.2Features946.7.3Functional Descriptions956.7.4Memory Mapping966.7.5USB Control Registers Mapping976.9Advanced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1356.10.3GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.7.1       Overview       94         6.7.2       Features       94         6.7.3       Functional Descriptions       95         6.7.4       Memory Mapping       96         6.7.5       USB Control Registers Mapping       97         6.9       Advarced Interrupt Controller       113         6.9.1       Overview       113         6.9.2       Features       113         6.9.3       Interrupt Sources       114         6.9.4       AIC Functional Descriptions       116         6.9.5       AIC Registers Mapping       118         6.9.6       AIC Control Registers       120         6.10       General Purpose I/O       134         6.10.2       GPIO Control Register Mapping       135         6.10.3       GPIO Control Register Description       136         6.10.1       Overview and Features       134         6.10.3       GPIO Control Register Description       136         6.10.1       IZVerview Control Register Description       136         6.10.1       IZVerview Serial Interface       137                                                                                            |

| 6.7.2Features946.7.3Functional Descriptions956.7.4Memory Mapping966.7.5USB Control Registers Mapping976.9Advarced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.7.3Functional Descriptions956.7.4Memory Mapping966.7.5USB Control Registers Mapping976.9Advanced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1356.10.2GPIO Control Register Description1366.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.7.4Memory Mapping966.7.5USB Control Registers Mapping976.9Advanced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1356.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.7.5USB Control Registers Mapping976.9Advanced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.9Advanced Interrupt Controller1136.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6.9.1Overview1136.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Surchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.9.2Features1136.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.9.3Interrupt Sources1146.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Suchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.9.4AIC Functional Descriptions1166.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6.9.5AIC Registers Mapping1186.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.9.6AIC Control Registers1206.10General Purpose I/O1346.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

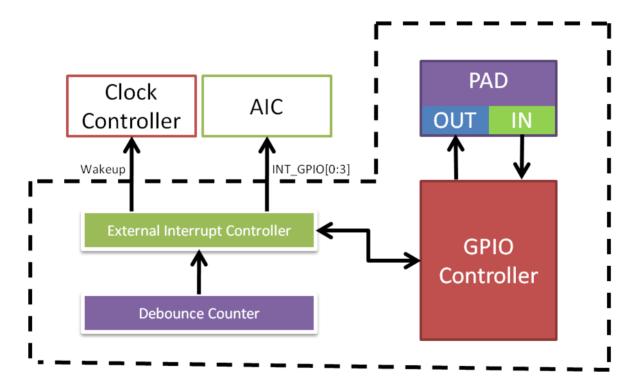

| 6.10 General Purpose I/O1346.10.1 Overview and Features1346.10.2 GPIO Control Register Mapping1356.10.3 GPIO Control Register Description1366.11 I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6.10.1Overview and Features1346.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6.10.2GPIO Control Register Mapping1356.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.10.3GPIO Control Register Description1366.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6.11I2C Synchronous Serial Interface157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6 11 1 Overview 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0.11.1 Overview 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.11.2 Feature 157                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

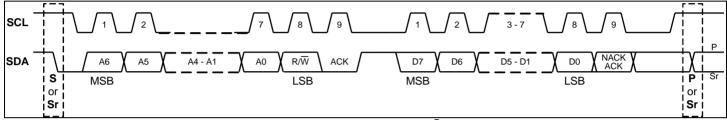

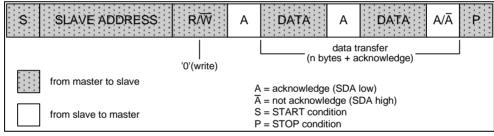

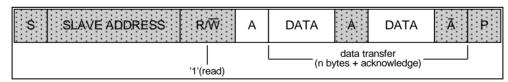

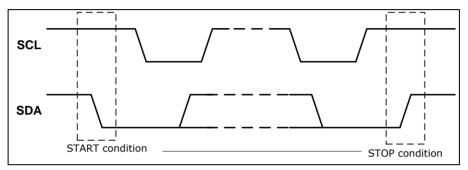

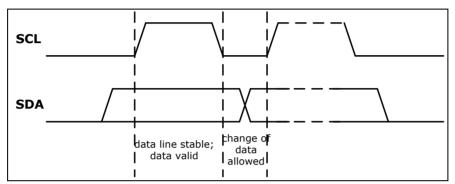

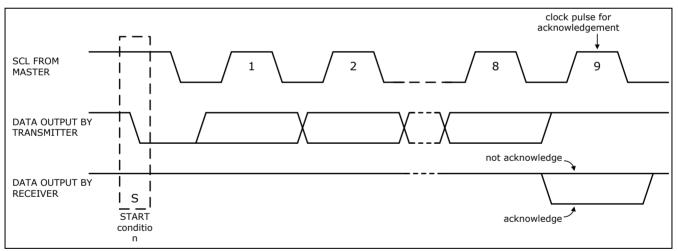

| 6.11.3 I <sup>2</sup> C Protocol 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

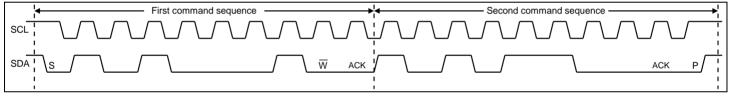

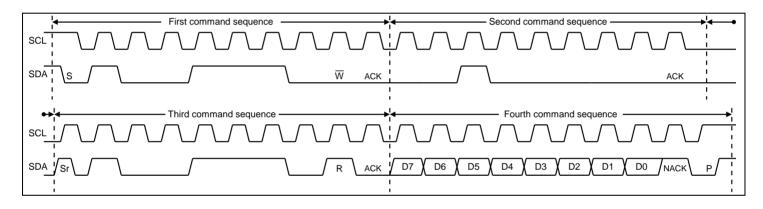

| 6.11.4 I <sup>2</sup> C Programming Examples 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

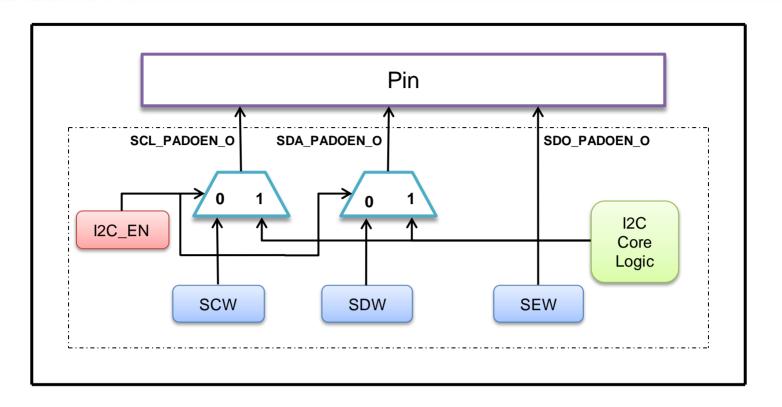

| 6.11.5 Software I <sup>2</sup> C Operation 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6.11.6 I <sup>2</sup> C Serial Interface Control Registers Mapping 164                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6.12 PWM-Timer 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6.12.1 Introduction 172                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.12.2 Features 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6.12.3 PWM Timer Start Procedure 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

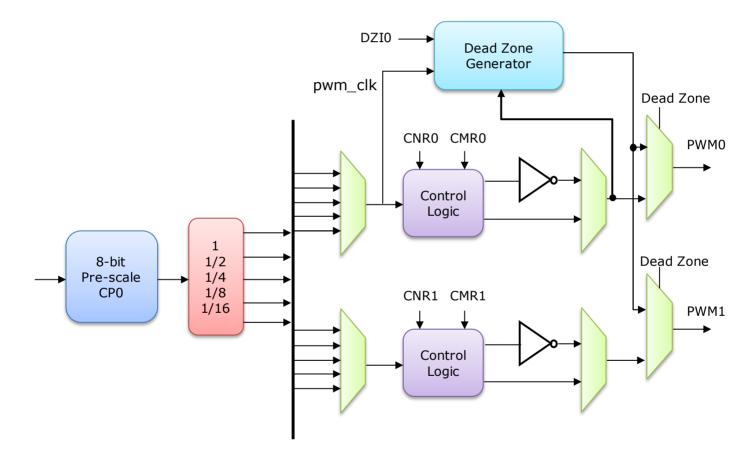

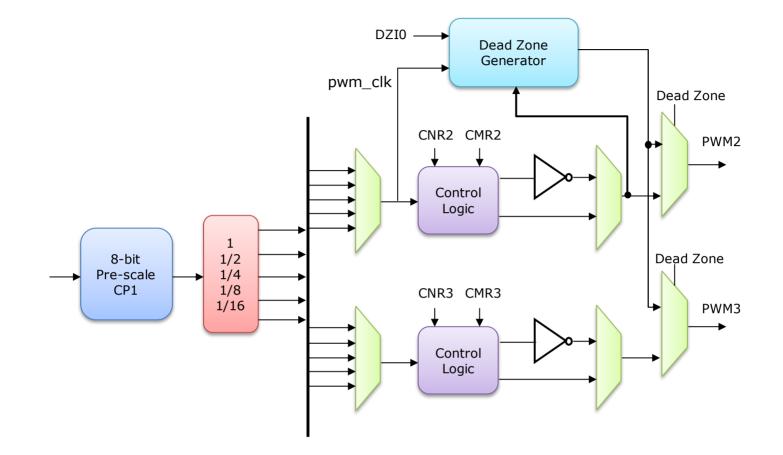

| 6.12.4 PWM Architecture 174                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

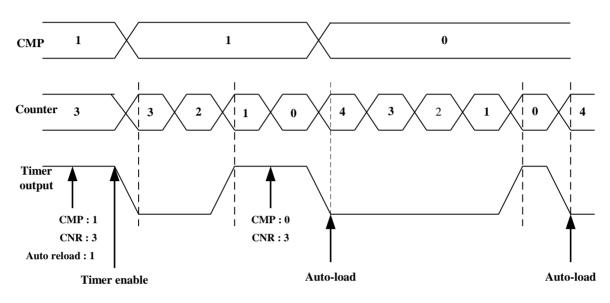

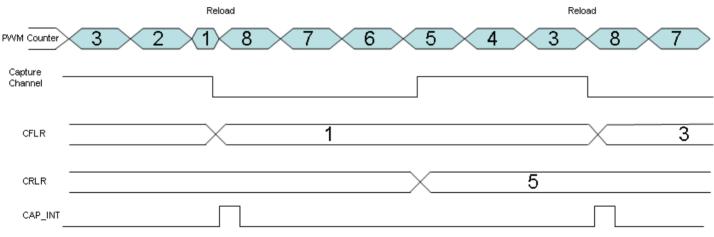

| 6.12.5 Basic Timer Operation 176                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

### NUC501

# nuvoton

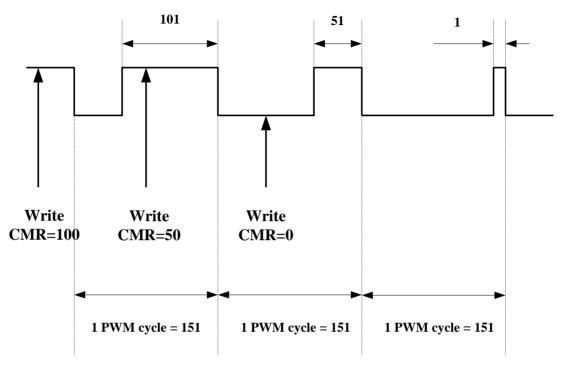

| 6.12  | 2.6 P\             | WM Double Buffering and Automatic Reload          | 176 |  |  |

|-------|--------------------|---------------------------------------------------|-----|--|--|

| 6.12  | 2.7 M              | lodulate Duty Ratio                               | 177 |  |  |

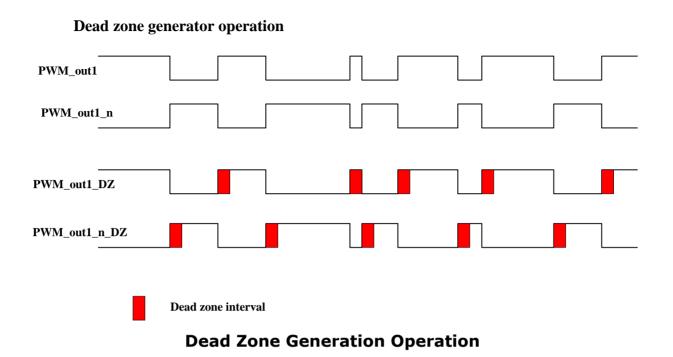

| 6.12  | 2.8 De             | ead-Zone Generator                                | 178 |  |  |

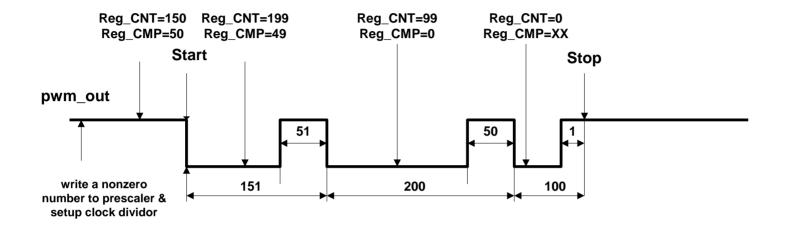

| 6.12  | 2.9 P\             | WM Timer Start Procedure                          | 179 |  |  |

| 6.12  | 2.10 P             | WM Timer Stop Procedure                           | 179 |  |  |

| 6.12  | 2.11 P             | WM Timer Register Mapping                         | 181 |  |  |

| 6.13  | Register           | r Description                                     | 182 |  |  |

| 6.14  | Real Tin           | ne Clock (RTC)                                    | 199 |  |  |

| 6.14  | 4.1 O <sup>r</sup> | verview                                           | 199 |  |  |

| 6.14  | 4.2 R <sup>-</sup> | TC Features                                       | 199 |  |  |

| 6.14  | 4.3 R <sup>-</sup> | TC Function Description                           | 200 |  |  |

| 6.14  | 1.4 R <sup>-</sup> | TC Register Mapping                               | 202 |  |  |

| 6.14  | 1.5 R <sup>-</sup> | TC Register Descriptions                          | 203 |  |  |

| 6.15  | Serial P           | eripheral Interface Controller (SPI Master/Slave) | 216 |  |  |

| 6.15  | 5.1 SI             | PI Function Description and Features              | 216 |  |  |

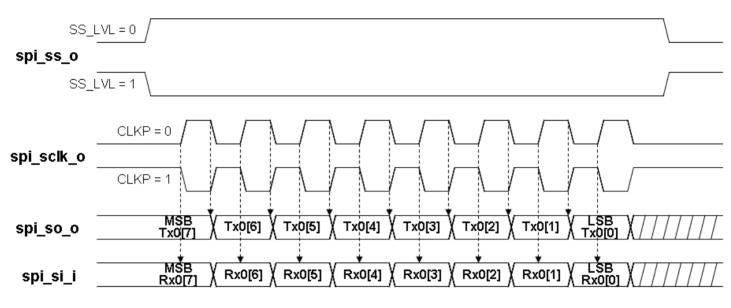

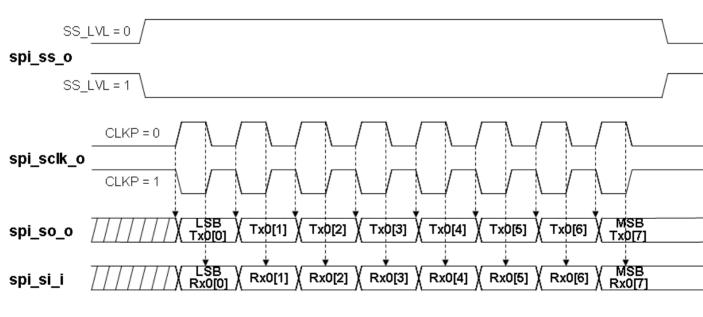

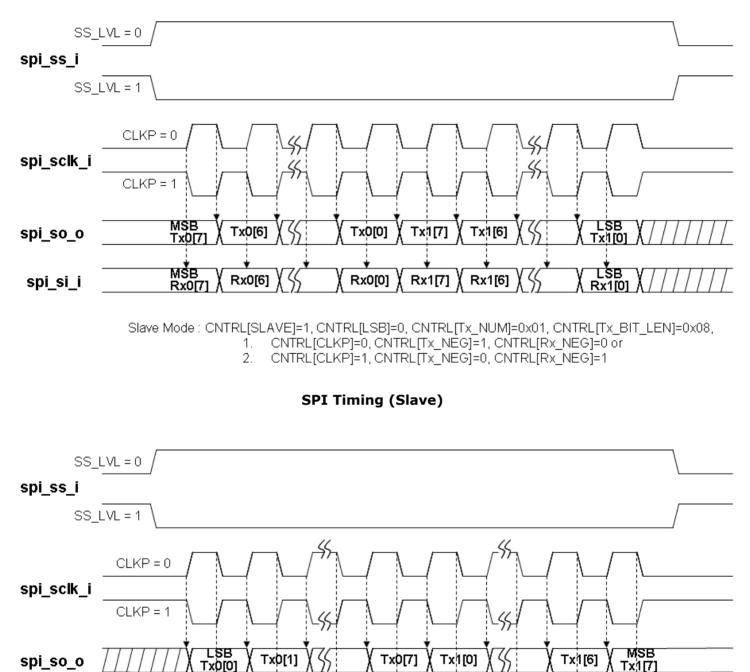

| 6.15  | 5.2 SI             | PIMS Timing Diagram                               | 217 |  |  |

| 6.15  | 5.3 SI             | PIMS Programming Example                          | 219 |  |  |

| 6.15  | 5.4 SI             | PIMS Serial Interface Control Register Map        | 220 |  |  |

| 6.15  | 5.5 SI             | PIMS Control Register Description                 | 221 |  |  |

| 6.16  | TIMER (            | Controller                                        | 228 |  |  |

| 6.16  | 6.1 G              | eneral Timer Controller                           | 228 |  |  |

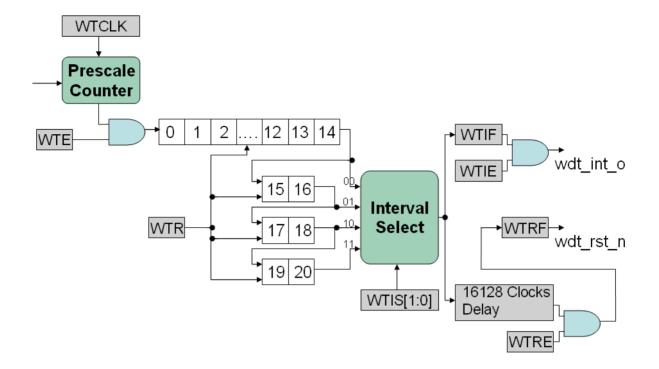

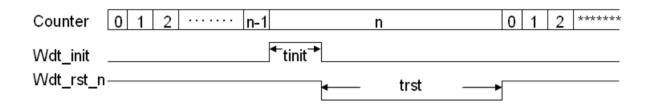

| 6.16  | 6.2 W              | /atchdog Timer                                    | 228 |  |  |

| 6.16  | 6.3 Ti             | imer Control Registers Map                        | 230 |  |  |

| 6.17  | UART Ir            | nterface Controller                               | 239 |  |  |

| 6.17  | 7.1 O <sup>r</sup> | verview                                           | 239 |  |  |

| 6.17  | 7.2 Fe             | eatures:                                          | 239 |  |  |

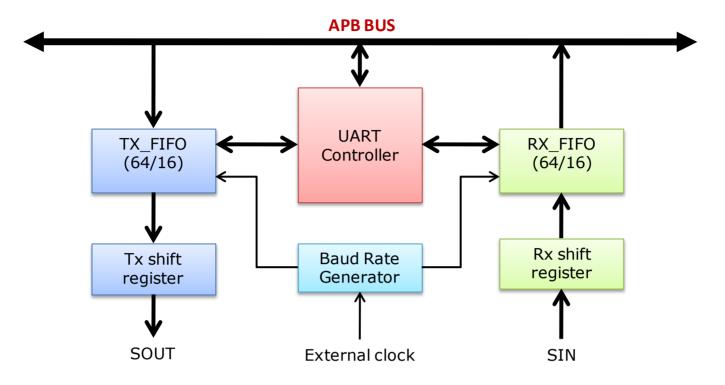

| 6.17  | 7.3 BI             | lock Diagram                                      | 239 |  |  |

| 6.17  | 7.4 Fu             | unctional Blocks Descriptions                     | 240 |  |  |

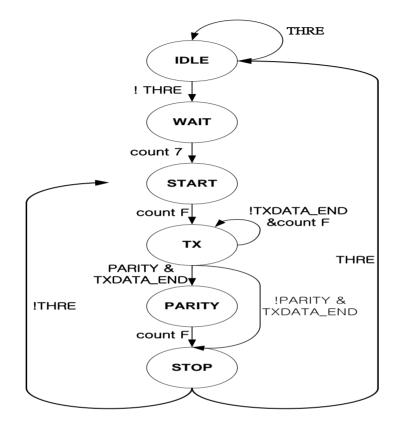

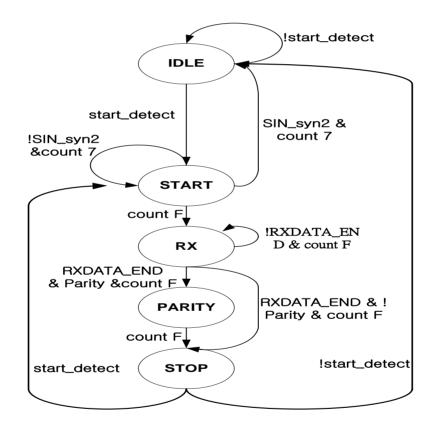

| 6.17  | 7.5 Fi             | inite State Machine                               | 242 |  |  |

| 6.17  | 7.6 U              | ART Interface Control Registers Mapping           | 245 |  |  |

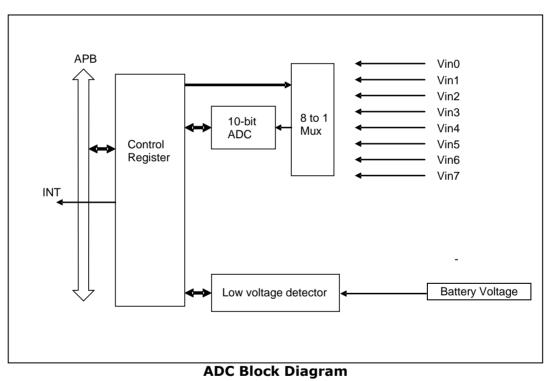

| 6.18  | Analog t           | to Digital Converter                              | 263 |  |  |

| 6.18  | 3.1 F€             | eatures                                           | 263 |  |  |

| 6.18  | 3.2 AI             | DC Functional Description                         | 263 |  |  |

| 6.18  | 3.3 AI             | DC Control Register Mapping                       | 264 |  |  |

| 6.18  | 3.4 AI             | DC Control Register Description                   | 266 |  |  |

| 7 Ele | ctrical G          | Characteristics                                   | 277 |  |  |

| 7.1   | Absolute           | e Maximum Ratings                                 | 277 |  |  |

| 7.2   | DC Specifications  |                                                   |     |  |  |

### NUC501

# nuvoTon

| 7 | .3 AC S | pecifications                 | 277 |

|---|---------|-------------------------------|-----|

|   | 7.3.1   | Audio DAC Characteristic      | 277 |

|   | 7.3.2   | ADC Characteristic            | 278 |

|   | 7.3.3   | Voice Recorder Characteristic | 278 |

| 8 | Package | Specifications                | 279 |

### **1** General Description

The NUC501 is an ARM7TDMI-based MCU, specifically designed to offer low-cost and high performance for various applications, like interactive toys, edutainment robots, and home appliances. It integrates the 32-bit RISC CPU with 32KB high-speed SRAM, crypto engine with OTP key, boot ROM, LDO regulator, ADC, DAC, I2C, SPI, USB2.0 FS Device, & GPIO into a cost-affordable while feature-rich micro-controller.

Owing to the simplicity of the NUC501 architecture that boots SpiMemory into the high-speed SRAM for program execution, the total system BOM is reduced to its minimum. Unlike usual ARM-based MCU products, the NUC501 operates without the use of SDRAM, which is usually the source of complexity, higher power consumption, and cost.

The ARM7TDMI runs up to 108MHz on the high-speed SRAM to offer enough horsepower for many MIPS-hungry tasks, while the remaining MIPS is still able to serve the need of application program. For those applications, like cartridge games, that require large code storage and variation of game play scenarios, the patented Extensible XIP Addressing on SpiMemory gives the flexibility whenever program execution speed is not a critical concern.

To protect the code against illegal pirating, the NUC501 provides a crypto engine that works with internal OTP2 key to encrypt the data stored at external SpiMemory when the design-in is finished. Without the knowledge of the OTP key, others can't decrypt the data even by means of ICE debugging.

The NUC501 is designed with special care to minimize the power consumption while allowing for the flexibility to reach for high performance. It includes the clock gating, variable frequency control for individual IP's, and bus control to reduce signal toggle. Besides, the NUC501 can be further operated under different power-saving modes: idle, power down with RTC active, and power down mode.

With so many practical peripherals integrated around the high-performance ARM7 CPU, the NUC501 is suitable for such applications as Interactive toys, edutainment robots, and home appliances. Whenever MIPS-hungry task meets cost-effective demand, you'll find the NUC501 truly useful to satisfy the requirement.

### 2 Feature

#### • 32-bit RISC CPU

- ARM7TDMI @ 108 MHz

- 16-bit Thumb mode supported to save code size

- Embedded 32 KB Local Memory divided into 16 segments for easier S/W programming

- Boot from SpiMemory or USB

- Program download into SRAM through JTAG before OTP key programmed

- Integrate JTAG port to support real time, non-stop ICE function for system development and debugging

#### • 6KB internal ROM

- Boot loader

- ICP for SpiFlash & security OTP key via USB

#### • 32KB internal SRAM

- Embedded 32KB SRAM for code and data

- 16 segments with address tags

- SpiMemory interface with code protection

- DMA mode for code booting from SpiMemory to internal SRAM

- Direct CPU read access from SpiMemory

- 128-bit OTP key for code protection against illegal pirating

- 2-bit SPI mode supported for doubling data transfer rate

- Shared (when not in use) with other SPI device for high-speed transfer via DMA

#### • Audio Process Unit

- Mono 16-bit Sigma-Delta DAC output

- Equalization function supported

- USB 2.0 Full speed device

- 6 programmable endpoints for Control, Bulk In/Out, Interrupt and Isochronous transfers

- 512-byte buffer

- Auto suspend function

- Remote wakeup capability

- **I**<sup>2</sup>**C**

- Compatible with Philips I<sup>2</sup>C standard

- Master mode

- SPI

- Programmable master/slave mode

- Speed up to 40MHz

#### • 4 Channel PWM

- Four 16-bit timers

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Capture and compare function

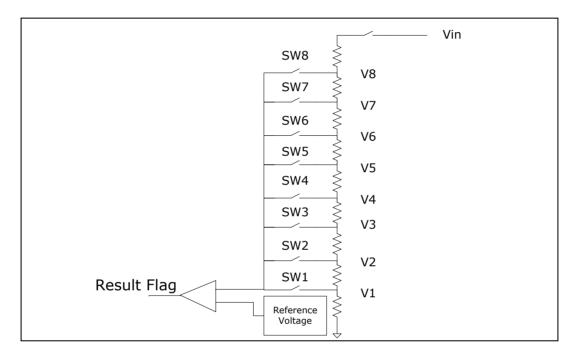

- Analog to Digital Converter

- 10-bit x 8-ch ADC for sensor, MIC, LVD, LVR

- Maximum conversion rate: 400K samples per second

- Power supply voltage: 3.3V

- Analog input voltage range: 0 ~ 3.3 volts

- Support wait-for-trigger mode & standby mode

- Dedicated LVD/LVR

- 8-level voltage detection

- Miscellaneous

- Two programmable 32-bit timers with 8-bit pre-scale

- One 32-bit watch dog timer

- 32.768KHz RTC function support

- Up to 26/37 GPIO pins for LQFP-48 / LQFP-64

- Two UART ports with flow control (TX, RX, CTS and RTS) and UART0 is for high speed

- Power management modes: normal, idle, power down with RTC, and power down

- 3.3V to 1.8V 200mA LDO regulator

- Software Support

- GNU-based, open-source IDE: compiler, linker and debugger

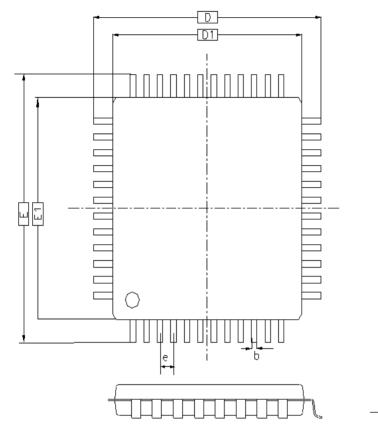

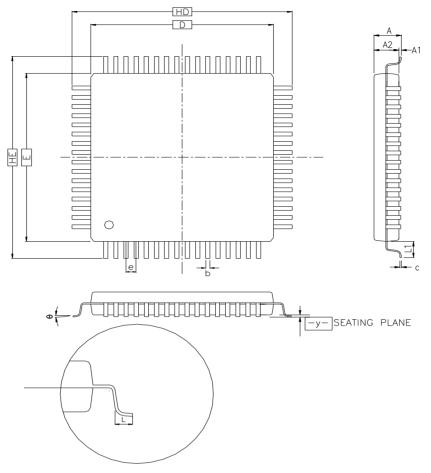

- Technology & Package

- 0.18um CMOS

- 3.3-volt single supply

- LQFP-48 (NUC501ADN)/ LQFP-64(NUC501BDN)

## **3 Pad and Pin Configuration**

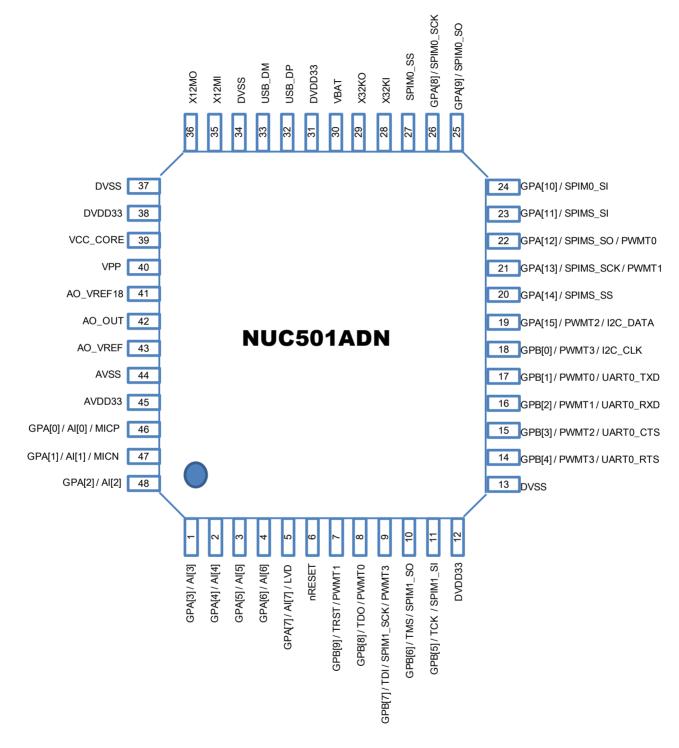

#### LQFP-48 Pin Out

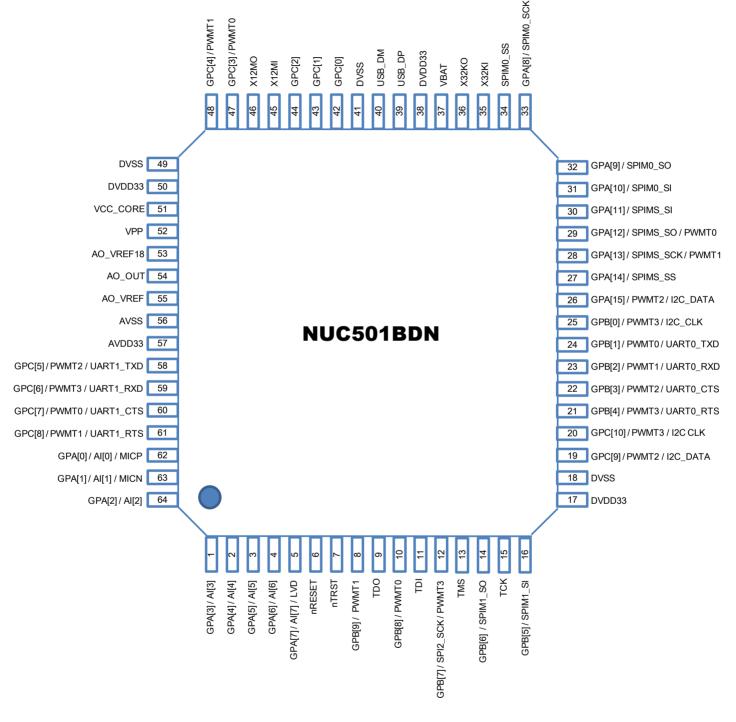

#### LQFP-64 Pin Out

### **Pin Descriptions**

In order to maximize the NUC501 application for different field, each pin of NUC501 is very flexible and can play up to four different functions. The user can program each pin to the wanted function for the different product.

The pin functions are controlled by the registers PAD\_REG0, PAG\_REG1 and PAD\_REG2. For each multiple function pin, the default function is the GPIO. When the user programs the PAD\_REG, the pins play the alternative function. If the different alternative functions are enabled simultaneous, the priority is

#### Alternative Function 1 > Alternative Function 2 > Alternative Function 3 > Default Function

For example:

If the GPA[12] is configured to be SPIMS\_SO by PAD\_REG1 and it is also configured to be PWMT0 by PAD\_REG0, the actual function of GPA[12] would be SPIMS\_SO because the SPIMS\_SO function priority is higher than PWMT0.

Except the multiple functions, each NUC501 output driving current strength is also controllable. The driving strength control register is the GPA\_DS, GPB\_DS and GPC\_DS. For different pin the driving can be 4mA or 8mA and 12mA or 16mA. For example, user can control the GPB[1] strength to 16mA and directed drive the high current LED to save PCB extra component to reduce the BOM cost.

| Default Function<br>Name | Alternative<br>Function 1 | Alternative<br>Function 2 | Alternative<br>Function 3 | Power on<br>setting |

|--------------------------|---------------------------|---------------------------|---------------------------|---------------------|

| GPIO                     |                           |                           |                           |                     |

| GPA[0]                   | AI[0]                     | MIC+                      |                           |                     |

| GPA[1]                   | AI[1]                     | MIC-                      |                           |                     |

| GPA[2]                   | AI[2]                     |                           |                           |                     |

| GPA[3]                   | AI[3]                     |                           |                           |                     |

| GPA[4]                   | AI[4]                     |                           |                           |                     |

| GPA[5]                   | AI[5]                     |                           |                           |                     |

| GPA[6]                   | AI[6]                     |                           |                           |                     |

| GPA[7]                   | AI[7]                     | LVD                       |                           |                     |

|                          | SPIM0_SS(Master)          |                           |                           |                     |

| GPA[8]                   | SPIM0_SCK                 |                           |                           | Power on set (IBR)  |

| GPA[9]                   | SPIM0_SO                  |                           |                           | Power on set (IBR)  |

| GPA[10]                  | SPIM0_SI                  |                           |                           |                     |

# nuvoTon

| GPA[11]      | SPIMS_SI        |           |           |                       |

|--------------|-----------------|-----------|-----------|-----------------------|

| GPA[12]      | SPIMS_SO        | PWMT0     |           | Power on set (IBR)    |

| GPA[13]      | SPIMS_SCK       | PWMT1     |           | Power on set (48/64)  |

| GPA[14]      | SPIMS_SS(Slave) | USB_DET   |           |                       |

| GPA[15]      | PWMT2           | USB_DET   | I2C_DATA  |                       |

| GPB[0]       | PWMT3           | USB_DET   | I2C_CLK   |                       |

| GPB[1]       | PWMT0           | USB_DET   | UART0_TXD | Power on set (ICE)    |

| GPB[2]       | PWMT1           | USB_DET   | UART0_RXD |                       |

| GPB[3]       | PWMT2           | USB_DET   | UART0_CTS |                       |

| GPB[4]       | PWMT3           | USB_DET   | UART0_RTS | Power on set (SPI_S0) |

| GPB[5]       | тск             | SPIM1_SI  |           |                       |

| GPB[6]       | TMS             | SPIM1_SO  | PWMT2     |                       |

| GPB[7]       | TDI             | SPIM1_SCK | PWMT3     |                       |

| GPB[8]       | TDO             | USB_DET   | РШМТО     | Power on set (SPI_S1) |

| GPB[9]       | nTRST           | USB_DET   | PWMT1     |                       |

| Audio DAC    |                 |           |           |                       |

| AO_OUT0      |                 |           |           |                       |

| AO_REF18     |                 |           |           |                       |

| AO_VREF      |                 |           |           |                       |

| USB2.0 Devic | ce              |           |           |                       |

| USB_DP       |                 |           |           |                       |

| USB_DM       |                 |           |           |                       |

| MISC         |                 |           |           |                       |

| nRESET       |                 |           |           |                       |

| X12M         |                 |           |           |                       |

| EX12M        |                 |           |           |                       |

| Х32К         |                 |           |           |                       |

| EX32K        |                 |           |           |                       |

| VPP (6.5V)           |           |           |  |

|----------------------|-----------|-----------|--|

| VBAT                 |           |           |  |

| USBVDD33             |           |           |  |

| DVDD33               |           |           |  |

| DVDD33               |           |           |  |

| AVDD33               |           |           |  |

| DVSS                 |           |           |  |

| DVSS                 |           |           |  |

| DVSS                 |           |           |  |

| AVSS                 |           |           |  |

| VCC_CORE<br>(OUTPUT) |           |           |  |

| Pin Function fo      | r LQFP 64 |           |  |

| тск                  |           |           |  |

| TMS                  |           |           |  |

| TDI                  |           |           |  |

| TDO                  |           |           |  |

| nTRST                |           |           |  |

| GPC[0]               | SPIM1_SO  | USB_DET   |  |

| GPC[1]               | SPIM1_SI  | USB_DET   |  |

| GPC[2]               | SPIM1_SCK | USB_DET   |  |

| GPC[3]               | РѠМТО     | USB_DET   |  |

| GPC[4]               | PWMT1     | USB_DET   |  |

| GPC[5]               | PWMT2     | UART1_TXD |  |

| GPC[6]               | PWMT3     | UART1_RXD |  |

| GPC[7]               | РѠМТО     | UART1_CTS |  |

| GPC[8]               | PWMT1     | UART1_RTS |  |

| GPC[9]               | PWMT2     | I2C_DATA  |  |

| GPC[10]              | PWMT3     | I2C_CLK   |  |

Table4.1 Pin function

| Symbol                      | СОВ | LQFP64 | LQFP48 | ТҮРЕ                              | Description                                                                                                                                                                                                                                   |

|-----------------------------|-----|--------|--------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPA[0] /<br>AI[0] /<br>MICP | 79  | 62     | 46     | 4/8mA I/O<br>with<br>Analog input | GPA[0] – General purpose input/output<br>digital pin<br>AI[0] – ADC analog input 0<br>MICP – MIC+                                                                                                                                             |

| GPA[1] /<br>AI[1] /<br>MICN | 80  | 63     | 47     | 4/8mA I/O<br>with<br>Analog input | GPA[1] – General purpose input/output digital pin                                                                                                                                                                                             |

| GPA[2] /<br>AI[2]           | 81  | 64     | 48     | 4/8mA I/O<br>with<br>Analog input | GPA[2] – General purpose input/output<br>digital pin                                                                                                                                                                                          |

| GPA[3] /<br>AI[3]           | 2   | 1      | 1      | 4/8mA I/O<br>with<br>Analog input | GPA[3] – General purpose input/output<br>digital pin                                                                                                                                                                                          |

| GPA[4]/<br>AI[4]            | 3   | 2      | 2      | 4/8mA I/O<br>with<br>Analog input | GPA[4] – General purpose input/output<br>digital pin                                                                                                                                                                                          |

| GPA[5] /<br>AI[5]           | 4   | 3      | 3      | 4/8mA I/O<br>with<br>Analog input | GPA[5]– General purpose input/output digital pin                                                                                                                                                                                              |

| GPA[6] /<br>AI[6]           | 5   | 4      | 4      | 4/8mA I/O<br>with<br>Analog input | GPA[6]– General purpose input/output digital pin                                                                                                                                                                                              |

| GPA[7] /<br>AI[7] /<br>LVD  | 6   | 5      | 5      | 4/8mA I/O<br>with<br>Analog input | GPA[7] – General purpose input/output<br>digital pin                                                                                                                                                                                          |

| GPA[8] /<br>SPIM0_SCK       | 42  | 33     | 26     | 4/8mA<br>I/O                      | GPA[8] – General purpose input/output<br>digital pin<br>SPIM0_SCK - Serial clock output pin for<br>SPIM0                                                                                                                                      |

| GPA[9] /<br>SPIM0_SO        | 41  | 32     | 25     | 4/8mA<br>I/O                      | GPA[9] – General purpose input/output<br>digital pin<br>SPIM0_SO - Serial data input/output pin<br>for SPIM0.<br>Normal SPI mode, this pin is used as data<br>out.<br>Fast SPI read mode, this pin is the 2 <sup>nd</sup> bit<br>for data in. |

| GPA[10] /<br>SPIM0_SI       | 40  | 31     | 24     | 4/8mA<br>I/O                      | GPA[10] – General purpose input/output<br>digital pin<br>SPIM0_SI - Serial data input pin for<br>SPIM0.                                                                                                                                       |

| GPA[11] /<br>SPIMS_SI       | 39  | 30     | 23     | 4/8mA<br>I/O                      | GPA[11] – General purpose input/output<br>digital pin<br>SPIMS_SI - Serial data input pin for<br>SPIMS.                                                                                                                                       |

| GPA[12] /<br>SPIMS_SO /     | 38  | 29     | 22     | 4/8mA<br>I/O                      | GPA[12] – General purpose input/output digital pin                                                                                                                                                                                            |

| PWMT0                 |    |    |      |                | SPIMS_SO - Serial data output pin for                       |

|-----------------------|----|----|------|----------------|-------------------------------------------------------------|

| PWMIU                 |    |    |      |                | SPIMS_SO - Senai data odtput pin foi                        |

|                       |    |    |      |                | PWMT0 – PWM output for timer 0                              |

| GPA[13] /             | 37 | 28 | 21   | 4/8mA          | GPA[13] – General purpose input/output                      |

| SPIMS_SCK             |    |    |      | I/O            | digital pin                                                 |

| /                     |    |    |      |                | SPIMS_SCK - Serial clock pin for SPIMS                      |

| PWMT1                 |    |    |      |                | (master/slave).                                             |

|                       |    |    |      |                | PWMT1 – PWM output for timer 1                              |

| GPA[14] /             | 36 | 27 | 20   | 4/8mA          | GPA[14] – General purpose input/output                      |

| SPIMS_SS /<br>USB_DET |    |    |      | I/O            | digital pin<br>SPIMS_SS - Serial chip select pin for        |

|                       |    |    |      |                | SPINS_33 - Senar chip select pin for<br>SPIMS slave mode.   |

|                       |    |    |      |                | USB_DET – USB detected pin                                  |

| GPA[15] /             | 35 | 26 | 19   | 4/8mA          | GPA[15] – General purpose input/output                      |

| PWMT2 /               |    |    |      | I/O            | digital pin                                                 |

| USB_DET /             |    |    |      |                | PWMT2 – PWM output for timer 2                              |

| IC2_DATA              |    |    |      |                | USB_DET – USB detected pin                                  |

|                       |    |    |      |                | I2C_DATA – I2C data input/output pin, if                    |

|                       |    |    |      |                | this pin is select for I2C function                         |

| GPB[0] /              | 34 | 25 | 18   | 4/8mA          | GPB[0] – General purpose input/output                       |

| PWMT3 /               |    |    |      | I/O            | digital pin<br>PWMT3 – PWM output for timer 3               |

| USB_DET /<br>I2C_CLK  |    |    |      |                | USB_DET- USB detected input                                 |

| 12C_CER               |    |    |      |                | I2C_CLK_ –I2C data output pin, if this pin                  |

|                       |    |    |      |                | is select for I2C function                                  |

| GPB[1] /              | 31 | 24 | 17   | 12/16mA        | GPB[1] – General purpose input/output                       |

| PWMT0 /               |    |    |      | I/O            | digital pin                                                 |

| USB_DET /             |    |    |      |                | PWMT0- PWM output for timer 0                               |

| UART0_TXD             |    |    |      |                | USB_DET- USB detected input                                 |

|                       |    |    |      |                | UARTO_TXD – Data transmitter output pin                     |

|                       | 20 | 22 | 10   | 12/16          | for UARTO (High speed)                                      |

| GPB[2] /<br>PWMT1 /   | 30 | 23 | 16   | 12/16mA<br>I/O | GPB[2] – General purpose input/output<br>digital pin        |

| USB_DET /             |    |    |      | 1/0            | PWMT1 – PWM output for timer 1                              |

| UARTO_RXD             |    |    |      |                | USB DET- USB detected input                                 |

|                       |    |    |      |                | UART0_RXD – Data receiver input pin for                     |

|                       |    |    |      |                | UARTO (High speed)                                          |

| GPB[3] /              | 29 | 22 | 15   | 12/16mA        | GPB[3] – General purpose input/output                       |

| PWMT2 /               |    |    |      | I/O            | digital pin                                                 |

| USB_DET /             |    |    |      |                | PWMT2 – PWM output for timer 2 c                            |

| UART0_CTS             |    |    |      |                | USB_DET- USB detected input                                 |

|                       |    |    |      |                | UARTO_CTS – Clear to Send input pin for                     |

| GPB[4] /              | 28 | 21 | 14   | 12/16mA        | UARTO (High speed)<br>GPB[4] – General purpose input/output |

| PWMT3 /               | 20 |    | 1 14 | I/O            | digital pin                                                 |

| USB_DET /             |    |    |      | 1,0            | PWMT3– PWM output for timer 3                               |

| UARTO_RTS             |    |    |      |                | USB_DET- USB detected input                                 |

|                       |    |    |      |                | UART0_RTS -Request to Send output pin                       |

|                       |    |    |      |                | for UART0 (High speed)                                      |

| GPB[5] /              | 20 | 16 | 11   | 12/16mA        | GPB[5] – General purpose input/output                       |

| TCK /                 |    |    |      | I/O            | digital pin                                                 |

| SPIM1_SI              |    |    |      |                | TCK - JTAG ICE Test Clock pin (LQFP48                       |

|                       |    |    |      |                | only)                                                       |

|                                              |    |    |    |                | SPI2_SI_A -Serial data input pin for                                                                                                                                                                     |

|----------------------------------------------|----|----|----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              |    |    |    |                | SPIM1 (master)                                                                                                                                                                                           |

| GPB[6] /<br>TMS /<br>SPIM1_SO/<br>PWMT2      | 18 | 14 | 10 | 12/16mA<br>I/O | GPB[6] – General purpose input/output<br>digital pin<br>TMS - JTAG ICE Test Mode Select pin<br>(LQFP48 only)<br>SPI2_SO –Serial data output pin for<br>SPIM1 (master)<br>PWMT2 – PWM output for timer 2c |

| GPB[7] /<br>TDI /<br>SPIM1_SCK<br>/<br>PWMT3 | 15 | 12 | 9  | 12/16mA<br>I/O | GPB[7] – General purpose input/output<br>digital pin<br>TDI – JTAG ICE TDO pin (LQFP48 only)<br>SPIM1_SCK –Serial clock output pin for<br>SPIM1 (master)<br>PWMT3 – PWM output for timer 3               |

| GPB[8] /<br>TDO /<br>USB_DET /<br>PWMT0      | 13 | 10 | 8  | 12/16mA<br>I/O | GPB[8] – General purpose input/output<br>digital pin<br>TDO – JTAG ICE TDO interface (LQFP48<br>only)<br>USB_DET– USB detected input<br>PWMT0 – PWM output for timer 0                                   |

| GPB[9] /<br>nTRST /<br>USB_DET /<br>PWMT1    | 10 | 8  | 7  | 4/8mA<br>I/O   | GPB[9] – General purpose input/output<br>digital pin<br>nTRST – JTAG ICE reset pin (LQFP48<br>only)<br>USB_DET– USB detected input<br>PWMT1 – PWM output for timer 1                                     |

| GPC[0] /<br>SPIM1_S0 /<br>USB_DET            | 54 | 42 |    | 4/8mA<br>I/O   | GPC[0] – General purpose input/output<br>digital pin<br>SPIM1_SO –Serial data output pin for<br>SPIM1 (master)<br>USB_DET– USB detected input                                                            |

| GPC[1] /<br>SPIM1_SI /<br>USB_DET            | 55 | 43 |    | 4/8mA<br>I/O   | GPC[1] – General purpose input/output<br>digital pin<br>SPIM1_SI –Serial data input pin for SPIM1<br>(master)<br>USB_DET– USB detected input                                                             |

| GPC[2] /<br>SPIM1_SCK<br>/<br>USB_DET        | 56 | 44 |    | 4/8mA<br>I/O   | GPC[2] – General purpose input/output<br>digital pin<br>SPIM1_SCK –Serial clock output pin for<br>SPIM1 (master)<br>USB_DET– USB detected input                                                          |

| GPC[3] /<br>PWMT0 /<br>USB_DET               | 59 | 47 |    | 4/8mA<br>I/O   | GPC[3] – General purpose input/output<br>digital pin<br>PWMT0 – PWM output for timer 0<br>USB_DET– USB detected input                                                                                    |