# LH75400/01/10/11 User's Guide

# **Content Revisions**

This document contains the following changes to content, causing it to differ from previous versions. Minor typographical changes, where they do not affect content, are not tracked here.

| DATE     | PAGE<br>NO. | SECTION, TABLE,<br>OR ILLUSTRATION | SUMMARY OF CHANGES                                                                                                                                                                                                                        |

|----------|-------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.5         | 1.5.1                              | Pull-up resistor value of 10 K $\Omega$ specified for LINREGEN.                                                                                                                                                                           |

|          | 1-7         | 1.7                                | Text corrected to reflect connectable crystal range, plus frequency yield of PLL.                                                                                                                                                         |

|          | 6-2         | Table 6-1                          | Numbers in Table heads and Notes clarified.                                                                                                                                                                                               |

|          | 6-4         | Table 6-4                          | 'HR-TFT Controller' replaced with 'Advanced LCD Interface'                                                                                                                                                                                |

|          | 7-13+       | Register Bit Fields                | Where Registers contain Read Only and Read/Write bits,<br>Reserved bits now read 'Write the Reset Value' for clarity.                                                                                                                     |

|          | 9-4         | 9.2.2                              | Crystal range connectable to XTALIN and XTALOUT clarified.                                                                                                                                                                                |

|          | 9-7         | Table 9-3                          | Bits 6:5 corrected to R/W, Write the Reset Value.                                                                                                                                                                                         |

|          | 9-9         | Table 9-10                         | Bits 15:0 corrected to 'Do not write any other value to these bits.'                                                                                                                                                                      |

|          | 9-13        | Tables 9-18, 19                    | Bits 8:3 corrected to R/W, Write the Reset Value.                                                                                                                                                                                         |

|          | 9-14        | Tables 9-20, 21                    | Bits 15:2 Reset values corrected.                                                                                                                                                                                                         |

|          | 9-15        | Tables 9-22, 23                    | Bit 1 corrected to R/W, Write the Reset Value.                                                                                                                                                                                            |

| 11-15-03 | 9-18        | Tables 9-30, 31                    | Bits 15:14 corrected to R/W, Write the Reset Value.                                                                                                                                                                                       |

|          | 9-20        | Tables 9-32, 33                    | Bit 7 corrected to W, Write only 0.                                                                                                                                                                                                       |

|          | 9-20        | Table 9-32                         | Register address space corrected.                                                                                                                                                                                                         |

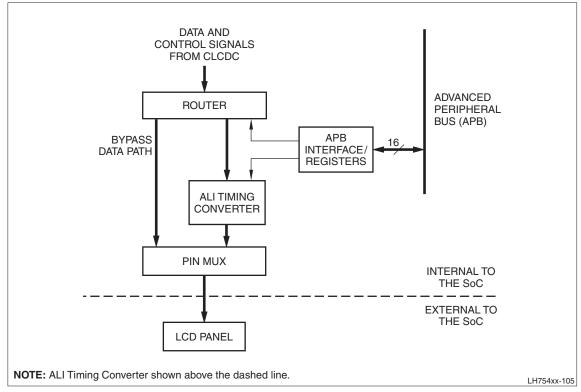

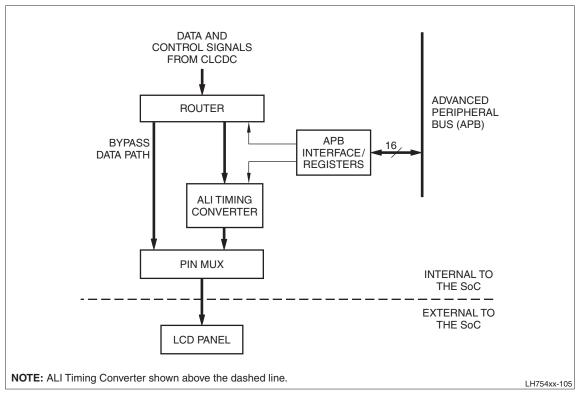

|          |             | Chapter 13                         | Rewritten to clarify operation of Advanced LCD Interface, formerly known as the HR-TFT Controller. Old register names are retained as notes. Register functions and formulae are clarified, but there are no changes to actual operation. |

|          | 13-4        | 13.3                               | Caution statement added regarding enabling LCD before initializing buffer space when REMAP = 1.                                                                                                                                           |

|          | 18-12       | 18.5.2.1                           | SCR bit description clarified.                                                                                                                                                                                                            |

|          | 18-16       | 18.5.2.5                           | CPSR Register clarified.                                                                                                                                                                                                                  |

|          | 19-4        | 19.2.3                             | UART0 and UART1 DMA capabilities clarified.                                                                                                                                                                                               |

|          | 23-13       | 23.3.2.4                           | Bit 5, Interrupt Mask Register is Reserved, R/W, Reset Value 0, Write the Reset Value.                                                                                                                                                    |

|          | 23-26       | 23.3.3                             | Text and formulas clarified.                                                                                                                                                                                                              |

#### **Record of Revisions**

| DATE    | PAGE<br>NO.                 | SECTION, TABLE,<br>OR ILLUSTRATION | SUMMARY OF CHANGES                                                                              |

|---------|-----------------------------|------------------------------------|-------------------------------------------------------------------------------------------------|

|         | _                           | —                                  | Preliminary status removed; Version numbering applied.                                          |

|         | 2-1,<br>3-1,<br>4-1,<br>5-1 | Features                           | Clock frequency and connectable crystals updated.                                               |

|         | 2-10, 3-10,<br>4-10, 5-10   | Tables<br>2-2, 3-2, 4-2, 5-2       | SSPFRM and SSPCLK I/O type corrected, Reset behavior updated.                                   |

|         | 1-7                         | 1.7                                | Text corrected to reflect updated connectable crystal range, plus frequency yield of PLL.       |

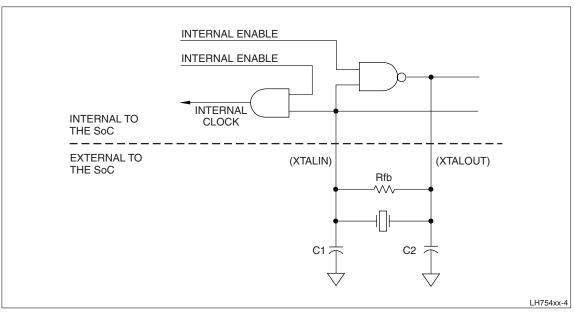

|         | 9-5,<br>9-6                 | 9.2.2, Figure 9-2                  | Text and illustration added clarifying clock sources.                                           |

| 5-14-04 | 12-9                        | Table 12-5                         | Transfer Direction description added.                                                           |

|         | 13-24                       | Table 13-22                        | VCOMPINTRENB description corrected.                                                             |

|         | 14-15                       | Table 14-20                        | LcdPwr description corrected.                                                                   |

|         | 15-8                        | 15.1.4                             | CMP0 bullet corrected to 'Duty Cycle'.                                                          |

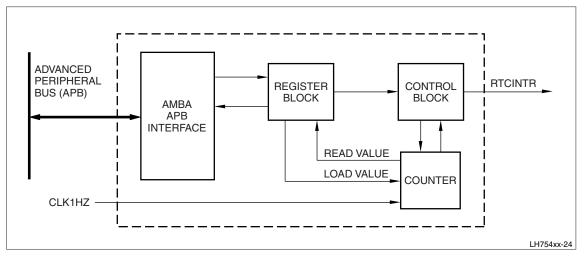

|         | 17-2                        | 17.2                               | Removed incorrect paragraph regarding RTC reset.                                                |

|         | 17-2                        | 17.2.1                             | Section added regarding the optional use of the RTC.                                            |

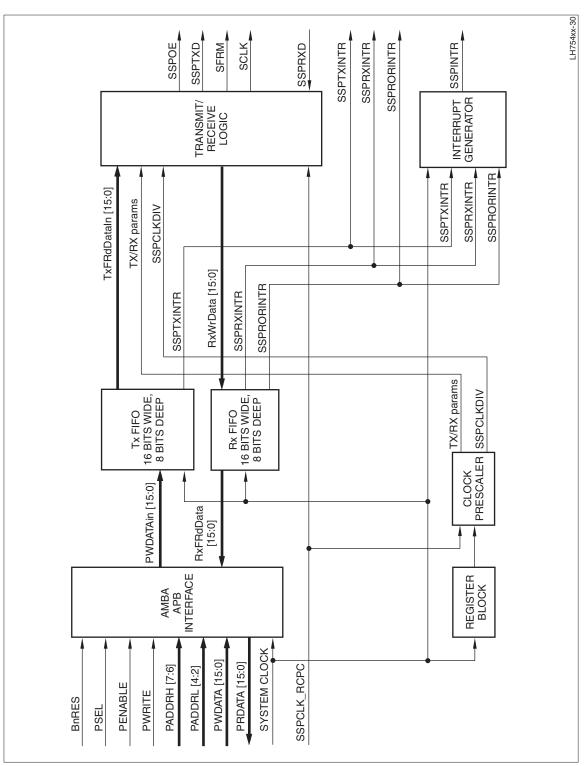

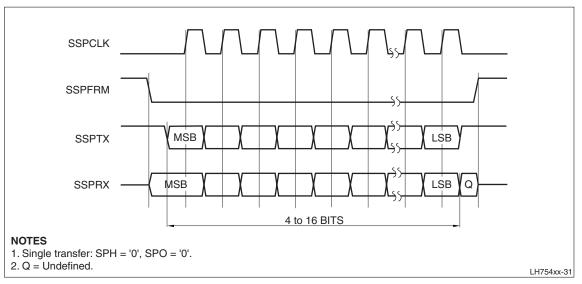

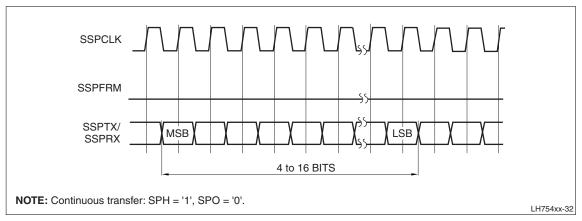

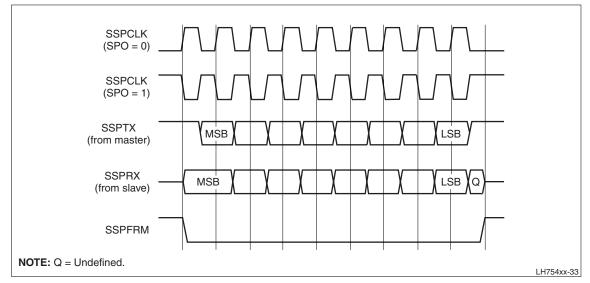

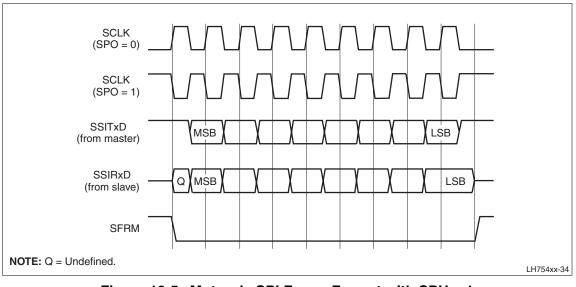

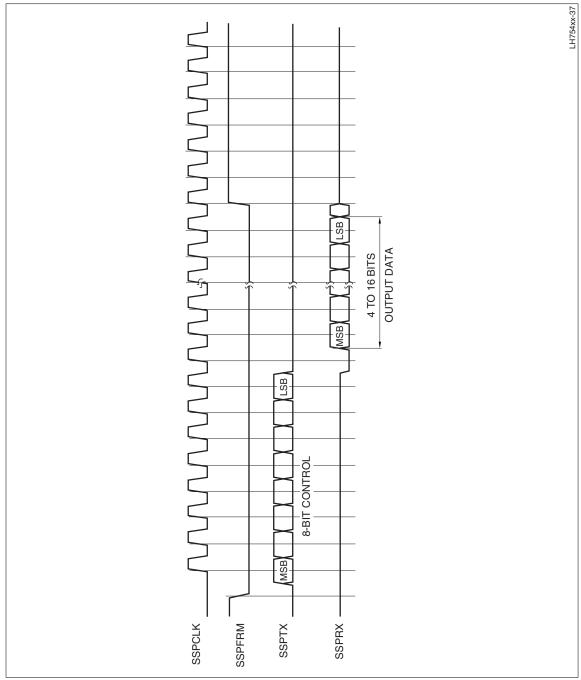

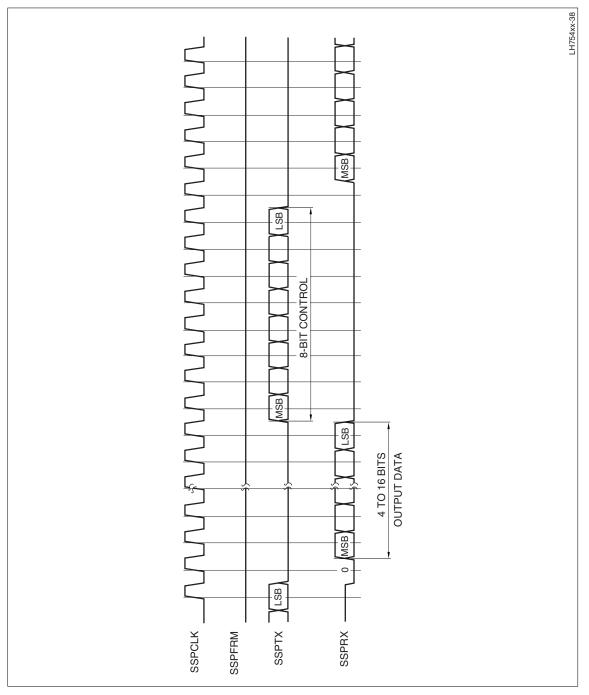

|         | 18-3                        | 18.2                               | Text added clarifying use and state of the SSPFRM pin during TI, SPI, and Microwire operations. |

|         | 18-4                        | Figure 18-2                        | Moved to Data Sheet for ease of maintenance.                                                    |

|         | 23-7                        | 23.1.4.1                           | Description of reference voltages added.                                                        |

|         | 26-13                       | 26.16                              | Type corrected to 'Ports E and F'                                                               |

### Record of Revisions (Cont'd)

| DATE     | PAGE<br>NO.                                                                                                               | SECTION, TABLE,<br>OR ILLUSTRATION  | SUMMARY OF CHANGES                                                                                                                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                                                                                                           | _                                   | Version numbering rolled to 1.1                                                                                                                        |

|          | xxxv                                                                                                                      | Preface                             | Reserved Bits notation clarified.                                                                                                                      |

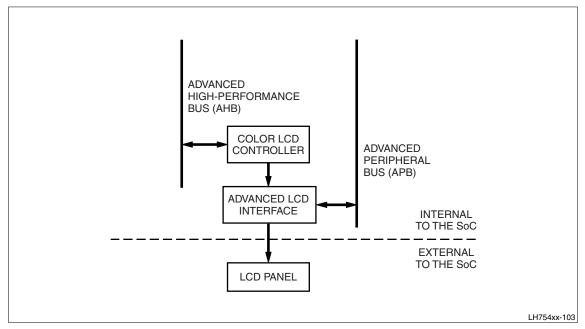

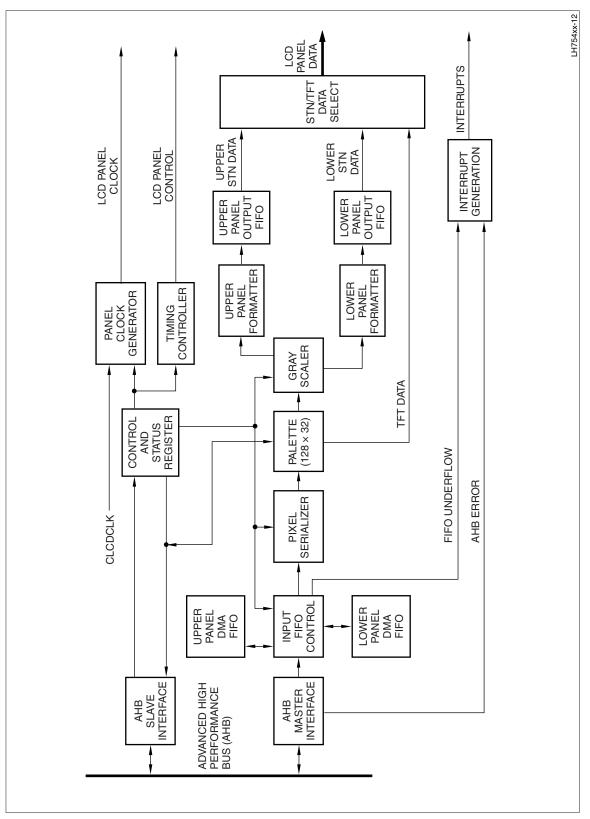

|          | 1-2, 13-31                                                                                                                | 1.2, 13.5                           | Text added to clarify allowable register access widths; whether word only or word, half-word, or byte accesses. Specific case of CLCD and ALI covered. |

|          | 1-3                                                                                                                       | 1.3.1                               | Section added: AHB Master Endian-ness.                                                                                                                 |

|          | 1-4                                                                                                                       | 1.3                                 | Text added to clarify APB access methods and allowable register write access widths.                                                                   |

|          | 1-5                                                                                                                       | 1.5.1                               | Linear Regulator enable must be tied directly to main power.                                                                                           |

|          | 1-9                                                                                                                       | 1.7                                 | Clarified input range of PLL and max operating frequency of MCUs.                                                                                      |

|          | 2-8, 3-8,<br>4-8, 5-8,<br>21-16                                                                                           | Tables 2-1, 3-1, 4-1,<br>5-1, 21-28 | Table Note added to clarify conditional use of GPIO Pin PG[0].                                                                                         |

| 8-20-05  | 7-8, 9-7,<br>10-7, 11-2,<br>12-7,<br>13-33,<br>14-7, 15-9,<br>17-3,<br>18-10,<br>19-5, 20-7,<br>21-3, 22-6,<br>23-8, 26-1 | Programmer's<br>Model (all)         | Text added to clarify allowable register access widths; whether word only or word, half-word, or byte accesses.                                        |

|          | 7-4                                                                                                                       | Table 7-2                           | Added case of Read from one memory bank, then read from a different mem-<br>ory bank.                                                                  |

|          | 10-3                                                                                                                      | 10.1.4                              | Clarified state of interrupts at Reset.                                                                                                                |

|          | 10-10                                                                                                                     | 10-2.2.3                            | Raw Interrupt Status Register function clarified.                                                                                                      |

|          | 13-10                                                                                                                     | 13.3.4                              | Incorrect description involving Intensity bit removed.                                                                                                 |

|          | 13-18                                                                                                                     | Table 13-14                         | Descriptions for VBP, VFP, and VSW updated for STN mode.                                                                                               |

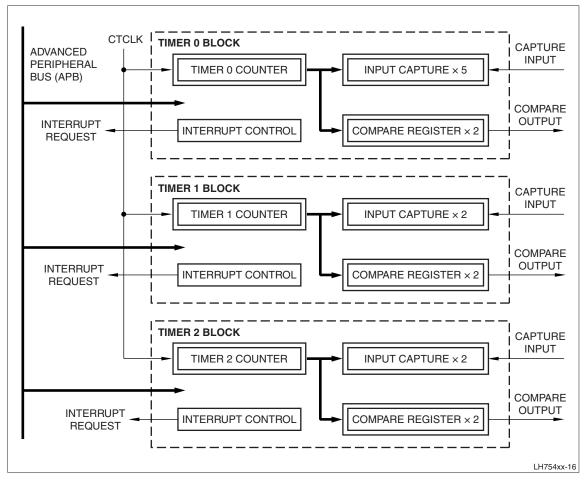

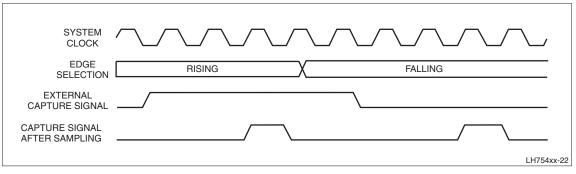

|          | 15-7                                                                                                                      | 15.1.3                              | Clarified Timer Capture feature.                                                                                                                       |

|          | 18-1                                                                                                                      | 18.1                                | Clarified text regarding interrupt-driven transfers.                                                                                                   |

|          | 21-9                                                                                                                      | 21.2.3.6                            | PDDR behavior clarified.                                                                                                                               |

|          | 23-5                                                                                                                      | 23.1.3                              | Updated incorrect cross-reference.                                                                                                                     |

|          | _                                                                                                                         | _                                   | Version numbering rolled to 1.2                                                                                                                        |

| 02.20.00 | 12-4                                                                                                                      | 12.2.2                              | DMA Controller waveforms moved to Data Sheet for simplicity of mainte-<br>nance and to have all interface drawings together in one place.              |

| 03-30-06 | 12-7                                                                                                                      | 12.3.1                              | Corrected high/low text references for Destination Address Registers.                                                                                  |

|          | 13-38                                                                                                                     | 13.6                                | LCD Interface waveforms moved to Data Sheet for simplicity of maintenance and to have all interface drawings together in one place.                    |

### Record of Revisions (Cont'd)

| DATE    | PAGE<br>NO. | SECTION, TABLE,<br>OR ILLUSTRATION | SUMMARY OF CHANGES                                                                                                                   |

|---------|-------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|         | All         | _                                  | Revision number rolled to Version 1.3.                                                                                               |

|         | 1-9         | Section 1.7                        | Corrected maximum frequencies for crystal oscillator (20 MHz) and PLL (140 MHz).                                                     |

|         | 2-1, 2-2    | Section 2.1,<br>Figure 2-1         | Corrected maximum crystal oscillator frequency.                                                                                      |

|         | 3-1, 3-2    | Section 3.1,<br>Figure 3-1         | Corrected maximum crystal oscillator frequency.                                                                                      |

|         | 4-1, 4-2    | Section 4.1,<br>Figure 4-1         | Corrected maximum crystal oscillator frequency.                                                                                      |

| 6-8-07  | 5-1, 5-2    | Section 5.1,<br>Figure 5-1         | Corrected maximum crystal oscillator frequency.                                                                                      |

|         | 9-4         | Section 9.2.2                      | Corrected maximum crystal oscillator frequency.                                                                                      |

|         | 13-24       | Table 13-24                        | Corrected text for Watermarks.                                                                                                       |

|         | 14-15       | Table 14-20                        | Corrected text for Watermarks.                                                                                                       |

|         | 21-2        | Section 21.1                       | Corrected text to read that ALL GPIO Ports are input at reset.                                                                       |

|         | 21-3        | Section 21.2.1                     | Clarified which address space had the reserved space; resorted table below by Port, for clarity. Reserved space more clearly marked. |

|         | 23-16       | Table 23-15                        | Pointer to Application Note added; confusing text on following page deleted.                                                         |

| 8-27-07 | All         | _                                  | All references to Sharp replaced with NXP. Revision number rolled to Version 1.4.                                                    |

### Record of Revisions (Cont'd)

# **Table of Contents**

| Preface  |

|----------|

| 1 101400 |

| Supplemental Documentation | xxxiii |

|----------------------------|--------|

| Terms and Conventions      | xxxiii |

| Multiplexed Pins           | xxxiii |

| Pin Names                  | xxxiv  |

| Peripheral Devices         | xxxiv  |

| Register Names             | xxxiv  |

| Register Addresses         | xxxiv  |

| Reserved Addresses         | xxxiv  |

| Reserved Bits              | xxxiv  |

| Register Tables            | xxxv   |

|                            |        |

## Chapter 1 – Introduction

| 1.2 ARM and Thumb State1-21.3 Bus Architecture1-21.3.1 AHB Master Endian-ness1-31.4 Operating Modes1-31.4 Operating Mode1-41.4.1 Normal Mode1-41.4.2 PLL Bypass Mode1-51.4.3 Embedded ICE Mode1-51.5 Power Supplies1-51.5.1 Linear Regulator Power1-51.5.2 PLL Power1-61.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage1-61.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-91.8 Reset Strategy1-10 | 1.1 Product Overview         |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----|

| 1.3.1 AHB Master Endian-ness1-31.4 Operating Modes1-41.4.1 Normal Mode1-41.4.2 PLL Bypass Mode1-51.4.3 Embedded ICE Mode1-51.5 Power Supplies1-51.5 Power Supplies1-51.5.1 Linear Regulator Power1-51.5.2 PLL Power1-61.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage1-61.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-9                                                                        | 1.2 ARM and Thumb State      | 1-2 |

| 1.4 Operating Modes1-41.4.1 Normal Mode1-41.4.2 PLL Bypass Mode1-51.4.3 Embedded ICE Mode1-51.5 Power Supplies1-51.5 Power Supplies1-51.5.1 Linear Regulator Power1-51.5.2 PLL Power1-61.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage1-61.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-9                                                                                                       | 1.3 Bus Architecture         |     |

| 1.4 Operating Modes1-41.4.1 Normal Mode1-41.4.2 PLL Bypass Mode1-51.4.3 Embedded ICE Mode1-51.5 Power Supplies1-51.5 Power Supplies1-51.5.1 Linear Regulator Power1-51.5.2 PLL Power1-61.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage1-61.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-9                                                                                                       | 1.3.1 AHB Master Endian-ness |     |

| 1.4.1 Normal Mode1-41.4.2 PLL Bypass Mode1-51.4.3 Embedded ICE Mode1-51.5 Power Supplies1-51.5 Power Supplies1-51.5.1 Linear Regulator Power1-51.5.2 PLL Power1-61.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage1-61.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-9                                                                                                                             | 1.4 Operating Modes          | 1-4 |

| 1.4.3 Embedded ICE Mode1-51.5 Power Supplies1-51.5.1 Linear Regulator Power1-51.5.2 PLL Power1-61.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage1-61.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-9                                                                                                                                                                                              |                              |     |

| 1.4.3 Embedded ICE Mode1-51.5 Power Supplies1-51.5.1 Linear Regulator Power1-51.5.2 PLL Power1-61.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage1-61.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-9                                                                                                                                                                                              | 1.4.2 PLL Bypass Mode        |     |

| 1.5 Power Supplies       1-5         1.5.1 Linear Regulator Power       1-5         1.5.2 PLL Power       1-6         1.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage       1-6         1.5.3 Real-World Component Selection       1-7         1.6 Crystal Oscillator Usage       1-8         1.7 Clocking Strategy       1-9                                                                                                                 | 1.4.3 Embedded ICE Mode      |     |

| 1.5.1 Linear Regulator Power.       1-5         1.5.2 PLL Power.       1-6         1.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage.       1-6         1.5.3 Real-World Component Selection       1-7         1.6 Crystal Oscillator Usage.       1-8         1.7 Clocking Strategy       1-9                                                                                                                                                  |                              |     |

| 1.5.2 PLL Power       1-6         1.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage       1-6         1.5.3 Real-World Component Selection       1-7         1.6 Crystal Oscillator Usage       1-8         1.7 Clocking Strategy       1-9                                                                                                                                                                                                     | 1.5.1 Linear Regulator Power |     |

| 1.5.2.1 PCB Mounted Analog Power Supply Filter for PLL Usage       1-6         1.5.3 Real-World Component Selection       1-7         1.6 Crystal Oscillator Usage       1-8         1.7 Clocking Strategy       1-9                                                                                                                                                                                                                                       | 1.5.2 PLL Power              |     |

| 1.5.3 Real-World Component Selection1-71.6 Crystal Oscillator Usage1-81.7 Clocking Strategy1-9                                                                                                                                                                                                                                                                                                                                                             |                              |     |

| 1.6 Crystal Oscillator Usage       1-8         1.7 Clocking Strategy       1-9                                                                                                                                                                                                                                                                                                                                                                             | •                            | -   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                              |     |

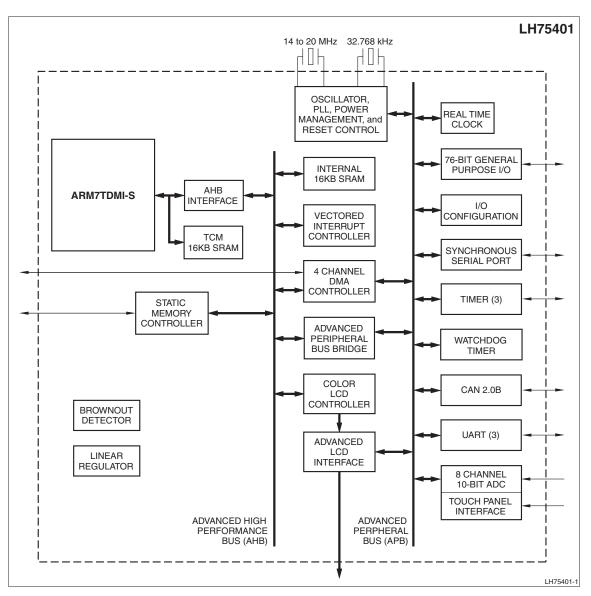

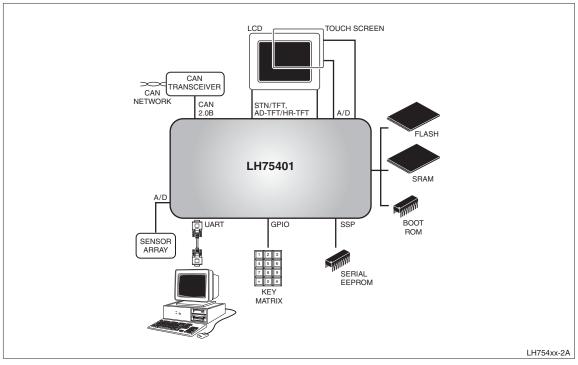

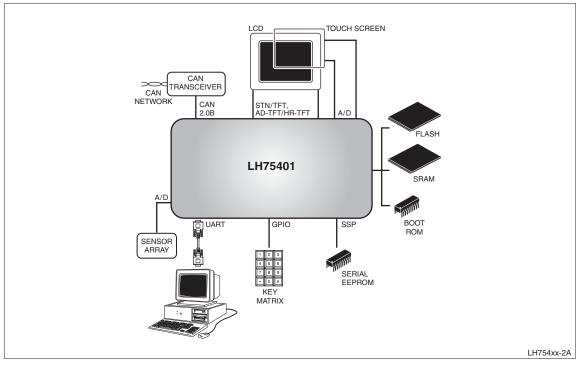

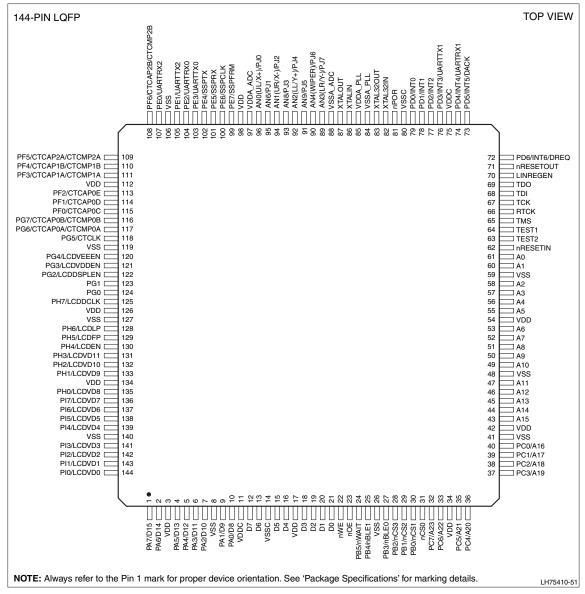

#### Chapter 2 – LH75401 MCU

| 2.1 LH75401 Features              | 2-1 |

|-----------------------------------|-----|

| 2.2 LH75401 Block Diagram         | 2-2 |

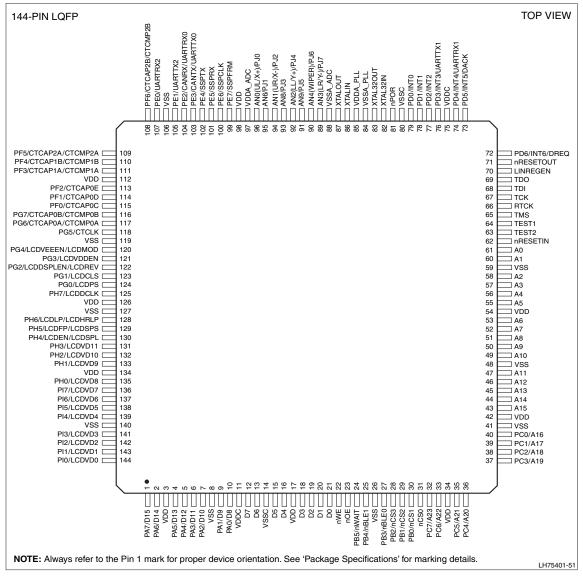

| 2.3 LH75401 Applications          | 2-3 |

| 2.4 LH75401 Pin Diagram           | 2-4 |

| 2.5 LH75401 Numerical Pin Listing | 2-5 |

| 2.6 LH75401 Signal Descriptions   | 2-9 |

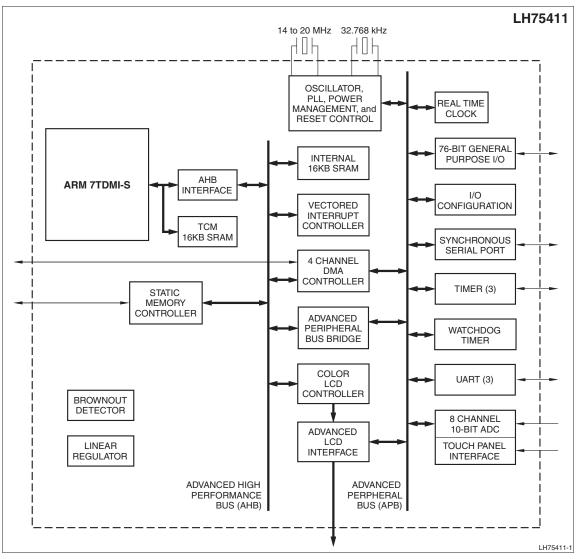

### Chapter 3 – LH75411 MCU

| 3.1 LH75411 Features              | 3-1 |

|-----------------------------------|-----|

| 3.2 LH75411 Block Diagram         |     |

| 3.3 LH75411 Applications          | 3-3 |

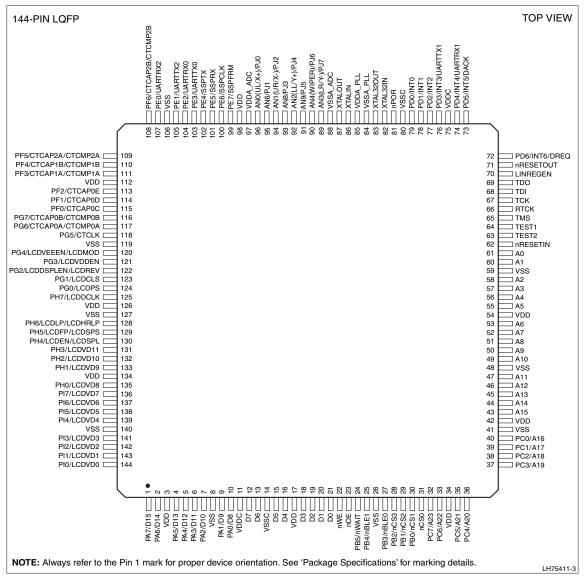

| 3.4 LH75411 Pin Diagram           |     |

| 3.5 LH75411 Numerical Pin Listing | 3-5 |

| 3.6 LH75411 Signal Descriptions   |     |

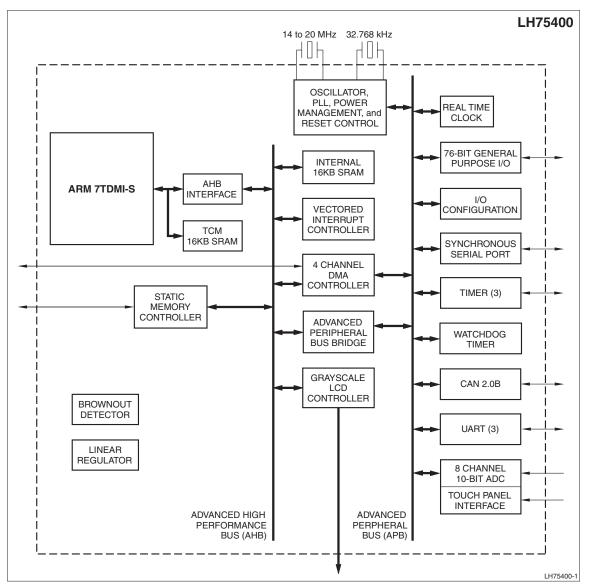

#### Chapter 4 – LH75400 MCU

| 4.1 LH75400 Features              |  |

|-----------------------------------|--|

| 4.2 LH75400 Block Diagram         |  |

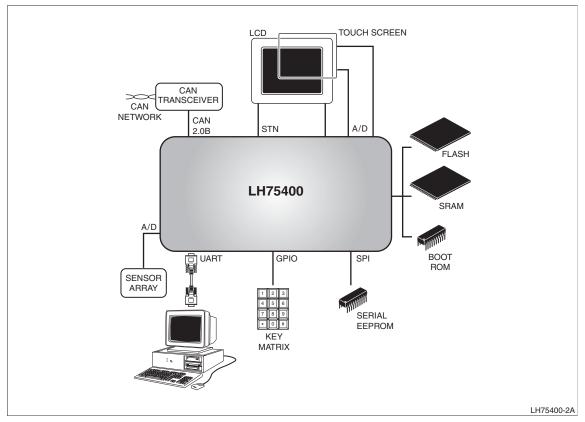

| 4.3 LH75400 Applications          |  |

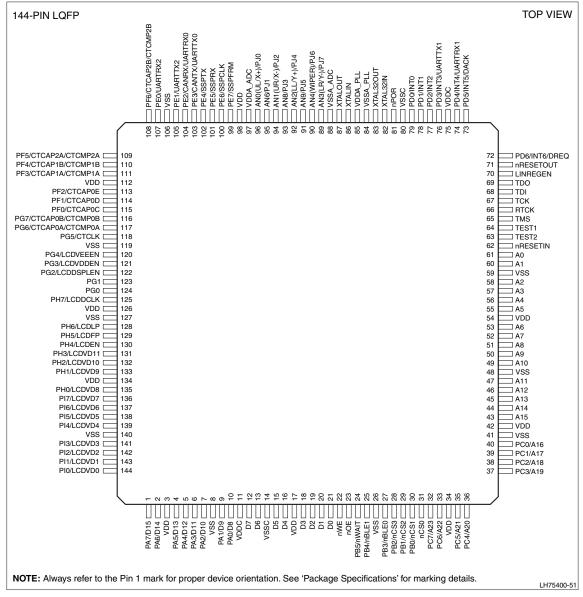

| 4.4 LH75400 Pin Diagram           |  |

| 4.5 LH75400 Numerical Pin Listing |  |

| 4.6 LH75400 Signal Descriptions   |  |

### Chapter 5 – LH75410 MCU

| 5.1 LH75410 Features              | 5-1 |

|-----------------------------------|-----|

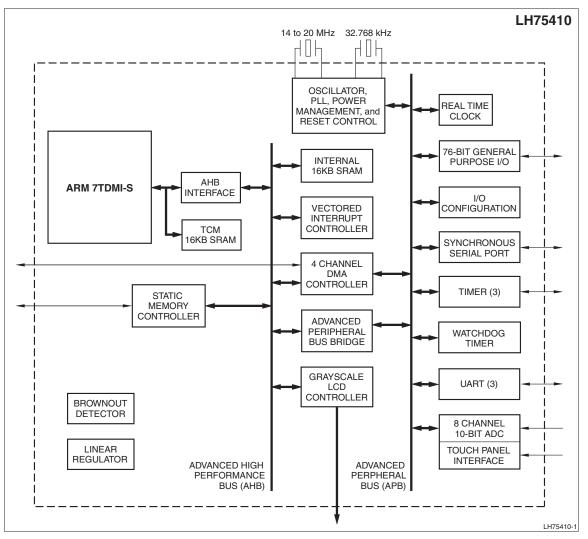

| 5.2 LH75410 Block Diagram         | 5-2 |

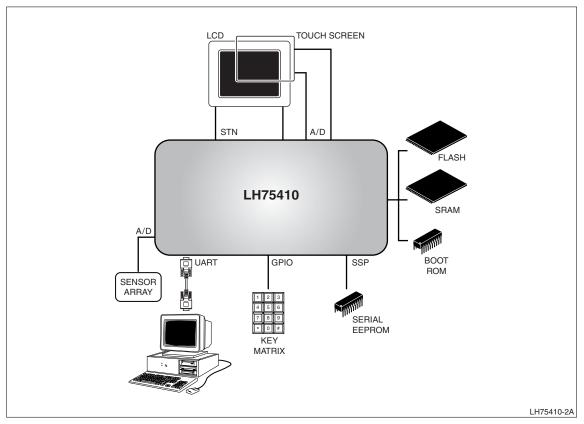

| 5.3 LH75410 Applications          |     |

| 5.4 LH75410 Pin Diagram           |     |

| 5.5 LH75410 Numerical Pin Listing | 5-5 |

| 5.6 LH75410 Signal Descriptions   |     |

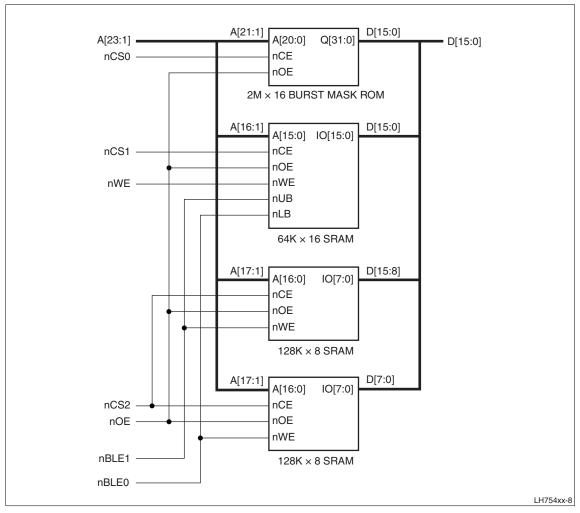

### **Chapter 6 – Memory Interface Architecture**

#### **Chapter 7 – Static Memory Controller**

| 7.1 SMC Features                                 | 7-1  |

|--------------------------------------------------|------|

| 7.2 SMC Theory of Operation                      | 7-2  |

| 7.2.1 SMC Write Process                          | 7-2  |

| 7.2.2 SMC Read Process                           | 7-3  |

| 7.2.3 SMC Burst Mode Read Process                | 7-3  |

| 7.2.4 External Memory Bus Cycle                  | 7-4  |

| 7.2.5 External Bus Read/Write Operations         | 7-5  |

| 7.2.6 SMC Memory Connection Diagram              | 7-7  |

| 7.3 SMC Programmer's Model                       | 7-8  |

| 7.3.1 SMC Register Summary                       |      |

| 7.3.2 SMC Register Definitions                   | 7-9  |

| 7.3.2.1 Configuration Register for Memory Bank 0 | 7-9  |

| 7.3.2.2 Configuration Register for Memory Bank 1 | 7-11 |

| 7.3.2.3 Configuration Register for Memory Bank 2 | 7-13 |

| 7.3.2.4 Configuration Register for Memory Bank 3 | 7-15 |

| 7.3.3 SMC Default Memory Widths                  | 7-17 |

|                                                  |      |

### **Chapter 8 – Static Random Access Memory Controller**

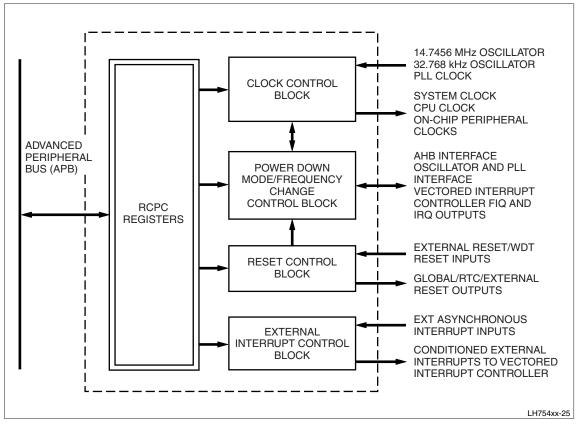

## Chapter 9 – Reset, Clock, and Power Controller

| 9.1 RCPC Features            | . 9-2 |

|------------------------------|-------|

| 9.2 RCPC Theory of Operation | . 9-2 |

| 9.2.1 Reset Generation       | . 9-3 |

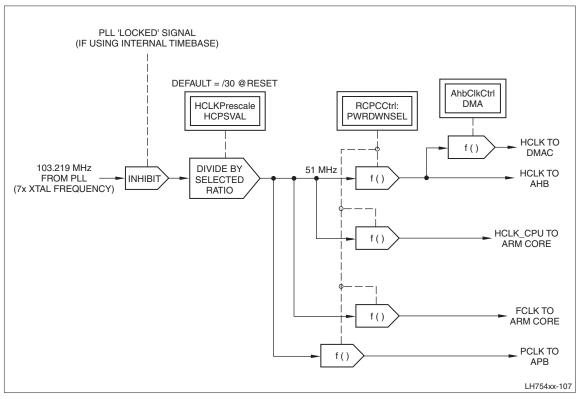

| 9.2.2 Clock Generation       | . 9-4 |

| 9.2.3 RCPC Power Modes       | . 9-5 |

| 9.2.3.1 Active Mode          | . 9-6 |

| 9.2.3.2 Standby Mode         | . 9-6 |

| 9.2.3.3 Sleep Mode           | . 9-6 |

| 9.2.3.4 Stop1 Mode           | . 9-6 |

| 9.2.3.5 Stop2 Mode           | . 9-6 |

| 9.3 RCPC Programmer's Model  | . 9-7 |

|                              |       |

| 9.3.1 RCPC Register Summary                        | 9-7   |

|----------------------------------------------------|-------|

| 9.3.2 RCPC Register Definitions                    | 9-8   |

| 9.3.2.1 Control Register                           | 9-8   |

| 9.3.2.2 Identification Register                    | 9-9   |

| 9.3.2.3 Remap Control Register                     | 9-9   |

| 9.3.2.4 Soft Reset Register                        |       |

| 9.3.2.5 Reset Status Register                      |       |

| 9.3.2.6 Reset Status Clear Register                |       |

| 9.3.2.7 HCLK Prescaler Register                    |       |

| 9.3.2.8 Peripheral Clock Control Register 0        |       |

| 9.3.2.9 Peripheral Clock Control Register 1        |       |

| 9.3.2.10 AHB Clock Control Register                |       |

| 9.3.2.11 LCD Clock Prescaler Register              |       |

| 9.3.2.12 SSP Clock Prescaler Register              |       |

| 9.3.2.13 External Interrupt Configuration Register |       |

| 9.3.2.14 External Interrupt Clear Register         | 9-21  |

| Chapter 10 – Vectored Interrupt Controller         |       |

| 10.1 Theory of Operation                           | 10-1  |

| 10.1.1 Interrupts                                  | 10-1  |

| 10.1.2 VIC Interrupt Listing                       | 10-2  |

| 10.1.3 Vectored Interrupts                         | 10-3  |

| 10.1.4 External Interrupts                         | 10-3  |

| 10.1.5 Clearing Interrupts                         | 10-4  |

| 10.1.6 Priority                                    | 10-4  |

| 10.1.7 Sequencing                                  | 10-5  |

| 10.1.8 External Level-Sensitive Interrupts         |       |

| 10.1.9 Software Guidelines                         | 10-7  |

| 10.2 VIC Programmer's Model                        | 10-7  |

| 10.2.1 VIC Register Summary                        | 10-8  |

| 10.2.2 VIC Register Definitions                    |       |

| 10.2.2.1 IRQ Status Register                       |       |

| 10.2.2.2 FIQ Status Register                       |       |

| 10.2.2.3 Raw Interrupt Status Register             |       |

| 10.2.2.4 Interrupt Select Register                 |       |

| 10.2.2.5 Interrupt Enable Register                 |       |

| 10.2.2.6 Interrupt Enable Clear Register           |       |

| 10.2.2.7 Software Interrupt Register               |       |

| 10.2.2.8 Software Interrupt Clear Register         |       |

| 10.2.2.9 Vector Address Register                   |       |

| 10.2.2.10 Default Vector Address Register          |       |

| 10.2.2.11 Vector Address Registers                 |       |

| 10.2.2.12 Vector Control Registers                 | 10-17 |

| 11.1 IOCON Theory of Operation       11-1         11.2 IOCON Programmer's Model       11-2         11.2.1 IOCON Register Summary.       11-2         11.2.1 IOCON Register Summary.       11-3         11.2.2 IDCON Register Summary.       11-3         11.2.2 IDCON Register Definitions       11-3         11.2.2.1 EBI Interface Muxing Register       11-6         11.2.2.3 Pins PD6/INT6 to PD0/INT0 Muxing Register       11-6         11.2.2.4 Timer Muxing Register       11-6         11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/nWAIT to PB0/ICS1 Resistor Muxing Register       11-14         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-16         11.2.2.11 Pins AN7/P.J7 to AN0/P.0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.3 1 DMA Controller Register Summary       12-5         12.3.1 DMA Controller Register Definitions       12-6         12.3.2.2 DMA Controller Register       12-6         12.3.2.3 Maximum Count Register       <                                                                                        | Chapter 11 – I/O Configuration                               |                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|

| 11.2 IOCON Programmer's Model       11-2         11.2.1 IOCON Register Summary       11-2         11.2.2 IOCON Register Definitions       11-3         11.2.2.1 EBI Interface Muxing Register       11-3         11.2.2.2 Pins PD6/INT6 to PD0/INT0 Muxing Register       11-6         11.2.2.3 Pins PE7/SSPRM to PD0/INT0 Muxing Register       11-6         11.2.2.4 Timer Muxing Register       11-10         11.2.2.5 LOD Mode Muxing Register       11-10         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/INWAIT to PB0/INT0 Resistor Muxing Register       11-11         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-16         11.2.2.11 Pins AN7/PJ7 to AN0/PJ0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-2         12.1 DMA Controller Register Summary       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Summary       12-6         12.3.2.3 DMA Controller Register       12-6         12.3.2.3 Low combaler Register       12-6                                                                                 |                                                              |                                    |

| 11.2.2 IOCON Register Definitions       11-3         11.2.2.1 EBI Interface Muxing Register       11-3         11.2.2.2 Pins PD6/INT6 to PD0/INT0 Muxing Register       11-5         11.2.2.3 Pins PE7/SSPRM to PD0/INT0 Muxing Register       11-6         11.2.2.4 Timer Muxing Register       11-6         11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/MWAIT to PB0/INT0 Resistor Muxing Register       11-11         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register       12-6         12.3.2 DMA Controller Register       12-6         12.3.2 DMA Controller Register       12-6         12.3.2 DX Cource Base Registers       12-6         12.3.2 DX Cource Register       12-6         12                                                                                   |                                                              |                                    |

| 11.2.2.1 EBI Interface Muxing Register       11-3         11.2.2.2 Pins PD6/INT6 to PD0/INT0 Muxing Register       11-5         11.2.2.3 Pins PE7/SSPRM to PD0/INT0 Muxing Register       11-6         11.2.2.4 Timer Muxing Register       11-6         11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.5 LCD Mode Muxing Register       11-11         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/WAIT to PB0/ICS1 Resistor Muxing Register       11-14         11.2.2.9 Pins PD7/A23 to PC0/A16 Resistor Muxing Register       11-16         11.2.2.9 Pins PD7/INT6 to PD0/INTO Resistor Muxing Register       11-16         11.2.2.9 Pins PD7/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.9 Pins PD7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.3 DMA Controller Register Summary       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register </td <td>11.2.1 IOCON Register Summary 11-2</td> | 11.2.1 IOCON Register Summary 11-2                           |                                    |

| 11.2.2.2 Pins PD6/INT6 to PD0/INT0 Muxing Register       11-5         11.2.2.3 Pins PE7/SSPRM to PD0/INT0 Muxing Register       11-6         11.2.2.4 Timer Muxing Register       11-10         11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.5 LCD Mode Muxing Register       11-11         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/nWAIT to PB0/nCS1 Resistor Muxing Register       11-13         11.2.2.9 Pins PC7/A23 to PC0/A16 Resistor Muxing Register       11-16         11.2.2.10 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PT5/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-16         11.2.2.11 Pins AN7/PJ7 to AN0/PJ0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Definitions       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Court Register       12-6         12.3.2.4 Control Register       12-9         12.3.2.5 Current Destination Register       12-9         12.3.2.6 Lurrent Destination Register       12-9                                                                          | 11.2.2 IOCON Register Definitions11-3                        |                                    |

| 11.2.2.3 Pins PE7/SSPRM to PD0/INT0 Muxing Register       11-6         11.2.2.4 Timer Muxing Register       11-8         11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/NWAIT to PB0/nCS1 Resistor Muxing Register       11-13         11.2.2.8 Pins PC7/A23 to PC0/A16 Resistor Muxing Register       11-14         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register 11-18       11.2.2.11 Pins AN7/PJ7 to AN0/PJ0         11.2.2.11 Pins AN7/PJ7 to AN0/PJ0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Definitions       12-6         12.3.2.2 Destination Base Registers       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-9         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.6 Current Destination Register       12-9                                                                | 11.2.2.1 EBI Interface Muxing Register11-3                   |                                    |

| 11.2.2.4 Timer Muxing Register       11-8         11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/nWAIT to PB0/nCS1 Resistor Muxing Register       11-14         11.2.2.8 Pins PC7/A23 to PC0/A16 Resistor Muxing Register       11-14         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PAT/D3 to AN0/PJ0       11-20         Chapter 12 - Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.1 Source Base Register       12-6         12.3.2.3 Maximum Count Register       12-9         12.3.2.4 Control Register       12-9         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.6 Current Destination Register       12-9 </td <td>11.2.2.2 Pins PD6/INT6 to PD0/INT0 Muxing Register</td>                                       | 11.2.2.2 Pins PD6/INT6 to PD0/INT0 Muxing Register           |                                    |

| 11.2.2.5 LCD Mode Muxing Register       11-10         11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register       11-11         11.2.2.7 Pins PB5/nWAIT to PB0/nCS1 Resistor Muxing Register       11-13         11.2.2.8 Pins PC7/A23 to PC0/A16 Resistor Muxing Register       11-14         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-16         11.2.2.11 Pins AN7/PJ7 to AN0/PJ0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-5         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Summary       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.7 Terminal Count Register       12-11         12.3.2.1 Status Register       12-12          12.3.2.8                                                                                                               | 11.2.2.3 Pins PE7/SSPRM to PD0/INT0 Muxing Register          |                                    |

| 11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register.       11-11         11.2.2.7 Pins PB5/nWAIT to PB0/nCS1 Resistor Muxing Register.       11-13         11.2.2.8 Pins PC7/A23 to PC0/A16 Resistor Muxing Register.       11-14         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register       11-18         11.2.2.11 Pins AN7/PJ7 to AN0/PJ0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features.       12-1         12.2 DMA Theory Of Operation.       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Controller Register Summary       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Summary       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-7         12.3.2.4 Control Register       12-9         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.1 Status Register       12-12 <td colspate="" register<="" td="" td<=""><td>11.2.2.4 Timer Muxing Register11-8</td></td>                      | <td>11.2.2.4 Timer Muxing Register11-8</td>                  | 11.2.2.4 Timer Muxing Register11-8 |

| 11.2.2.7 Pins PB5/nWAIT to PB0/nCS1 Resistor Muxing Register.       11-13         11.2.2.8 Pins PC7/A23 to PC0/A16 Resistor Muxing Register.       11-14         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register 11-18       11-20 <b>Chapter 12 – Direct Memory Access Controller</b> 11-20         12.1 DMA Controller Features.       12-1         12.2 DMA Theory Of Operation.       12-2         12.2.1 Interrupt, Error, and Status Registers.       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-6         12.3.2 DMA Controller Register Definitions.       12-6         12.3.2 DMA Controller Register       12-6         12.3.2 DMA Controller Register       12-6         12.3.2 DMA Controller Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register.       12-6         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.7 Terminal Count Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.1 Status Register       12-12         Chapter 13 - Color Liquid Cr                                                                                                     | 11.2.2.5 LCD Mode Muxing Register11-10                       |                                    |

| 11.2.2.8 Pins PC7/A23 to PC0/A16 Resistor Muxing Register       11-14         11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SPRM to PE0/UARTRX2 Resistor Muxing Register 11-18       11-20         Chapter 12 - Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.3 Maximum Count Register       12-7         12.3.2.4 Control Register       12-9         12.3.2.5 Current Source Registers       12-9         12.3.2.8 Interrupt Mask Register       12-9         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 - Color Liquid Crystal Display Controller         13.1 Introduction       13-5 <td>11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register</td>                                          | 11.2.2.6 Pins PA7/D15 to PA0/D8 Resistor Muxing Register     |                                    |

| 11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register       11-16         11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register 11-18       11.2.2.11 Pins AN7/PJ7 to AN0/PJ0         11.2.2.11 Pins AN7/PJ7 to AN0/PJ0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-9         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.1 DY Panel Architecture       13-3         13.1 Introduction       13-2         13.1 Introduction       13-2         13.3 LCD D Features       13-4         13.3 How Pixels are Stored in Me                                                                                                                      | 11.2.2.7 Pins PB5/nWAIT to PB0/nCS1 Resistor Muxing Register |                                    |

| 11.2.2.10 Pins PE7/SSPRM to PE0/UARTRX2 Resistor Muxing Register 11-18         11.2.2.11 Pins AN7/PJ7 to AN0/PJ0         11.20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-6         12.3.2.5 Current Source Registers       12-6         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.9 Interrupt Clear Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.2 CLCDC Features       13-3         13.3 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                               | 11.2.2.8 Pins PC7/A23 to PC0/A16 Resistor Muxing Register    |                                    |

| 11.2.2.11 Pins AN7/PJ7 to AN0/PJ0       11-20         Chapter 12 – Direct Memory Access Controller         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.3 DMA Controller Register Definitions       12-6         12.3.2.4 Control Register       12-6         12.3.2.5 Current Source Registers       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.9 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       13-3         13.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.2 Pixel Serializer       13-7         13.3.3 How Pixels are Stored in                                                                                                                                                          | 11.2.2.9 Pins PD6/INT6 to PD0/INT0 Resistor Muxing Register  |                                    |

| Chapter 12 – Direct Memory Access Controller       12.1         12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-6         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.9 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller       13-3         13.1 Introduction       13-2         13.3.1 LCD Panel Architecture       13-3         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memory       13-8 <td></td>                                                                                                                                           |                                                              |                                    |

| 12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-9         12.3.2.9 Interrupt Clear Register       12-10         12.3.2.9 Interrupt Clear Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller       13-3         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 LCD DMA FIFOs       13-7         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are                                                                                                                                                       | 11.2.2.11 Pins AN7/PJ7 to AN0/PJ011-20                       |                                    |

| 12.1 DMA Controller Features       12-1         12.2 DMA Theory Of Operation       12-2         12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 LCD DMA FIFOs       13-7         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memor                                                                                                                                                         | Chapter 12 – Direct Memory Access Controller                 |                                    |

| 12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Registers       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-6         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                 | •                                                            |                                    |

| 12.2.1 Interrupt, Error, and Status Registers       12-4         12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Registers       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-6         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Register       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                 | 12.2 DMA Theory Of Operation12-2                             |                                    |

| 12.3 DMA Programmer's Model       12-5         12.3.1 DMA Controller Register Summary       12-5         12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-9         12.3.2.9 Interrupt Clear Register       12-10         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                 |                                                              |                                    |

| 12.3.2 DMA Controller Register Definitions       12-6         12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-10         12.3.2.9 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller       13-2         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.2 Pixel Serializer       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · ·                                                        |                                    |

| 12.3.2.1 Source Base Registers       12-6         12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 - Color Liquid Crystal Display Controller       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.2 Pixel Serializer       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12.3.1 DMA Controller Register Summary                       |                                    |

| 12.3.2.2 Destination Base Register       12-6         12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 - Color Liquid Crystal Display Controller       13-3         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.2 Pixel Serializer       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 12.3.2 DMA Controller Register Definitions                   |                                    |

| 12.3.2.3 Maximum Count Register       12-6         12.3.2.4 Control Register       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 - Color Liquid Crystal Display Controller       13-2         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.2 Pixel Serializer       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.3.2.1 Source Base Registers                               |                                    |

| 12.3.2.4 Control Register.       12-7         12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-9         12.3.2.9 Interrupt Clear Register       12-10         12.3.2.10 Status Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.2 Pixel Serializer       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12.3.2.2 Destination Base Register                           |                                    |

| 12.3.2.5 Current Source Registers       12-9         12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12.3.2.3 Maximum Count Register 12-6                         |                                    |

| 12.3.2.6 Current Destination Registers       12-9         12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.3.1 LCD DMA FIFOs       13-7         13.3.3 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 12.3.2.4 Control Register                                    |                                    |

| 12.3.2.7 Terminal Count Register       12-9         12.3.2.8 Interrupt Mask Register       12-10         12.3.2.9 Interrupt Clear Register       12-11         12.3.2.10 Status Register       12-12         Chapter 13 – Color Liquid Crystal Display Controller         13.1 Introduction       13-2         13.1.1 LCD Panel Architecture       13-3         13.2 CLCDC Features       13-4         13.3 CLCDC Theory of Operation       13-5         13.1.1 LCD DMA FIFOs       13-7         13.3.1 How Pixels are Stored in Memory       13-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12.3.2.5 Current Source Registers                            |                                    |