#### **LPC29xx- Base Module**

# Agenda

- Introduction

- Memory support

- Subsystems

- PCR (Power Clock & Reset)

- General (GeSS)

- Networking (IVNSS)

- Peripheral (PeSS)

- Modulation and Sampling (MSCSS)

- Power modes

- DMA support

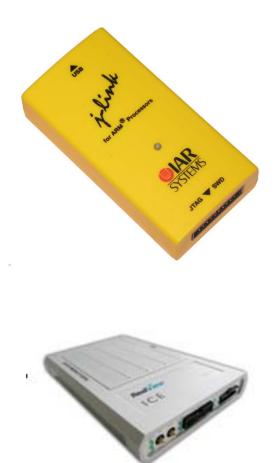

- Tools

#### Introduction

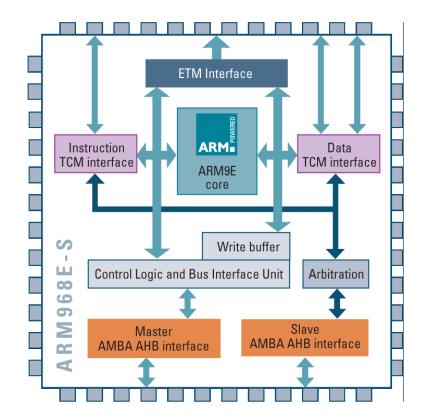

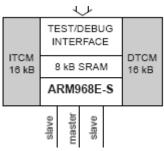

ARM968E-S Overview

LPC29xx Derivatives

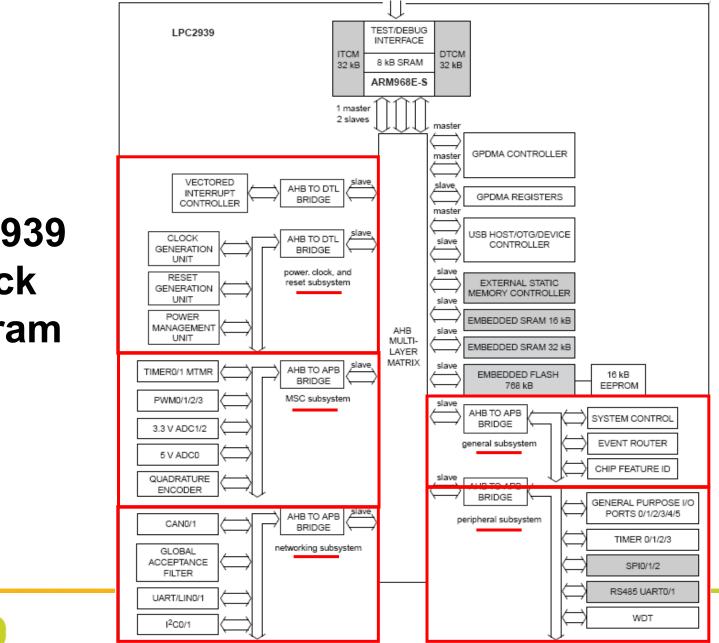

LPC29xx Block Diagram

#### The ARM9E Processor Family ARM968E-S (& ARM926EJ-S)

- ARMv5TE instruction set – DSP instructions

- Tightly Coupled Memories

Next slide

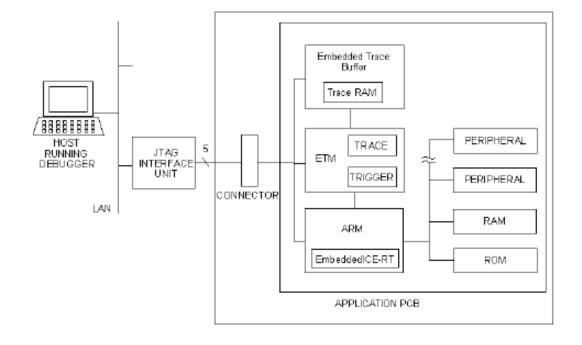

- ETM9 interface

# Tightly coupled memory (TCM)

- TCM is a low-latency memory that provides predictable performance

- TCM accesses are deterministic and do not access the AHB

- Cache on the other hand is not predictable

- Due to its deterministic behavior, TCM can hold critical routines, such as interrupt handling routines or real-time tasks where the indeterminacy of a cache is highly undesirable

- Can easily be controlled by a small footprint embedded OS

- Cache requires a MUCH larger OS to manage it efficiently

## **Configuring TCM's using Keil Tools**

| - sheed - haisions - fer uixh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | การขางขางและ แรงรายการวรรายราย ขางมีร่วงรายรายการและ และ และ และ และ และ และ และ และ และ                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 🖹 File Edit Yiew Project Debug                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ; Fl <u>a</u> sh Pe <u>ri</u> pherals <u>T</u> ools <u>S</u> VCS <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                      |

| 12 😂 🖬 🗊 🕺 🖻 🛍                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 으으   準 律 🔏 % % % 🙀 💷 🔍 🖊 🔶 🔶                                                                                                                                                                                                                                                                                                                      |

| 🔹 🎬 🛎 🛸 🕌 🗱 🔊                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | LPC29xx_Debug 💽 🛃 🐂                                                                                                                                                                                                                                                                                                                               |

| Project Workspace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | - × 175                                                                                                                                                                                                                                                                                                                                           |

| CPC29xx_Debug  CPC29x_Debug         | 176 /*Out clock from CGU1 is 400KH2<br>177 ICLK0_CLK_CONF = AUTOBLK; //400<br>178 OUT_CLK_CONF = CLK_SEL_ICLK0  <br>179<br>180 /* Add your codes here */<br>181 GPIOResetInit();<br>182                                                                                                                                                           |

| target.c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Options for File 'adc.c'                                                                                                                                                                                                                                                                                                                          |

| <pre>timer.c uart.c swi_handler.s sram_test.r adc.c adc.c addc.c addc.c</pre> | Properties       C/C++         Path:       C:\nxpmcu\software\csps\lpc292x\bsps\mcb29xx\examples\keil_examples         File Type:       C Source file         Size:       3315 Bytes         Iast change:       Fri Sep 19 11:39:35 2008         Stop on Exit Code:       Not specified         Custom Arguments:       Image: Stop on Exit Code: |

| Files Regs Dooks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Memory Assignment:<br>Code / Const: RAM1 [0x0-0x7FFF]<br>Zero Initialized Data: RAM2 [0x40000-0x87FFF]<br>Other Data: IRAM1 [0x80004000-0x8000BFFF]                                                                                                                                                                                               |

## LPC29xx Family- An Introduction

- Industry's fastest running ARM968 running at 125MHz

- Memory support

- On-chip SRAM and Flash, EEPROM, TCM, External Memory Interface

- Key peripherals

- Motor control block

- PWM, QEI, two 3.3V and one 5V ADC

- 2 CAN controllers

- 2 LIN controllers

- USB FS OTG/Host/Device controllers

" Industry's Fastest ARM Flash MCU running at 7 125MHz "

#### **LPC29xx** Derivatives

| Part<br>number | Flash  | SRAM<br>(incl<br>ETB) | TCM<br>(I/D) | CAN | LIN/<br>UART | Pins | UART<br>R§485 | SPI | 3V3<br>ADC | 5 V<br>ADC | SMC | USB<br>device | USB<br>host | USB<br>OTG | ЕТМ | QEI | l2C-bus | Clkout<br>pin |

|----------------|--------|-----------------------|--------------|-----|--------------|------|---------------|-----|------------|------------|-----|---------------|-------------|------------|-----|-----|---------|---------------|

| LPC2939        | 768 kB | 56 kB                 | 32/32 kB     | 2   | 2            | 208  | 2             | 3   | 2          | Yes        | Yes | Yes           | Yes         | Yes        | Yes | Yes | Yes     | Yes           |

| LPC2930        | -      | 56 kB                 | 32/32 kB     | 2   | 2            | 208  | 2             | 3   | 2          | Yes        | Yes | Yes           | Yes         | Yes        | Yes | Yes | Yes     | Yes           |

| LPC2929        | 768 kB | 56 kB                 | 32/32 kB     | 2   | 2            | 144  | 2             | 3   | 2          | Yes        | Yes | Yes           | No          | Yes        | Yes | Yes | Yes     | Yes           |

| LPC2927        | 512 kB | 56 kB                 | 32/32 kB     | 2   | 2            | 144  | 2             | 3   | 2          | Yes        | Yes | Yes           | No          | Yes        | Yes | Yes | Yes     | Yes           |

| LPC2925        | 512 kB | 40 kB                 | 16/16 kB     | 2   | 2            | 100  | 2             | 3   | 2          | No         | No  | Yes           | No          | No         | Yes | Yes | Yes     | Yes           |

| LPC2923        | 256 kB | 24 kB                 | 16/16 kB     | 2   | 2            | 100  | 2             | 3   | 2          | No         | No  | Yes           | No          | No         | Yes | Yes | Yes     | Yes           |

| LPC2921        | 128 kB | 24 kB                 | 16/16 kB     | 2   | 2            | 100  | 2             | 3   | 2          | No         | No  | Yes           | No          | No         | Yes | Yes | Yes     | Yes           |

| LPC2919/01     | 768 kB | 56 kB                 | 16/16 kB     | 2   | 2            | 144  | 2             | 3   | 2          | No         | Yes | No            | No          | No         | Yes | Yes | Yes     | Yes           |

| LPC2917/01     | 512 kB | 56 kB                 | 16/16 kB     | 2   | 2            | 144  | 2             | 3   | 2          | No         | Yes | No            | No          | No         | Yes | Yes | Yes     | Yes           |

Remark: Note that parts LPC2927 and LPC2929 are not fully pin compatible with parts LPC2917/01 and LPC2919/01 or LPC2917 and LPC2919. On the LPC2927/29 the MSCSS and timer blocks have a reduced pinout.

.....

#### LPC2939 Block Diagram

9

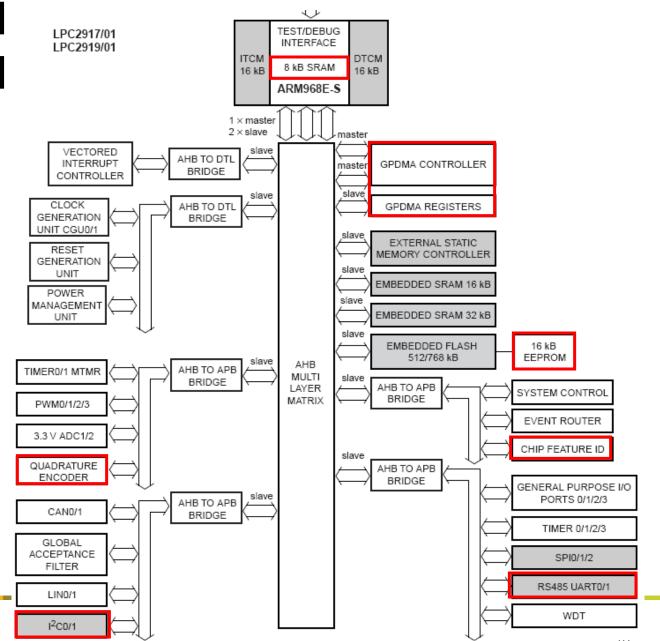

# LPC2919/01 LPC2917/01

- 8KB ETB

- QEI

- I2C0/1

- GP DMA

- Chip Feature ID

- RS485 UARTs

- 125MHz

## **Memory Support**

SRAM

EMC

Flash

EEPROM

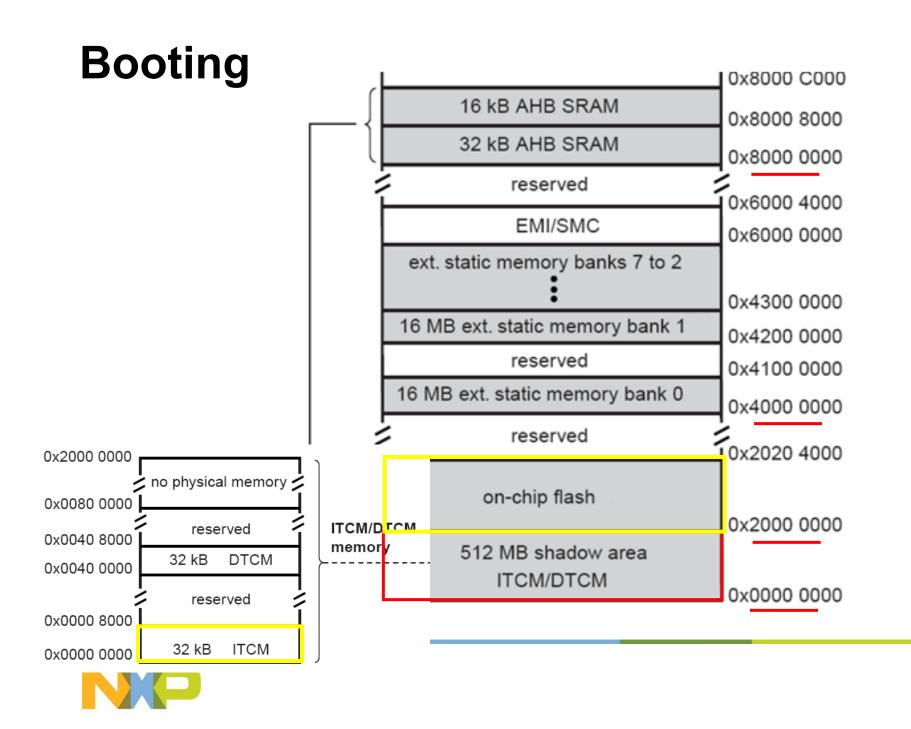

Booting

## **Overview**

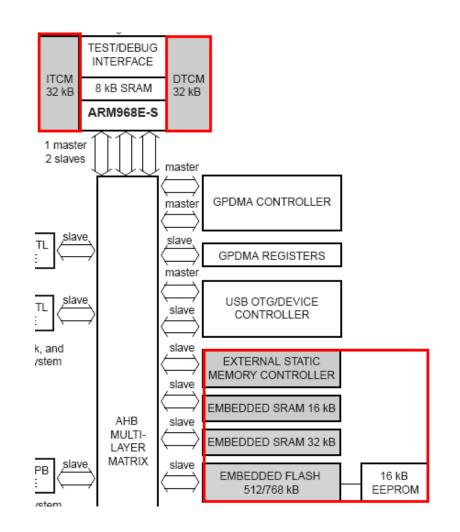

- 32KB or 16KB Instruction and Data TCMs

- On-chip SRAM- Up to 56KB

- On-chip Flash- Up to 768KB

- 16KB EEPROM

- 8KB ETB SRAM

- External static memory controller

## SRAM

- ▶ 56KB SRAM

- 32 KB general purpose SRAM

- Independent additional 16 KB SRAM

- 8KB ETB RAM

- LPC2921, LPC2923, LPC2925

- Memory shadowing from Flash to SRAM supported enabling faster interrupt execution from SRAM

| Part number | Flash  | SRAM            |                 |

|-------------|--------|-----------------|-----------------|

|             |        | SRAM<br>(16 kB) | SRAM<br>(32 kB) |

| LPC2917/01  | 512 kB | yes             | yes             |

| LPC2919/01  | 768 kB | yes             | yes             |

| LPC2921     | 128 kB | yes             | no              |

| LPC2923     | 256 kB | yes             | no              |

| LPC2925     | 512 kB | no              | yes             |

| LPC2927     | 512 kB | yes             | yes             |

| LPC2929     | 768 kB | yes             | yes             |

| LPC2930     | -      | yes             | yes             |

| LPC2939     | 768 kB | yes             | yes             |

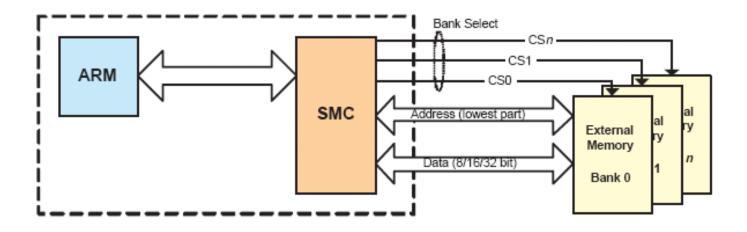

#### **External Memory Interface**

- 8 memory banks each capable of addressing 16MB

- 24-bit Address and 32-bit data bus

- Data bus configurable as 8-, 16- or 32-bit width

- Unused data bus pins become general purpose I/O

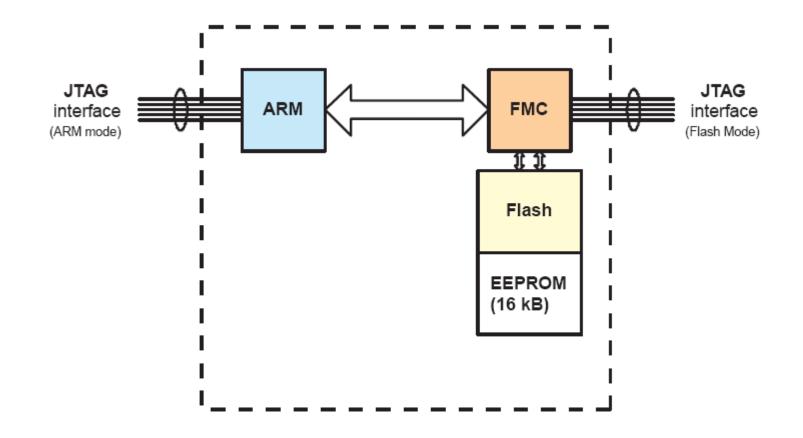

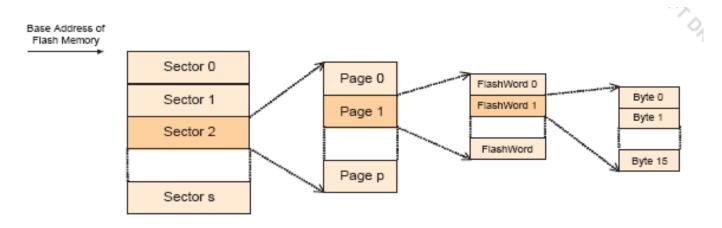

## **Flash Memory**

## **Flash Operations**

- Erasing: Done per sector

- Burning: Programming is done per page (smallest flash write block is 16 bytes)

- Protection

- Sector wise write protection

- JTAG interface can be disabled as well

## **Flash Features**

- Flash signature generation

- 128-bit signature from a range of Flash memory

- Flash interrupts

- END\_OF\_BURN, END\_OF\_ERASE, END\_OF\_MISR

- Index sector

- JTAG access protection

- Storage of customer information

- Sector security

- Flash endurance- 100K cycles (-25°C to 85°C)

- Flash retention- 10 years (<100K cycles @ -40°C to 85°C)</p>

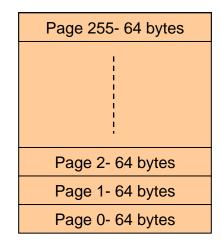

#### EEPROM

- 256 pages= 16KB

- Prerequisites for EEPROM operations

- Minimum operating voltage= 1.5V

- Need a 375kHz clock for erase/program operations

- EEPROM and Flash are independent modules

#### **16KB EEPROM**

## **EEPROM Operations**

- 8-bit, 16-bit and 32-bit read operations

- 8-bit, 16-bit and 32-bit write operations

- Erase/program page

- BIST operation supported that would lead to 2 16-bit signatures

- The EEPROM can be powered down

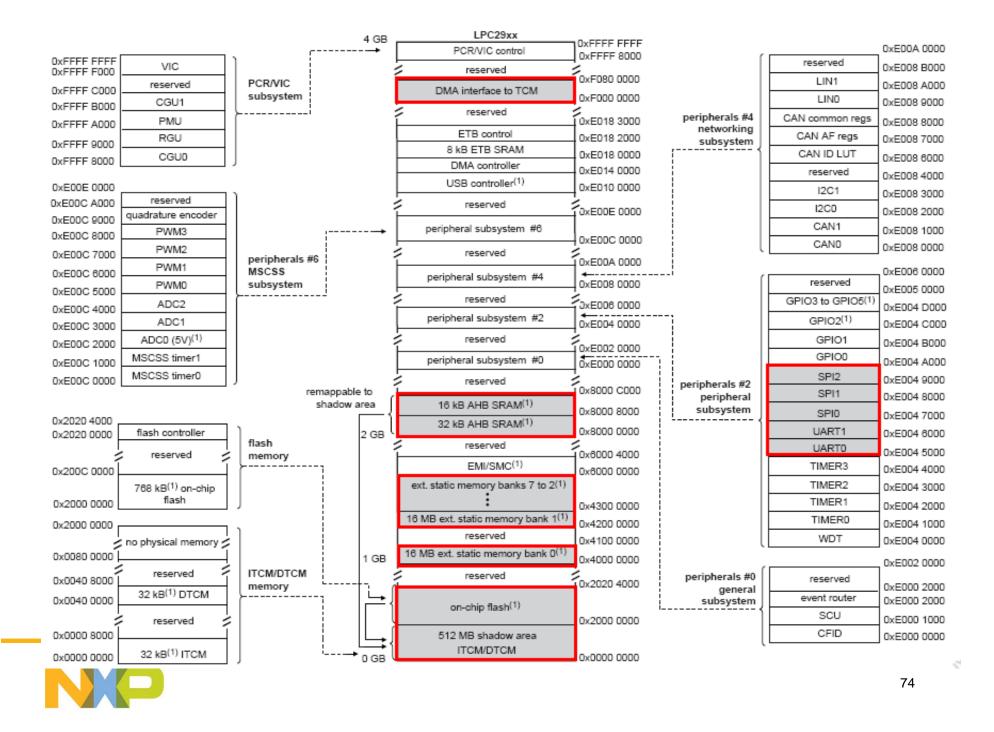

#### **Memory Regions**

| Memory region # | Address     | Description                            |

|-----------------|-------------|----------------------------------------|

| 0               | 0x0000 0000 | TCM area and shadow area               |

| 1               | 0x2000 0000 | embedded flash area                    |

| 2               | 0x4000 0000 | external static memory area            |

| 3               | 0x6000 0000 | external static memory controller area |

| 4               | 0x8000 0000 | internal SRAM area                     |

| 5               | 0xA000 0000 | not used                               |

| 6               | 0xC000 0000 | not used                               |

| 7               | 0xE000 0000 | bus-peripherals area                   |

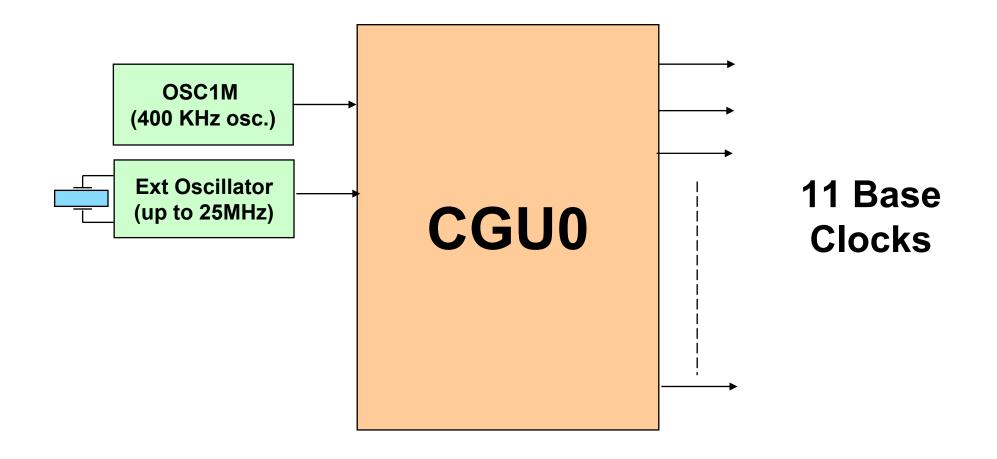

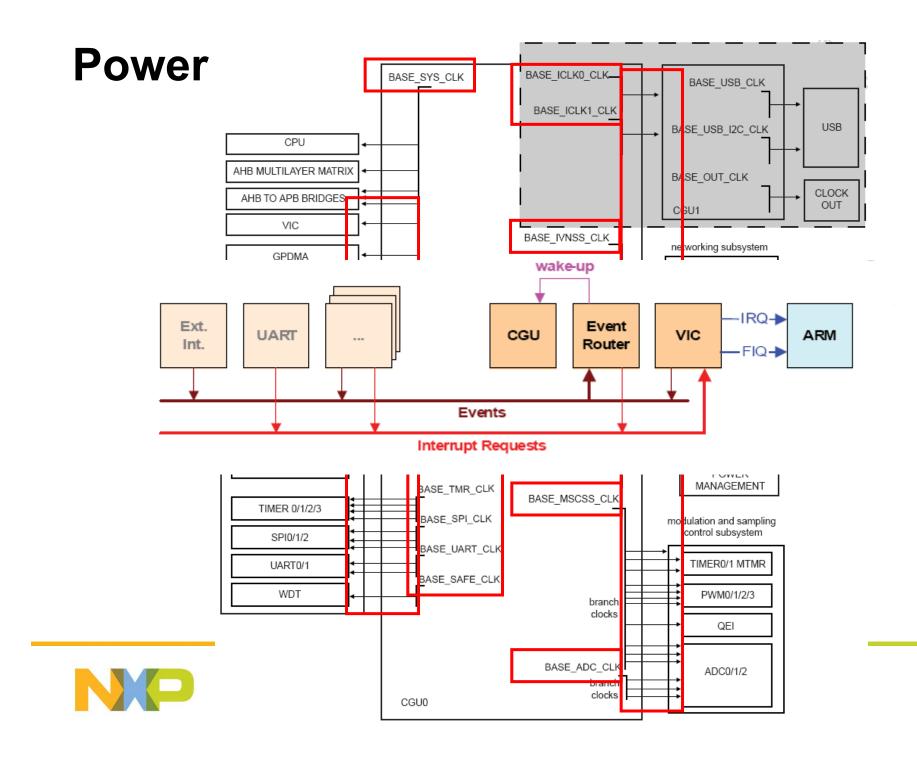

Power, Clock & Reset Subsystem (PCRSS)

Clock Generation Unit (CGU)

Reset Generation Unit (RGU)

Power Management Unit (PMU)

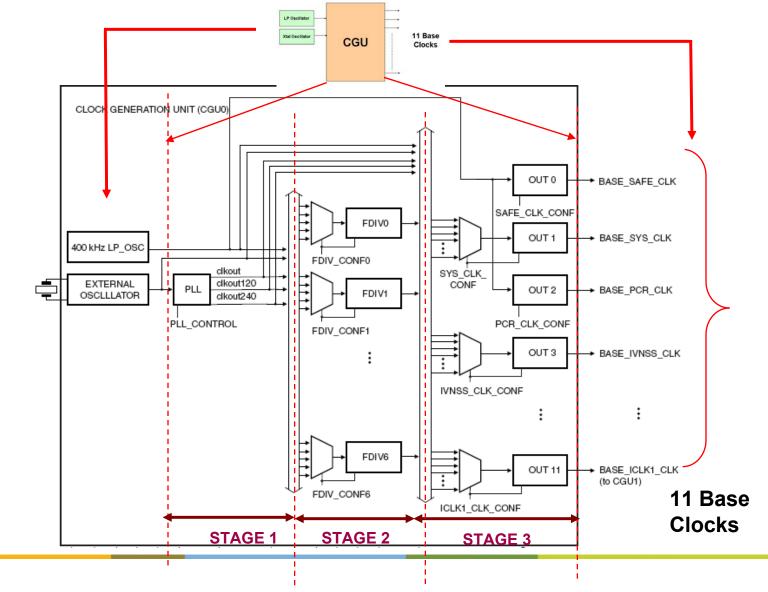

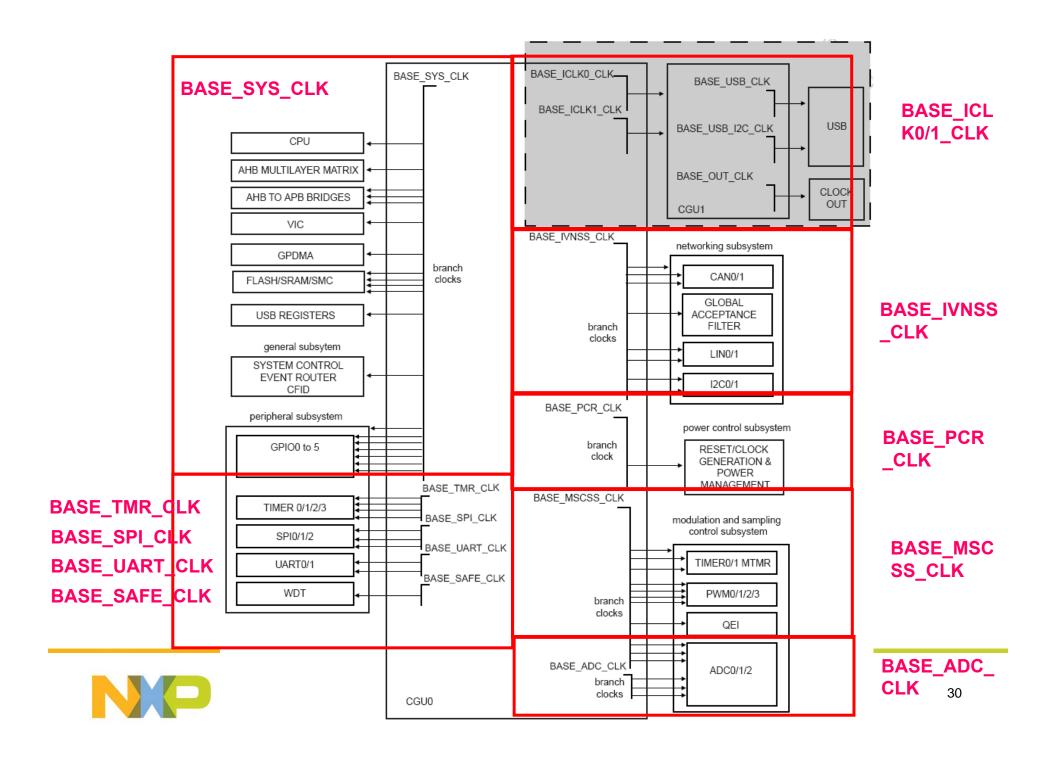

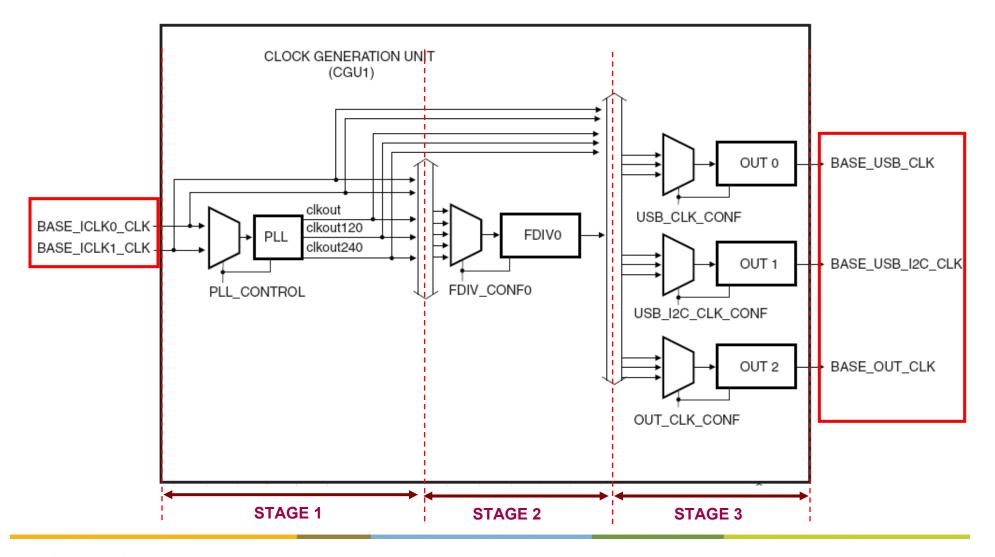

## **Clock Structure: CGU0 and CGU1**

- CGU0 provides clocks to all the subsystems

- CGU1 provides clock to the USB block and provides a clock output

- Both CGUs are functionally identical

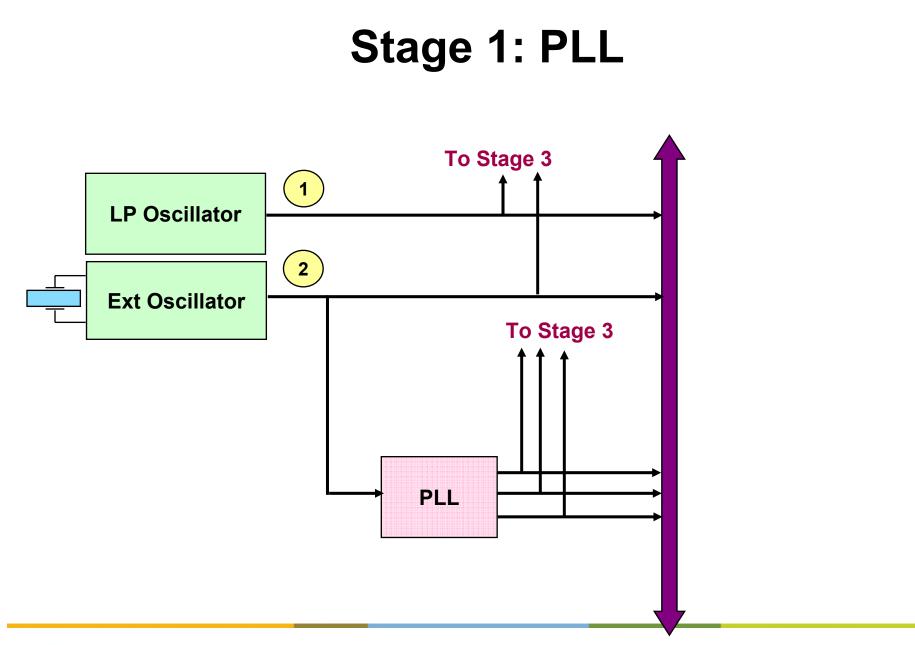

## **CGU0** Operation

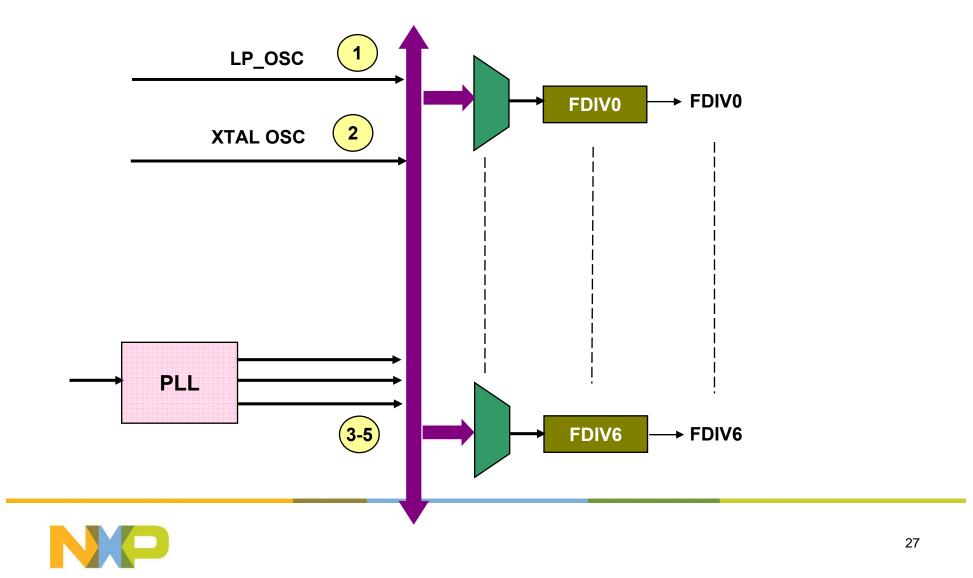

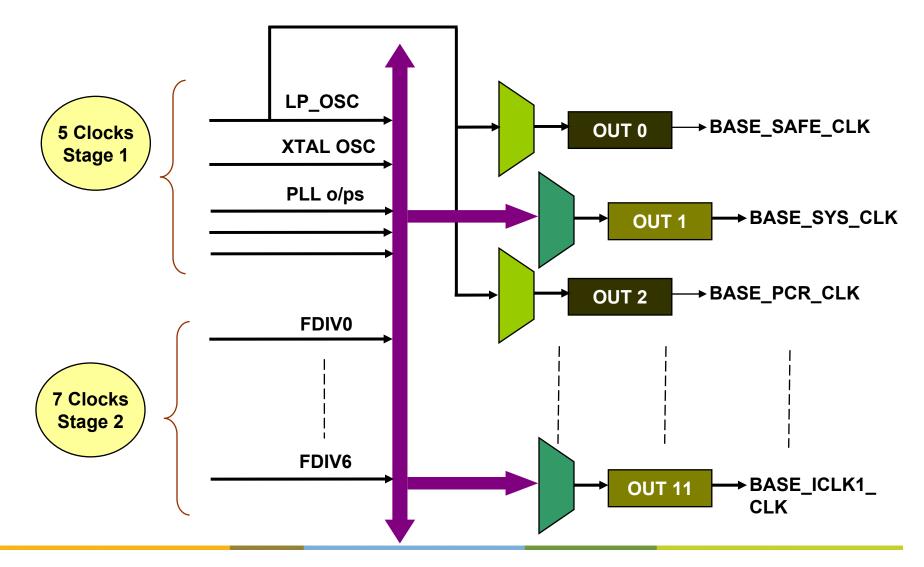

## **CGU0 Breakdown**

#### **Stage 2: Fractional Dividers**

#### **Stage 3: Output Registers**

## The 11 Base Clocks

| BASE CLOCK     | DESTINATION          |

|----------------|----------------------|

| BASE_SAFE_CLK  | Watchdog timer       |

| BASE_SYS_CLK   | ARM and AHB clock    |

| BASE_PCR_CLK   | PCR subsystem        |

| BASE_IVNSS_CLK | Networking subsystem |

| BASE_MSCSS_CLK | MSC subsystem        |

| BASE_ICLK0_CLK | Used by CGU1         |

| BASE_UART_CLK  | Clock to UARTs       |

| BASE_SPI_CLK   | Clock to SPIs        |

| BASE_TMR_CLK   | Clock to Timers      |

| BASE_ADC_CLK   | Clock to ADCs        |

| BASE_ICLK1_CLK | Used by CGU1         |

## CGU1

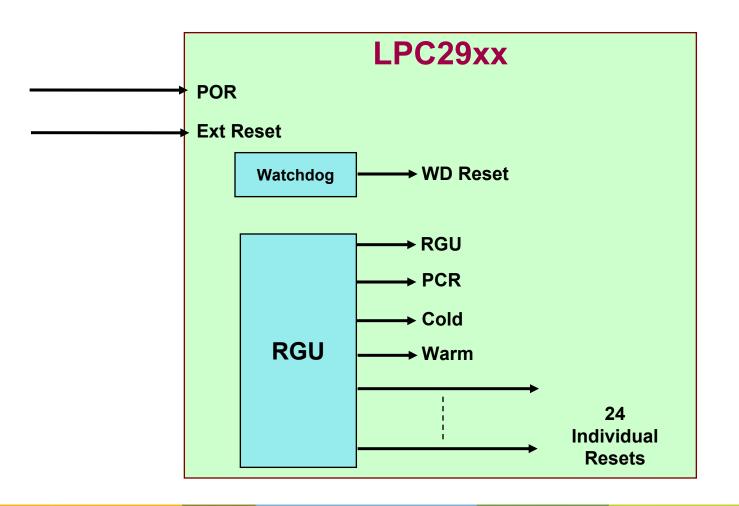

# RGU

#### **Block Resets Explained**

| Priority | Reset        | OSC1M | RGU | WDT | SCU | Flash<br>controller | CFID | Memory<br>controllers<br>(SRAM,SMC) | all other<br>peripherals |

|----------|--------------|-------|-----|-----|-----|---------------------|------|-------------------------------------|--------------------------|

| 1        | POR          | yes   | yes | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 2        | EXT<br>RESET | no    | yes | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 3        | RGU          | no    | yes | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 4        | WDT          | no    | no  | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 5        | PCR          | no    | no  | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 6        | Cold         | no    | no  | no  | no  | yes                 | yes  | yes                                 | yes                      |

| 7        | Warm         | no    | no  | no  | no  | no                  | no   | no                                  | yes                      |

## **RGU Summary**

- Activation of reset

- Group reset- RGU, PCR, Cold and Warm

- Provides 24 individual resets to different blocks like SPI, UART, USB etc.

- Other key functions

- Monitoring

- Finding the source of reset

- Locking the CGU

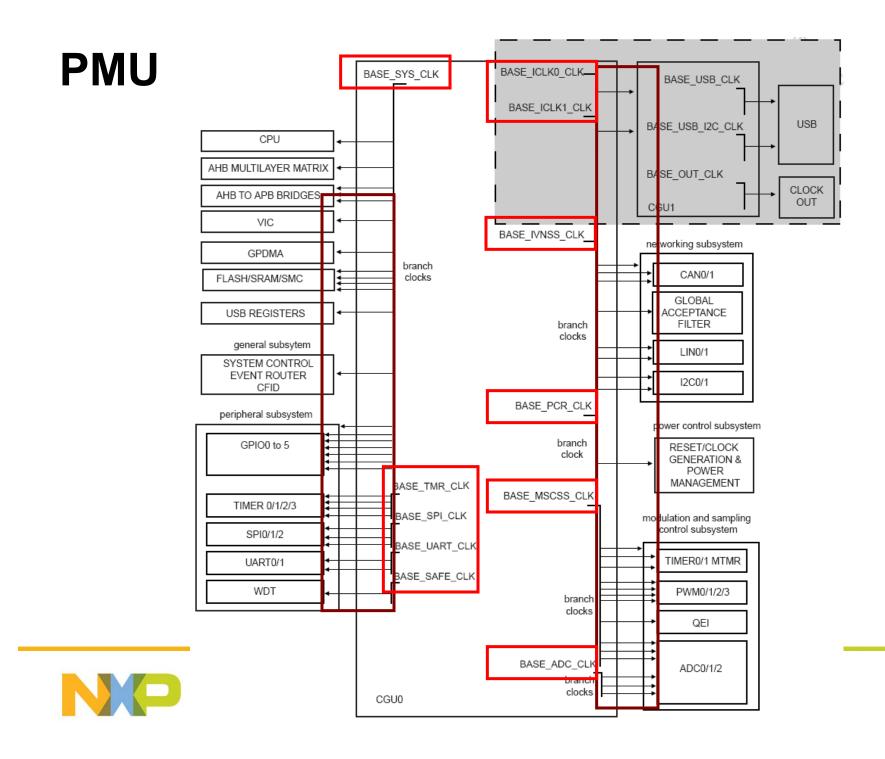

## **PMU Explained**

- Configuration and status registers are provided for all branch clocks (except CLK\_SYS\_CPU, CLK\_SYS & CLK\_SYS\_PCR)

- Individual branch clocks can be also be switched off

- Individual branch clocks can be made ready for sleep mode

- Using a single PD bit, all selected branch clocks can be put to sleep

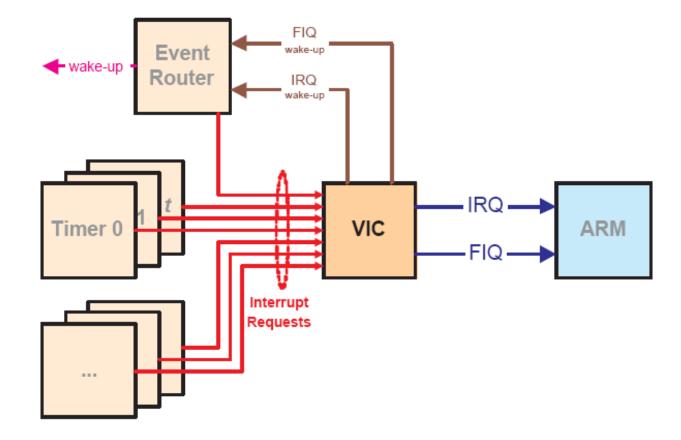

- Wakeup from idle mode, can be achieved with the Event router which is covered later

### General Subsystem (GeSS)

- System Control Unit (SCU)

- Event Router

- [Vectored Interrupt Controller]

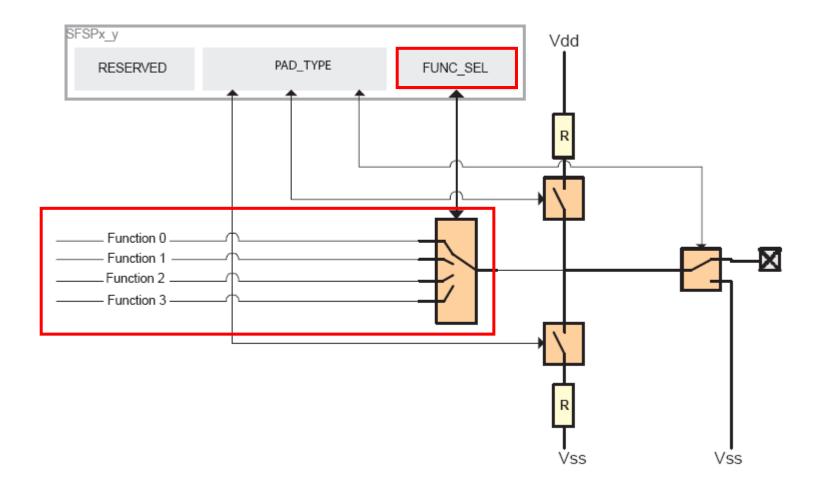

### **SCU- Selecting Pin Function**

### **Input Pads**

- Analog input

- Digital input

- With internal pull up/down

- With internal pull up

- With internal pull down

- With bus keeper

- When pull up is activated the input is NOT 5V TOLERANT

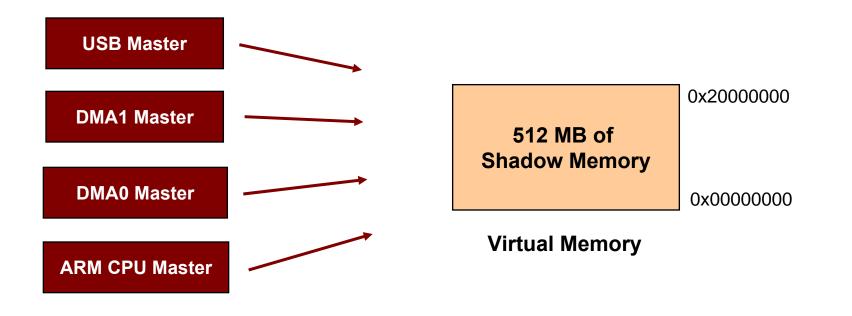

### **SCU- Memory Mapping**

Shadow memory mapping registers defines which part of the memory region is present in the shadow memory area

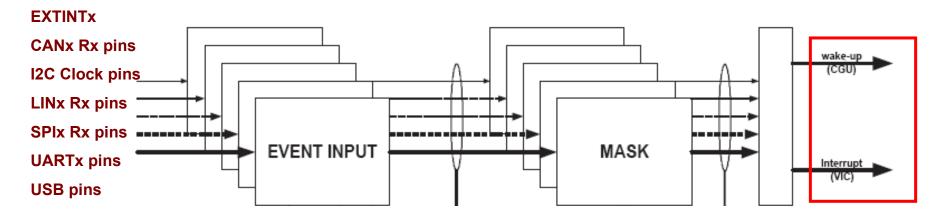

### **Event Router- What is it?**

- Main purpose:

- Uses "events" to wake up the CGU

- Uses "events" to act like an interrupt source to the VIC

- Events:

- External pins

- Internal interrupts

- Interacts with the VIC in both ways

- Acts like a source of interrupt to the VIC

- Or use the VIC as a source to wake up the CGU

### **Event Router**

#### **CAN** interrupt

**VIC IRQ**

**VIC FIQ**

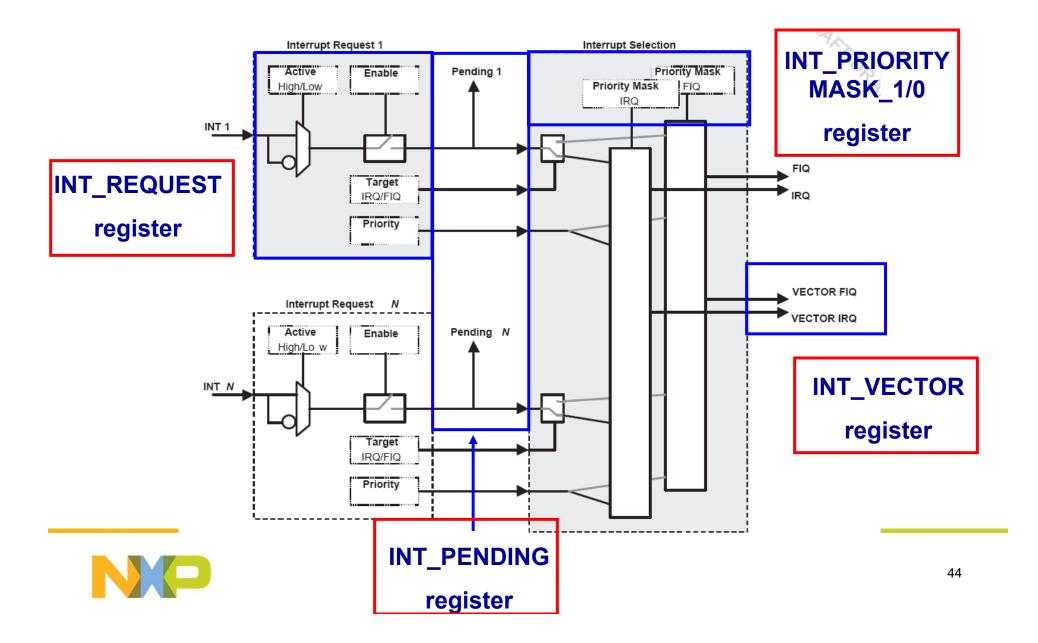

### **Vectored Interrupt Controller (VIC)**

### An Inside Look into the VIC

## Interrupt Execution (Nested & Non-Nested)

# Networking Subsystem (IVNSS)

CANLIN

▶ |<sup>2</sup>C

### **2 CAN Controllers- Key Features**

- Data rates up to 1 Mb/s, CAN 2.0B & ISO 11898 compatible

- Supports Full-CAN mode and extensive message filtering

- Each controller supports triple transmit buffers and double receive buffers

- Error and System Diagnostics Support, Self Reception Mode & Listen Only Mode

- Advanced Hardware Acceptance Filter to reduce CPU load

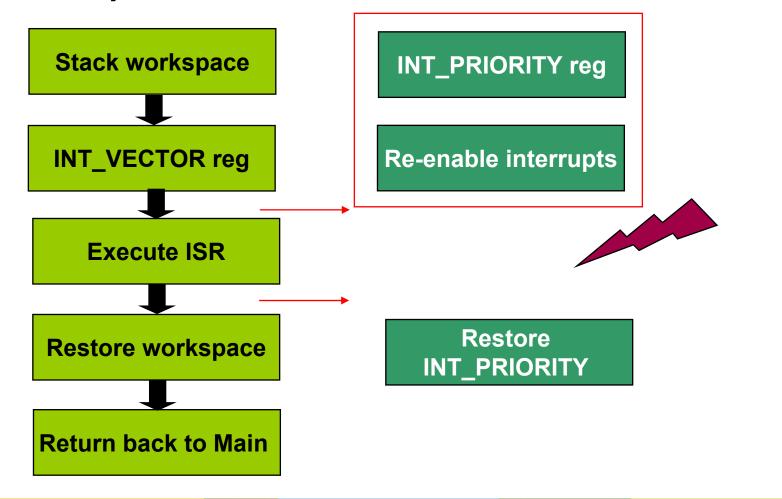

### **CAN Functional Description**

### **Global Acceptance Filter**

- Uses a 2KB look-up table

- The table can contain up to 1024 SFI or 512 EFI or mixture of both types

- Broken up into 5 sections

- CAN configuration example: http://www.nxp.com/acrobat\_download/applicationnotes/AN10674\_1.pdf

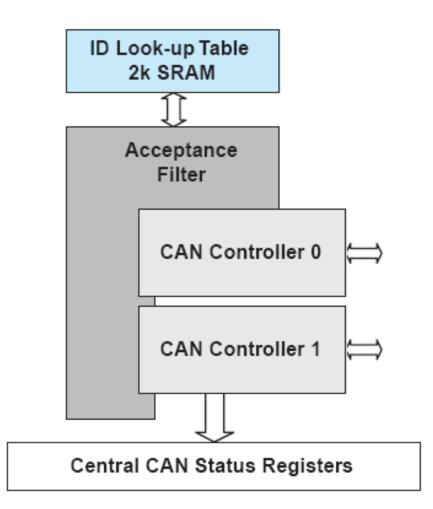

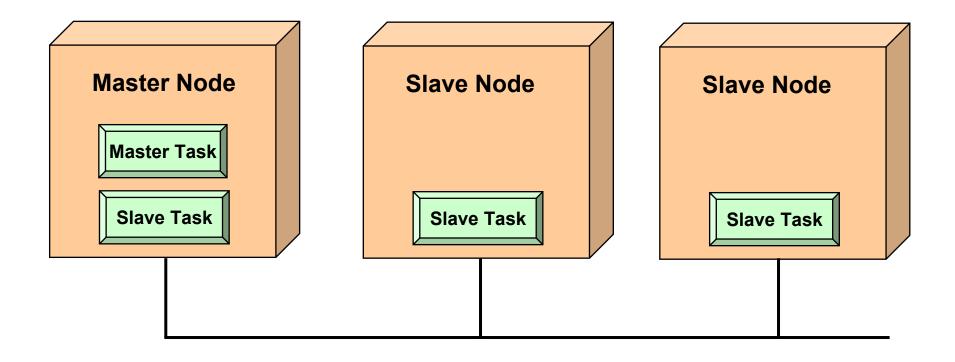

### **LIN-An Introduction**

- Low cost sub network, complementing CAN and FlexRay

- Single master, multiple slaves concept

- Based on the UART interface

- Speed up to 20Kbits/sec

### **LIN Network**

### **LIN Message Transmission**

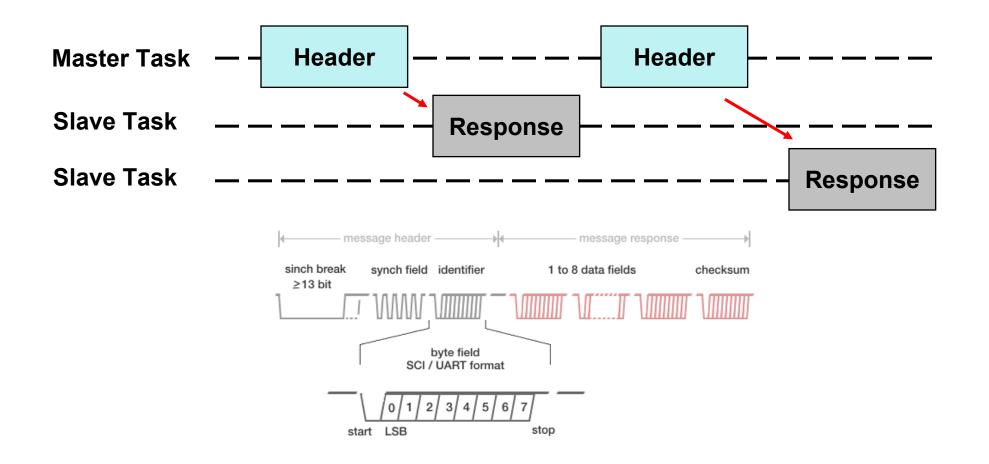

### **LIN Master Controller**

- 4 32-bit Message buffers

- Programmable sync-break from 10-16 bits

- Step-by-step example for using the LIN master"

#### 2 I<sup>2</sup>C-Interfaces

- 400 KHz transfer rates (Fast I2C)

- Easy to configure as master, slave or master/slave

- Multi-master bus with arbitration control

- Supports multiple address recognition and a bus monitor mode

## Peripheral Subsystem (PeSS) IO ports SPIs Timers UARTs

### **General Purpose IO Ports**

- Up to 108 IO pins with programmable pull up, pull down and bus keeper

- 6 GPIO ports each capable of accessing up to 32 pins

- The pins must be routed in the SCU

| Part number   | GPIO<br>port 0 | GPIO<br>port 1 | GPIO<br>port 2 | GPIO<br>port 3 | GPIO<br>port 4 | GPIO<br>port 5 | GPIO<br>port<br>5/USB |

|---------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------------|

| LPC2917/19/01 | P0[31:0]       | P1[31:0]       | P2[27:0]       | P3[15:0]       | -              | -              | -                     |

| LPC2921/23/25 | P0[31:0]       | P1[27:0]       | -              | -              | -              | -              | P5[19:18]             |

| LPC2927/29    | P0[31:0]       | P1[27:0]       | P2[27:0]       | P3[15:0]       | -              | -              | P5[19:18]             |

| LPC2930       | P0[31:0]       | P1[27:0]       | P2[27:0]       | P3[15:0]       | P4[23:0]       | P5[15:0]       | P5[19:16]             |

| LPC2939       | P0[31:0]       | P1[27:0]       | P2[27:0]       | P3[15:0]       | P4[23:0]       | P5[15:0]       | P5[19:16]             |

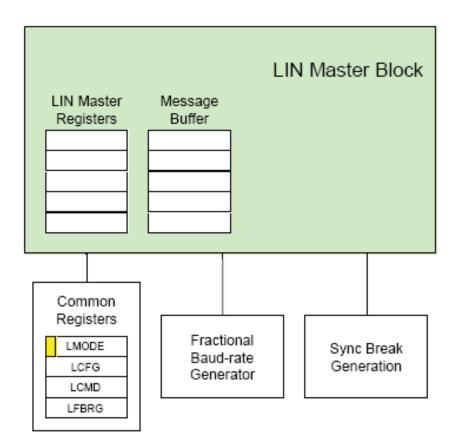

### Timers 0/1/2/3

### Watchdog-Features

- The timer registers are protected by key sequences

- Two operating modes- Normal and debug

- Internal chip reset when not triggered periodically- Through RGU

| Priority | Reset        | OSC1M | RGU | WDT | SCU | Flash<br>controller | CFID | Memory<br>controllers<br>(SRAM,SMC) | all other<br>peripherals |

|----------|--------------|-------|-----|-----|-----|---------------------|------|-------------------------------------|--------------------------|

| 1        | POR          | yes   | yes | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 2        | EXT<br>RESET | no    | yes | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 3        | RGU          | no    | yes | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 4        | WDT          | no    | no  | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 5        | PCR          | no    | no  | yes | yes | yes                 | yes  | yes                                 | yes                      |

| 6        | Cold         | no    | no  | no  | no  | yes                 | yes  | yes                                 | yes                      |

| 7        | Warm         | no    | no  | no  | no  | no                  | no   | no                                  | yes                      |

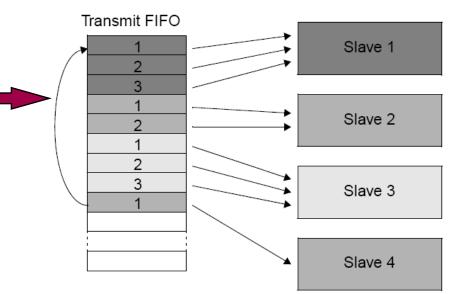

### SPI 0/1/2

- Master or slave operation

- Supports up to four slaves in sequential multi-slave operation (next slide)

- Programmable clock bit rate and pre-scaler, based on SPI source clock from the CGU

- Separate transmit and receive FIFO buffers, 16-bit wide, 32 locations deep

- Programmable data frame size from 4 to 16 bits

- Internal loop back test mode

### **SPI Mode of Operation**

- Master mode

- Normal transmission mode

- Software intervention needed each time a new slave needs to be addressed

- Sequential-slave mode

- Will sequentially transmit data to 4 slaves as long as data is available in the FIFO

- Max. clock rate in master mode <= fclk\_spi/2

- Slave mode

- Max. clock rate in slave mode= fclk\_spi/4

### **UART 0/1 Interfaces**

- Industry standard 16C550 UARTs

- RS-485/9-bit mode support. Great for Multiprocessor Environment!

- I6 bytes FIFO message buffer for transmit and receive

- Fractional divider

- Standard modem interface signals included (CTS, DCD, DTS, DTR, RI, RTS)

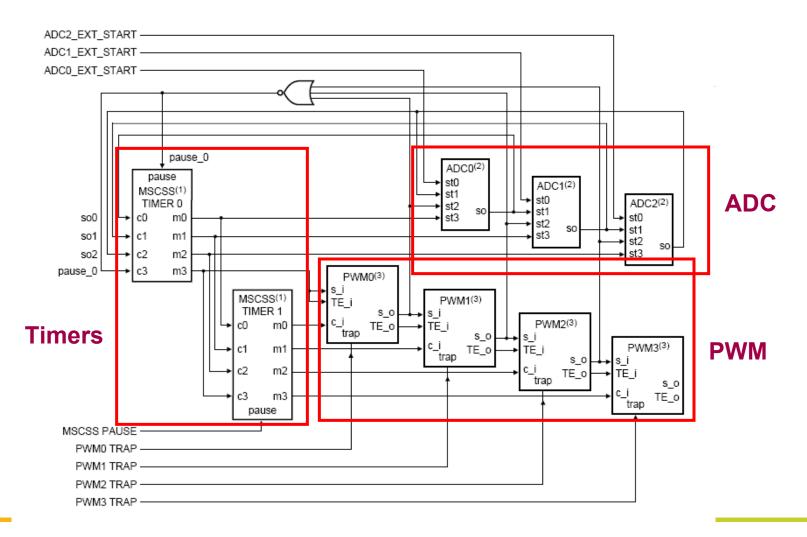

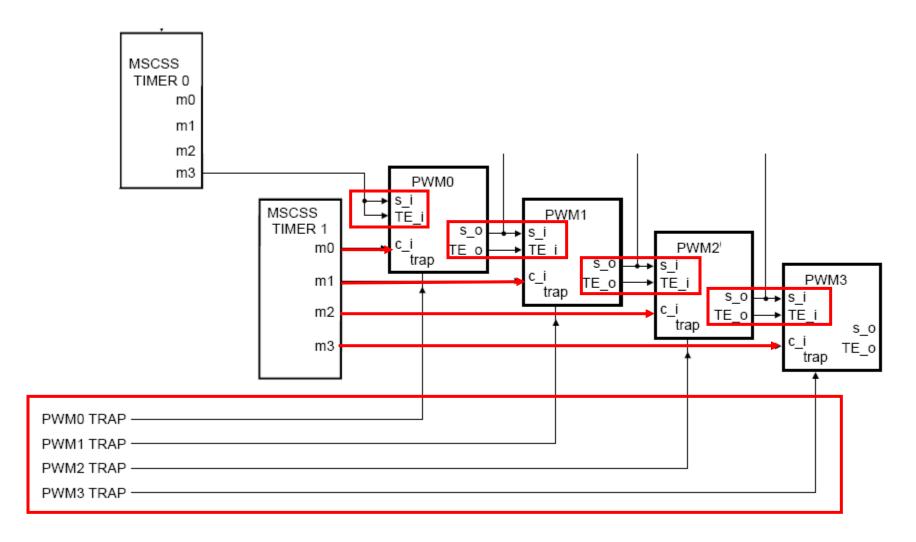

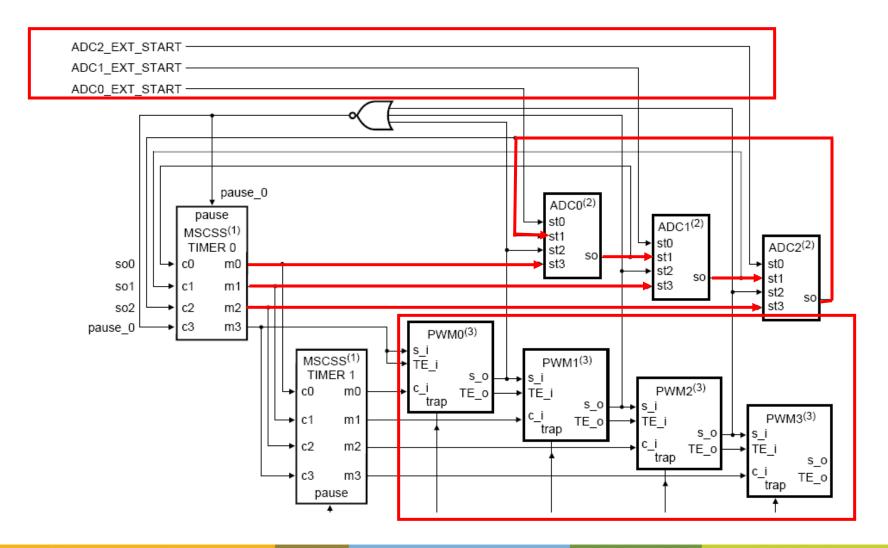

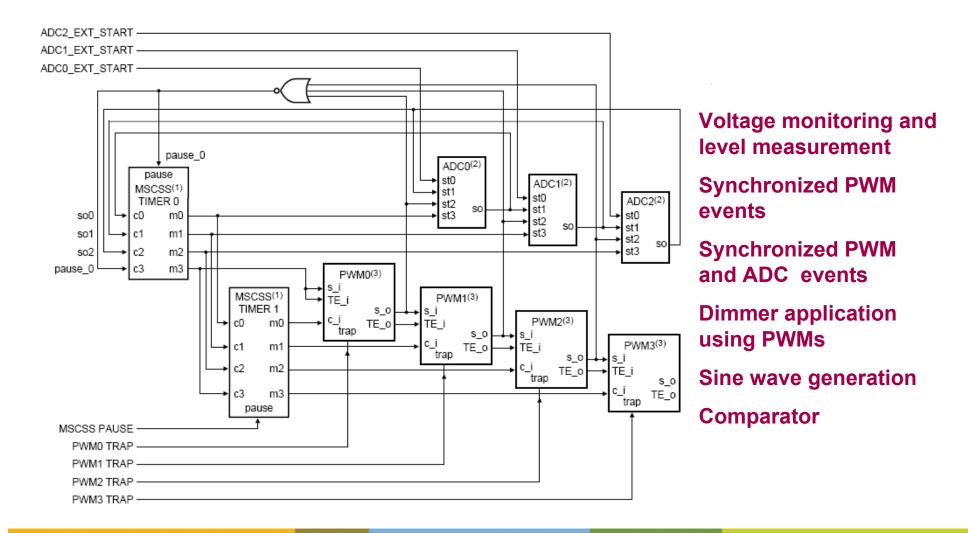

MSC Subsystem (MSCSS) • PWM • ADC

### **MSCSS-** The Big Picture

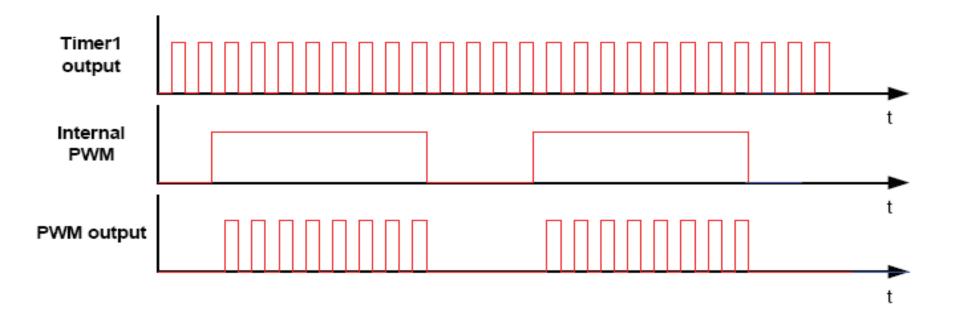

### **PWM Blocks- Key Features**

- 4 PWM blocks that can operate synchronously

- Each PWM can produce 6 PWM outputs

- Operation modes

- Continuous

- Burst

- Trap

- Run-once

- Capture Functionality

- Shadow register set

### **PWM Explained (1)**

- -

### **PWM Explained (2)**

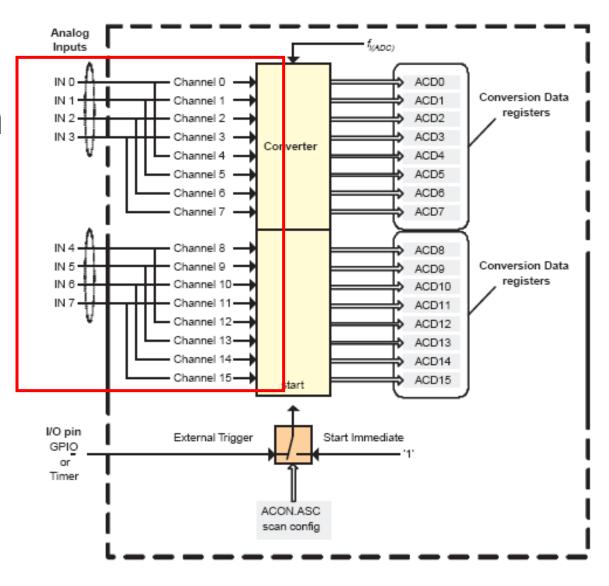

### **ADC-Key features**

- Two 10-bit ADCs, 8-channels each, with 3.3 V measurement range

- One 8-channel 10-bit ADC with 5.0 V measurement range

- Total 24 analog inputs, with conversion times as low as 2.44 µs per channel

- Each channel provides a compare function to minimize interrupts

### ADC Block Diagram

### **ADC Start Conditions**

### **MSCSS-** Possible Applications

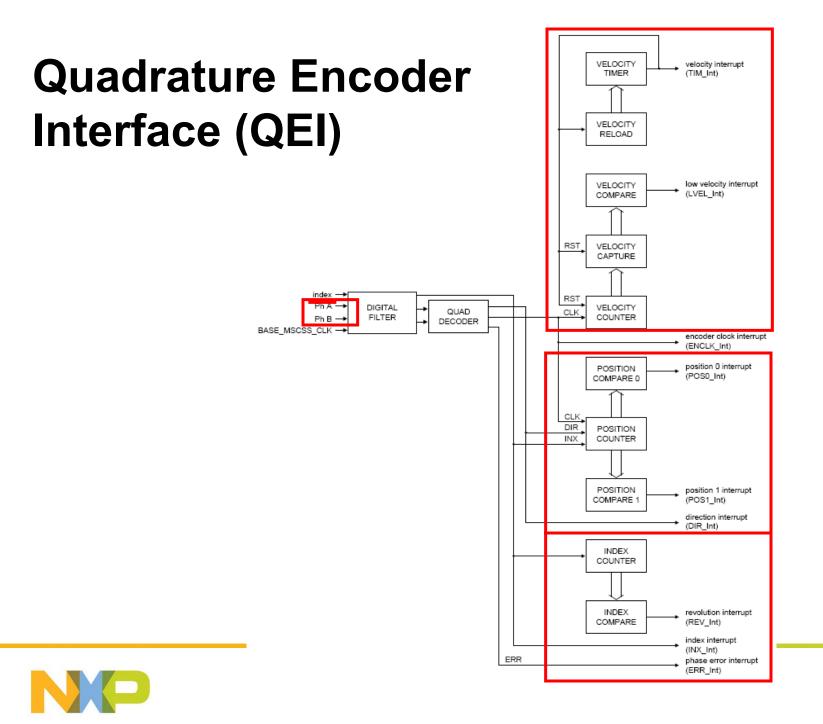

### **QEI- Key Features**

- Tracks encoder position

- Digital filter with programmable delays for encoder input signals

- Programmable for 2X or 4X position counting.

- Velocity capture

- Index counter for revolution counting

- Can combine index and position interrupts to produce an interrupt for whole and partial revolution displacement

# **Other Peripherals**

GPDMA

USB FS Host/Device/OTG Controllers

# **USB** Portfolio

| Core                                                                                                  | Product | On-Chip Controller |      |     | No. of |              |  |  |  |

|-------------------------------------------------------------------------------------------------------|---------|--------------------|------|-----|--------|--------------|--|--|--|

|                                                                                                       |         | Device             | Host | OTG | Ports  | On-chip PHY  |  |  |  |

| ARM968                                                                                                | LPC2921 | FS                 | -    | -   | 1      | Yes          |  |  |  |

|                                                                                                       | LPC2923 | FS                 | -    | -   | 1      | Yes          |  |  |  |

|                                                                                                       | LPC2925 | FS                 | -    | -   | 1      | Yes          |  |  |  |

|                                                                                                       | LPC2927 | FS                 | -    | FS  | 1      | Device       |  |  |  |

|                                                                                                       | LPC2929 | FS                 | -    | FS  | 1      | Device       |  |  |  |

|                                                                                                       | LPC2930 | FS                 | FS   | FS  | 2      | Device, Host |  |  |  |

|                                                                                                       | LPC2939 | FS                 | FS   | FS  | 2      | Device, Host |  |  |  |

| Notes: All devices (except LPC2927/29) with 2 ports can be used in the following combinations: Device |         |                    |      |     |        |              |  |  |  |

| (OTG) + Host, Host (OTG) + Host, Host + Device                                                        |         |                    |      |     |        |              |  |  |  |

# **USB Device/ Host/ OTG controllers**

- Device

- Supports 32 physical (16 logical) endpoints

- Supports Control, Bulk, Interrupt and Isochronous endpoints

- Scalable realization of endpoints at run time

- Supports SoftConnect and GoodLink features

- Host controller

- OHCI compliant

- The Host Controller has four USB states visible to the SW Driver

- OTG

- Fully compliant with On-The-Go supplement to the USB 2.0 Specification, Revision 1.0a

- Hardware support for Host Negotiation Protocol (HNP)

- Includes a programmable timer required for HNP and SRP

- Supports any OTG transceiver compliant with the OTG Transceiver Specification

# **Power Modes**

#### **Power Numbers- LPC2939**

| Symbol                | Parameter           | Conditions                                                | Min  | Тур  | Мах  | Unit       |

|-----------------------|---------------------|-----------------------------------------------------------|------|------|------|------------|

| Supplies              |                     |                                                           |      |      |      |            |

| Core supply           |                     |                                                           |      |      |      |            |

| V <sub>DD(CORE)</sub> | core supply voltage |                                                           | 1.71 | 1.80 | 1.89 | V          |

| I <sub>DD(CORE)</sub> | core supply current | ARM9 and all<br>peripherals active at<br>max clock speeds | -    | 1.1  | 2.5  | mA/<br>MHz |

|                       |                     | all clocks off                                            | -    | 30   | 475  | μA         |

| I/O supply            |                     |                                                           |      |      |      |            |

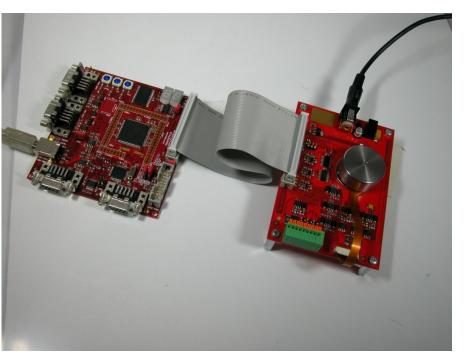

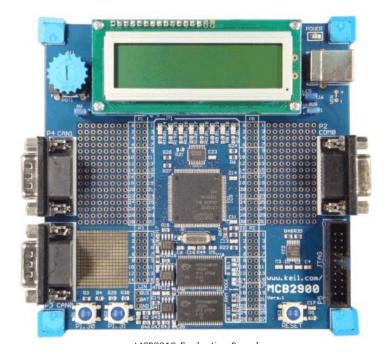

### **Evaluation Boards**

#### **Hitex LPC2919 Board**

Keil LPC2919 Board

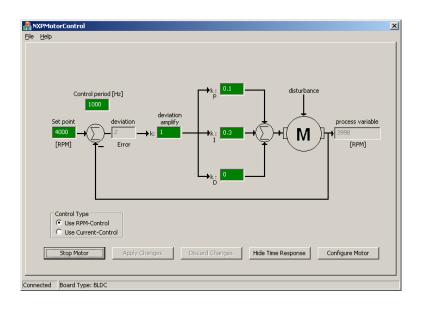

### **Motor Control Application**