# UM10308 P89LPC9331/9341/9351/9361 User manual Rev. 03 — 17 June 2009

User manual

### **Document information**

| Info     | Content                                                        |

|----------|----------------------------------------------------------------|

| Keywords | P89LPC9331/9341/9351/9361                                      |

| Abstract | Technical information for the P89LPC9331/9341/9351/9361 device |

# P89LPC9331/9341/9351/9361 User manual

# **Revision history**

| Rev | Date     | Description                                                  |

|-----|----------|--------------------------------------------------------------|

| 03  | 20090617 | Added information for the P89LPC9361 device.                 |

| 02  | 20090505 | Added information for the P89LPC9331 and P89LPC9341 devices. |

| 01  | 20081118 | Initial version.                                             |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

### P89LPC9331/9341/9351/9361 User manual

# 1. Introduction

The P89LPC9331/9341/9351/9361 are single-chip microcontrollers designed for applications demanding high-integration, low cost solutions over a wide range of performance requirements. The P89LPC9331/9341/9351/9361 are based on a high performance processor architecture that executes instructions in two to four clocks, six times the rate of standard 80C51 devices. Many system-level functions have been incorporated into the P89LPC9331/9341/9351/9361 in order to reduce component count, board space, and system cost.

Table 1. Product comparison overview

| Device     | Flash<br>Memory | Sector size | ADC1 | ADC0 | PGA0 | PGA1 | Temp<br>Sensor | CCU | DATA<br>EEPROM |

|------------|-----------------|-------------|------|------|------|------|----------------|-----|----------------|

| P89LPC9331 | 4 kB            | 1 kB        | Χ    | Χ    | -    | -    | Χ              | -   | -              |

| P89LPC9341 | 4 kB            | 1 kB        | Χ    | Χ    | -    | -    | Χ              | -   | -              |

| P89LPC9351 | 8 kB            | 1 kB        | Χ    | Χ    | Χ    | Χ    | Χ              | Χ   | Χ              |

| P89LPC9361 | 16 kB           | 1 kB        | Χ    | Χ    | Χ    | Χ    | Χ              | Χ   | Χ              |

**Product Comparison Overview**

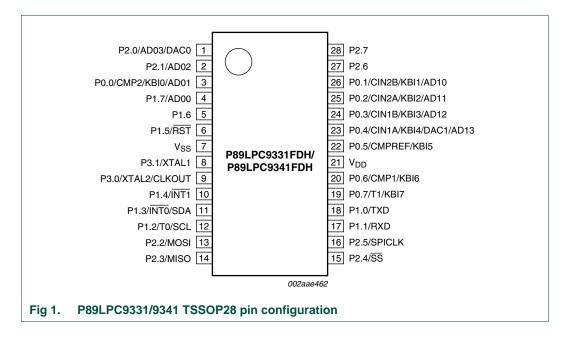

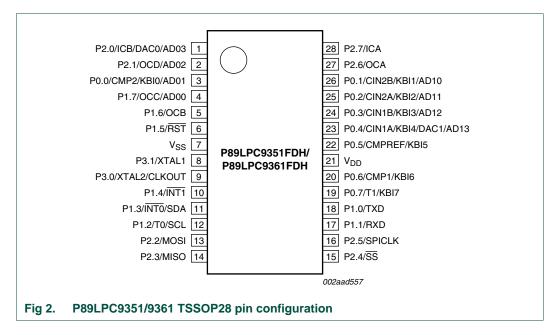

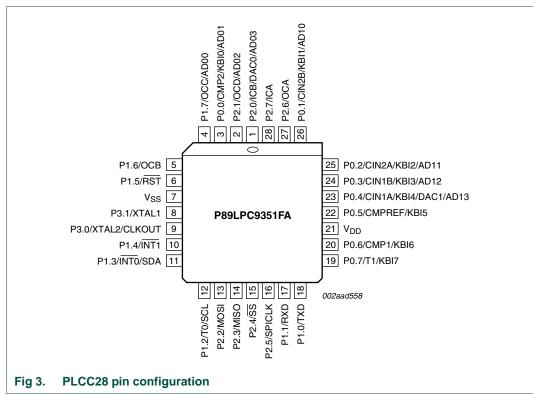

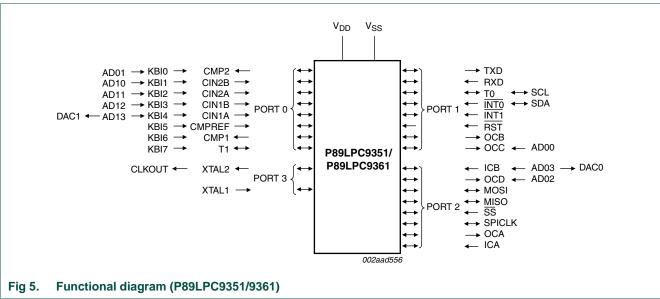

# 1.1 Pin configuration

### P89LPC9331/9341/9351/9361 User manual

# P89LPC9331/9341/9351/9361 User manual

# 1.2 Pin description

Table 2. Pin description

|                | Pin                | Type     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------|--------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | PLCC28,<br>TSSOP28 |          |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0.0 to P0.7   |                    | I/O      | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. During reset Port 0 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <a configurations"="" href="Section5.1" port="">Section5.1</a> "Port configurations" for details. |

|                |                    |          | The Keypad Interrupt feature operates with Port 0 pins.                                                                                                                                                                                                                                                                                                                                                                                       |

|                |                    |          | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |                    |          | Port 0 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                            |

| P0.0/CMP2/     | 3                  | I/O      | <b>P0.0</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| KBI0/AD01      |                    | 0        | CMP2 — Comparator 2 output                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                |                    | <u>l</u> | KBI0 — Keyboard input 0.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                    | l        | AD01 — ADC0 channel 1 analog input.                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.1/CIN2B/    | 26                 | I/O      | <b>P0.1</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| KBI1/AD10      |                    | I        | CIN2B — Comparator 2 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |                    | I        | KBI1 — Keyboard input 1.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                    | I        | AD10 — ADC1 channel 0 analog input.                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.2/CIN2A/    | 25                 | I/O      | <b>P0.2</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (BI2/AD11      |                    | I        | CIN2A — Comparator 2 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |                    | I        | KBI2 — Keyboard input 2.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                    | I        | AD11 — ADC1 channel 1 analog input.                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.3/CIN1B/    | 24                 | I/O      | P0.3 — Port 0 bit 3. High current source.                                                                                                                                                                                                                                                                                                                                                                                                     |

| KBI3/AD12      |                    | I        | CIN1B — Comparator 1 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |                    | I        | KBI3 — Keyboard input 3.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                    | I        | AD12 — ADC1 channel 2 analog input.                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.4/CIN1A/    | 23                 | I/O      | P0.4 — Port 0 bit 4. High current source.                                                                                                                                                                                                                                                                                                                                                                                                     |

| KBI4/DAC1/AD13 |                    | I        | CIN1A — Comparator 1 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |                    | I        | KBI4 — Keyboard input 4.                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                |                    | 0        | DAC1 — Digital-to-analog converter output 1.                                                                                                                                                                                                                                                                                                                                                                                                  |

|                |                    | I        | AD13 — ADC1 channel 3 analog input.                                                                                                                                                                                                                                                                                                                                                                                                           |

| P0.5/CMPREF/   | 22                 | I/O      | <b>P0.5</b> — Port 0 bit 5. High current source.                                                                                                                                                                                                                                                                                                                                                                                              |

| KBI5           |                    | I        | CMPREF — Comparator reference (negative) input.                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                    | I        | KBI5 — Keyboard input 5.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P0.6/CMP1/KBI6 | 20                 | I/O      | <b>P0.6</b> — Port 0 bit 6. High current source.                                                                                                                                                                                                                                                                                                                                                                                              |

|                |                    | 0        | CMP1 — Comparator 1 output.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                |                    | I        | KBI6 — Keyboard input 6.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P0.7/T1/KBI7   | 19                 | I/O      | P0.7 — Port 0 bit 7. High current source.                                                                                                                                                                                                                                                                                                                                                                                                     |

|                |                    | I/O      | T1 — Timer/counter 1 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                                 |

|                |                    |          |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# P89LPC9331/9341/9351/9361 User manual

Table 2.

Pin description ...continued

| Symbol        | Pin                | Type          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | PLCC28,<br>TSSOP28 |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| P1.0 to P1.7  |                    | I/O, I<br>[1] | <b>Port 1:</b> Port 1 is an 8-bit I/O port with a user-configurable output type, except for three pins as noted below. During reset Port 1 latches are configured in the input only mode with the internal pull-up disabled. The operation of the configurable Port 1 pins as inputs and outputs depends upon the port configuration selected. Each of the configurable port pins are programmed independently. Refer to Section 5.1 "Port configurations" for details. P1.2 to P1.3 are open drain when used as outputs. P1.5 is input only. |

|               |                    |               | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |                    |               | Port 1 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P1.0/TXD      | 18                 | I/O           | <b>P1.0</b> — Port 1 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                    | 0             | TXD — Transmitter output for serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P1.1/RXD      | 17                 | I/O           | <b>P1.1</b> — Port 1 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|               |                    | I             | RXD — Receiver input for serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1.2/T0/SCL   | 12                 | I/O           | P1.2 — Port 1 bit 2 (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |                    | I/O           | <b>T0</b> — Timer/counter 0 external count input or overflow output (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |                    | I/O           | SCL — I <sup>2</sup> C-bus serial clock input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P1.3/INT0/SDA | 11                 | I/O           | P1.3 — Port 1 bit 3 (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |                    | I             | INT0 — External interrupt 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |                    | I/O           | SDA — I <sup>2</sup> C-bus serial data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P1.4/INT1     | 10                 | I/O           | P1.4 — Port 1 bit 4. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |                    | I             | INT1 — External interrupt 1 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

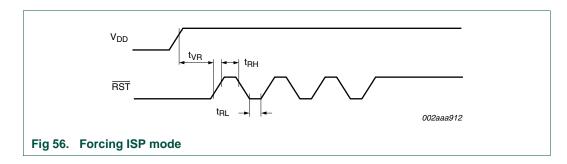

| P1.5/RST      | 6                  | I             | <b>P1.5</b> — Port 1 bit 5 (input only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |                    | I             | <b>RST</b> — External Reset input during power-on or if selected via UCFG1. When functioning as a reset input, a LOW on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor begins execution at address 0. Also used during a power-on sequence to force ISP mode.                                                                                                                                                                                                      |

| P1.6/OCB      | 5                  | I/O           | P1.6 — Port 1 bit 6. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |                    | 0             | OCB — Output Compare B. (P89LPC9351/9361)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P1.7/OCC/AD00 | 4                  | I/O           | P1.7 — Port 1 bit 7. High current source.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |                    | 0             | OCC — Output Compare C. (P89LPC9351/9361)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |                    | I             | AD00 — ADC0 channel 0 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P2.0 to P2.7  |                    | I/O           | Port 2: Port 2 is an 8-bit I/O port with a user-configurable output type. During reset Port 2 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 2 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <a href="Section5.1">Section5.1</a> "Port configurations" for details.                                                                                                                                   |

|               |                    |               | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|               |                    |               | Port 2 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P2.0/ICB/DAC0 | 1                  | I/O           | <b>P2.0</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| /AD03         |                    | I             | ICB — Input Capture B. (P89LPC9351/9361)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|               |                    | 0             | DAC0 — Digital-to-analog converter output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|               |                    | I             | AD03 — ADC0 channel 3 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# P89LPC9331/9341/9351/9361 User manual

Table 2. Pin description ...continued

| Symbol          | Pin                | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|--------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | PLCC28,<br>TSSOP28 |      |                                                                                                                                                                                                                                                                                                                                                                                                            |

| P2.1/OCD/AD02   | 2                  | I/O  | <b>P2.1</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | 0    | OCD — Output Compare D. (P89LPC9351/9361)                                                                                                                                                                                                                                                                                                                                                                  |

|                 |                    | I    | AD02 — ADC0 channel 2 analog input.                                                                                                                                                                                                                                                                                                                                                                        |

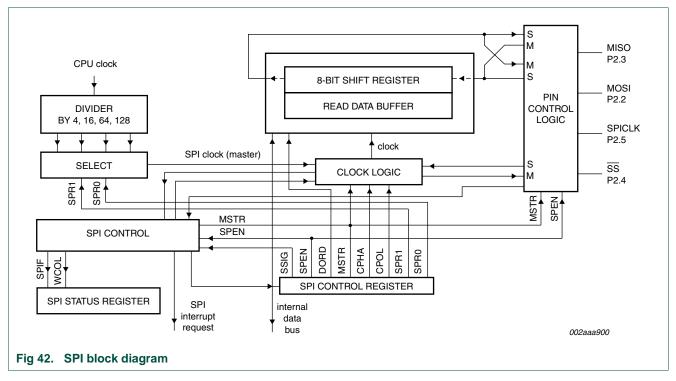

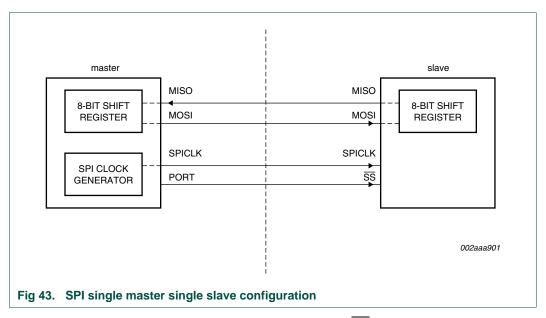

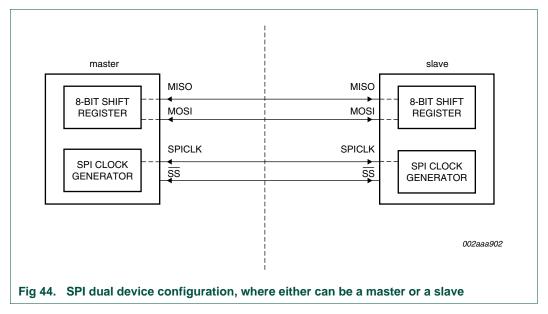

| P2.2/MOSI       | 13                 | I/O  | <b>P2.2</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | I/O  | <b>MOSI</b> — SPI master out slave in. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                         |

| P2.3/MISO       | 14                 | I/O  | <b>P2.3</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | I/O  | <b>MISO</b> — When configured as master, this pin is input, when configured as slave, this pin is output.                                                                                                                                                                                                                                                                                                  |

| P2.4/SS         | 15                 | I/O  | <b>P2.4</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | I    | SS — SPI Slave select.                                                                                                                                                                                                                                                                                                                                                                                     |

| P2.5/SPICLK     | 16                 | I/O  | <b>P2.5</b> — Port 2 bit 5.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | I/O  | <b>SPICLK</b> — SPI clock. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                     |

| P2.6/OCA        | 27                 | I/O  | <b>P2.6</b> — Port 2 bit 6.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | 0    | OCA — Output Compare A. (P89LPC9351/9361)                                                                                                                                                                                                                                                                                                                                                                  |

| P2.7/ICA        | 28                 | I/O  | <b>P2.7</b> — Port 2 bit 7.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | I    | ICA — Input Capture A. (P89LPC9351/9361)                                                                                                                                                                                                                                                                                                                                                                   |

| P3.0 to P3.1    |                    | I/O  | Port 3: Port 3 is a 2-bit I/O port with a user-configurable output type. During reset Port 3 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 3 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to <a href="Section5.1">Section5.1</a> "Port configurations" for details. |

|                 |                    |      | All pins have Schmitt trigger inputs.                                                                                                                                                                                                                                                                                                                                                                      |

|                 |                    |      | Port 3 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                         |

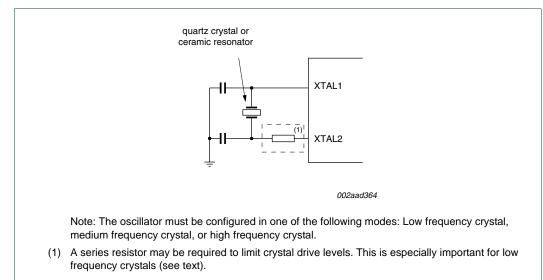

| P3.0/XTAL2/     | 9                  | I/O  | <b>P3.0</b> — Port 3 bit 0.                                                                                                                                                                                                                                                                                                                                                                                |

| CLKOUT          |                    | 0    | <b>XTAL2</b> — Output from the oscillator amplifier (when a crystal oscillator option is selected via the flash configuration.                                                                                                                                                                                                                                                                             |

|                 |                    | 0    | <b>CLKOUT</b> — CPU clock divided by 2 when enabled via SFR bit (ENCLK -TRIM.6). It can be used if the CPU clock is the internal RC oscillator, watchdog oscillator or external clock input, except when XTAL1/XTAL2 are used to generate clock source for the RTC/system timer.                                                                                                                           |

| P3.1/XTAL1      | 8                  | I/O  | <b>P3.1</b> — Port 3 bit 1.                                                                                                                                                                                                                                                                                                                                                                                |

|                 |                    | I    | <b>XTAL1</b> — Input to the oscillator circuit and internal clock generator circuits (when selected via the flash configuration). It can be a port pin if internal RC oscillator or watchdog oscillator is used as the CPU clock source, <b>and</b> if XTAL1/XTAL2 are not used to generate the clock for the RTC/system timer.                                                                            |

| V <sub>SS</sub> | 7                  | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                     |

| $V_{DD}$        | 21                 | I    | <b>Power supply:</b> This is the power supply voltage for normal operation as well as Idle and Power-down modes.                                                                                                                                                                                                                                                                                           |

<sup>[1]</sup> Input/output for P1.0 to P1.4, P1.6, P1.7. Input for P1.5.

### P89LPC9331/9341/9351/9361 User manual

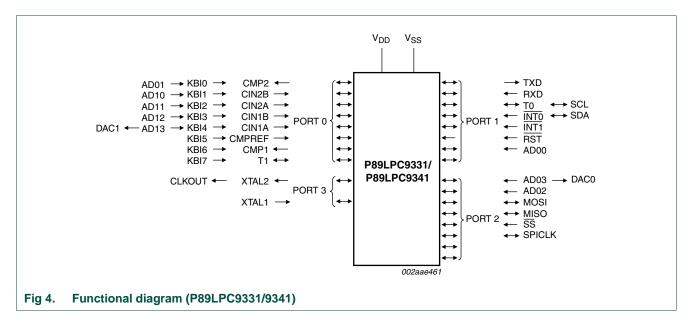

# 1.3 Functional diagram

### P89LPC9331/9341/9351/9361 User manual

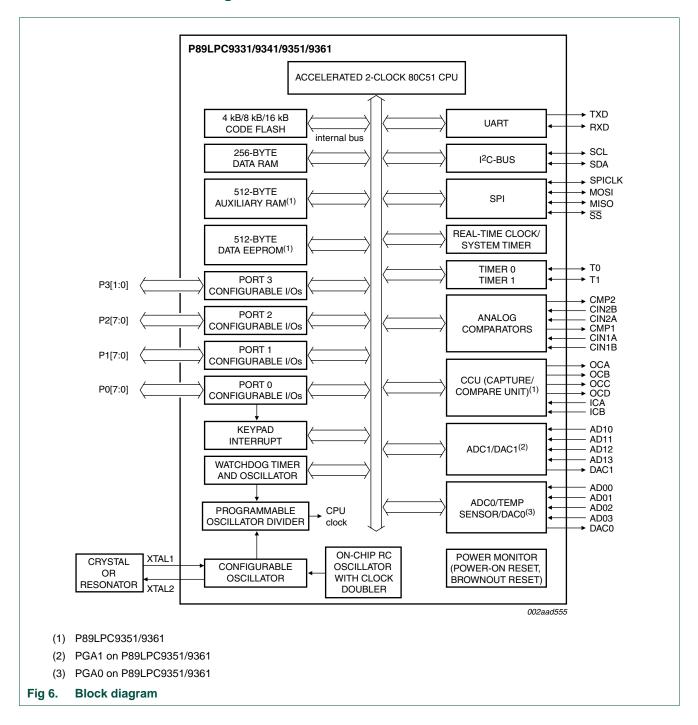

# 1.4 Block diagram

### P89LPC9331/9341/9351/9361 User manual

# 1.5 Special function registers

Remark: SFR accesses are restricted in the following ways:

- User must **not** attempt to access any SFR locations not defined.

- Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

- SFR bits labeled '-', '0' or '1' can **only** be written and read as follows:

- '-' Unless otherwise specified, must be written with '0', but can return any value when read (even if it was written with '0'). It is a reserved bit and may be used in future derivatives.

- '0' **must** be written with '0', and will return a '0' when read.

- '1' **must** be written with '1', and will return a '1' when read.

Table 3. Special function registers - P89LPC9331/9341 \* indicates SFRs that are bit addressable.

| Name    | Description                        | SFR    | Bit function | ns and addre | sses  |        |        |        |        |        | Reset | value     |

|---------|------------------------------------|--------|--------------|--------------|-------|--------|--------|--------|--------|--------|-------|-----------|

|         |                                    | addr.  | MSB          |              |       |        |        |        |        | LSB    | Hex   | Binary    |

|         | Bit a                              | ddress | E7           | <b>E</b> 6   | E5    | E4     | E3     | E2     | E1     | E0     |       |           |

| ACC*    | Accumulator                        | E0H    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

| ADCON0  | A/D control register 0             | 8EH    | ENBI0        | ENADCI0      | TMM0  | EDGE0  | ADCI0  | ENADC0 | ADCS01 | ADCS00 | 00    | 0000 0000 |

| ADCON1  | A/D control register 1             | 97H    | ENBI1        | ENADCI1      | TMM1  | EDGE1  | ADCI1  | ENADC1 | ADCS11 | ADCS10 | 00    | 0000 0000 |

| ADINS   | A/D input<br>select                | АЗН    | ADI13        | ADI12        | ADI11 | ADI10  | ADI03  | ADI02  | ADI01  | ADI00  | 00    | 0000 0000 |

| ADMODA  | A/D mode register A                | C0H    | BNDI1        | BURST1       | SCC1  | SCAN1  | BNDI0  | BURST0 | SCC0   | SCAN0  | 00    | 0000 0000 |

| ADMODB  | A/D mode register B                | A1H    | CLK2         | CLK1         | CLK0  | INBND0 | ENDAC1 | ENDAC0 | BSA1   | BSA0   | 00    | 000x 0000 |

| AD0BH   | A/D_0<br>boundary high<br>register | BBH    |              |              |       |        |        |        |        |        | FF    | 1111 1111 |

| AD0BL   | A/D_0<br>boundary low<br>register  | A6H    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

| AD0DAT0 | A/D_0 data register 0              | C5H    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

| AD0DAT1 | A/D_0 data register 1              | C6H    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

| AD0DAT2 | A/D_0 data register 2              | C7H    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

| AD0DAT3 | A/D_0 data register 3              | F4H    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

| AD1BH   | A/D_1<br>boundary high<br>register | C4H    |              |              |       |        |        |        |        |        | FF    | 1111 1111 |

| AD1BL   | A/D_1<br>boundary low<br>register  | BCH    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

| AD1DAT0 | A/D_1 data register 0              | D5H    |              |              |       |        |        |        |        |        | 00    | 0000 0000 |

**Table 3. Special function registers - P89LPC9331/9341** ...continued \* indicates SFRs that are bit addressable.

| Name Description   | Description                           | SFR    | Bit function | s and addre | esses |      |      |     |       |       | Reset value |           |  |

|--------------------|---------------------------------------|--------|--------------|-------------|-------|------|------|-----|-------|-------|-------------|-----------|--|

|                    |                                       | addr.  | MSB          |             |       |      |      |     |       | LSB   | Hex         | Binary    |  |

| AD1DAT1            | A/D_1 data register 1                 | D6H    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| AD1DAT2            | A/D_1 data register 2                 | D7H    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| AD1DAT3            | A/D_1 data register 3                 | F5H    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| AUXR1              | Auxiliary<br>function<br>register     | A2H    | CLKLP        | EBRR        | ENT1  | ENT0 | SRST | 0   | -     | DPS   | 00          | 0000 00x0 |  |

|                    | Bit a                                 | ddress | F7           | F6          | F5    | F4   | F3   | F2  | F1    | F0    |             |           |  |

| B*                 | B register                            | F0H    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| BRGR0 <sup>2</sup> | Baud rate<br>generator 0<br>rate low  | BEH    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| BRGR1 <sup>2</sup> | Baud rate<br>generator 0<br>rate high | BFH    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| BRGCON             | Baud rate<br>generator 0<br>control   | BDH    | -            | -           | -     | -    | -    | -   | SBRGS | BRGEN | 00[2]       | xxxx xx00 |  |

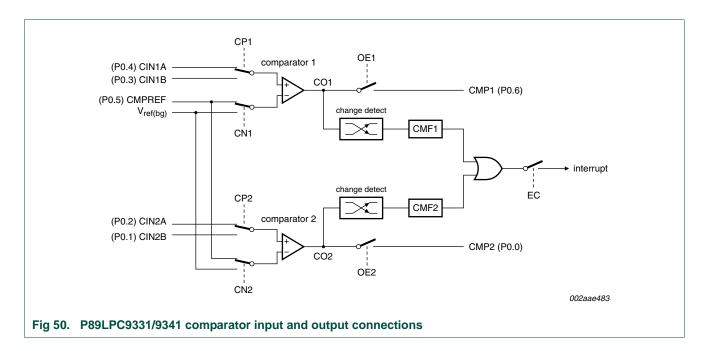

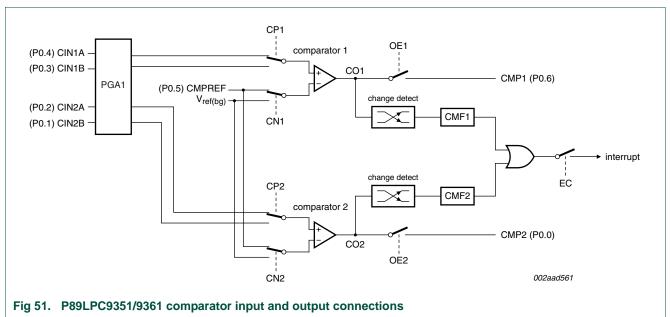

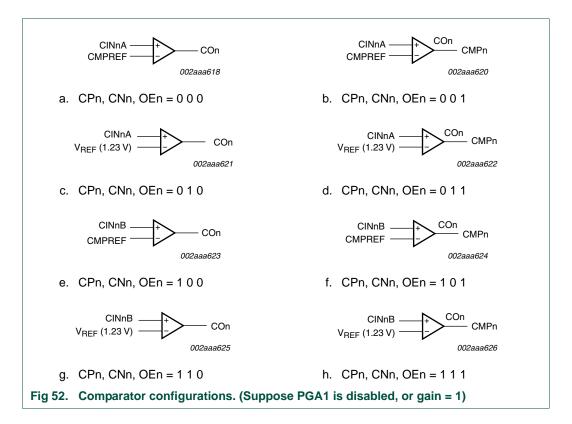

| CMP1               | Comparator 1 control register         | ACH    | -            | -           | CE1   | CP1  | CN1  | OE1 | CO1   | CMF1  | 00[1]       | xx00 0000 |  |

| CMP2               | Comparator 2 control register         | ADH    | -            | -           | CE2   | CP2  | CN2  | OE2 | CO2   | CMF2  | 00[1]       | xx00 0000 |  |

| DIVM               | CPU clock<br>divide-by-M<br>control   | 95H    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| DPTR               | Data pointer<br>(2 bytes)             |        |              |             |       |      |      |     |       |       |             |           |  |

| DPH                | Data pointer<br>high                  | 83H    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

| DPL                | Data pointer low                      | 82H    |              |             |       |      |      |     |       |       | 00          | 0000 0000 |  |

**Table 3. Special function registers - P89LPC9331/9341** ...continued \* indicates SFRs that are bit addressable.

| Name   | Description                                                  | SFR    | Bit function | ns and addre | esses   |         |         |         |            |         | Reset | value     |

|--------|--------------------------------------------------------------|--------|--------------|--------------|---------|---------|---------|---------|------------|---------|-------|-----------|

|        |                                                              | addr.  | MSB          |              |         |         |         |         |            | LSB     | Hex   | Binary    |

| FMADRH | Program flash address high                                   | E7H    |              |              |         |         |         |         |            |         | 00    | 0000 0000 |

| FMADRL | Program flash address low                                    | E6H    |              |              |         |         |         |         |            |         | 00    | 0000 0000 |

| FMCON  | Program flash control (Read)                                 | E4H    | BUSY         | -            | -       | -       | HVA     | HVE     | SV         | OI      | 70    | 0111 0000 |

|        | Program flash control (Write)                                | E4H    | FMCMD.7      | FMCMD.6      | FMCMD.5 | FMCMD.4 | FMCMD.3 | FMCMD.2 | FMCMD.1    | FMCMD.0 |       |           |

| FMDATA | Program flash data                                           | E5H    |              |              |         |         |         |         |            |         | 00    | 0000 0000 |

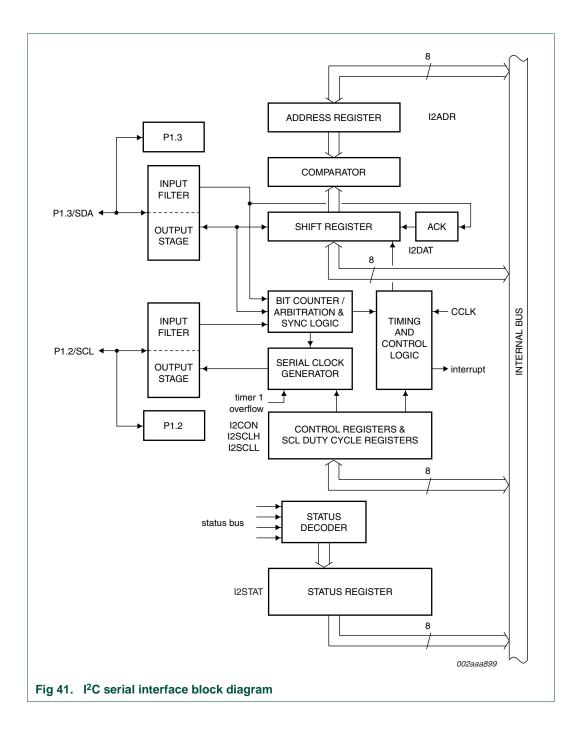

| I2ADR  | I <sup>2</sup> C-bus slave<br>address<br>register            | DBH    | I2ADR.6      | I2ADR.5      | I2ADR.4 | I2ADR.3 | I2ADR.2 | I2ADR.1 | I2ADR.0    | GC      | 00    | 0000 0000 |

|        | Bit a                                                        | ddress | DF           | DE           | DD      | DC      | DB      | DA      | D9         | D8      |       |           |

| I2CON* | I <sup>2</sup> C-bus control register                        | D8H    | -            | I2EN         | STA     | STO     | SI      | AA      | -          | CRSEL   | 00    | x000 00x0 |

| I2DAT  | I <sup>2</sup> C-bus data register                           | DAH    |              |              |         |         |         |         |            |         |       |           |

| I2SCLH | Serial clock<br>generator/SCL<br>duty cycle<br>register high | DDH    |              |              |         |         |         |         |            |         | 00    | 0000 0000 |

| I2SCLL | Serial clock<br>generator/SCL<br>duty cycle<br>register low  | DCH    |              |              |         |         |         |         |            |         | 00    | 0000 0000 |

| I2STAT | I <sup>2</sup> C-bus status register                         | D9H    | STA.4        | STA.3        | STA.2   | STA.1   | STA.0   | 0       | 0          | 0       | F8    | 1111 1000 |

|        | Bit a                                                        | ddress | AF           | AE           | AD      | AC      | AB      | AA      | A9         | A8      |       |           |

| IEN0*  | Interrupt<br>enable 0                                        | A8H    | EA           | EWDRT        | EBO     | ES/ESR  | ET1     | EX1     | ET0        | EX0     | 00    | 0000 0000 |

|        | Bit a                                                        | ddress | EF           | EE           | ED      | EC      | EB      | EA      | <b>E</b> 9 | E8      |       |           |

| IEN1*  | Interrupt<br>enable 1                                        | E8H    | EAD          | EST          | -       | -       | ESPI    | EC      | EKBI       | El2C    | 00[1] | 00x0 0000 |

**Table 3. Special function registers - P89LPC9331/9341** ...continued \* indicates SFRs that are bit addressable.

| Name   | Description                          | SFR    | Bit function | ns and addre | esses          |               |               |               |               |              | Reset      | value     |

|--------|--------------------------------------|--------|--------------|--------------|----------------|---------------|---------------|---------------|---------------|--------------|------------|-----------|

|        |                                      | addr.  | MSB          |              |                |               |               |               |               | LSB          | Hex        | Binary    |

|        | Bit a                                | ddress | BF           | BE           | BD             | ВС            | ВВ            | ВА            | В9            | B8           |            |           |

| IP0*   | Interrupt<br>priority 0              | В8Н    | -            | PWDRT        | РВО            | PS/PSR        | PT1           | PX1           | PT0           | PX0          | 00[1]      | x000 0000 |

| IP0H   | Interrupt<br>priority 0 high         | В7Н    | -            | PWDRTH       | PBOH           | PSH/<br>PSRH  | PT1H          | PX1H          | PT0H          | PX0H         | 00[1]      | x000 0000 |

|        | Bit a                                | ddress | FF           | FE           | FD             | FC            | FB            | FA            | F9            | F8           |            |           |

| IP1*   | Interrupt<br>priority 1              | F8H    | PAD          | PST          | -              | -             | PSPI          | PC            | PKBI          | PI2C         | 00[1]      | 00x0 0000 |

| IP1H   | Interrupt<br>priority 1 high         | F7H    | PADH         | PSTH         | -              | -             | PSPIH         | PCH           | PKBIH         | PI2CH        | 00[1]      | 00x0 0000 |

| KBCON  | Keypad control register              | 94H    | -            | -            | -              | -             | -             | -             | PATN<br>_SEL  | KBIF         | 00[1]      | xxxx xx00 |

| KBMASK | Keypad<br>interrupt mask<br>register | 86H    |              |              |                |               |               |               |               |              | 00         | 0000 0000 |

| KBPATN | Keypad pattern register              | 93H    |              |              |                |               |               |               |               |              | FF         | 1111 1111 |

|        | Bit a                                | ddress | 87           | 86           | 85             | 84            | 83            | 82            | 81            | 80           |            |           |

| P0*    | Port 0                               | 80H    | T1/KB7       | CMP1<br>/KB6 | CMPREF<br>/KB5 | CIN1A<br>/KB4 | CIN1B<br>/KB3 | CIN2A<br>/KB2 | CIN2B<br>/KB1 | CMP2<br>/KB0 | [1]        |           |

|        | Bit a                                | ddress | 97           | 96           | 95             | 94            | 93            | 92            | 91            | 90           |            |           |

| P1*    | Port 1                               | 90H    | -            | -            | RST            | ĪNT1          | INT0/SDA      | T0/SCL        | RXD           | TXD          | <u>[1]</u> |           |

|        | Bit a                                | ddress | A7           | A6           | A5             | <b>A4</b>     | A3            | A2            | <b>A</b> 1    | Α0           |            |           |

| P2*    | Port 2                               | A0H    | -            | -            | SPICLK         | SS            | MISO          | MOSI          | -             | -            | <u>[1]</u> |           |

|        | Bit a                                | ddress | B7           | В6           | B5             | B4            | В3            | B2            | B1            | В0           |            |           |

| P3*    | Port 3                               | B0H    | -            | -            | -              | -             | -             | -             | XTAL1         | XTAL2        | <u>[1]</u> |           |

| P0M1   | Port 0 output<br>mode 1              | 84H    | (P0M1.7)     | (P0M1.6)     | (P0M1.5)       | (P0M1.4)      | (P0M1.3)      | (P0M1.2)      | (P0M1.1)      | (P0M1.0)     | FF[1]      | 1111 1111 |

| P0M2   | Port 0 output<br>mode 2              | 85H    | (P0M2.7)     | (P0M2.6)     | (P0M2.5)       | (P0M2.4)      | (P0M2.3)      | (P0M2.2)      | (P0M2.1)      | (P0M2.0)     | 00[1]      | 0000 0000 |

| P1M1   | Port 1 output<br>mode 1              | 91H    | (P1M1.7)     | (P1M1.6)     | -              | (P1M1.4)      | (P1M1.3)      | (P1M1.2)      | (P1M1.1)      | (P1M1.0)     | D3[1]      | 11x1 xx11 |

Table 3. Special function registers - P89LPC9331/9341 ...continued

| * indicates SFRs that are bit addr | ressable. |

|------------------------------------|-----------|

|------------------------------------|-----------|

| Name   | Description                        | SFR    |          |          |          |          |          |          |          |          | Reset value |           |  |

|--------|------------------------------------|--------|----------|----------|----------|----------|----------|----------|----------|----------|-------------|-----------|--|

|        |                                    | addr.  | MSB      |          |          |          |          |          |          | LSB      | Hex         | Binary    |  |

| P1M2   | Port 1 output mode 2               | 92H    | (P1M2.7) | (P1M2.6) | -        | (P1M2.4) | (P1M2.3) | (P1M2.2) | (P1M2.1) | (P1M2.0) | 00[1]       | 00x0 xx00 |  |

| P2M1   | Port 2 output mode 1               | A4H    | (P2M1.7) | (P2M1.6) | (P2M1.5) | (P2M1.4) | (P2M1.3) | (P2M1.2) | (P2M1.1) | (P2M1.0) | FF[1]       | 1111 1111 |  |

| P2M2   | Port 2 output mode 2               | A5H    | (P2M2.7) | (P2M2.6) | (P2M2.5) | (P2M2.4) | (P2M2.3) | (P2M2.2) | (P2M2.1) | (P2M2.0) | 00[1]       | 0000 0000 |  |

| P3M1   | Port 3 output mode 1               | В1Н    | -        | -        | -        | -        | -        | -        | (P3M1.1) | (P3M1.0) | 03[1]       | xxxx xx11 |  |

| P3M2   | Port 3 output mode 2               | В2Н    | -        | -        | -        | -        | -        | -        | (P3M2.1) | (P3M2.0) | 00[1]       | xxxx xx00 |  |

| PCON   | Power control register             | 87H    | SMOD1    | SMOD0    | -        | BOI      | GF1      | GF0      | PMOD1    | PMOD0    | 00          | 0000 000  |  |

| PCONA  | Power control register A           | В5Н    | RTCPD    | -        | VCPD     | ADPD     | I2PD     | SPPD     | SPD      | -        | 00[1]       | 0000 0000 |  |

|        | Bit a                              | ddress | D7       | D6       | D5       | D4       | D3       | D2       | D1       | D0       |             |           |  |

| PSW*   | Program status word                | D0H    | CY       | AC       | F0       | RS1      | RS0      | OV       | F1       | Р        | 00          | 0000 000  |  |

| PT0AD  | Port 0 digital input disable       | F6H    | -        | -        | PT0AD.5  | PT0AD.4  | PT0AD.3  | PT0AD.2  | PT0AD.1  | -        | 00          | xx00 000  |  |

| RSTSRC | Reset source register              | DFH    | -        | BOIF     | BOF      | POF      | R_BK     | R_WD     | R_SF     | R_EX     | [3]         |           |  |

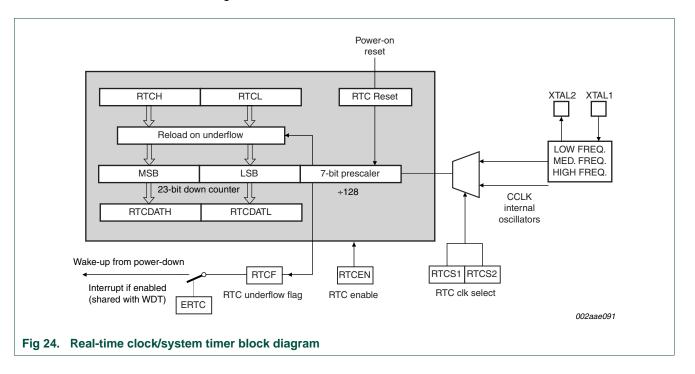

| RTCCON | RTC control                        | D1H    | RTCF     | RTCS1    | RTCS0    | -        | -        | -        | ERTC     | RTCEN    | 60[1][6]    | 011x xx0  |  |

| RTCH   | RTC register high                  | D2H    |          |          |          |          |          |          |          |          | 00[6]       | 0000 0000 |  |

| RTCL   | RTC register low                   | D3H    |          |          |          |          |          |          |          |          | 00[6]       | 0000 0000 |  |

| SADDR  | Serial port<br>address<br>register | A9H    |          |          |          |          |          |          |          |          | 00          | 0000 0000 |  |

| SADEN  | Serial port address enable         | В9Н    |          |          |          |          |          |          |          |          | 00          | 0000 000  |  |

| SBUF   | Serial Port data buffer register   | 99H    |          |          |          |          |          |          |          |          | xx          | XXXX XXX  |  |

**Table 3. Special function registers - P89LPC9331/9341** ...continued \* indicates SFRs that are bit addressable.

| Name   | Description                                | SFR    | Bit function | s and addre | esses  |        |        |        |        |        | Reset  | value     |

|--------|--------------------------------------------|--------|--------------|-------------|--------|--------|--------|--------|--------|--------|--------|-----------|

|        |                                            | addr.  | MSB          |             |        |        |        |        |        | LSB    | Hex    | Binary    |

|        | Bit a                                      | ddress | 9F           | 9E          | 9D     | 9C     | 9B     | 9A     | 99     | 98     |        |           |

| SCON*  | Serial port control                        | 98H    | SM0/FE       | SM1         | SM2    | REN    | TB8    | RB8    | TI     | RI     | 00     | 0000 0000 |

| SSTAT  | Serial port<br>extended<br>status register | BAH    | DBMOD        | INTLO       | CIDIS  | DBISEL | FE     | BR     | OE     | STINT  | 00     | 0000 0000 |

| SP     | Stack pointer                              | 81H    |              |             |        |        |        |        |        |        | 07     | 0000 0111 |

| SPCTL  | SPI control register                       | E2H    | SSIG         | SPEN        | DORD   | MSTR   | CPOL   | CPHA   | SPR1   | SPR0   | 04     | 0000 0100 |

| SPSTAT | SPI status register                        | E1H    | SPIF         | WCOL        | -      | -      | -      | -      | -      | -      | 00     | 00xx xxxx |

| SPDAT  | SPI data register                          | ЕЗН    |              |             |        |        |        |        |        |        | 00     | 0000 0000 |

| TAMOD  | Timer 0 and 1 auxiliary mode               | 8FH    | -            | -           | -      | T1M2   | -      | -      | -      | T0M2   | 00     | xxx0 xxx0 |

|        | Bit a                                      | ddress | 8F           | 8E          | 8D     | 8C     | 8B     | 8A     | 89     | 88     |        |           |

| TCON*  | Timer 0 and 1 control                      | 88H    | TF1          | TR1         | TF0    | TR0    | IE1    | IT1    | IE0    | IT0    | 00     | 0000 0000 |

| TH0    | Timer 0 high                               | 8CH    |              |             |        |        |        |        |        |        | 00     | 0000 0000 |

| TH1    | Timer 1 high                               | 8DH    |              |             |        |        |        |        |        |        | 00     | 0000 0000 |

| TL0    | Timer 0 low                                | 8AH    |              |             |        |        |        |        |        |        | 00     | 0000 0000 |

| TL1    | Timer 1 low                                | 8BH    |              |             |        |        |        |        |        |        | 00     | 0000 0000 |

| TMOD   | Timer 0 and 1 mode                         | 89H    | T1GATE       | T1C/T       | T1M1   | T1M0   | T0GATE | T0C/T  | T0M1   | T0M0   | 00     | 0000 0000 |

| TRIM   | Internal<br>oscillator trim<br>register    | 96H    | RCCLK        | ENCLK       | TRIM.5 | TRIM.4 | TRIM.3 | TRIM.2 | TRIM.1 | TRIM.0 | [5][6] |           |

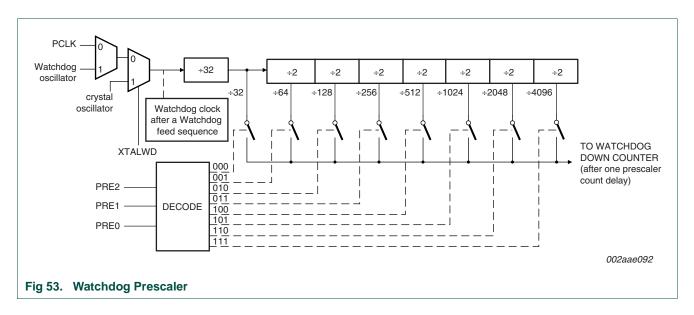

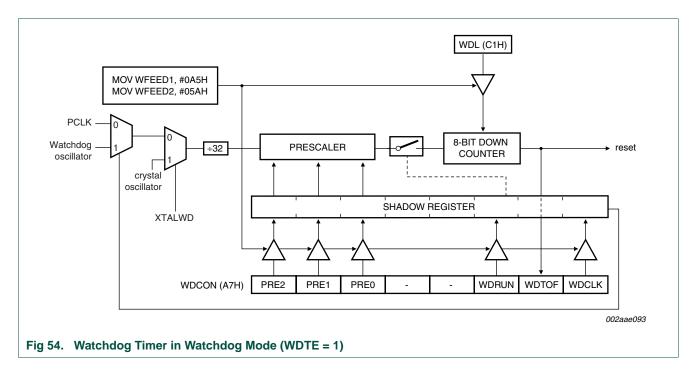

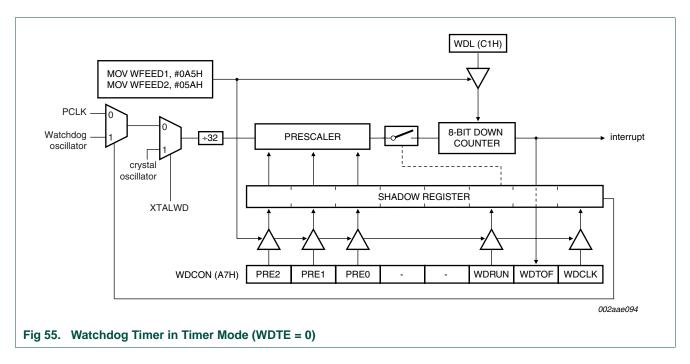

| WDCON  | Watchdog control register                  | А7Н    | PRE2         | PRE1        | PRE0   | -      | -      | WDRUN  | WDTOF  | WDCLK  | [4][6] |           |

Table 3. Special function registers - P89LPC9331/9341 ...continued

\* indicates SFRs that are bit addressable.

| Name   | Description        | _     | Bit functions and addresses | Reset value |           |  |

|--------|--------------------|-------|-----------------------------|-------------|-----------|--|

|        |                    | addr. | MSB                         | Hex         | Binary    |  |

| WDL    | Watchdog load      | C1H   |                             | FF          | 1111 1111 |  |

| WFEED1 | Watchdog<br>feed 1 | C2H   |                             |             |           |  |

| WFEED2 | Watchdog<br>feed 2 | СЗН   |                             |             |           |  |

- [1] All ports are in input only (high-impedance) state after power-up.

- BRGR1 and BRGR0 must only be written if BRGEN in BRGCON SFR is logic 0. If any are written while BRGEN = 1, the result is unpredictable.

- The RSTSRC register reflects the cause of the P89LPC9331/9341 reset except BOIF bit. Upon a power-up reset, all reset source flags are cleared except POF and BOF; the power-on reset value is x011 0000.

- [4] After reset, the value is 1110 01x1, i.e., PRE2 to PRE0 are all logic 1, WDRUN = 1 and WDCLK = 1. WDTOF bit is logic 1 after watchdog reset and is logic 0 after power-on reset. Other resets will not affect WDTOF.

- On power-on reset and watchdog reset, the TRIM SFR is initialized with a factory preprogrammed value. Other resets will not cause initialization of the TRIM register.

- The only reset sources that affect these SFRs are power-on reset and watchdog reset.

| Table 4. | Extended special function registers - P89LPC9331/93 | 341 <u>[1]</u> |

|----------|-----------------------------------------------------|----------------|

|----------|-----------------------------------------------------|----------------|

| Name    | Description                               | SFR   | Bit function | ns and addres | sses |        |        |       |         |         | Rese | t value   |

|---------|-------------------------------------------|-------|--------------|---------------|------|--------|--------|-------|---------|---------|------|-----------|

|         |                                           | addr. | MSB          |               |      |        |        |       |         | LSB     | Hex  | Binary    |

| BODCFG  | BOD<br>configuration<br>register          | FFC8H | -            | -             | -    | -      | -      | -     | BOICFG1 | BOICFG0 | [2]  |           |

| CLKCON  | CLOCK Control register                    | FFDEH | CLKOK        | -             | -    | XTALWD | CLKDBL | FOSC2 | FOSC1   | FOSC0   | [3]  |           |

| TPSCON  | Temperature<br>sensor control<br>register | FFCAH | -            | -             | -    | -      | TSEL1  | TSEL0 | -       | -       | 00   | 0000 0000 |

| RTCDATH | Real-time clock<br>data register<br>high  | FFBFH |              |               |      |        |        |       |         |         | 00   | 0000 0000 |

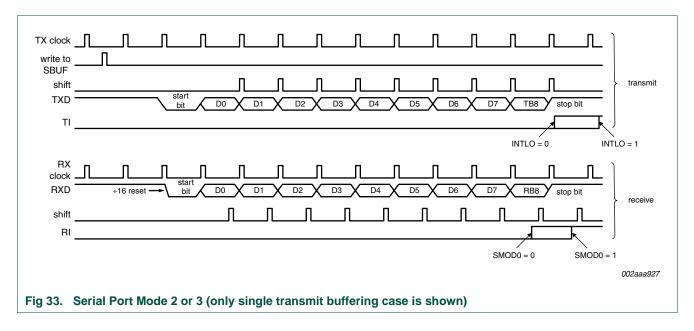

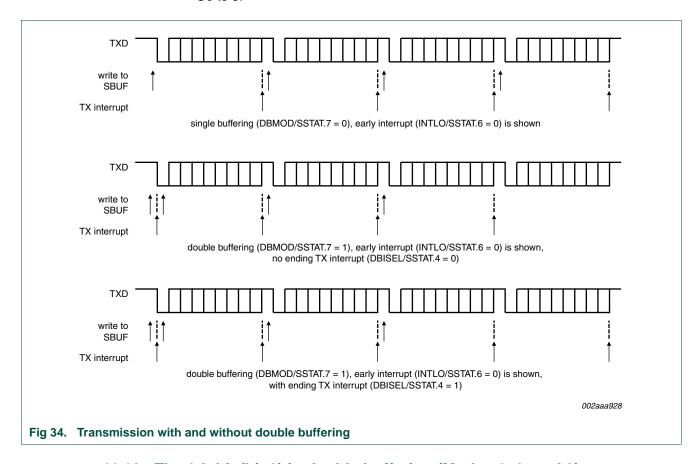

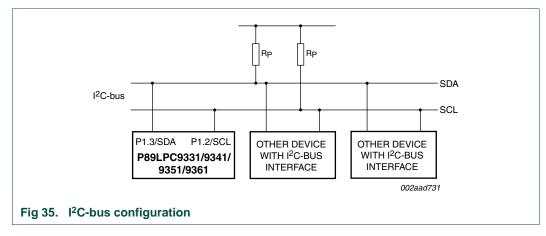

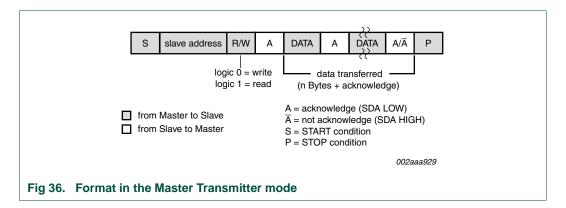

| RTCDATL | Real-time clock data register low         | FFBEH |              |               |      |        |        |       |         |         | 00   | 0000 0000 |