## **S3FM02G**

## 32-Bit CMOS MICROCONTROLLERS

Revision 1.00 January 2011

## User's Manual

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

© 2010 Samsung Electronics Co., Ltd. All rights reserved.

### **Important Notice**

The information in this publication has been carefully checked and is believed to be entirely accurate at the time of publication. Samsung assumes no responsibility, however, for possible errors or omissions, or for any consequences resulting from the use of the information contained herein.

Samsung reserves the right to make changes in its products or product specifications with the intent to improve function or design at any time and without notice and is not required to update this documentation to reflect such changes.

This publication does not convey to a purchaser of semiconductor devices described herein any license under the patent rights of Samsung or others.

Samsung makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Samsung assume any liability arising out of the application or use of any product or circuit and specifically disclaims any and all liability, including without limitation any consequential or incidental damages.

"Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by the customer's technical experts.

Samsung products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, for other applications intended to support or sustain life, or for any other application in which the failure of the Samsung product could create a situation where personal injury or death may occur.

Should the Buyer purchase or use a Samsung product for any such unintended or unauthorized application, the Buyer shall indemnify and hold Samsung and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, expenses, and reasonable attorney fees arising out of, either directly or indirectly, any claim of personal injury or death that may be associated with such unintended or unauthorized use, even if such claim alleges that Samsung was negligent regarding the design or manufacture of said product.

#### Copyright © 2010 Samsung Electronics Co., Ltd.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric or mechanical, by photocopying, recording, or otherwise, without the prior written consent of Samsung Electronics.

Samsung Electronics Co., Ltd. San #24 Nongseo-Dong, Giheung-Gu Yongin-City, Gyeonggi-Do, Korea 446-711

Contact Us: prodakim @samsung.com

TEL: (82)-(31)-209-4956 FAX: (82)-(31)-209-6494

Home Page: http://www.samsungsemi.com

## **Revision History**

| Revision No. | Date          | Description | Author(s) |

|--------------|---------------|-------------|-----------|

| 1.00         | Jan. 10, 2011 | •           | Juil. Kim |

## **Table of Contents**

| 1 | OVERVIEW                                       | <b>1-</b> 1     |

|---|------------------------------------------------|-----------------|

|   | 1.1 Purpose This Document                      | 1               |

|   | 1.2 Instruction to S3FM02G                     | 1-              |

|   | 1.3 Features                                   |                 |

|   | 1.4 Block Diagram                              | 1-6             |

| 2 | PIN CONFIGURATION                              | 2-1             |

|   | 2.1 Pin Configuration                          | 2- <sup>-</sup> |

|   | 2.2 Pin Assignments                            | 2-2             |

|   | 2.3 Pin Description                            |                 |

|   | 2.3.1 Miscellaneous                            |                 |

|   | 2.3.2 Clock Manager                            |                 |

|   | 2.3.3 External Interrupt                       |                 |

|   | 2.3.4 DEBUG Interface                          |                 |

|   | 2.3.6 Encoder Interface                        |                 |

|   | 2.3.7 IMC Interface                            |                 |

|   | 2.3.8 TIMER Interface                          |                 |

|   | 2.3.9 PWM Interface                            | 2-7             |

|   | 2.3.10 I2C Interface                           | 2-7             |

|   | 2.3.11 CAN Interface                           |                 |

|   | 2.3.12 SSP Interface                           |                 |

|   | 2.3.13 LCD Controller Interface                |                 |

|   | 2.3.14 ADC Interface                           |                 |

|   | 2.3.16 GPIOs                                   |                 |

|   | 2.3.17 FLASH                                   |                 |

|   | 2.3.18 Power                                   |                 |

| 3 | SYSTEM MEMORY MANAGEMENT                       | 3-1             |

|   | 3.1 Default Memory Map                         |                 |

|   | 3.2 Special Function Register Map              |                 |

|   | 3.2.1 Core Special Function Register Map       |                 |

|   | 3.2.2 Peripheral Special Function Register Map |                 |

| 4 | ANALOG TO DIGITAL CONVERTER (ADC0)             | <b>4-</b> 1     |

|   | 4.1 Overview                                   | 4               |

|   | 4.1.1 Features.                                |                 |

|   | 4.1.2 Pin Description                          |                 |

|   | 4.1.3 Block Diagram                            |                 |

|   | 4.2 General Operation                          |                 |

|   | 4.2.1 ADC Input and Output                     |                 |

|   | 4.2.2 Analog Cell Clock Frequency              |                 |

|   | 4.2.3 Conversion Sequence Definition           |                 |

|   | 4.2.4 One-shot and Continuous Mode             |                 |

|   | 4.2.5 Conversion Start Sources                 | 4-5             |

|   | 4.2.6 Power Management                  | 4-5  |

|---|-----------------------------------------|------|

|   | 4.2.7 Flags and Interrupt               | 4-6  |

|   | 4.2.8 Software Sequence for Conversion  | 4-7  |

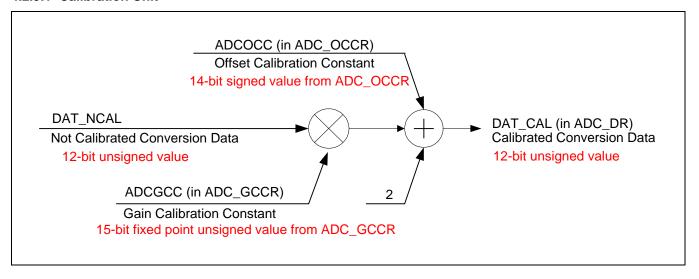

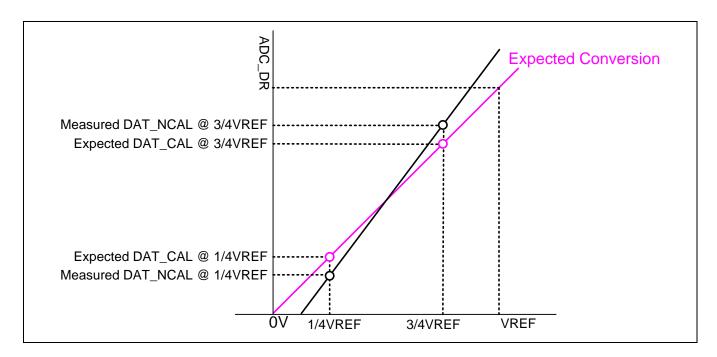

|   | 4.2.9 Calibration                       |      |

|   | 4.2.10 Operation Sequence               |      |

|   | 4.3 Register Description                |      |

|   | 4.3.1 Register Map Summary              | 4-11 |

| 5 | ANALOG TO DIGITAL CONVERTER (ADC1)      | 5-1  |

|   | 5.1 Overview                            | 5-1  |

|   | 5.1.1 Features                          | 5-1  |

|   | 5.1.2 Pin Description                   | 5-1  |

|   | 5.1.3 Block Diagram                     | 5-2  |

|   | 5.2 General Operation                   | 5-3  |

|   | 5.2.1 ADC Input and Output              | 5-3  |

|   | 5.2.2 Analog Cell Clock Frequency       | 5-3  |

|   | 5.2.3 Conversion Sequence Definition    | 5-4  |

|   | 5.2.4 One-shot and Continuous Mode      |      |

|   | 5.2.5 Conversion Start Sources          |      |

|   | 5.2.6 Power Management                  |      |

|   | 5.2.7 Flags and Interrupt               |      |

|   | 5.2.8 Software Sequence for Conversion  |      |

|   | 5.2.9 Calibration                       |      |

|   | 5.3 Register Description                |      |

|   | 5.3.1 Register Map Summary              | 5-10 |

| 6 | CONTROLLER AREA NETWORK (CAN)           | 6-1  |

|   | 6.1 Overview                            | 6-1  |

|   | 6.1.1 Features                          | 6-1  |

|   | 6.1.2 Pin Description                   | 6-2  |

|   | 6.2 Functional Description              | 6-2  |

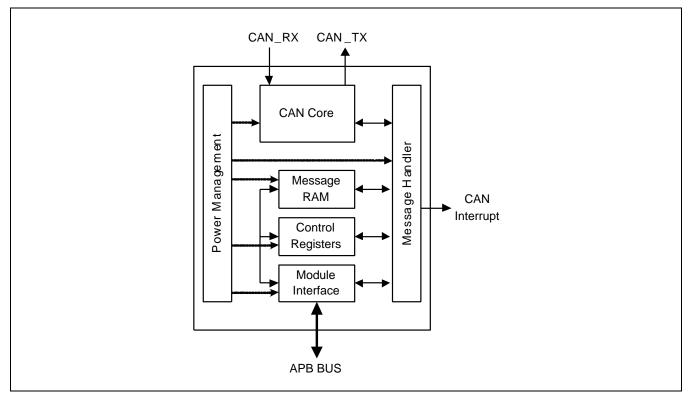

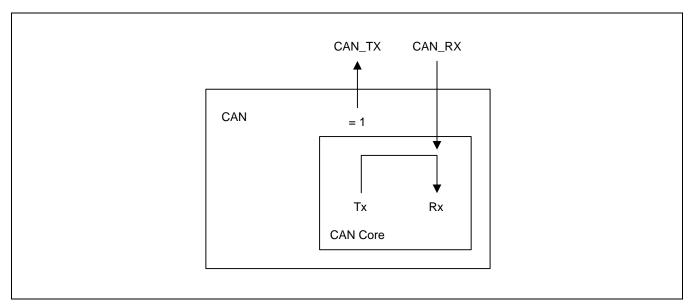

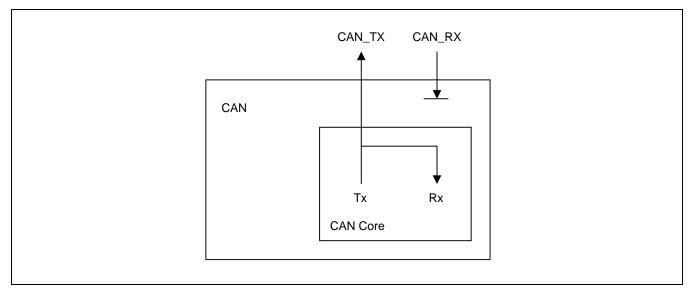

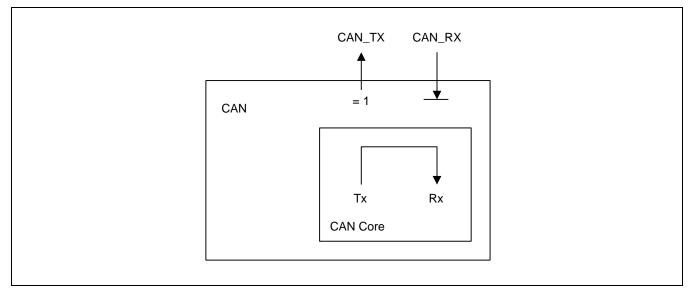

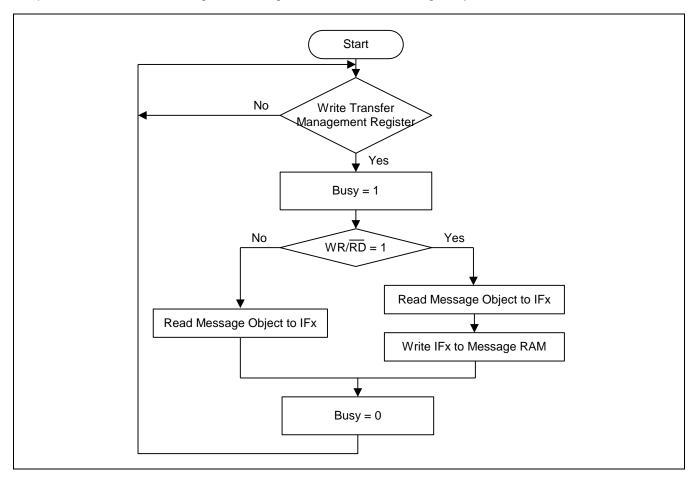

|   | 6.2.1 Block Diagram                     | 6-2  |

|   | 6.2.2 General Operation                 | 6-3  |

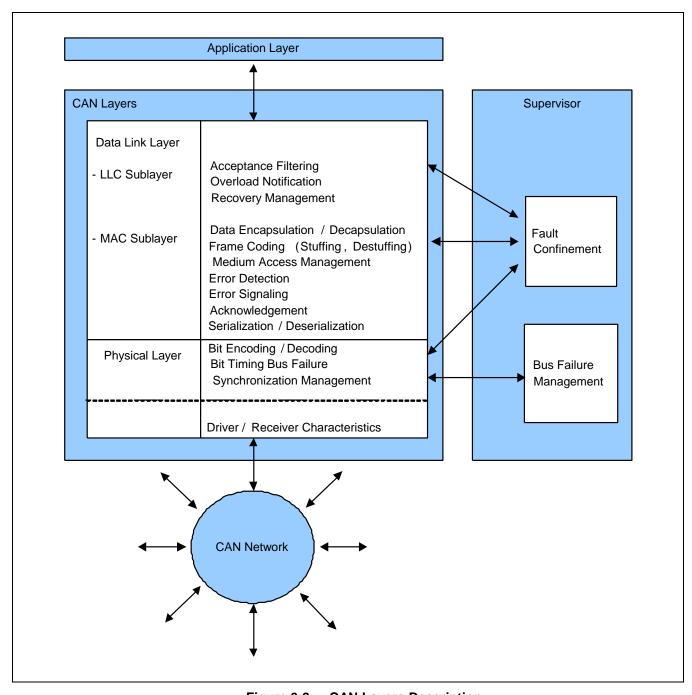

|   | 6.2.3 Basic Concepts                    |      |

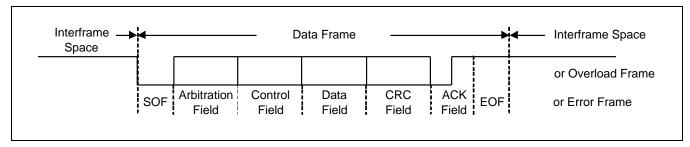

|   | 6.2.4 Message Transfer                  |      |

|   | 6.2.5 Message Filtering                 |      |

|   | 6.2.6 Message validation                |      |

|   | 6.2.7 Coding                            |      |

|   | 6.2.8 Error Handling                    |      |

|   | 6.2.9 Fault Confinement                 |      |

|   | 6.2.10 Oscillator Tolerance             |      |

|   | 6.2.11 Bit Timing Requirements          |      |

|   | 6.2.12 Hard Synchronization             |      |

|   | 6.3 Operating Modes                     |      |

|   | 6.3.1 Software Initialization           |      |

|   | 6.3.2 CAN Message Transfer              |      |

|   | 6.3.3 Message Interface Register Sets   |      |

|   | 6.3.4 Message Object                    | 6-32 |

|   | 6.3.5 Disabled Automatic Retransmission |      |

|   | 6.3.6 Test Mode                         | 6.22 |

|   |                                         |      |

|   | 6.3.7 Silent Mode                       | 6-33 |

|   | 6.3.9 Loop Back Mode Combined With Silent Mode    | 6-35        |

|---|---------------------------------------------------|-------------|

|   | 6.3.10 Basic Mode                                 | 6-36        |

|   | 6.3.11 Control of pin CAN_TX                      | 6-37        |

|   | 6.3.12 Bus off Recovery Sequence                  | 6-37        |

|   | 6.4 CAN Application                               | 6-38        |

|   | 6.4.1 Management of Message Objects               |             |

|   | 6.4.2 Message Handler State Machine               | 6-38        |

|   | 6.4.3 Configuration of a Transmit Object          | 6-42        |

|   | 6.4.4 Updating a Transmit Object                  | 6-42        |

|   | 6.4.5 Configuration of a Receive Object           |             |

|   | 6.4.6 Handling of Received Message                |             |

|   | 6.4.7 Configuration of a FIFO Buffer              |             |

|   | 6.4.8 Reception of messages with FIFO Buffers     |             |

|   | 6.4.9 Handling of Interrupts                      |             |

|   | 6.4.10 Configuration of the bit Timing            |             |

|   | 6.5 Register Description                          |             |

|   | 6.5.1 Register Map Summary                        | 6-57        |

| 7 | CLOCK & POWER MANAGER                             | <b>7-</b> 1 |

|   | 7.1 Overview                                      | 7-          |

|   | 7.1.1 Features                                    | 7-2         |

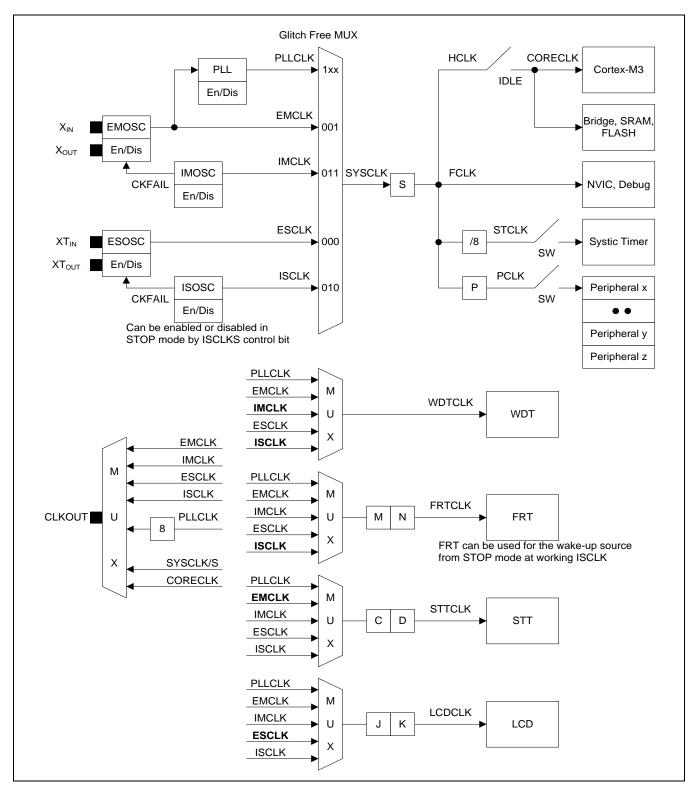

|   | 7.2 Clock Management                              |             |

|   | 7.2.1 SYSCLK and Flash Smart Option               |             |

|   | 7.2.2 Clock Control State Machine                 |             |

|   | 7.2.3 EMCLK                                       | 7-7         |

|   | 7.2.4 ESCLK                                       | 7-8         |

|   | 7.2.5 IMCLK                                       | 7-8         |

|   | 7.2.6 ISCLK                                       | 7-9         |

|   | 7.2.7 PLL (Phase Locked Loop)                     |             |

|   | 7.2.8 SYSCLK Source Clock Selection               |             |

|   | 7.2.9 Clock Monitor                               |             |

|   | 7.3 Power Management                              |             |

|   | 7.3.1 Power Modes                                 |             |

|   | 7.3.2 Low Power Mode and Wake-Up                  |             |

|   | 7.4 Reset Management                              |             |

|   | 7.4.1 Pin Reset (NRST)                            |             |

|   | 7.4.2 Power-on Reset (PORST)                      |             |

|   | 7.4.3 LVD Reset (LVDRST)                          |             |

|   | 7.4.4 External Main Clock Monitor Reset (EMCMRST) |             |

|   | 7.4.5 External Sub Clock Monitor Reset (ESCMRST)  |             |

|   | 7.4.6 Watchdog Reset (WDTRST)                     |             |

|   | 7.4.7 Software Reset (SWRST)                      |             |

|   | 7.4.8 CPU Request Reset (SYSRST)                  |             |

|   | 7.5 Basic Timer                                   |             |

|   |                                                   |             |

|   | 7.6 Register Description                          |             |

| 8 | DATA FLASH CONTROLLER                             |             |

| U |                                                   |             |

|   | 8.1 Overview                                      |             |

|   | 8.1.1 Features                                    |             |

|   | 8.2 Functional Description                        | Χ₌:         |

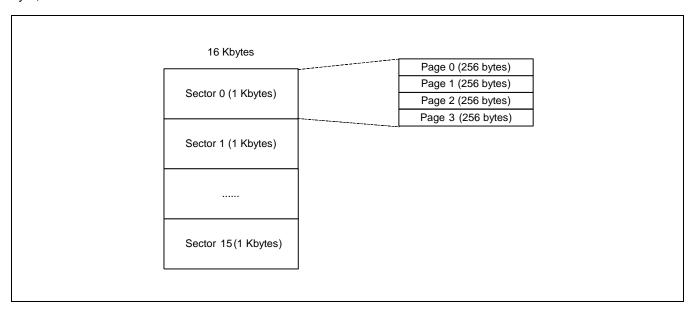

|     | 8.2.1 Organization                    | 8-3  |

|-----|---------------------------------------|------|

|     | 8.2.2 Operation                       | 8-4  |

|     | 8.2.3 Data Protection                 |      |

|     | 8.3 Register Description              |      |

|     | 8.3.1 Register Map Summary            | 8-9  |

| 9   | DIRECT MEMORY ACCESS (DMA) CONTROLLER | 9-1  |

|     | 9.1 Overview                          |      |

|     | 9.2 Functional Description            |      |

|     | 9.2.1 Block Diagram                   |      |

|     | 9.2.2 General Operation               |      |

|     | 9.2.3 Operation Mode                  |      |

|     | 9.2.4 Data Transfer Size              |      |

|     | 9.2.6 Operation Sequence              |      |

|     | 9.3 Register Description              |      |

|     | 9.3.1 Register Map Summary            |      |

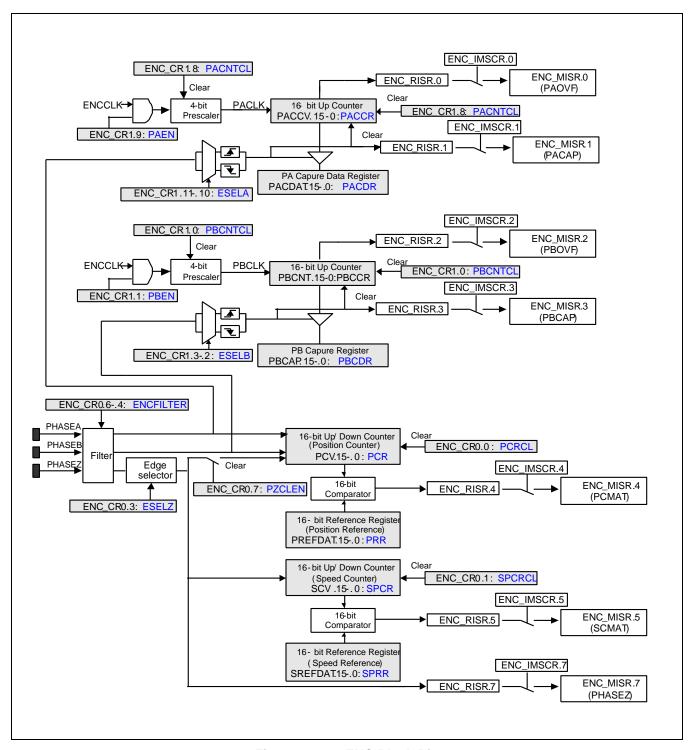

| 10  | ENCODER COUNTER                       | 10-1 |

| . • | 10.1 Overview                         |      |

|     | 10.1.1 Features                       |      |

|     | 10.1.2 Pin Description                |      |

|     | 10.2 Functional Description           |      |

|     | 10.2.1 Block Diagram                  |      |

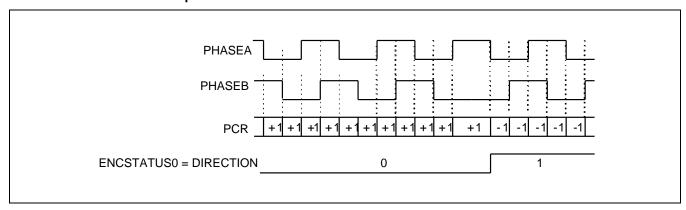

|     | 10.2.2 Operation                      | 10-3 |

|     | 10.3 Register Description             | 10-4 |

|     | 10.3.1 Register Map Summary           | 10-4 |

| 11  | I FREE RUNNING TIMER                  | 11-1 |

|     | 11.1 Overview                         | 11-1 |

|     | 11.1.1 Features                       |      |

|     | 11.2 Functional Description           |      |

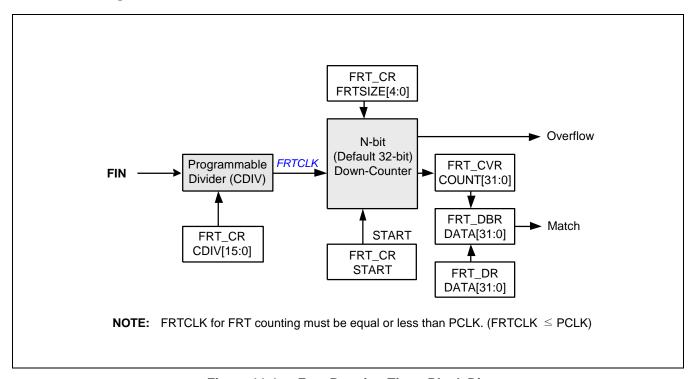

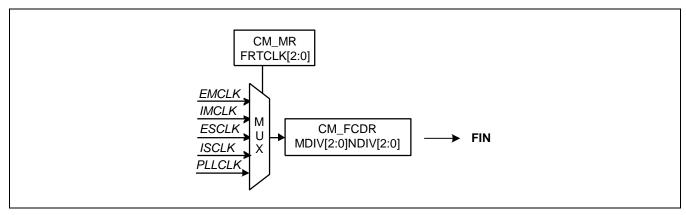

|     | 11.2.1 Block Diagram                  |      |

|     | 11.2.2 Timer Count Size               |      |

|     | 11.2.3 Timer Clock                    |      |

|     | 11.2.4 Count and Data Register        |      |

|     | 11.2.5 Interrupt                      |      |

|     | 11.3.1 Register Map Summary           |      |

| 12  | 2 GENERAL PURPOSE IO (GPIO)           | 12-1 |

| 12  | 12.1 Overview                         |      |

|     | 12.1.1 Features                       |      |

|     | 12.1.2 Pin Description                |      |

|     | 12.2 Functional Description           |      |

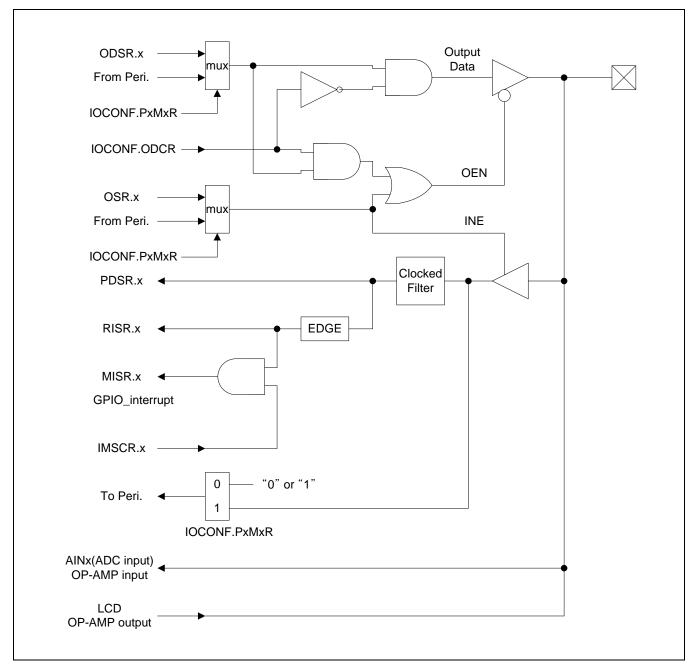

|     | 12.2.1 Block Diagram                  |      |

|     | 12.2.2 Operation                      |      |

|     | 12.2.3 Operation Mode                 |      |

|     | 12.2.4 Interrupt                      | 12-5 |

|     | 12.3 Register Description             |      |

|     | 12.3.1 Register Map Summary           | 12-6 |

| 13 INTER-INTEGRATED CIRCUIT (IIC)                | 13-1 |

|--------------------------------------------------|------|

| 13.1 Overview                                    | 13-1 |

| 13.1.1 Features                                  |      |

| 13.1.2 Pin Description                           |      |

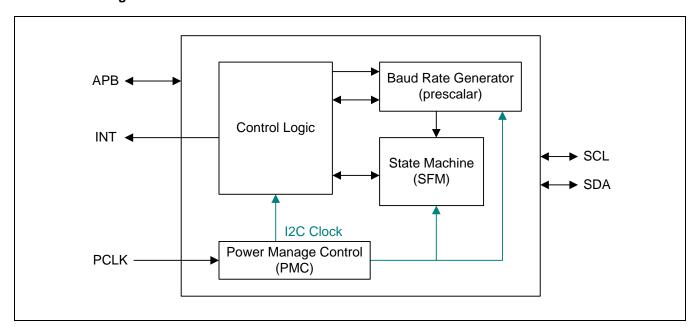

| 13.2 Functional Description                      |      |

| 13.2.1 Block Diagram                             |      |

| 13.2.2 Functional Operation                      |      |

| 13.2.3 Extensions to the I2C-bus Specification   |      |

| 13.2.4 1 Fast Mode                               |      |

| 13.3 Inter-Integrated Circuit Timing             |      |

| 13.4 Register Description                        |      |

| 13.4.1 Register Map Summary                      |      |

| 14 INVERTER MOTOR CONTROLLER (IMC)               | 14-1 |

| 14.1 Overview                                    |      |

| 14.1.1 Features                                  |      |

| 14.1.2 Pin Description                           |      |

| 14.2 Functional Description                      |      |

| 14.2.1 Block Diagram                             |      |

| 14.2.2 Operation                                 |      |

| 14.2.3 Phase Signal Generation                   |      |

| 14.3 Register Description                        |      |

| 14.3.1 Register Map Summary                      |      |

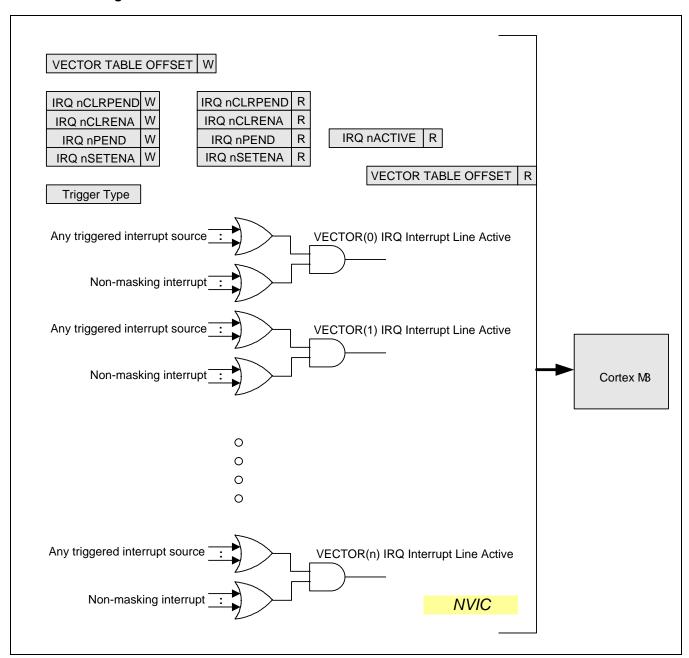

| 15 INTERRUPT CONTROLLER                          | 15-1 |

| 15.1 Overview                                    | 15-1 |

| 15.1.1 Features                                  | 15-1 |

| 15.2 Functional Description                      | 15-2 |

| 15.2.1 Block Diagram                             |      |

| 15.2.2 Interrupt Sources & Vectors               |      |

| 15.2.3 System Interrupt Vector                   |      |

| 16 I/O CONFIGURATION (IOCONF)                    | 16-1 |

| 16.1 Overview                                    | 16-1 |

| 16.1.1 Features                                  |      |

| 16.2 Functional Description                      |      |

| 16.2.1 General Description                       |      |

| 16.2.2 Peripheral Configuration                  |      |

| 16.3 Register Description                        |      |

| 16.3.1 Register Map Summary                      | 16-6 |

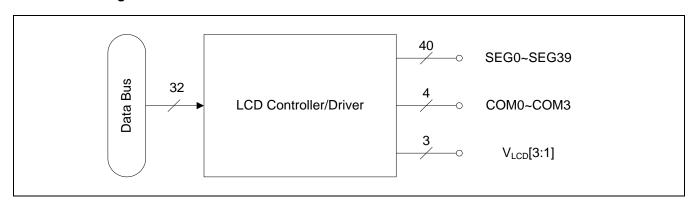

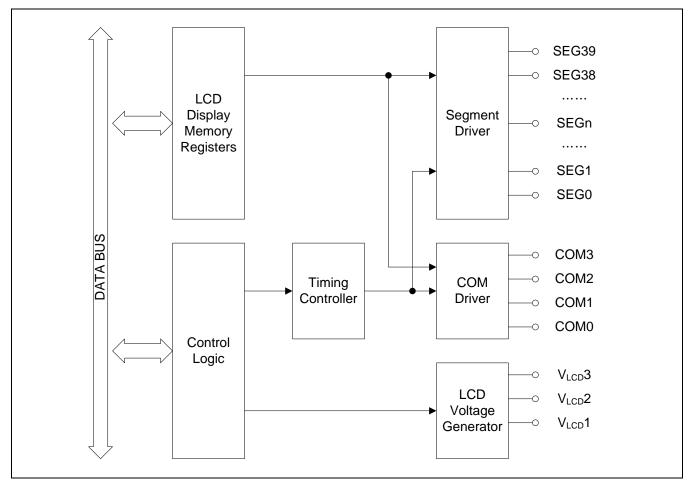

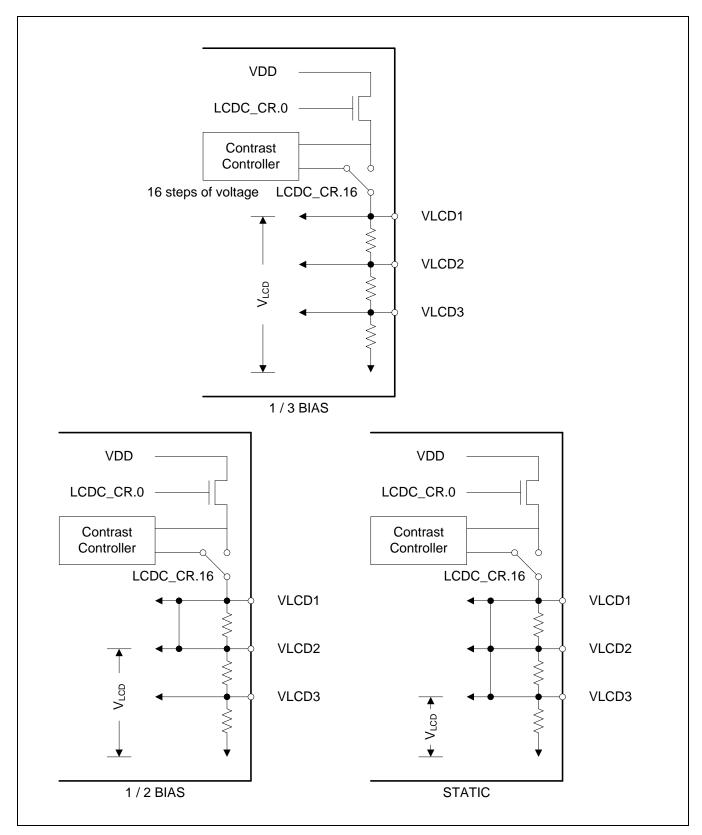

| 17 LCD CONTROLLER                                | 17-1 |

| 17.1 Overview                                    |      |

| 17.1.1 Features                                  |      |

| 17.1.2 Pin Description                           |      |

| 17.2 Functional Description                      |      |

| 17.2.1 Block Diagram                             |      |

| 17.2.2 LCD Display Memory                        |      |

| 17.2.3 LCD Clock Generator and Timing Controller |      |

| 17.2.4 LCD Voltage Driving Method                | 17-4 |

| 17.2.5 LCD Output Signal Waveform    |       |

|--------------------------------------|-------|

| 17.3 Register Description            |       |

| 17.3.1 Register Map Summary          |       |

| 18 OPERATIONAL AMPLIFIER (OPAMP)     | 18-1  |

| 18.1 Overview                        |       |

| 18.1.1 Features                      | 18-1  |

| 18.1.2 Pin Description               |       |

| 18.2 Functional Description          |       |

| 18.2.1 Block Diagram                 |       |

| 18.2.2 Gain Generation Circuit       |       |

| 18.2.3 Edge Detection circuit        |       |

| 18.3 Register Description            |       |

| 18.3.1 Register Map Summary          |       |

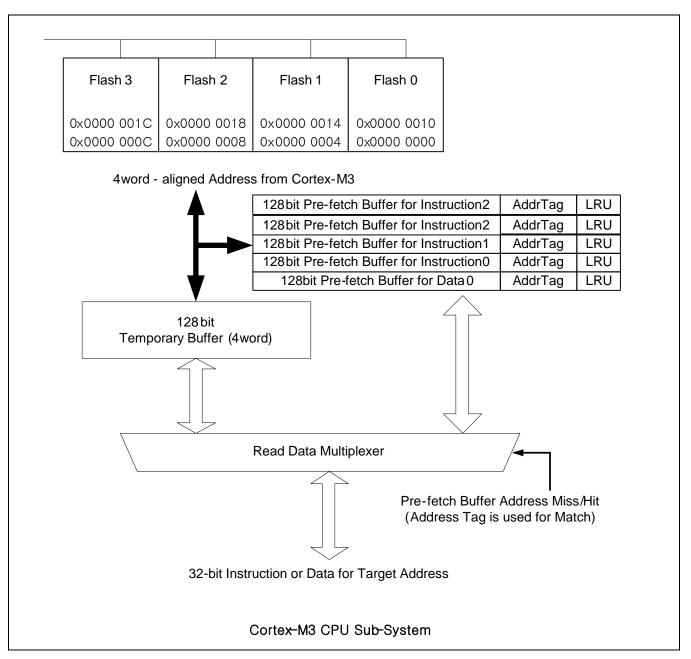

| 19 PROGRAM FLASH CONTROLLER          | 19-1  |

| 19.1 Overview                        |       |

| 19.1.1 Features                      |       |

| 19.2 Functional Description          |       |

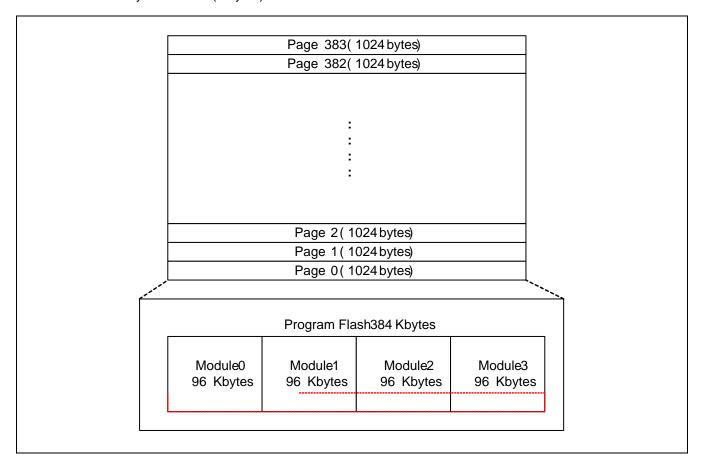

| 19.2.1 Organization                  |       |

| 19.2.2 Smart Option                  |       |

| 19.2.3 Programming Method            | 19-8  |

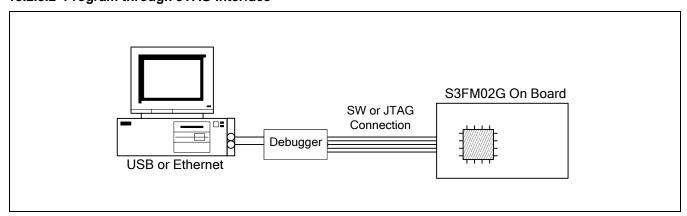

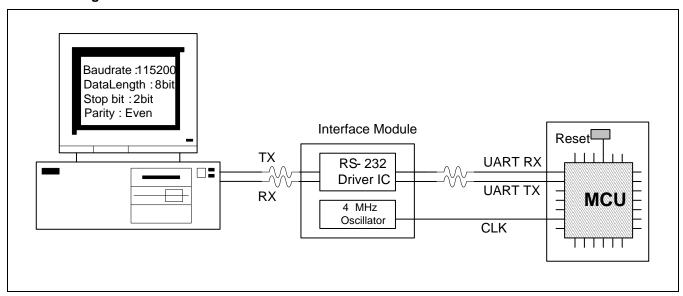

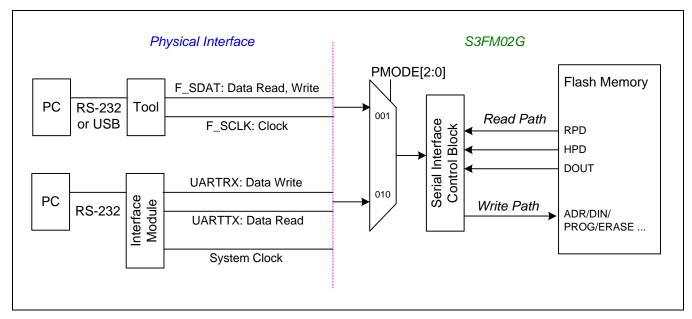

| 19.3 Tool Program Mode               |       |

| 19.3.1 Tool Information              |       |

| 19.3.2 Operation                     |       |

| 19.4 Register Description            |       |

| 19.4.1 Register Map Summary          |       |

| 20 PULSE WIDTH MODULATION (PWM)      | 20-1  |

| 20.1 Overview                        | 20-1  |

| 20.1.1 Features                      |       |

| 20.1.2 Pin Description               |       |

| 20.2 Functional Description          |       |

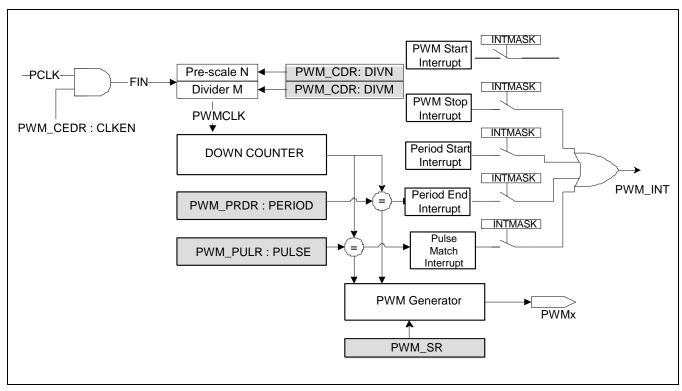

| 20.2.1 Block Diagram                 | 20-2  |

| 20.2.2 General Description           |       |

| 20.2.3 Clock and Operation Frequency |       |

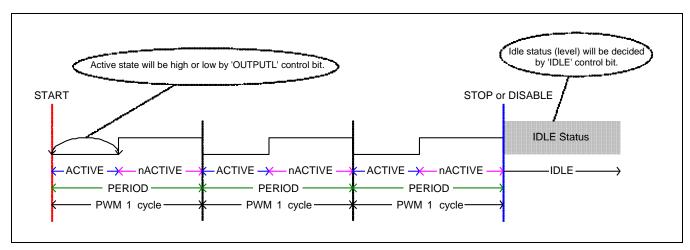

| 20.2.4 Period                        | 20-4  |

| 20.2.5 Active Level                  | 20-4  |

| 20.2.6 nActive Witdh                 | 20-4  |

| 20.2.7 Idle Level                    |       |

| 20.2.8 Parameter Relationship        |       |

| 20.2.9 Extension Bit                 | 20-5  |

| 20.3 Register Description            | 20-10 |

| 20.3.1 Register Map Summary          | 20-10 |

| 21 SERIAL PERIPHERAL INTERFACE (SPI) | 21-1  |

| 21.1 Overview                        | 21-1  |

| 21.1.1 Features                      | 21-1  |

| 21.1.2 Pin Description               |       |

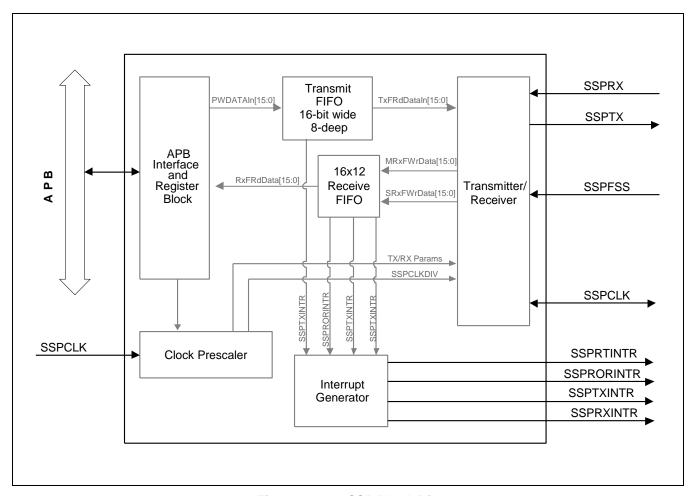

| 21.2 Functional Description          | 21-3  |

| 21.2.1 Block Diagram                 | 21-3  |

| 21.2.2 Operation                             | 21-4       |

|----------------------------------------------|------------|

| 21.3 Register Description                    |            |

| 21.3.1 Register Map Summary                  |            |

| 22 STAMP TIMER (STT)                         | 22-1       |

| 22.1 Overview                                | 22-1       |

| 22.1.1 Features                              |            |

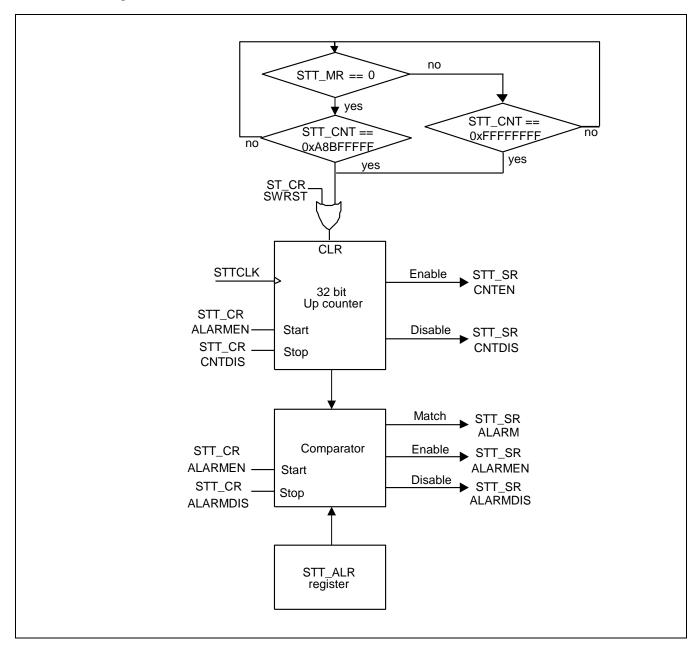

| 22.2 Functional Description                  |            |

| 22.2.1 Block Diagram                         |            |

| 22.2.2 Programming Examples                  |            |

| 22.3 Register Description                    |            |

| 22.3.1 Register Map Summary                  |            |

| 23 TIMER/COUNTER                             | 23-1       |

| 23.1 Overview                                | 23-1       |

| 23.1.1 Features                              |            |

| 23.1.2 Pin Description                       |            |

| 23.2 Functional Description                  |            |

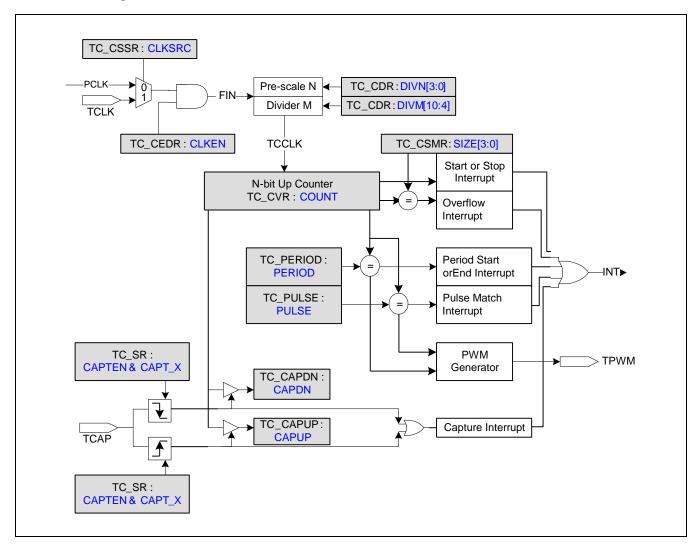

| 23.2.1 Block Diagram                         |            |

| 23.2.2 Timer Count Size                      |            |

| 23.2.3 Timer Clock                           |            |

| 23.2.4 Operation Modes                       |            |

| 23.2.5 Interrupt                             |            |

| 23.3 Register Description                    |            |

| 23.3.1 Register Map Summary                  |            |

| 24 UNIVERSAL SYNC/ASYNC RECEIVER/TRANS       | MITTER24-1 |

| 24.1 Overview                                | 24-1       |

| 24.1.1 Features                              |            |

| 24.1.2 Pin Description                       |            |

| 24.2 Functional Description                  |            |

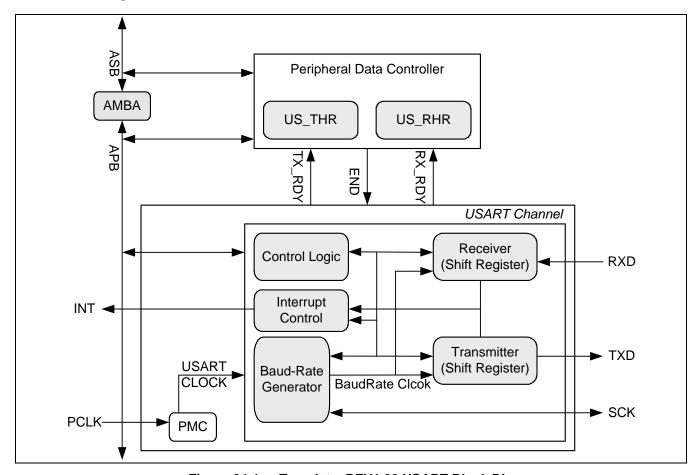

| 24.2.1 Block Diagram                         |            |

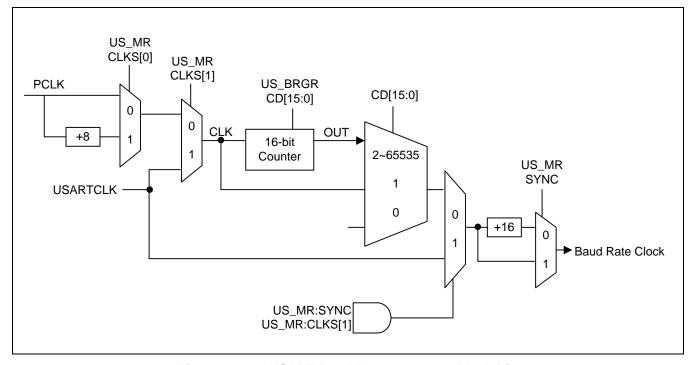

| 24.2.2 Baud Rate Generator                   |            |

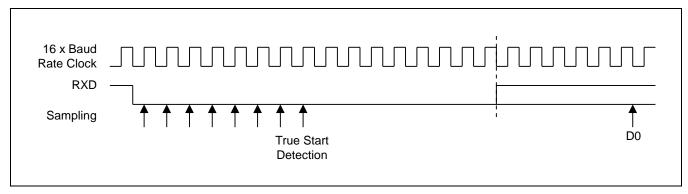

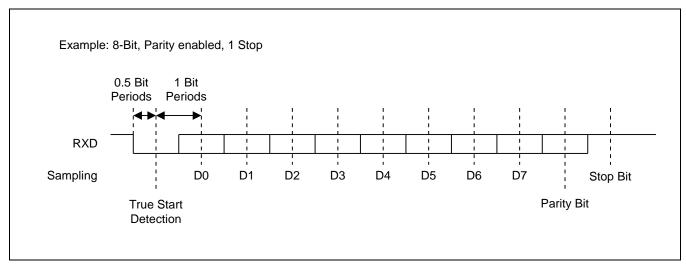

| 24.2.3 Receiver                              | 24-13      |

| 24.2.4 Transmitter                           | 24-16      |

| 24.2.5 Break                                 | 24-18      |

| 24.3 Programming Examples                    | 24-23      |

| 24.4 Register Description                    | 24-24      |

| 24.4.1 Register Map Summary                  | 24-24      |

| 24.5 4MHz–40MHz Asynchronous Mode (SYNC = 0) | 24-58      |

| 25 WATCHDOG TIMER                            | 25-1       |

| 25.1 Overview                                | 25-1       |

| 25.1.1 Feature                               |            |

| 25.2 Functional Description                  |            |

| 25.2.1 Block Diagram                         |            |

| 25.2.2 Watchdog Timer Functionality          |            |

| 25.2.3 Watchdog Timer Events                 |            |

| 25.2.4 Example                               |            |

| 25.3 Register Description                    | 25-5       |

| 25.3.1 Register Map Summary                  | 25-5       |

| 26 ELECTRICAL DATA                                    | 26-1 |

|-------------------------------------------------------|------|

| 26.1 Absolute Maximum Ratings                         | 26-1 |

| 26.2 Recommended Operation Conditions                 |      |

| 26.3 I/O D.C. Characteristics                         |      |

| 26.4 I/O Capacitance                                  | 26-4 |

| 26.5 RESET Input Characteristics                      | 26-4 |

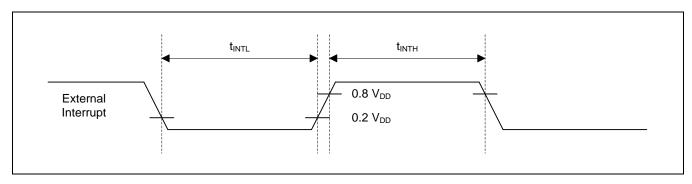

| 26.6 External Interrupt Input Characteristics         | 26-5 |

| 26.7 Oscillator Characteristics                       | 26-6 |

| 26.7.1 External Main Clock Oscillator Characteristics | 26-6 |

| 26.7.2 External Sub Clock Oscillator Characteristics  | 26-6 |

| 26.7.3 Internal Main Clock Oscillator Characteristics | 26-7 |

| 26.7.4 Internal Sub Clock Oscillator Characteristics  | 26-7 |

| 26.7.5 PLL Characteristics                            | 26-7 |

| 26.8 Current Consumption                              | 26-8 |

| 26.9 LVD Characteristics                              |      |

| 26.10 12-Bit ADC0 Characteristics                     |      |

| 26.10.1 OP-AMP Characteristics                        |      |

| 26.11 10-Bit ADC1 Characteristics                     |      |

| 26.12 LCD Characteristics                             |      |

| 26.13 Memory Characteristics                          |      |

| 26.13.1 Program Flash Memory Characteristics          |      |

| 26.13.2 Data FLASH Memory Characteristics             |      |

| 26.14 ESD Characteristics                             |      |

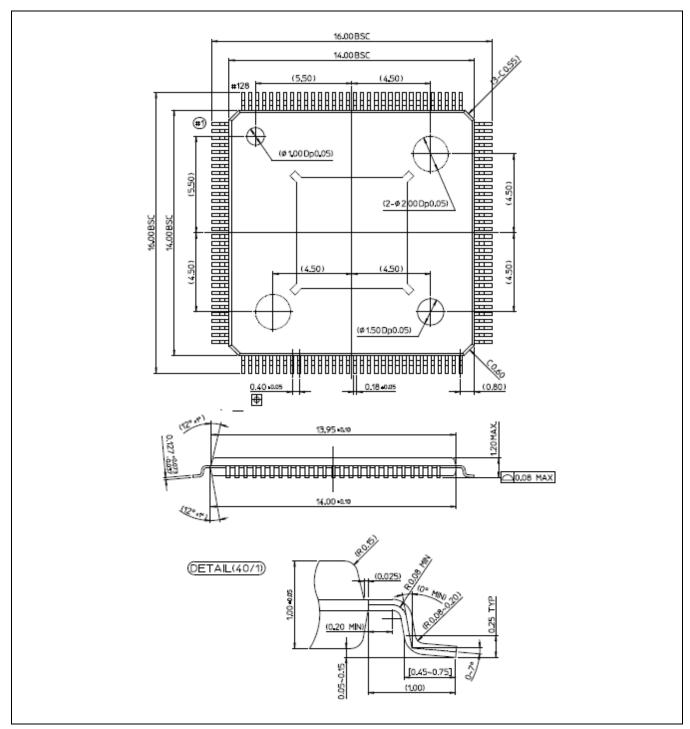

| 27 PACKAGE SPECIFICATION                              | 27-1 |

| 27.1 Overview                                         | 27-1 |

| 27.2 Packago Dimonsion                                | 27.0 |

## **List of Figures**

| Figure<br>Number | Title                                               | Page<br>Number |

|------------------|-----------------------------------------------------|----------------|

| Figure 1-1       | S3FM02G Block Diagram                               | 1-6            |

| Figure 2-1       | Pin Configuration                                   | 2-1            |

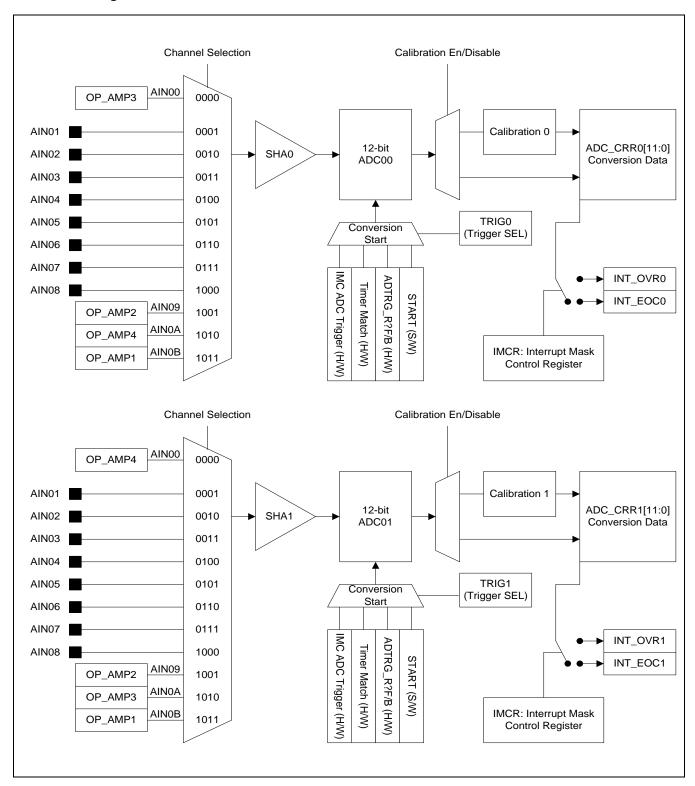

| Figure 4-1       | ADC0 Block Diagram                                  | 4-2            |

| Figure 4-2       | ADC Flow chart                                      |                |

| Figure 5-1       | ADC1 Block Diagram                                  | 5-2            |

| Figure 6-1       | Controller Area Network (CAN) Block Diagram         | 6-2            |

| Figure 6-2       | CAN Layers Description                              | 6-5            |

| Figure 6-3       | Data Frame                                          | 6-10           |

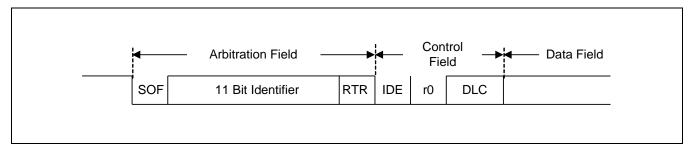

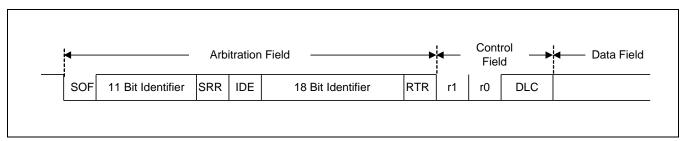

| Figure 6-4       | Standard Format                                     | 6-11           |

| Figure 6-5       | Extended Format                                     | 6-11           |

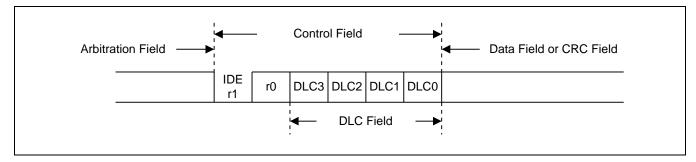

| Figure 6-6       | CAN Control Field                                   | 6-13           |

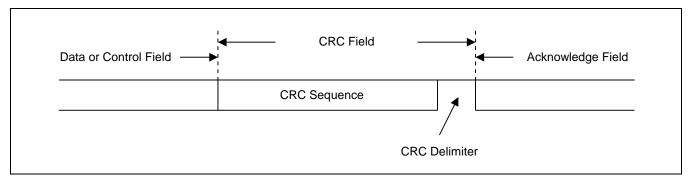

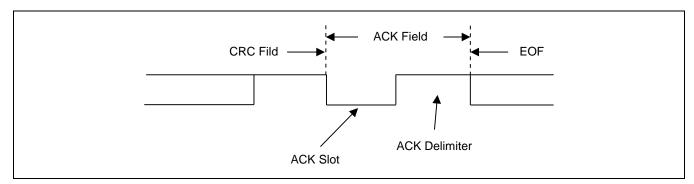

| Figure 6-7       | CRC Field                                           | 6-14           |

| Figure 6-8       | ACK Field                                           | 6-15           |

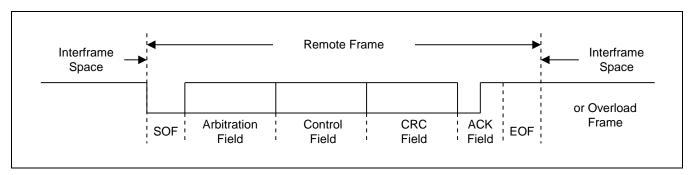

| Figure 6-9       | Remote Frame                                        | 6-16           |

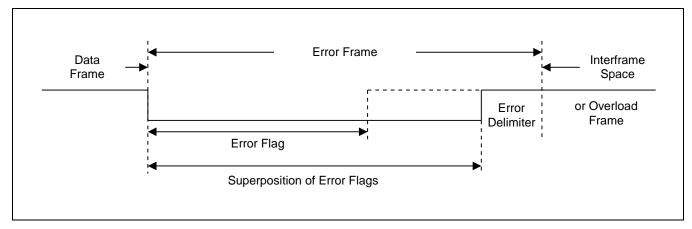

| Figure 6-10      | Error Frame                                         | 6-17           |

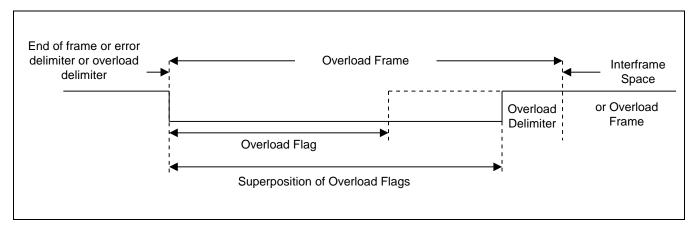

| Figure 6-11      | Overload Frame                                      | 6-18           |

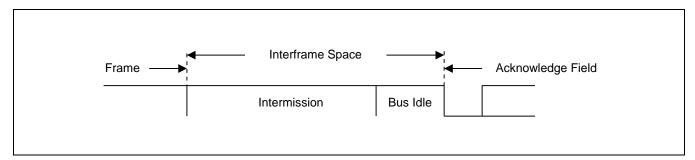

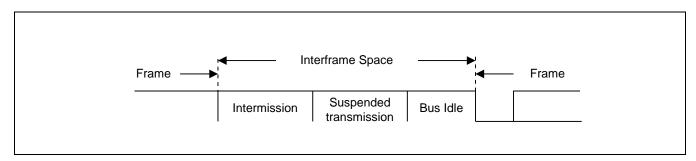

| Figure 6-12      | Interframe Space for Receiver                       | 6-19           |

| Figure 6-13      | Interframe Space for Transmitter                    | 6-19           |

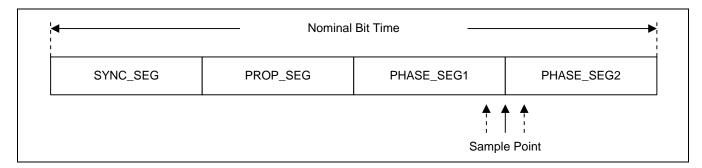

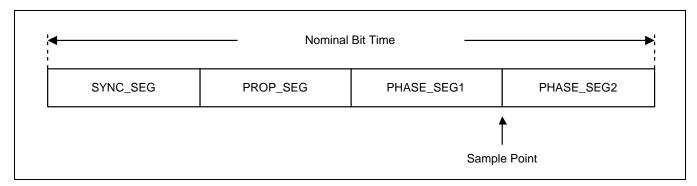

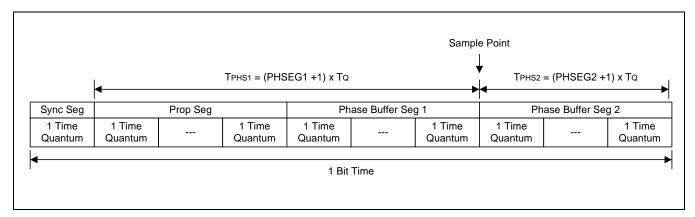

| Figure 6-14      | Partition of Bit Time                               | 6-25           |

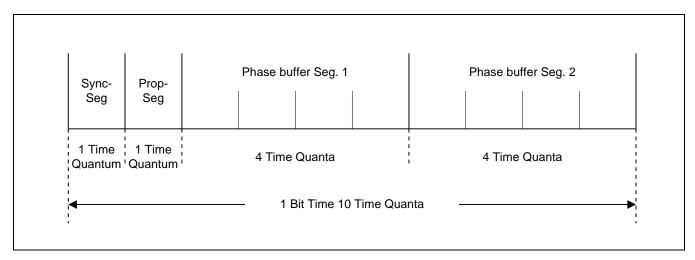

| Figure 6-15      | Example of Nominal Bit Time                         | 6-27           |

| Figure 6-16      | CAN Core in Silent Mode                             | 6-33           |

| Figure 6-17      | CAN Core in Loop Back Mode                          | 6-34           |

| Figure 6-18      | CAN Core in Loop Back Combined with Silent Mode     | 6-35           |

| Figure 6-19      | Data Transfer Between IFx Registers and Message RAM | 6-39           |

| Figure 6-20      | CPU Handling of a FIFO Buffer                       | 6-45           |

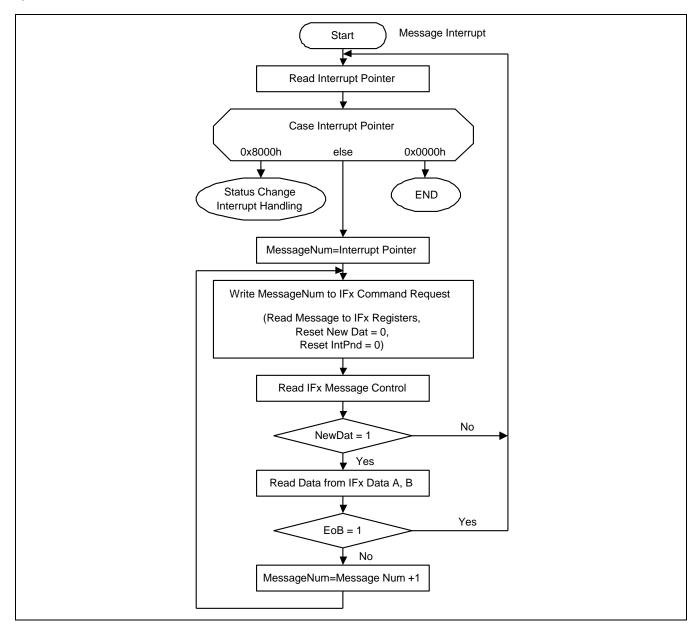

| Figure 6-21      | Bit Timing                                          | 6-47           |

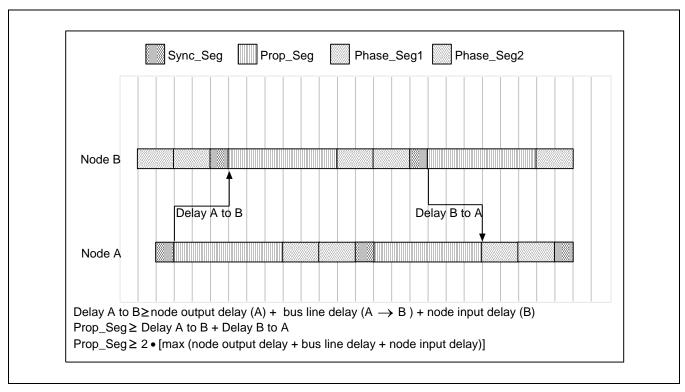

| Figure 6-22      | Propagation Time Segment                            | 6-48           |

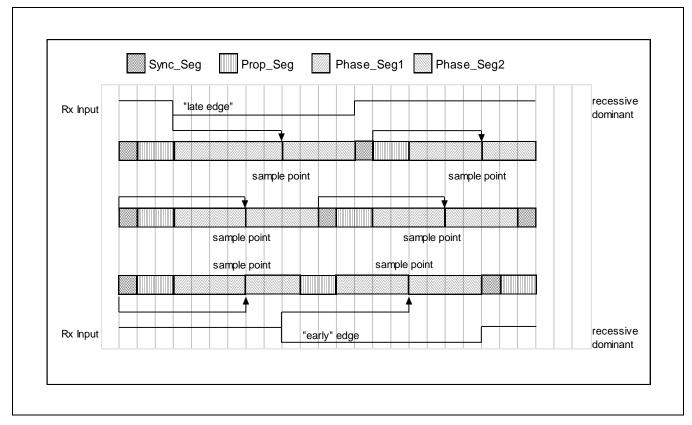

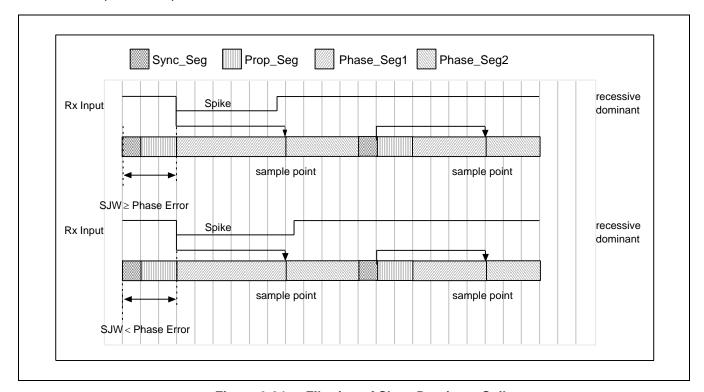

| Figure 6-23      | Synchronization on Late and Early Edges             | 6-50           |

| Figure 6-24      | Filtering of Short Dominant Spikes                  | 6-51           |

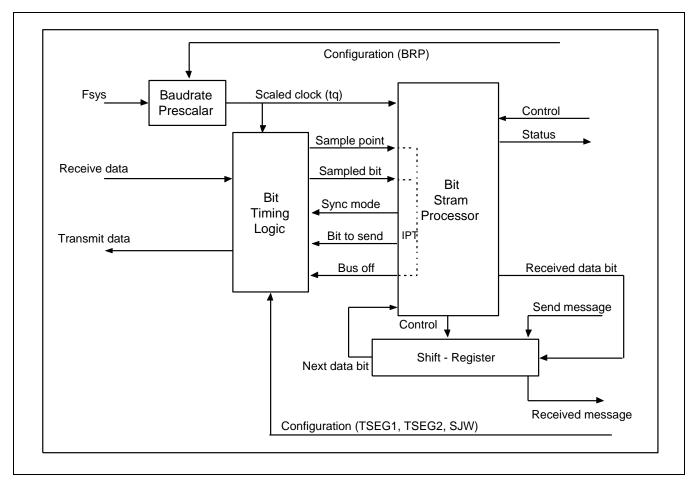

| Figure 6-25      | Structure of the CAN Controller Core                | 6-53           |

| Figure 6-26      | CAN Bit Time Built up from Time Quantum             | 6-65           |

| Figure 6-27      | Open Drain Mode                                     | 6-97           |

| Figure 7-1       | System Clock Tree Block Diagram                     |                |

| Figure 7-2       | System Clock Selection                              |                |

| Figure 7-3       | Clock Control State Machine                         |                |

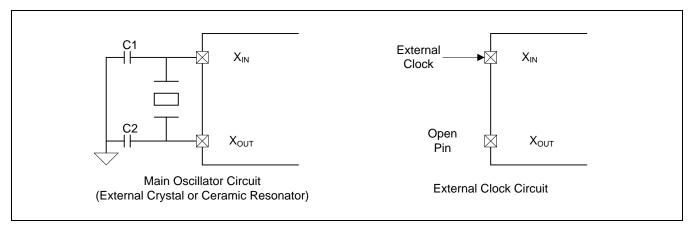

| Figure 7-4       | Crystal/Ceramic Resonator/External Clock Operation  |                |

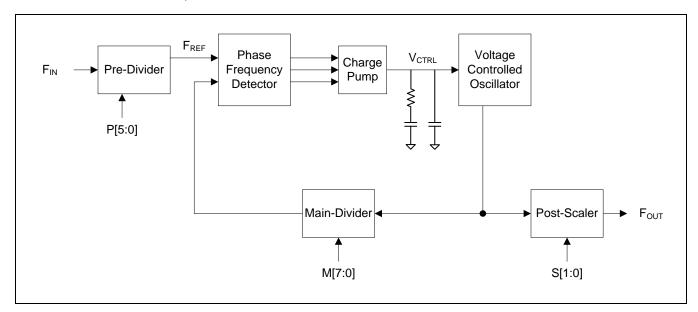

| Figure 7-5       | PLL (Phase-Locked Loop) Block Diagram               |                |

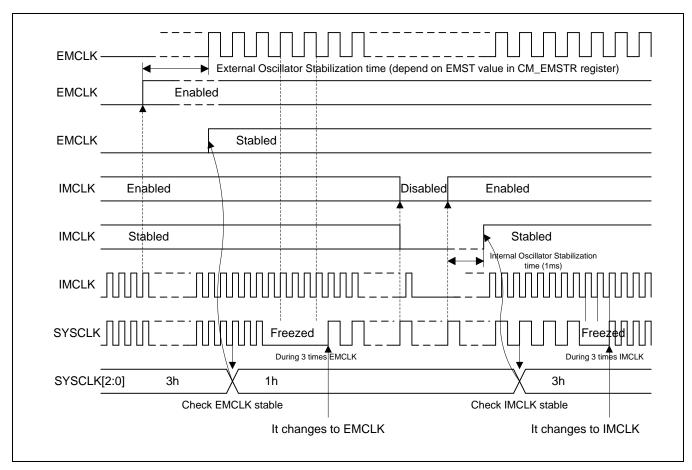

| Figure 7-6       | The case that changes clock source for SYSCLK       |                |

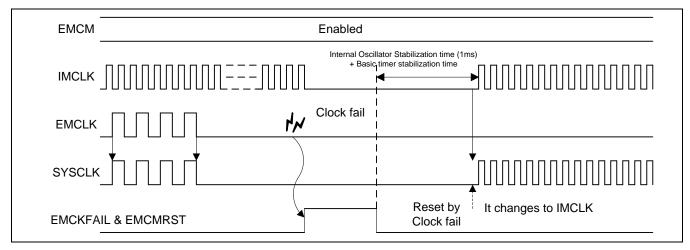

| Figure 7-7       | External Main Oscillator Fail with Reset            |                |

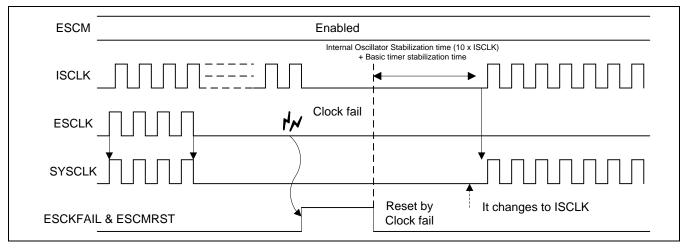

| Figure 7-8       | External Sub Oscillator Fail with Reset             | 7-14           |

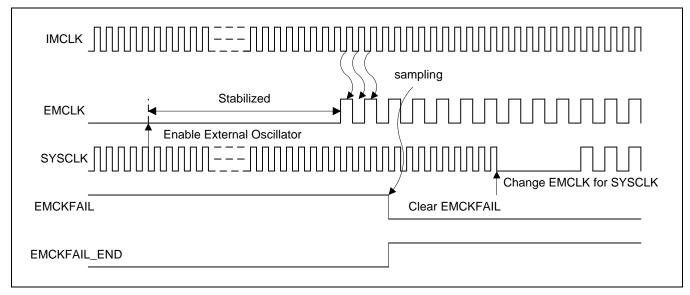

| Figure 7-9       | End of Clock Fail                                   | 7-15           |

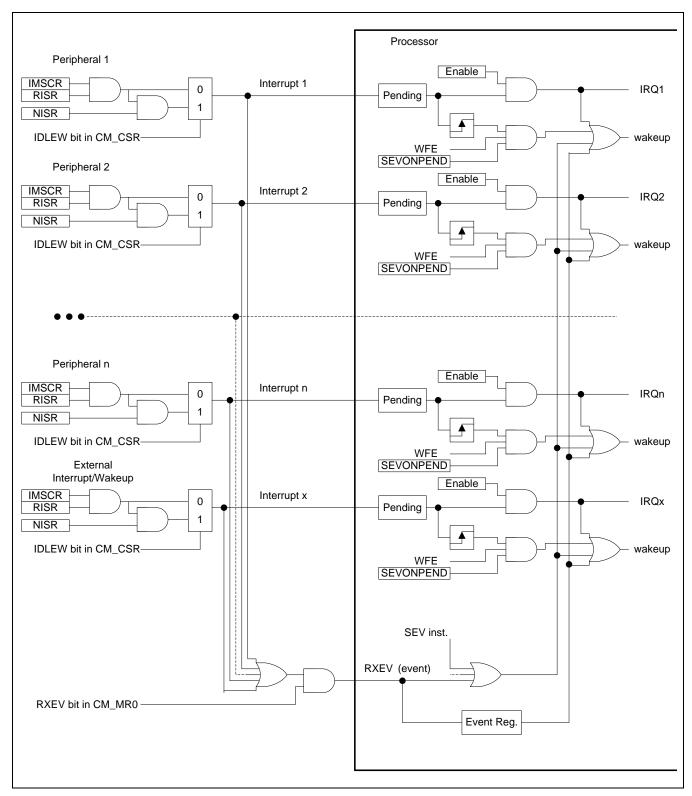

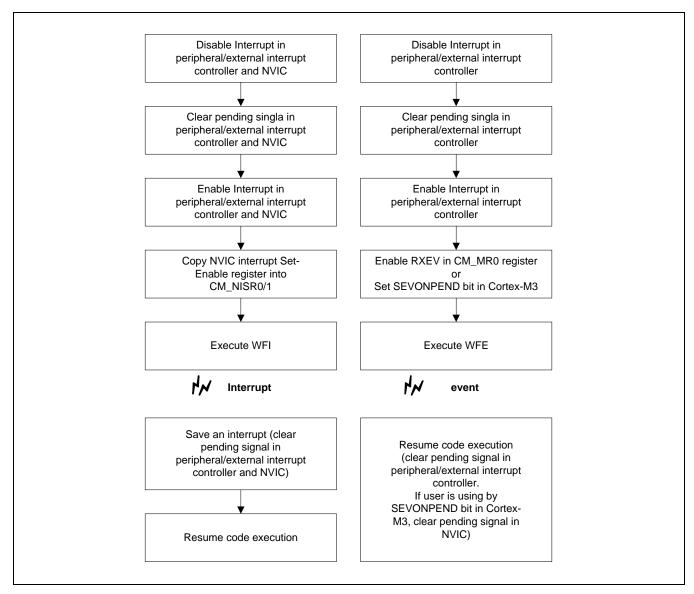

| Figure 7-10 | Interrupt and Event                                                       | 7-20  |

|-------------|---------------------------------------------------------------------------|-------|

| Figure 7-11 | Different Handling Process for Interrupt and Event in IDLE or STOP Mode   |       |

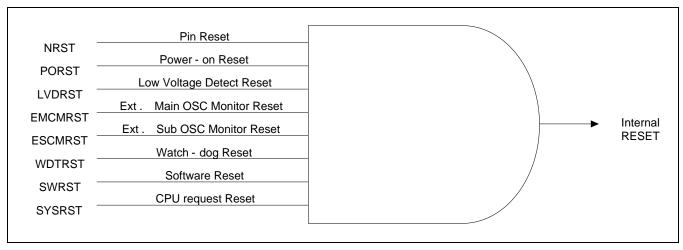

| Figure 7-12 | RESET Sources                                                             |       |

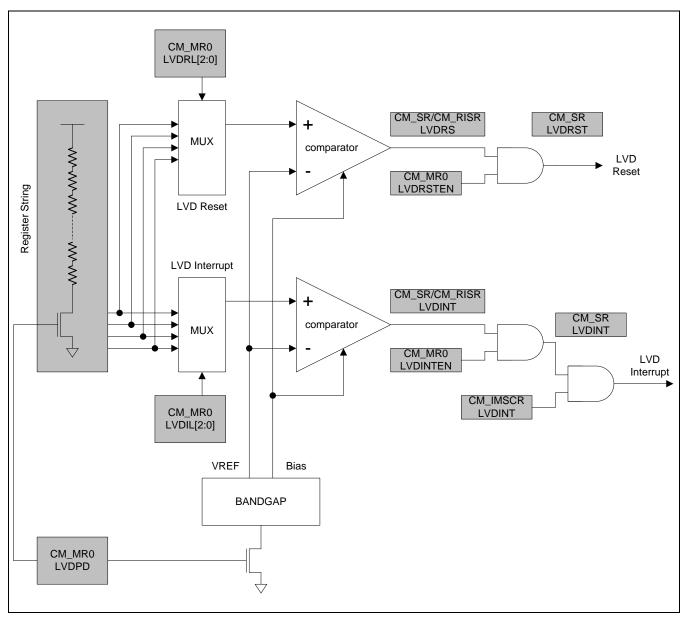

| Figure 7-13 | LVD Block Diagram                                                         | 7-24  |

| Figure 7-14 | RESET @EMCLK                                                              | 7-27  |

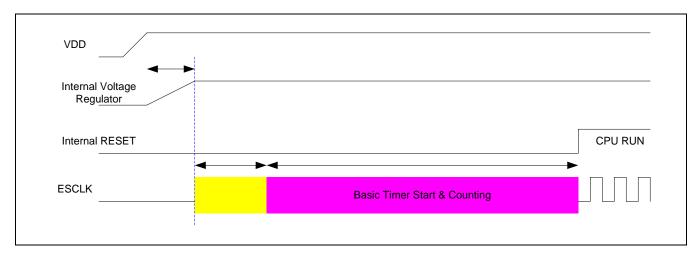

| Figure 7-15 | RESET @ESCLK                                                              | 7-27  |

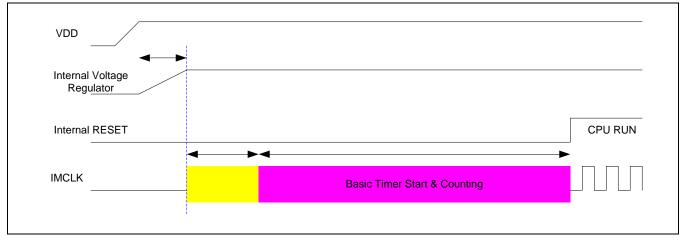

| Figure 7-16 | RESET @IMCLK                                                              | 7-27  |

| Figure 7-17 | RESET @ISCLK                                                              | 7-28  |

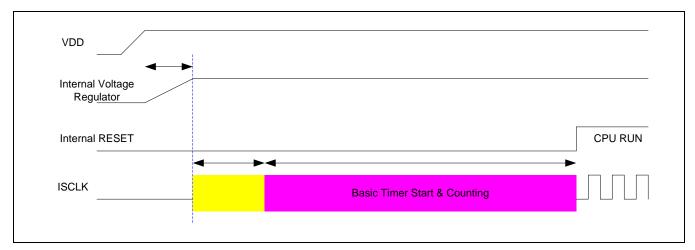

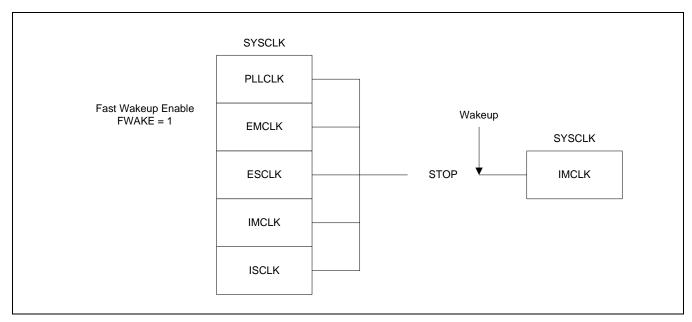

| Figure 7-18 | Fast Wake-up                                                              | 7-28  |

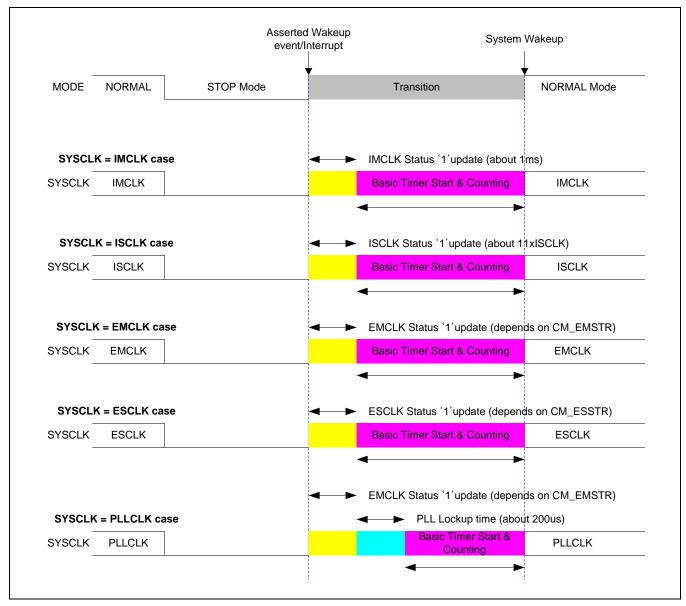

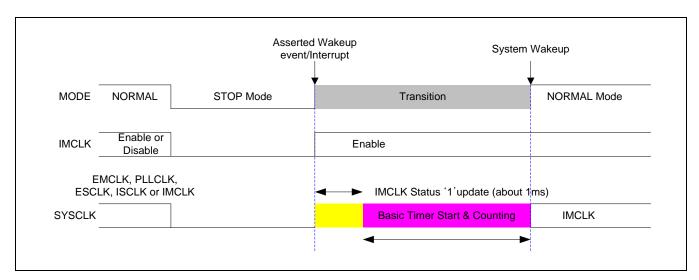

| Figure 7-19 | Basic Timer and Exit of STOP mode when FWAKE is "0"                       | 7-29  |

| Figure 7-20 | Basic Timer and Exit of STOP mode when FWAKE is "1" (SYSCLK = IMCLK)      | 7-30  |

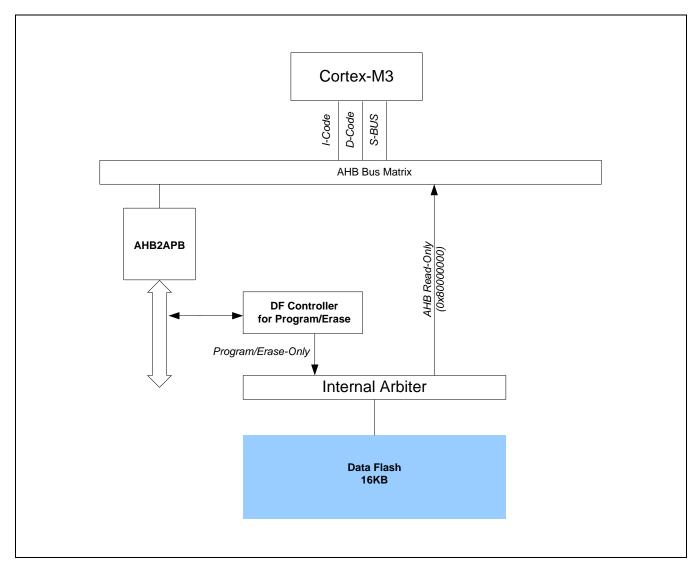

| Figure 8-1  | DFLASH Block Diagram                                                      |       |

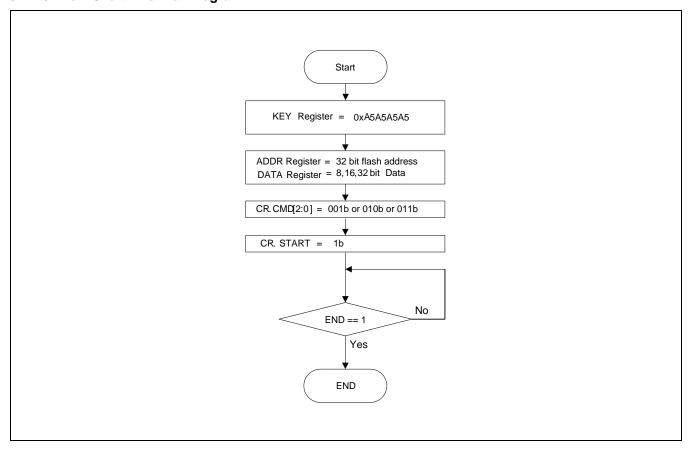

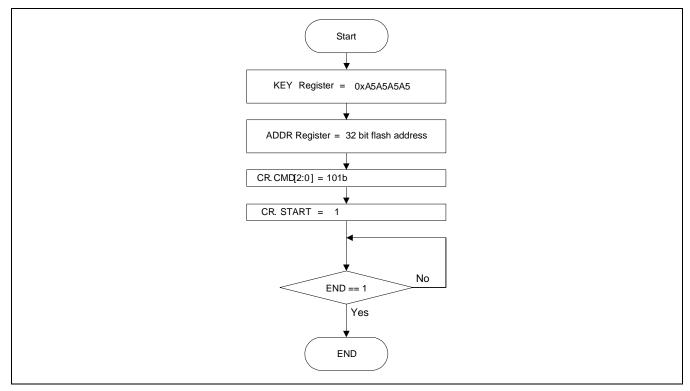

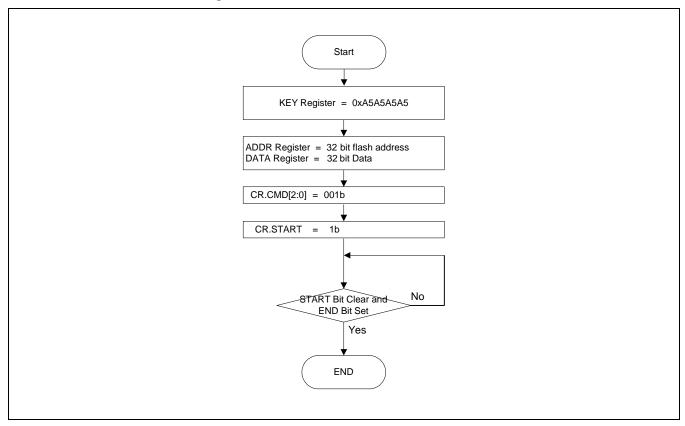

| Figure 8-2  | Normal Program Flow Chart                                                 |       |

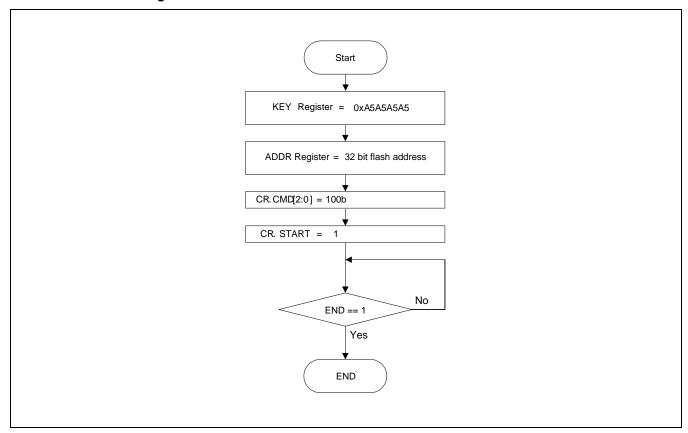

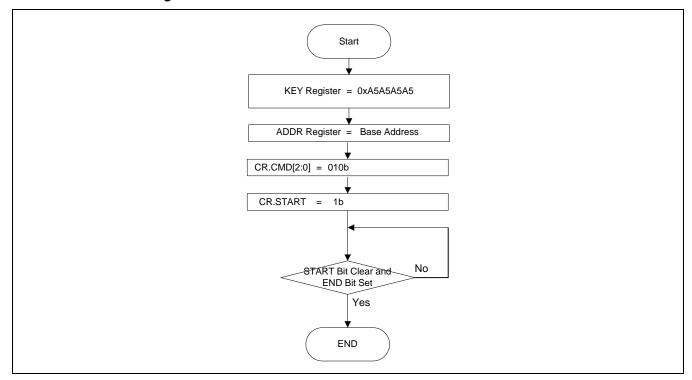

| Figure 8-3  | Page Erase Flow Chart                                                     |       |

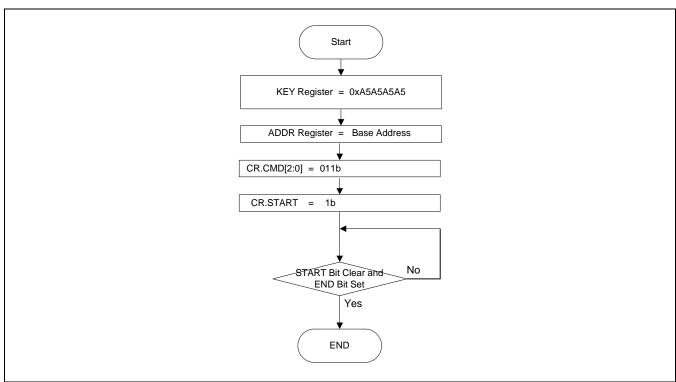

| Figure 8-4  | Sector Erase Flow Chart                                                   |       |

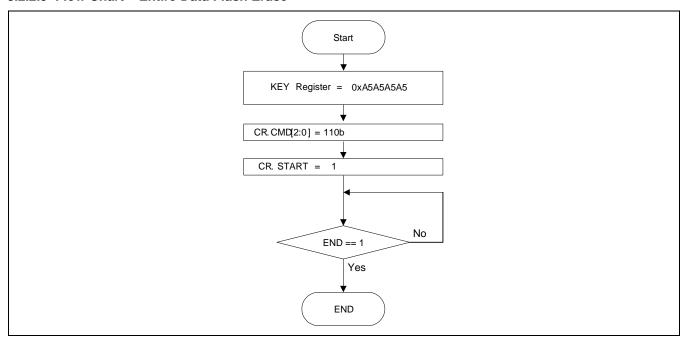

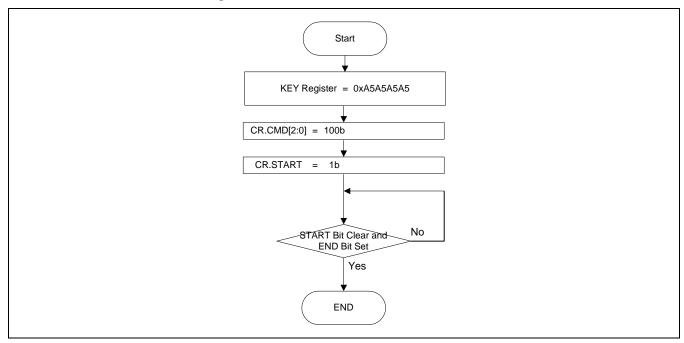

| Figure 8-5  | Entire Data Flash Erase Flow Chart                                        | 8-7   |

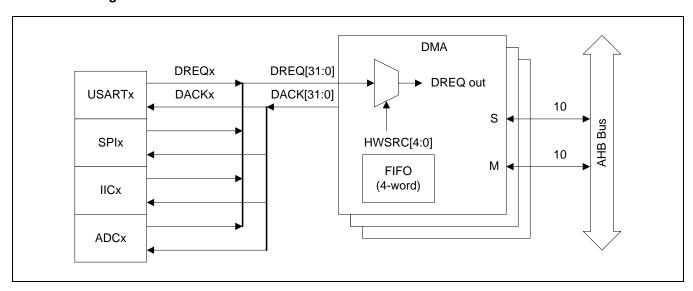

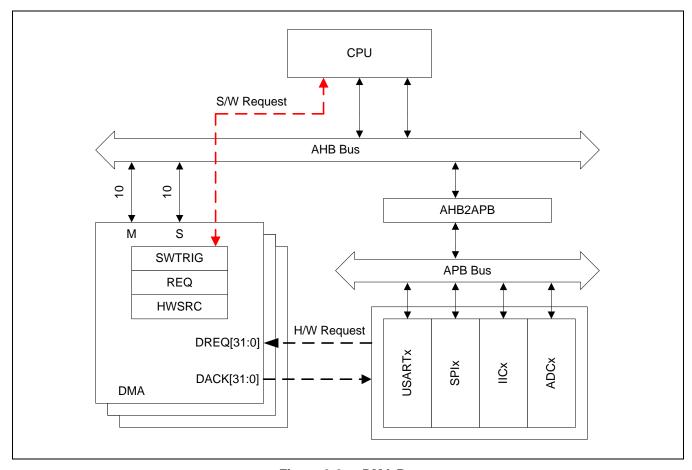

| Figure 9-1  | DMA Block Diagram                                                         |       |

| Figure 9-2  | DMA Request                                                               |       |

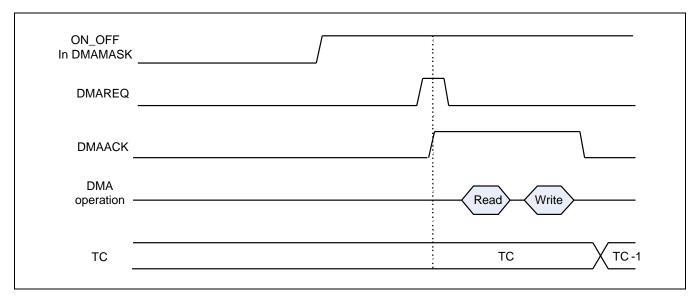

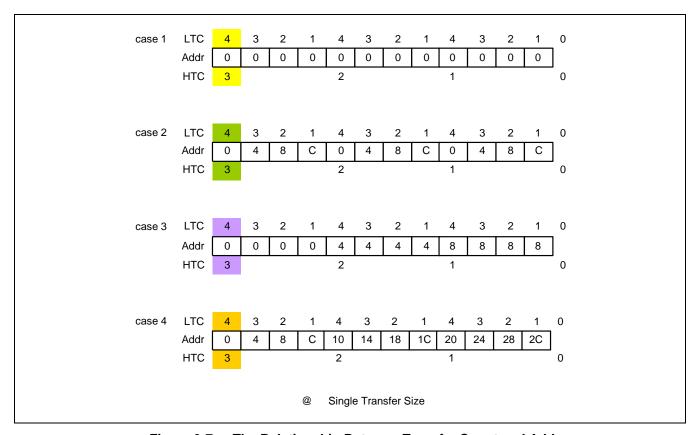

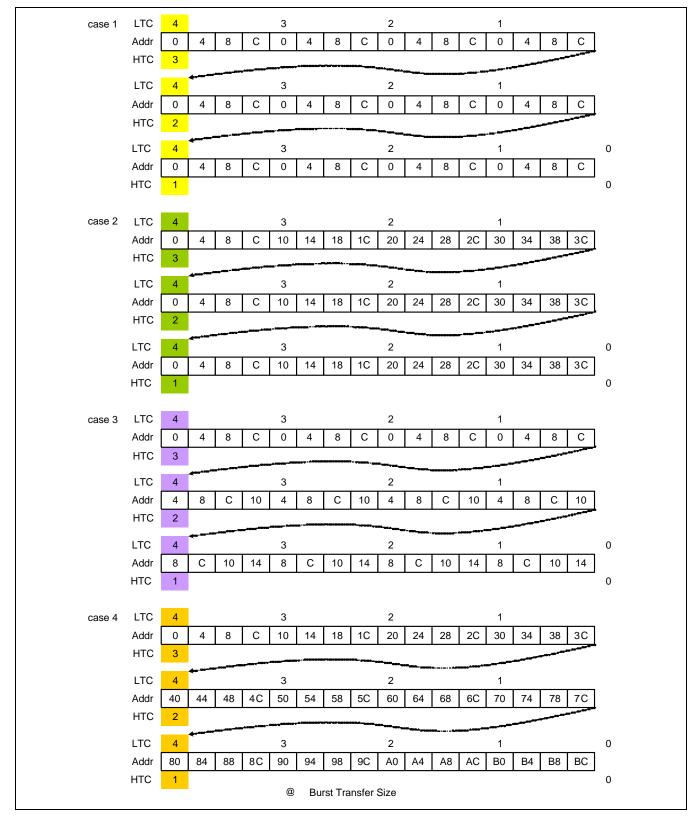

| Figure 9-3  | Single Transfer in Single Service Mode                                    |       |

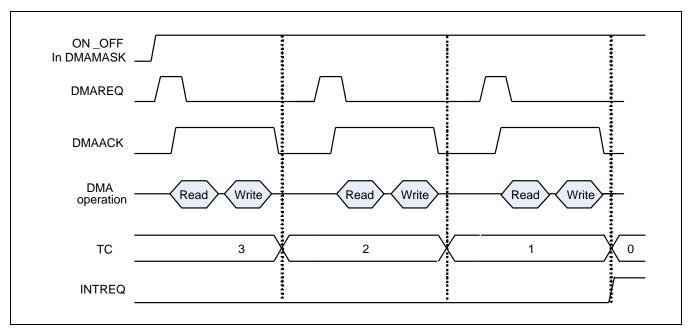

| Figure 9-4  | Sequential Transfer in Single Mode                                        |       |

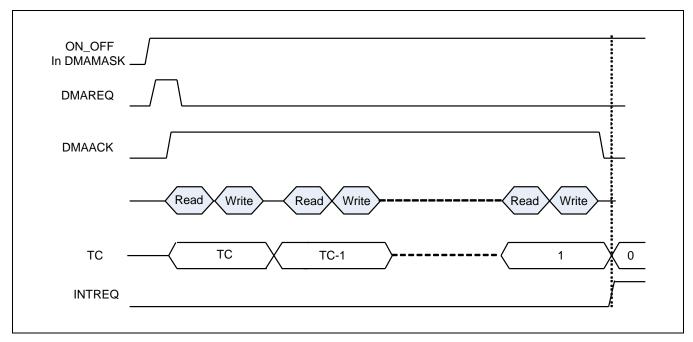

| Figure 9-5  | Continuous Service Mode                                                   |       |

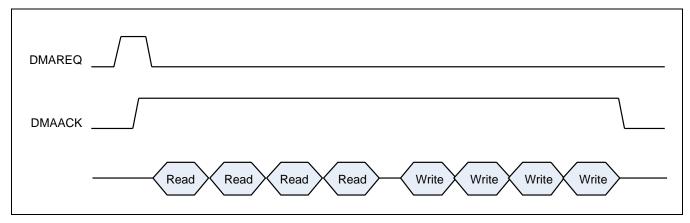

| Figure 9-6  | Burst (4-unit) Transfer Size                                              |       |

| Figure 9-7  | The Relationship Between Transfer Count and Address                       |       |

| Figure 9-8  | The Relationship Between Transfer Count and Address                       | 9-10  |

| Figure 10-1 | ENC Block Diagram                                                         |       |

| Figure 10-2 | Position Counter Operation                                                | 10-3  |

| Figure 11-1 | Free Running Timer Block Diagram                                          |       |

| Figure 11-2 | FRT Clock Source                                                          | 11-3  |

| Figure 12-1 | GPIO Block Diagram                                                        | 12-3  |

| Figure 13-1 | Inter-Integrated Circuit (IIC) Block Diagram                              |       |

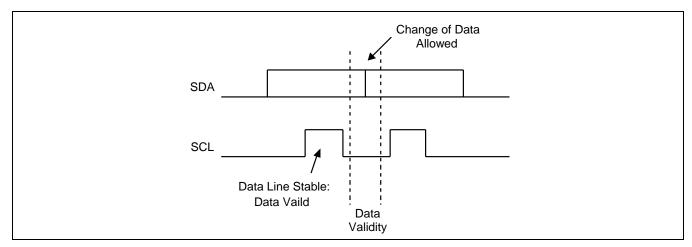

| Figure 13-2 | Data Validity                                                             |       |

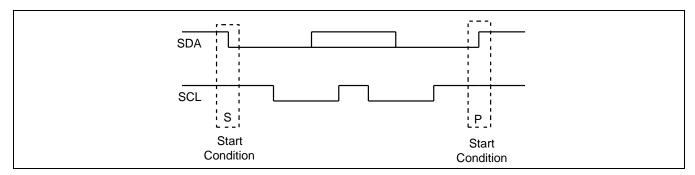

| Figure 13-3 | Start and Stop Conditions                                                 |       |

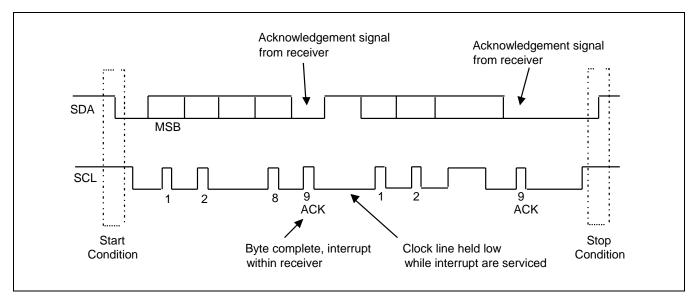

| Figure 13-4 | Data Transfer on the I2C Bus                                              |       |

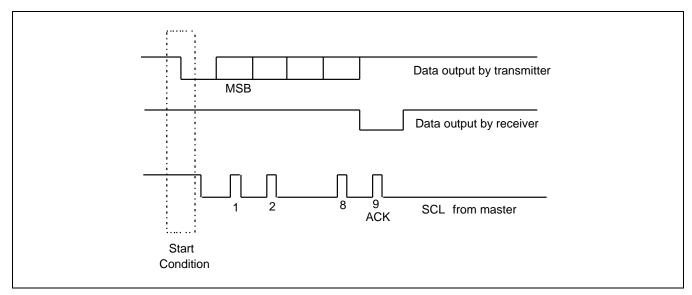

| Figure 13-5 | Acknowledge                                                               | 13-8  |

| Figure 13-6 | A Master-Transmitter Addresses a Slave                                    |       |

| Figure 13-7 | A Master-Transmitter Addresses a Slave-Receiver with a 10-bits Address    |       |

| Figure 13-8 | Hold and Setup Delays                                                     | 13-40 |

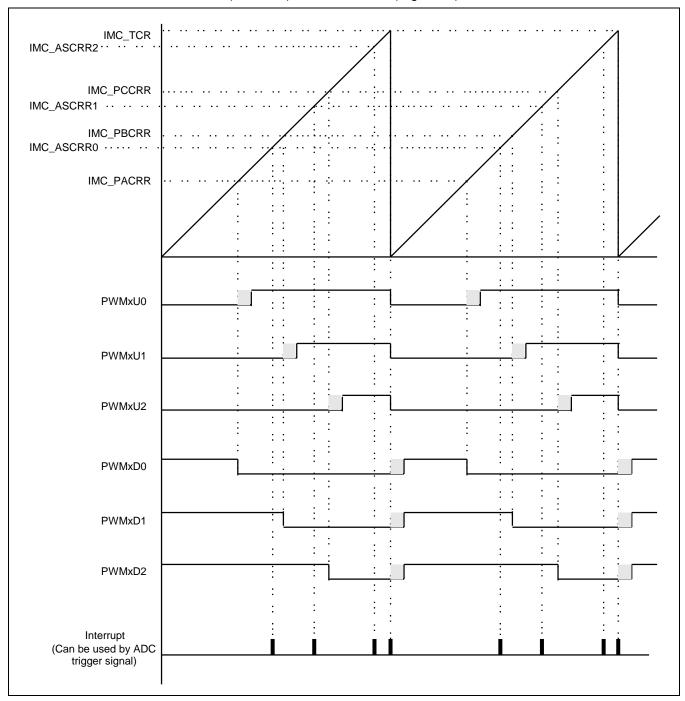

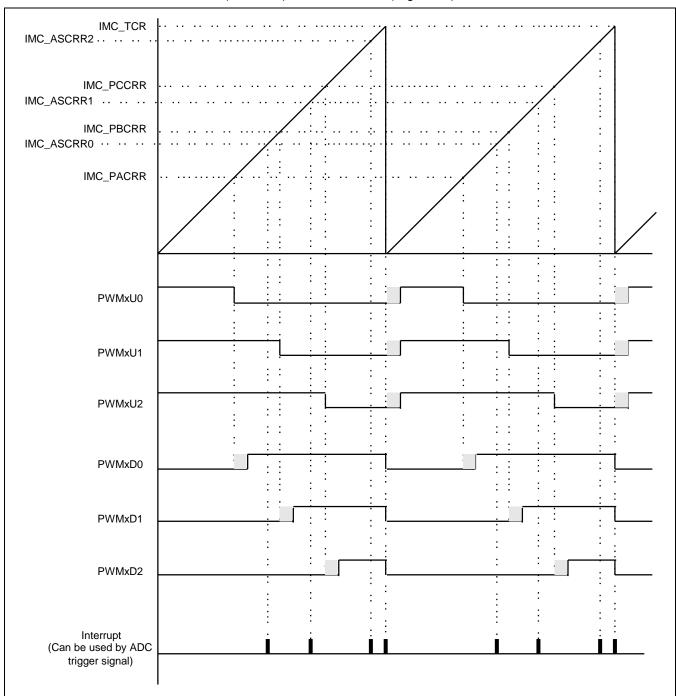

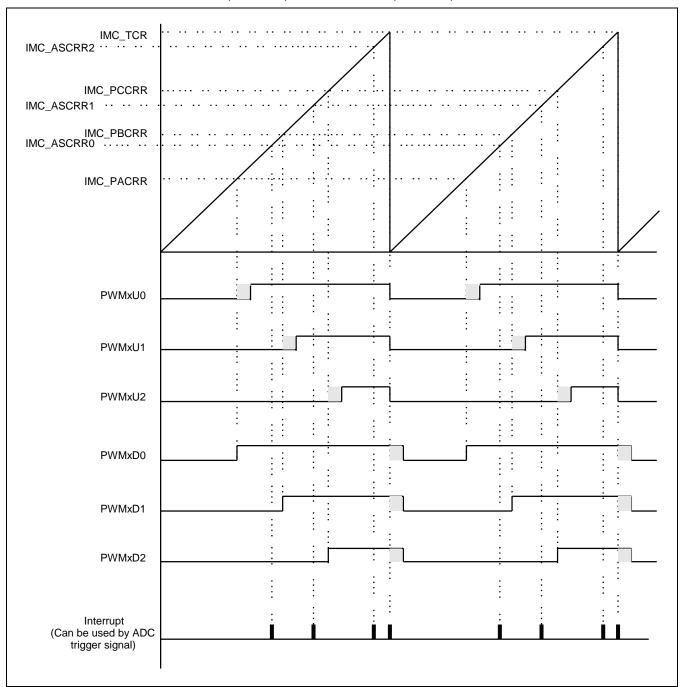

| Figure 14-1 | IMC Block Diagram                                                         |       |

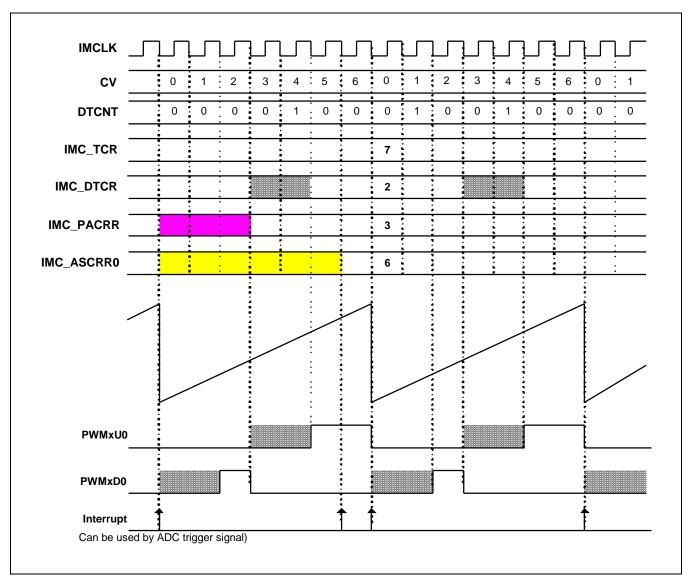

| Figure 14-2 | Tri-angular Wave Signal Generation                                        |       |

| Figure 14-3 | Saw-Tooth Wave Signal Generation                                          |       |

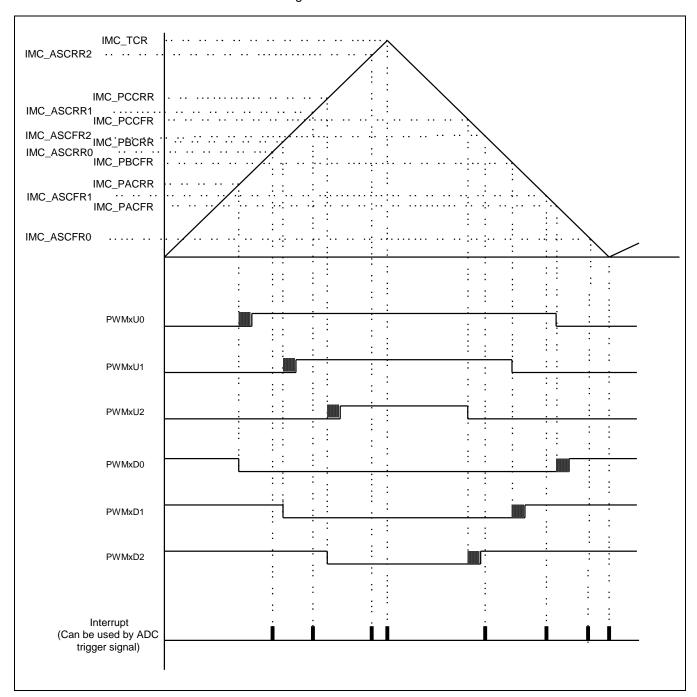

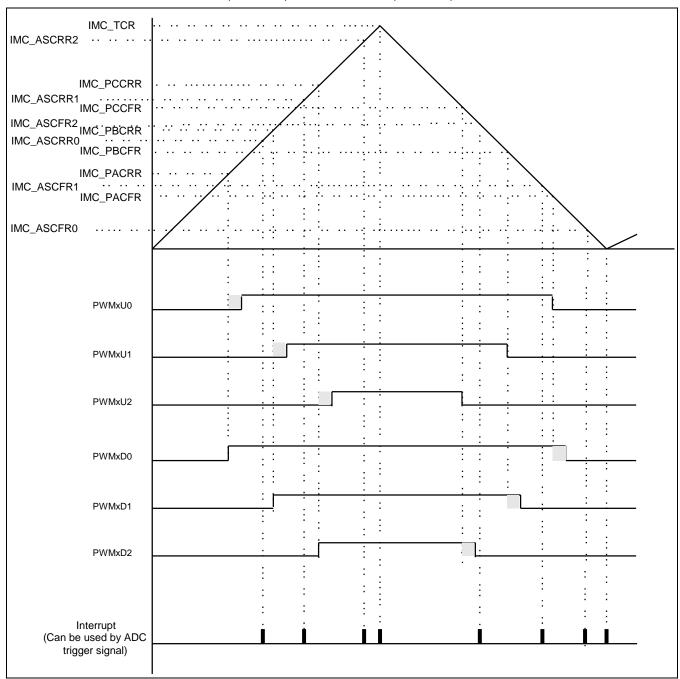

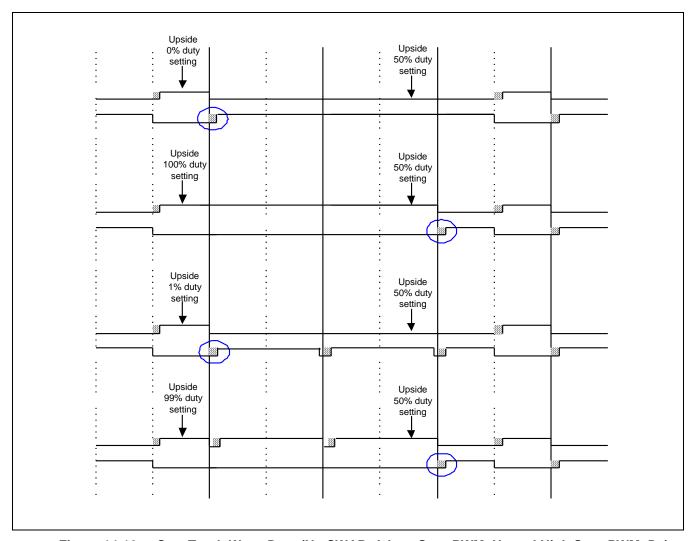

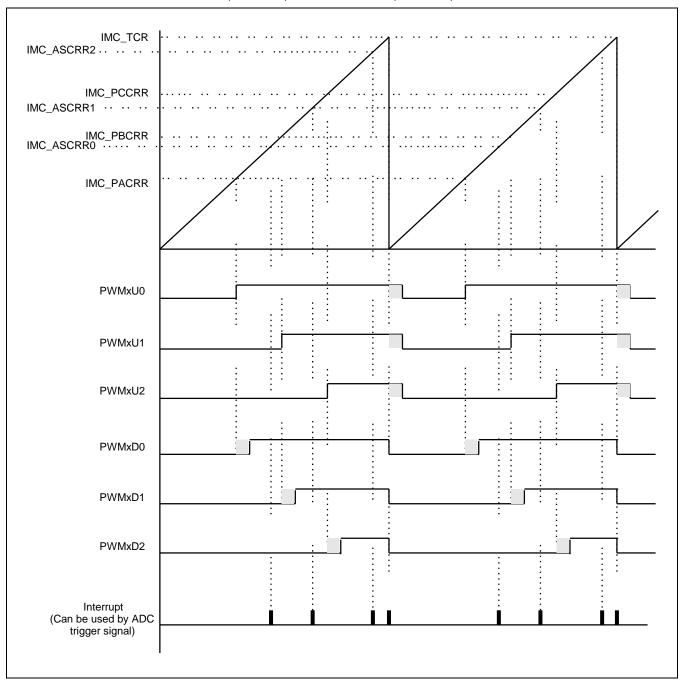

| Figure 14-4 | Tri-Angular Wave (No SWAP, A Low Start PWMxUy and High Start PWMxDy)      |       |

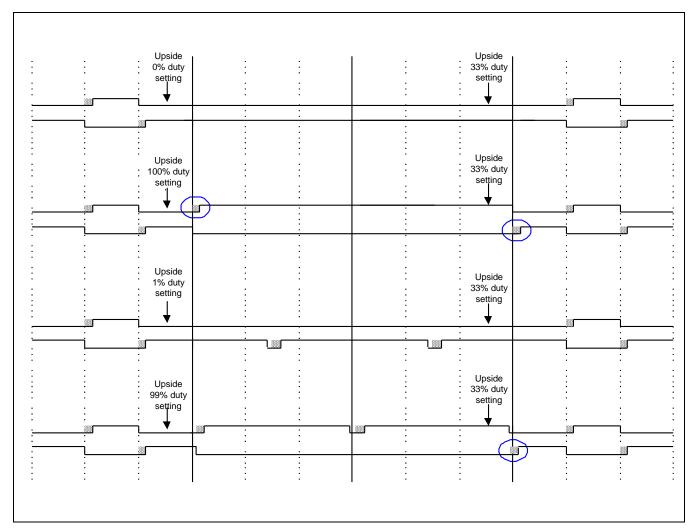

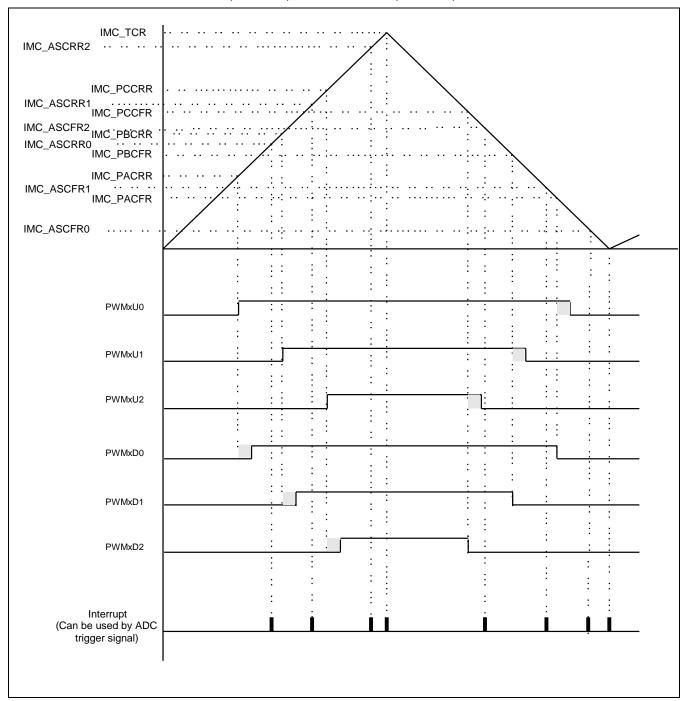

| Figure 14-5 | Tri-Angular Wave Duty (No SWAP, A Low Start PWMxUy and High Start PWMxDy) |       |

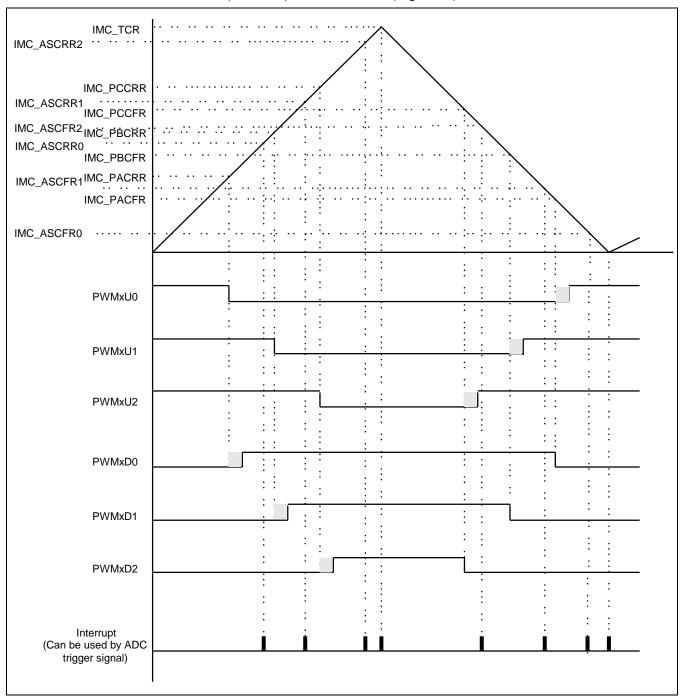

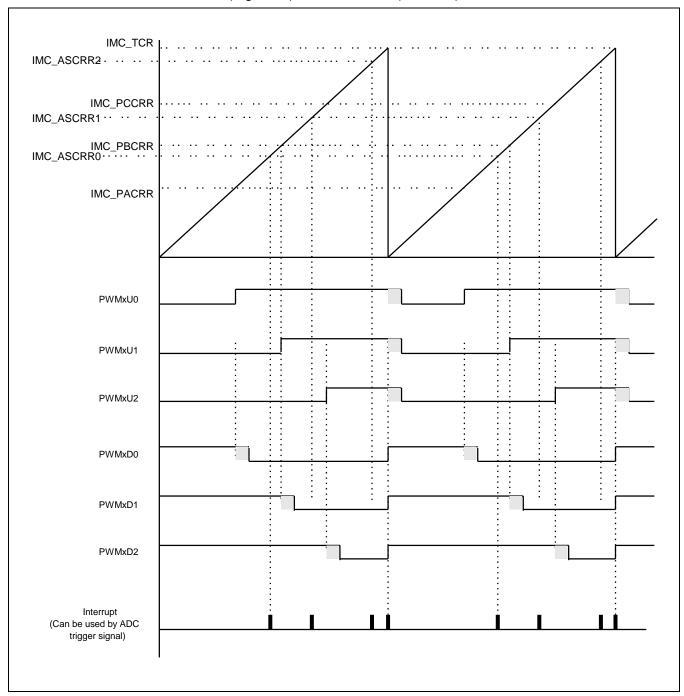

| Figure 14-6 | Tri-Angular Wave (SWAP, A Low Start PWMxUy and High Start PWMxDy)         |       |

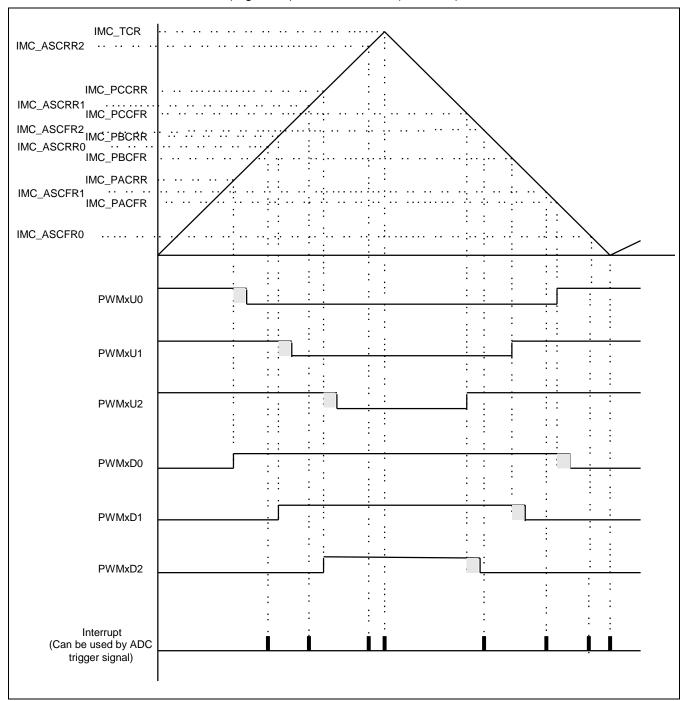

| Figure 14-7 | Tri-Angular Wave Duty (SWAP, A Low Start PWMxUy and High Start PWMxDy)    |       |

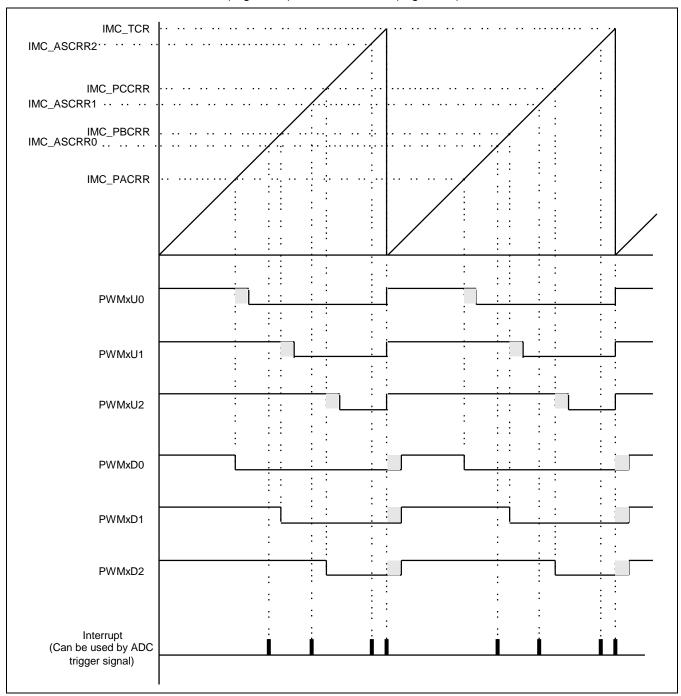

| Figure 14-8 | Tri-Angular Wave (No SWAP, A Low Start PWMxUy and Low Start PWMxDy)       |       |

| Figure 14-9 | THEATIGUIAL VVAVE (SVVAF, A LOW STALL FVVIVIXOY AND LOW STALL FVVIVIXOY)  | 14-10 |

| Figure 14-10 | Tri-Angular Wave (No SWAP, A High Start PWMxUy and Low Start PWMxDy)             | 14-11 |

|--------------|----------------------------------------------------------------------------------|-------|

| Figure 14-11 | Tri-Angular Wave Duty (No SWAP, A High Start PWMxUy and Low Start PWMxDy)        |       |

| Figure 14-12 | Tri-Angular Wave (SWAP, A High Start PWMxUy and Low Start PWMxDy)                |       |

| Figure 14-13 | Tri-Angular Wave (No SWAP, A High Start PWMxUy and High Start PWMxDy)            |       |

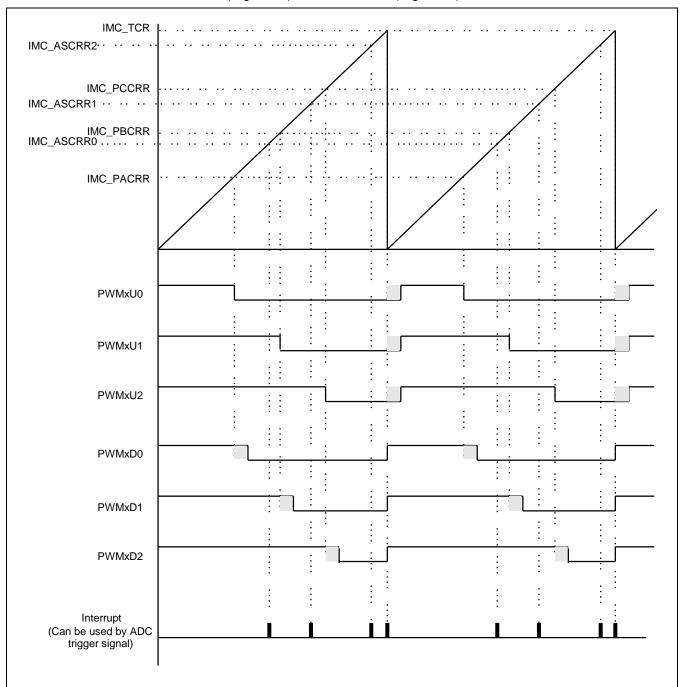

| igure 14-14  | Tri-Angular Wave (SWAP, A High Start PWMxUy and High Start PWMxDy)               |       |

| Figure 14-15 | Saw-Tooth Wave (No SWAP, A Low Start PWMxUy and High Start PWMxDy)               |       |

| Figure 14-16 | Saw-Tooth Wave Duty (No SWAP, A Low Start PWMxUy and High Start PWMxDy)          |       |

| Figure 14-17 | Saw-Tooth Wave (SWAP, A Low Start PWMxUy and High Start PWMxDy)                  |       |

| Figure 14-17 | Saw-Tooth Wave (No SWAP, A Low Start PWMxUy and Low Start PWMxDy)                |       |

| Figure 14-18 | Saw-Tooth Wave (SWAP, A Low Start PWMxUy and Low Start PWMxDy)                   |       |

| -            | Saw-Tooth Save (No SWAP, A Low Start PWMxUy and Low Start PWMxDy)                |       |

| Figure 14-20 | Saw-Tooth Wave (SWAP, A High Start PWMxUy and Low Start PWMxDy)                  |       |

| Figure 14-21 | •                                                                                |       |

| Figure 14-22 | Saw-Tooth Wave (No SWAP, A High Start PWMxUy and High Start PWMxDy)              |       |

| Figure 14-23 | Saw-Tooth Wave (SWAP, A High Start PWMxUy and High Start PWMxDy)                 |       |

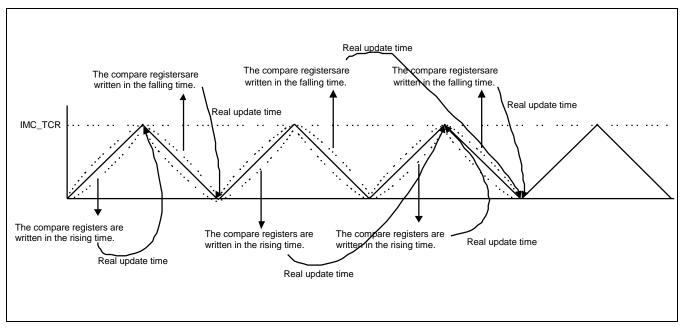

| Figure 14-24 | Synchronous Write at Zero & IMC_TCR Match (SYNCSEL = 00'b, NUMSKIP = 00000'b)    |       |

| igure 14-25  | Synchronous Write at Zero & IMC_TCR Match (SYNCSEL = 00'b, NUMSKIP = 00000'b)    |       |

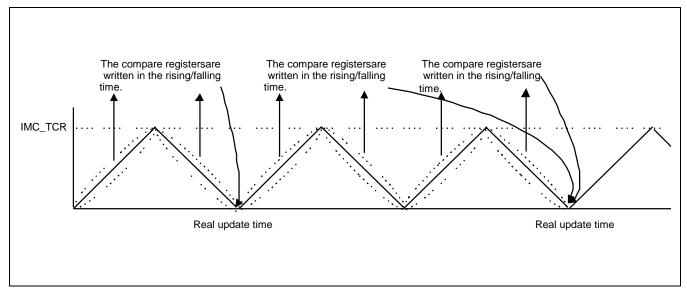

| Figure 14-26 | Synchronous Write at Zero Match (SYNCSEL = 01'b, NUMSKIP = 00000'b)              |       |

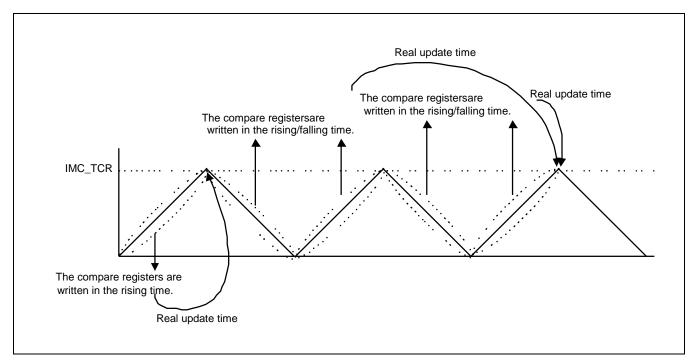

| igure 14-27  | Synchronous Write at IMC_TCR Match (SYNCSEL = 10'b, NUMSKIP = 00000'b)           |       |

| igure 14-28  | Synchronous Write at Zero & IMC_TCR Match (SYNCSEL = 00'b, NUMSKIP = 00001'b)    |       |

| Figure 14-30 | Synchronous Write at Zero Match (SYNCSEL = 01'b, NUMSKIP = 00001'b)              |       |

| igure 14-29  | Synchronous Write at IMC_TCR Match (SYNCSEL = 10'b, NUMSKIP = 00001'b)           |       |

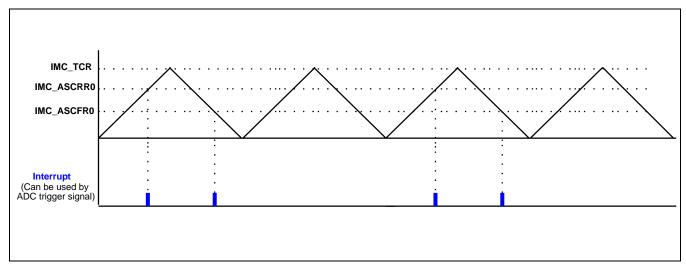

| Figure 14-32 | The Skip Control of ADC Trigger Signal Interrupt                                 | 14-35 |

| Figure 15-1  | Interrupt Control Block Diagram                                                  | 15-2  |

| 44           | LOD O A H. T. DI L D'                                                            | 47.0  |

| Figure 17-1  | LCD Controller Top Block Diagram                                                 |       |

| Figure 17-2  | LCD Controller Block Diagram                                                     |       |

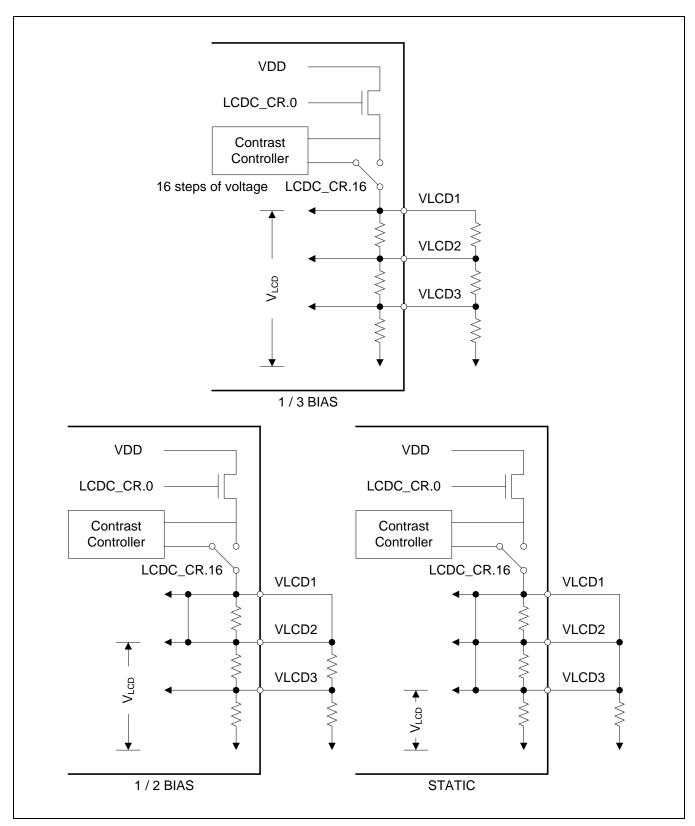

| Figure 17-3  | Voltage Dividing Internal Resistor Circuit Diagram                               |       |

| igure 17-4   | Voltage Dividing External Resistor Circuit Diagram                               |       |

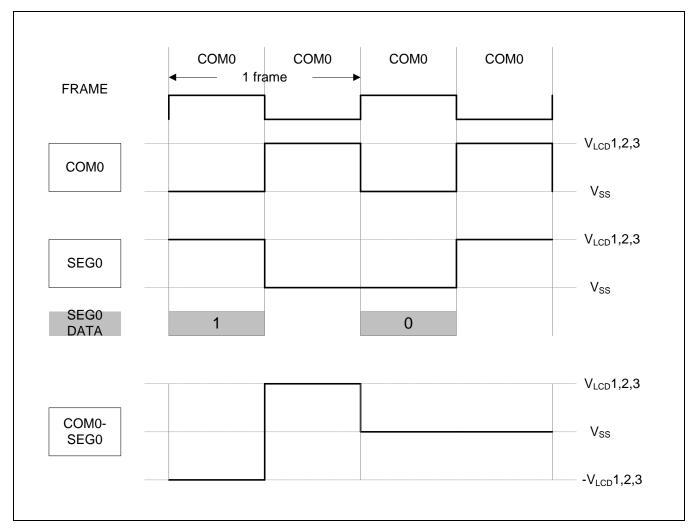

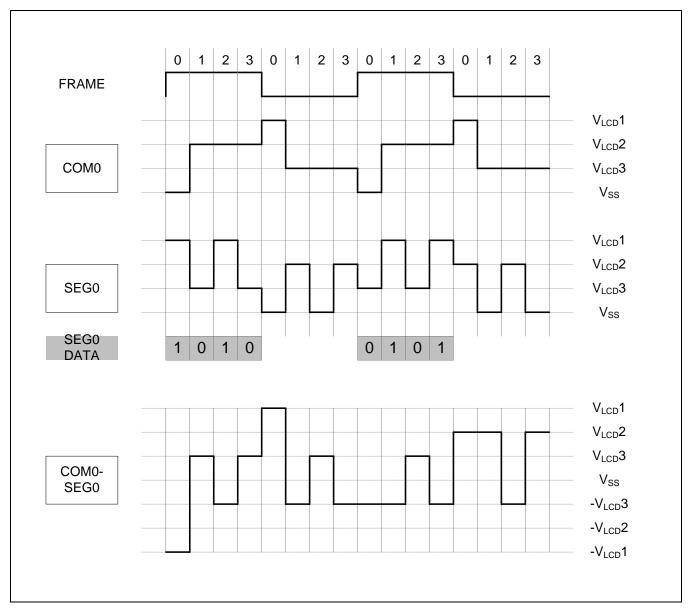

| Figure 17-5  | COM/SEG Signal in Static Mode                                                    |       |

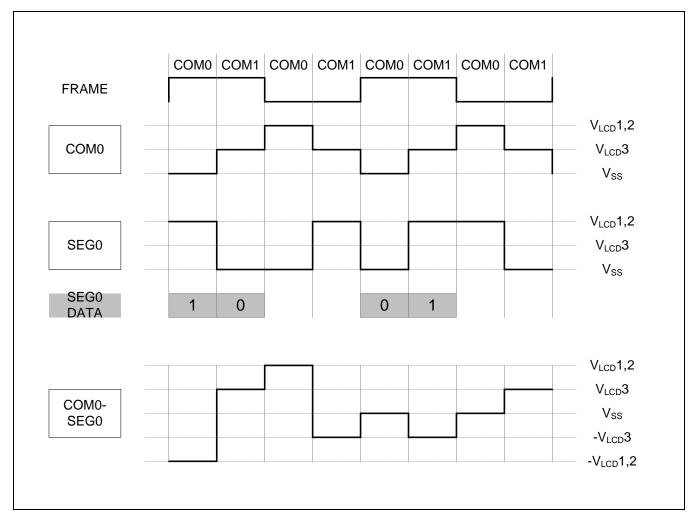

| igure 17-6   | COM/SEG Signal in 1/2Duty and 1/2Bias Mode                                       |       |

| igure 17-7   | COM/SEG Signal in 1/3Duty and 1/2Bias Mode                                       |       |

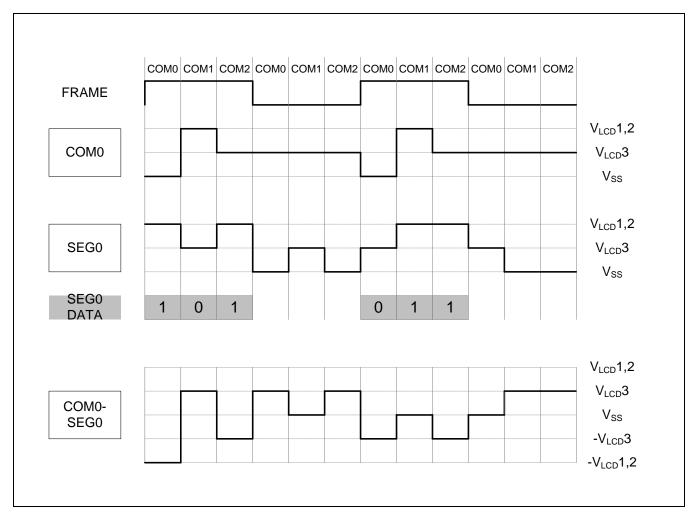

| igure 17-8   | COM/SEG Signal in 1/3Duty and 1/3Bias Mode                                       |       |

| Figure 17-9  | COM/SEG Signal in 1/4Duty and 1/3Bias Mode                                       | 17-11 |

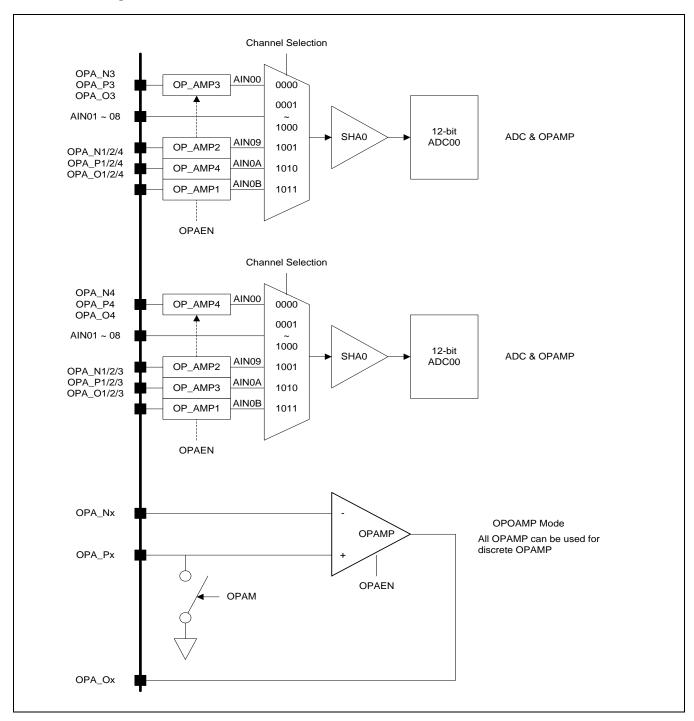

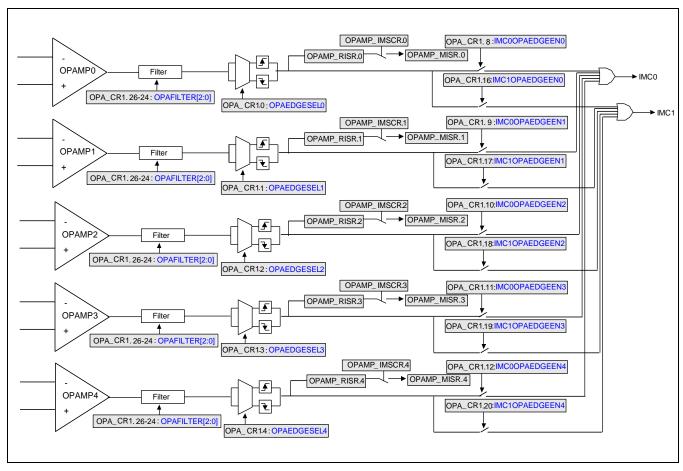

| igure 18-1   | OP-AMP Block Diagram                                                             | 18-2  |

| Figure 18-2  | Edge Detection Diagram                                                           |       |

| -iau no 40 4 | Drawaya Flook Block Biogram                                                      | 40.0  |

| igure 19-1   | Program Flash Block Diagram                                                      |       |

| Figure 19-2  | JTAG Interface Program                                                           |       |

| Figure 19-3  | UART Interface Program                                                           |       |

| Figure 19-4  | Comparison between UART Interface and Serial Interface                           |       |

| Figure 19-5  | Normal Program Flow Chart                                                        |       |

| igure 19-6   | Page Erase Flow Chart                                                            |       |

| igure 19-7   | Sector Erase Flow Chart                                                          |       |

| Figure 19-8  | Entire Program Flash Erase Flow Chart                                            |       |

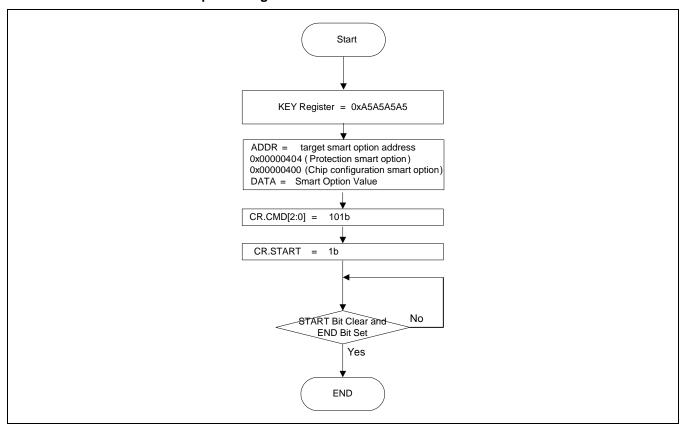

| Figure 19-9  | Smart Option Program Flow Chart                                                  |       |

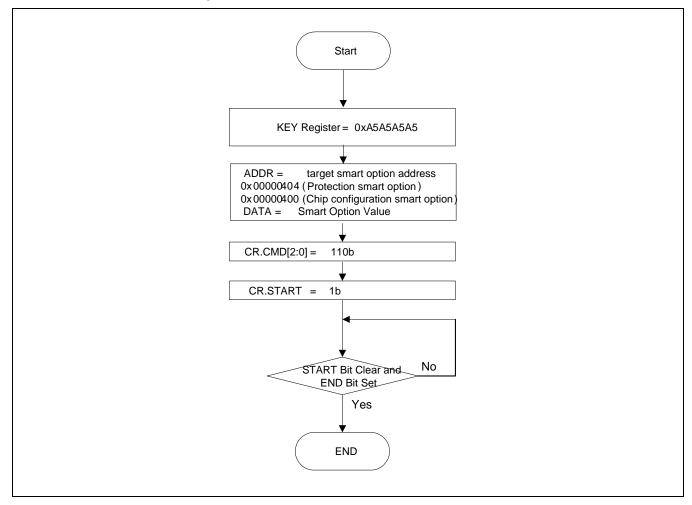

| Figure 19-10 | Smart Option Erase Flow Chart                                                    | 19-16 |

| Figure 20-1  | Pulse Width Modulation (PWM) Block Diagram                                       | 20-2  |

| Figure 20-2  | PWM Cycle Description                                                            | 20-3  |

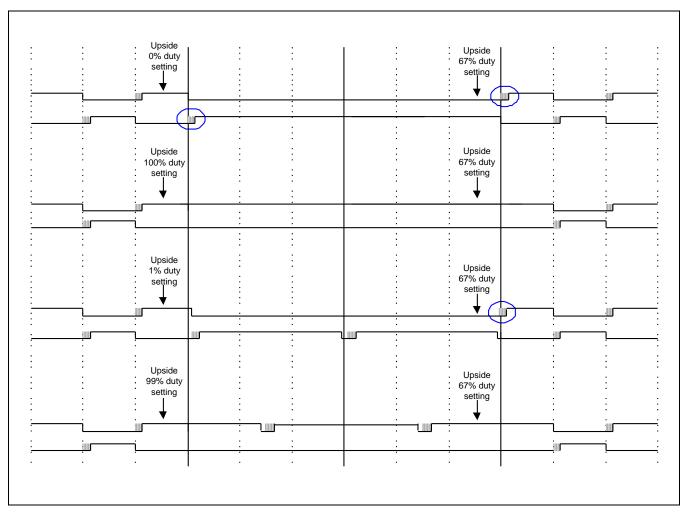

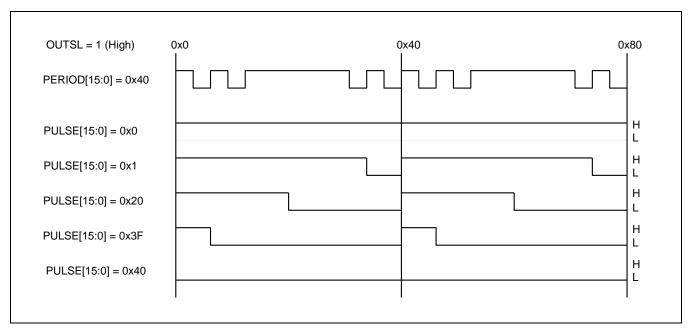

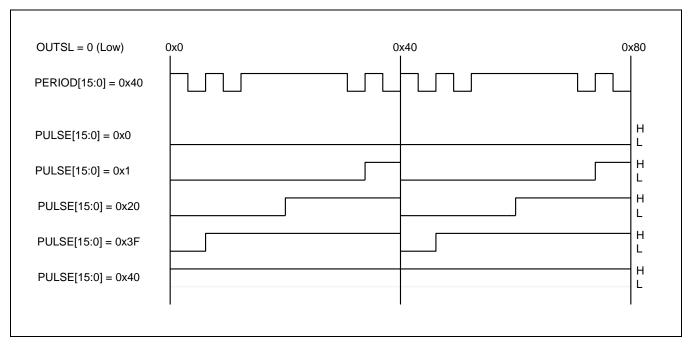

| Figure 20-3  | PWM Basic Waveform (OUTSL=1, PWM Period=0x40, Pulse=0x0, 0x1, 0x20, 0x3F, 0x40). |       |

| igure 20-4   | PWM Basic Waveform (OUTSL=0, PWM Period=0x40, Pulse=0x0, 0x1, 0x20, 0x3F, 0x40). |       |

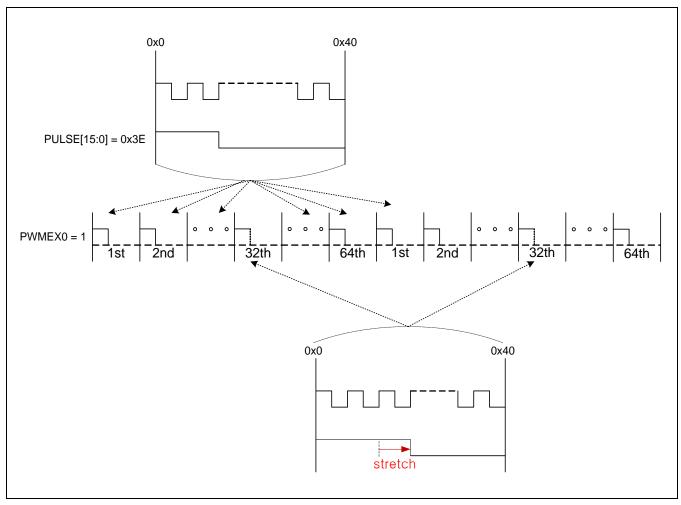

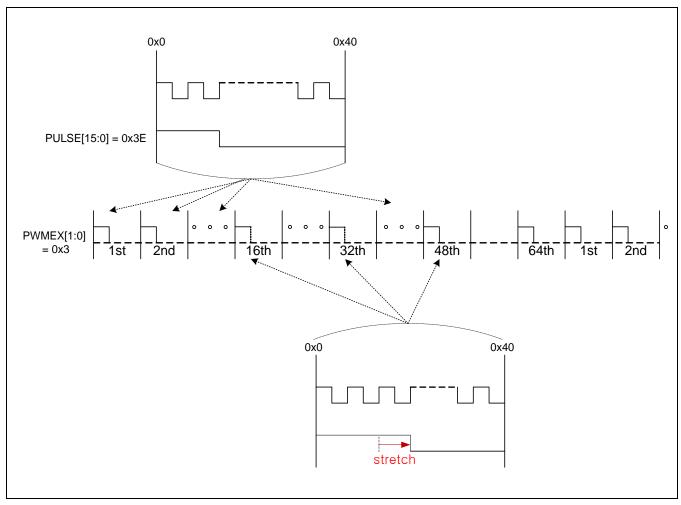

| Figure 20-5  | Extended PWM Waveform (PWM Period = 0x40, Pulse=0x3E, PWMEX0)            | 20-7  |

|--------------|--------------------------------------------------------------------------|-------|

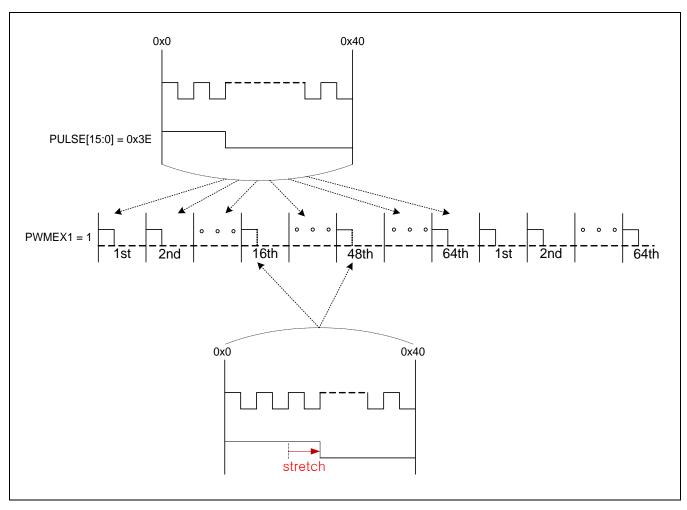

| Figure 20-6  | Extended PWM Waveform (PWM Period = 0x40, Pulse=0x3E, PWMEX1)            |       |

| Figure 20-7  | Extended PWM Waveform (PWM Period = 0x40, Pulse=0x3E, PWMEX1 and PWMEX   |       |

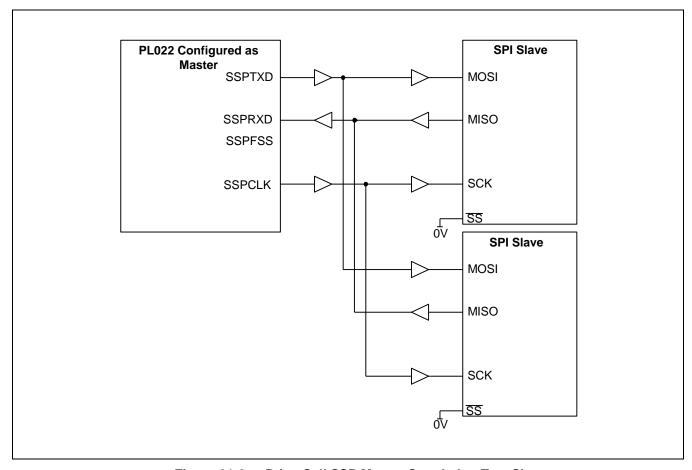

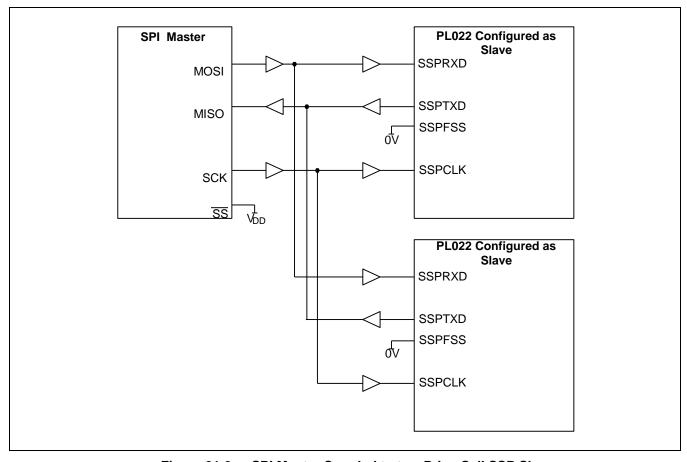

| Figure 21-1  | SSP Block Diagram                                                        | 21-3  |

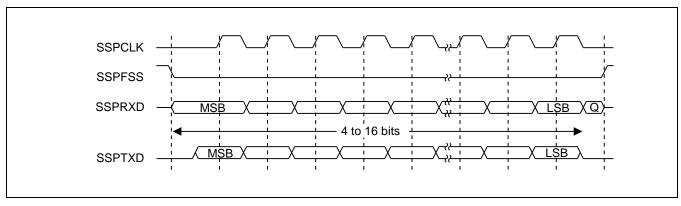

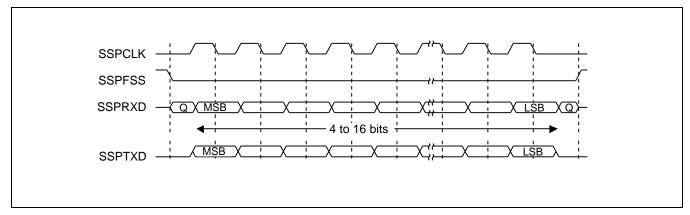

| Figure 21-2  | Motorola SPI Frame Format (Single Transfer) with SPO = 0 and SPH = 0     |       |

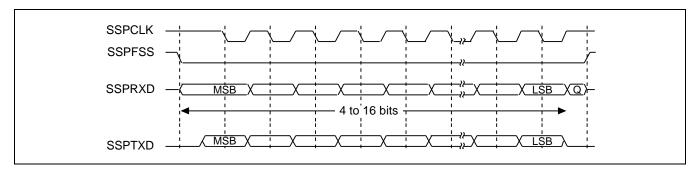

| Figure 21-3  | Motorola SPI Frame Format (Continuous Transfer) with SPO = 0 and SPH = 0 | 21-11 |

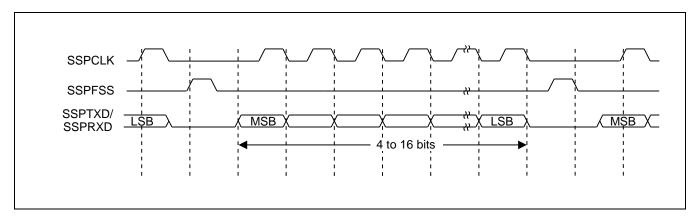

| Figure 21-4  | Motorola SPI Frame Format with SPO = 0 and SPH = 1                       | 21-12 |

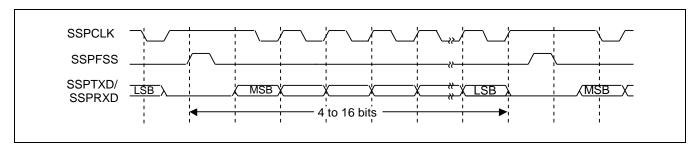

| Figure 21-5  | Motorola SPI Frame Format (Single Transfer) with SPO = 1 and SPH = 0     | 21-13 |

| Figure 21-6  | Motorola SPI Frame Format (Continuous Transfer) with SPO = 1 and SPH = 0 | 21-13 |

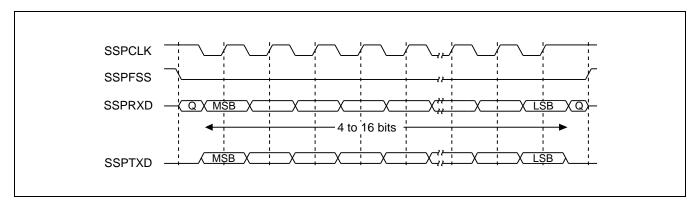

| Figure 21-7  | Motorola SPI Frame Format with SPO = 1 and SPH = 1                       | 21-14 |

| Figure 21-8  | PrimeCell SSP Master Coupled to Two Slaves                               | 21-15 |

| Figure 21-9  | SPI Master Coupled to two PrimeCell SSP Slaves                           |       |

| Figure 22-1  | Stamp Timer (STT) Block Diagram                                          | 22-2  |

| Figure 23-1  | TC Block Diagram                                                         | 23-2  |

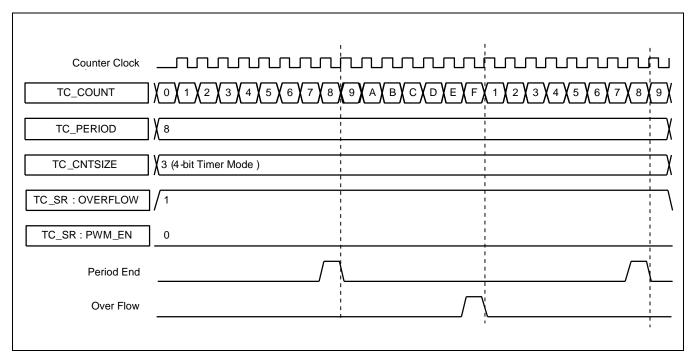

| Figure 23-2  | Simplified Timer Function Diagram: Match & Overflow Timer Mode           | 23-4  |

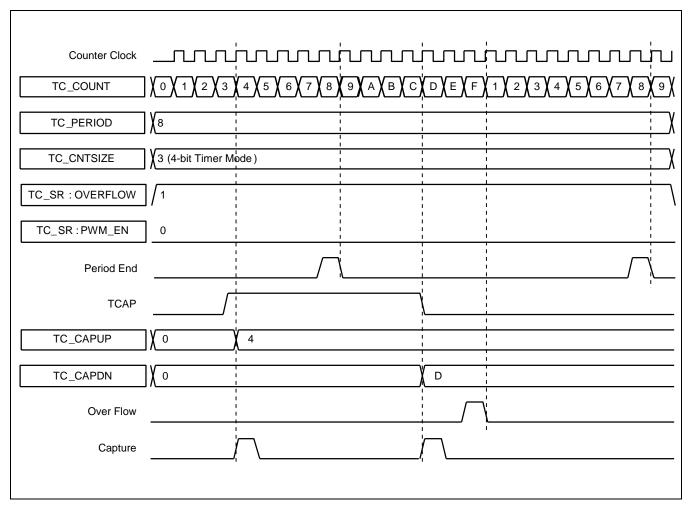

| Figure 23-3  | Simplified Timer Function Diagram: Capture Mode                          | 23-5  |

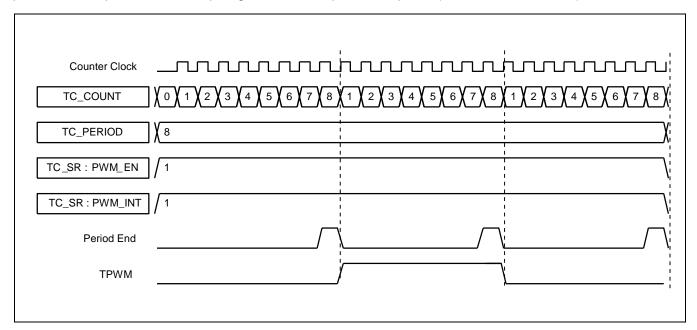

| Figure 23-4  | Simplified Timer Function Diagram: Interval Timer Mode                   | 23-6  |

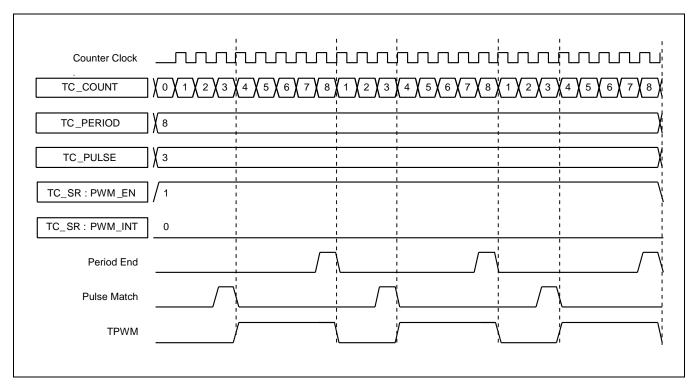

| Figure 23-5  | Simplified Timer Function Diagram: PWM Mode                              | 23-7  |

| Figure 24-1  | Template_REV1.08 USART Block Diagram                                     | 24-3  |

| Figure 24-2  | USART Baud Rate Generator Block Diagram                                  | 24-4  |

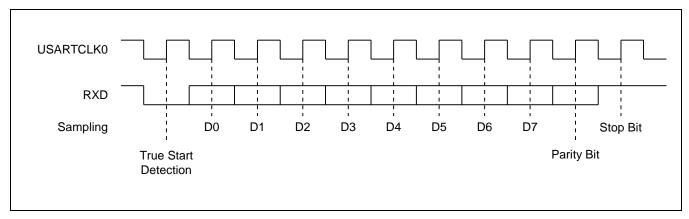

| Figure 24-3  | Asynchronous Mode, Start Bit Detection                                   |       |

| Figure 24-4  | Asynchronous Mode, Character Reception                                   |       |

| Figure 24-5  | Synchronous Mode, Character Reception                                    |       |

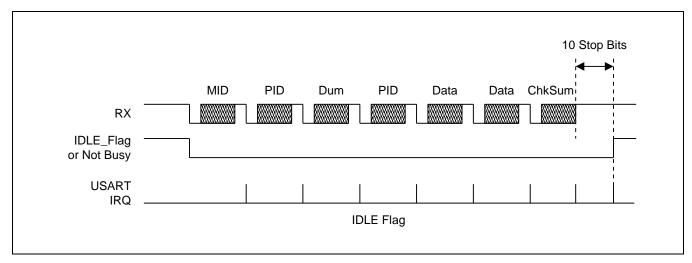

| Figure 24-6  | IDLE Flag                                                                |       |

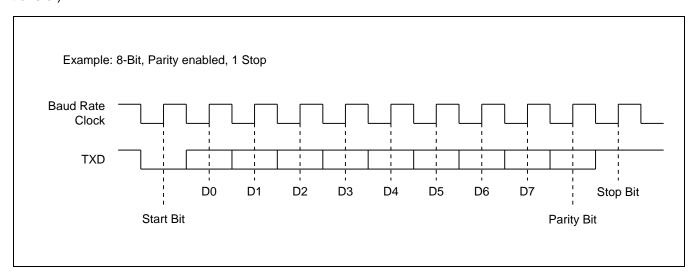

| Figure 24-7  | Synchronous and Asynchronous Modes, Character Transmission               |       |

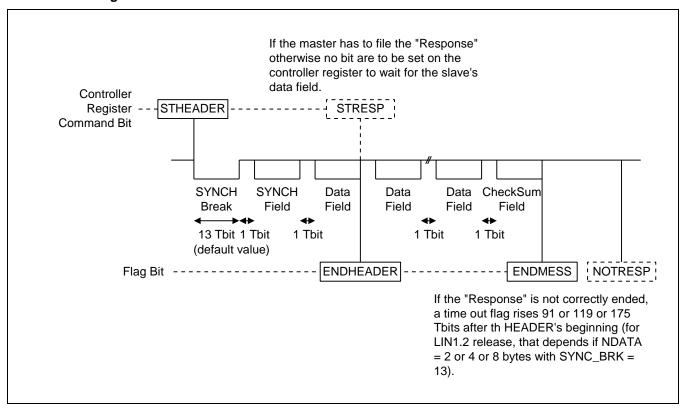

| Figure 24-8  | Message Characteristics                                                  |       |

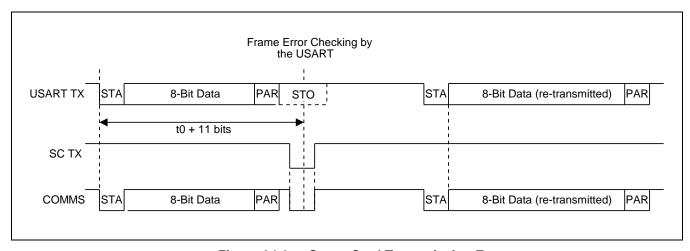

| Figure 24-9  | Smart-Card Transmission Error                                            |       |

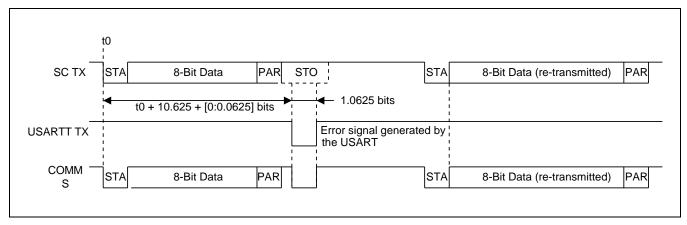

| Figure 24-10 | Error Signaling on Reception                                             | 24-22 |

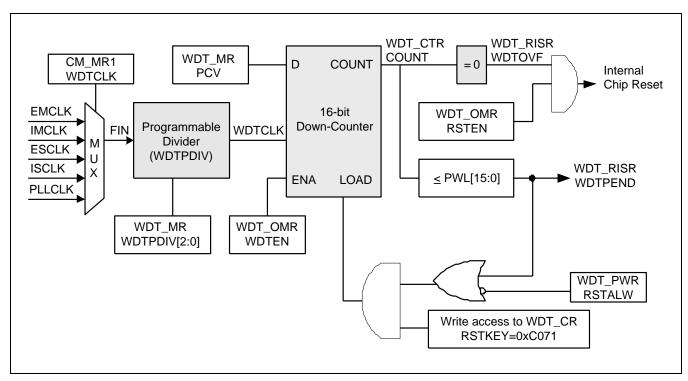

| Figure 25-1  | Watchdog Timer Block Diagram                                             | 25-2  |

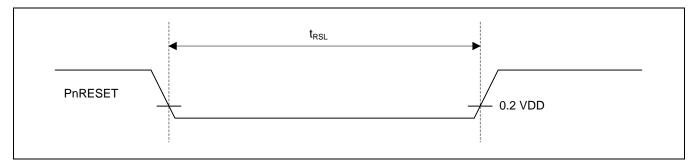

| Figure 26-1  | Input Timing for nRESET                                                  |       |

| Figure 26-2  | Input Timing for External Interrupt                                      | 26-5  |

| Figure 27-1  | 128ETQFP-1414 Package Dimension                                          | 27-2  |

## **List of Tables**

| Table<br>Number | Title                                                | Page<br>Number |

|-----------------|------------------------------------------------------|----------------|

| Table 2-1       | Pin Assignments – Pin Number Order                   | 2-2            |

| Table 3-1       | Memory Map                                           | 3-1            |

| Table 3-2       | Core Special Function Register Map                   |                |

| Table 3-3       | Peripheral Memory Map                                | 3-2            |

| Table 4-1       | ADC0 Pin Description                                 | 4-1            |

| Table 4-2       | ADC Input & Output Range                             |                |

| Table 4-3       | CCNT[2:0] Values and the Number of Conversions       |                |

| Table 4-4       | ICNUMx Values and Selected Input                     |                |

| Table 4-5       | ADC0 Control Special Function Registers              |                |

| Table 4-6       | CCNT[2:0] Values and the Count Value of Conversions  |                |

| Table 4-7       | ICNUMx[2:0] Values                                   | 4-21           |

| Table 5-1       | ADC1 Pin Description                                 |                |

| Table 5-2       | ADC1 Input & Output Range                            |                |

| Table 5-3       | CCNT[2:0] Values and the Number of Conversions       |                |

| Table 5-4       | ICNUMx Values and Selected Input                     |                |

| Table 5-5       | ADC1 Special Function Registers                      |                |

| Table 5-6       | CCNT[2:0] Values and the Count Value of Conversions  |                |

| Table 5-7       | ICNUMx[2:0] Values                                   | 5-19           |

| Table 6-1       | Controller Area Network (CAN) Pin Description        |                |

| Table 6-2       | Identifier Length within Standard and Extended Frame |                |

| Table 6-3       | RTR Bit                                              |                |

| Table 6-4       | IDE Bit                                              | 6-12           |

| Table 6-5       | Data Length Code (NOTE)                              | 6-13           |

| Table 6-6       | Interface Register Sets                              | 6-31           |

| Table 6-7       | Message Object Content                               |                |

| Table 6-8       | Initialization of a Transmit Object                  |                |

| Table 6-9       | Initialization of a Receive Object                   | 6-43           |

| Table 6-10      | Parameters of the CAN Bit Time                       | 6-47           |

| Table 6-11      | Bit rate and Minimal Core Frequency                  |                |

| Table 6-12      | Control of CAN_TX Pin                                | 6-96           |

| Table 7-1       | Summary of Smart Option for Clock Manager            | 7-4            |

| Table 7-2       | Clock Definition                                     | 7-5            |

| Table 7-3       | Clock Status at Reset and Wakeup                     | 7-5            |

| Table 7-4       | Operation Mode Definition                            | 7-6            |

| Table 7-5       | Clock Monitor Function                               | 7-13           |

| Table 7-6       | Clock Monitor Control                                | 7-13           |

| Table 7-7       | IDLE on Sleep-now                                    | 7-18           |

| Table 7-8       | IDLE on Sleep-on-Exit                                | 7-18           |

| Table 7-9       | Clock Status on STOP and Wakeup                      |                |

| Table 7-10      | Reset ID Flag                                        |                |

| Table 7-11      | The Wake-up Sources And Pin Assignment               |                |

| Table 9-1   | DMA Control Special Function Registers                               |       |

|-------------|----------------------------------------------------------------------|-------|

| Table 9-2   | The Cases by the Address Control                                     | 9-9   |

| Table 10-1  | ENC Pin Description                                                  | 10-1  |

| Table 12-1  | GPIO Pin Description                                                 | 12-2  |

| Table 13-1  | Inter-Integrated Circuit (IIC) Pin Description                       | 13-1  |

| Table 13-2  | Examples of Baud Rate Configuration                                  | 13-4  |

| Table 13-3  | Definition of Bytes in First Byte                                    | 13-11 |

| Table 13-4  | Timing Requirements                                                  |       |

| Table 13-5  | Values of FSCL in kHz Depending of PRV, FAST and PCLK                |       |

| Table 13-6  | Master/Transmitter Mode Status Codes                                 | 13-27 |

| Table 13-7  | Master/Receiver Mode Status Codes                                    |       |

| Table 13-8  | Slave/Receiver Mode Status Codes                                     | 13-29 |

| Table 13-9  | Slave/Transmitter Mode Status Codes                                  |       |

| Table 13-10 |                                                                      |       |

| Table 14-1  | IMC Pin Description                                                  | 14-1  |

| Table 15-1  | Core Exception Vector                                                | 15-3  |

| Table 15-2  | System Interrupt Vectors & Sources                                   | 15-4  |

| Table 16-1  | GPIO 0 Function Mode Configuration                                   | 16-2  |

| Table 16-2  | GPIO 1 Function Mode Configuration                                   |       |

| Table 16-3  | GPIO 2 Function Mode Configuration                                   | 16-4  |

| Table 16-4  | GPIO 3 Function Mode Configuration                                   |       |

| Table 17-1  | Pin Description                                                      | 17-1  |

| Table 17-2  | 4COM x 40SEG Display Memory Organization                             | 17-3  |

| Table 17-3  | LCD Drive voltage Values                                             | 17-4  |

| Table 18-1  | OP AMP Pin Description                                               | 18-1  |

| Table 19-1  | Protection Smart Option Address and Protection Bits                  | 19-6  |

| Table 19-2  | Hardware Protection Area Configuration                               |       |

| Table 19-3  | Used to Read/Write/Erase the Flash ROM with UART Interface           |       |

| Table 19-4  | The Pins Used to Read/Write/Erase the Flash ROM in Tool Program Mode | 19-10 |

| Table 20-1  | PWM Pin Description                                                  | 20-1  |

| Table 20-2  | PERIOD and PULSE Field Relationship                                  | 20-5  |

| Table 21-1  | SSP Pin Description                                                  | 21-2  |

| Table 23-1  | Pin Description                                                      | 23-1  |

| Table 24-1  | USART Pin Description                                                | 24-2  |

| Table 24-2  | Asynchronous Mode (SYNC = 0)                                         |       |

| Table 24-3  | Synchronous Mode (SYNC = 1)                                          |       |

| Table 24-4  | Asynchronous Mode (SYNC = 0)                                         |       |

| Table 26-1  | Absolute Maximum Ratings                                             | 26-1  |

| Table 26-2  | Recommended Operating Conditions                                     |       |

| Table 27-1 A | Absolute Maximum Ratings | 27- | -1 |

|--------------|--------------------------|-----|----|

|--------------|--------------------------|-----|----|

## **List of Conventions**

#### **Register RW Access Type Conventions**

| Туре | Definition   | Description                                                                                                                                             |

|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| R    | Read Only    | The application has permission to read the Register field. Writes to read-only fields have no effect.                                                   |

| W    | Write Only   | The application has permission to write in the Register field.                                                                                          |

| RW   | Read & Write | The application has permission to read and writes in the Register field. The application sets this field by writing 1'b1 and clears it by writing 1'b0. |

#### **Register Value Conventions**

| Expression       | Description                                        |

|------------------|----------------------------------------------------|

| Х                | Undefined bit                                      |

| X                | Undefined multiple bits                            |

| ?                | Undefined, but depends on the device or pin status |

| Device dependent | The value depends on the device                    |

| Pin value        | The value depends on the pin status                |

#### **Reset Value Conventions**

| Expression | Description |

|------------|-------------|

| 0          |             |

| 1          |             |

| Х          |             |

**Warning:** Some bits of control registers are driven by hardware or write only. As a result the indicated reset value and the read value after reset might be different.

Overview

#### 1.1 Purpose This Document

The purpose of this document is to provide a complete reference specification of S3FM02G.

#### 1.2 Instruction to S3FM02G

S3FM02G is a family of cost-effective and high-performance microcontrollers with Cortex<sup>TM</sup>-M3 designed by Advanced RISC Machines (ARM). This Microcontroller unit (MCU) applies to inverter motor control within the home applications.

- ARM Cortex<sup>TM</sup>-M3 Core

- Built-in up to 384 Kbytes Program Flash Memory

- Built-in up to 16 Kbytes Data Flash Memory

- Internal up to 24 Kbytes SRAM for stack, data memory, or code memory

- Operating temperature: -40 ~ 85 °C

- Operating voltage range: 2.7 ~ 5.5 V

- Interrupt controller: Dynamically reconfigurable Nested Vectored Interrupt Controller (NVIC)

- Clock and Power Controller (CM)

- 10ch x DMA Controller (DMAC)

- Watch-Dog Timer (WDT)

- 8ch x 16-bit Timer/Counters (TC)

- 32-bit Free-Running Timer (FRT)

- 8ch x 16-bit PWM

- 2ch x 16bit Encoder Counter (ENC)

- 2ch x 6-Phase Inverter Motor Controller (IMC)

- 2ch x I2C, 2ch x SSP, 2ch x CAN and 4ch x USART

- 12-bit ADC(4 channels with OP-AMP)

- 10-bit ADC

- 5ch OP-AMP

- 4com x 40seg LCD Controller (LCDC)

- Support Normal, High-speed, IDLE, and STOP mode

#### 1.3 Features

- CPU

- 32-bit RISC ARM Cortex<sup>TM</sup>-M3 Core

- ETM function embedded with ARM Cortex<sup>TM</sup>-M3

- SWD(Serial Wire Debug) and JTAG Debugging Solution

#### Memory

- Up to 384 Kbytes Internal Program Full Flash

- Up to 16 Kbytes Internal Data Flash

- Up to 24 Kbytes Internal SRAM

- Only little-endian support

- Interrupt Controller

- Supports Nested Vectored Interrupt Controller of Cortex<sup>TM</sup>-M3

- Dynamically reconfigurable Interrupt Priority (16 priority levels)

- Clock Manager (CM)

- External Oscillator 4 ~ 8MHz (EMCLK: External Main Clock) and 32.768KHz (ESCLK: External Sub-Clock)

- Internal Oscillator 8/16/20MHz (IMCLK: Internal Main Clock) and 32.768KHz (ISCLK: Internal Sub-Clock)

- Up to 75MHz by Phase-Locked Loop Control (PLL)

- Clock Monitor to detect an external main and sub-oscillator failure

- Support Low Power Mode (IDLE / STOP) by Clock Gating Control

- Programmable Clock Dividers (SDIV, PDIV)

- Reset Management

- Include basic timer for reset generation and STOP wake-up

- DMAC: Direct Memory Access Controller

- Up to 10 channels

- Transfer from Memory to Memory

- Transfer between Peripheral and Memory

- Transfer between Peripheral and Peripheral

- WDT: Watchdog Timer

- Configurable micro-controller reset event

- Programmable 16-bit down counter

- TC: 16-bit Timer/Counter

- Up to 8 channels (TC0 ~ TC7)

- Operation in an interval, capture, match & overflow, or PWM mode

- Match and overflow interrupt

- Selectable an internal or external timer clock

- FRT: Free Running Timer

- 32-bit Timer

- Can operate in stop mode with ISCLK, as an independent timer

- PWM: Pulse Width Modulation

- Up to 8 channels

- 16-bit PWM signal generation

- Interval Mode

- Programmable Idle Level

- Support extension PWM function

- ENC: Encoder Counter

- Up to 2 channels

- 3 input signals: PHASEA, PHASEB, and PHASEZ

- Support position counter and speed counter

- Up/Down counter

- Support capture mode

- IMC: Inverter Motor Controller

- UP to 2 channels

- Support 3-Phase 16-bit PWM generation

- Programmable dead time insertion

- ADC conversion start signal generation

- CAN: Controller Area Network

- CAN0/1 With 32 Buffers

- Support CAN 2.0A and 2.0B Full Speed

- Stampable Message

- USART: Universal Sync/Async Receiver Transmitter

- Up to 4 channels

- Support 5, 6, 7, and 8bit Data length

- Programmable baud rate generator

- Parity, framing and overrun error detection

- Support loop-back mode

- Support full duplex

- Idle flag for J1587 protocol

- Support LIN protocol: LIN1.2 or LIN 2.0 configurable release

- Smart-card protocol: Error signaling and re-transmission

- Dedicated DMA channel

- SSP: Serial Synchronous Peripheral Interface

- Up to 2 channels

- Programmable data frame from 4 to 16-bit

- Support Master and Slave Mode

- Programmable Clock Pre-scale

- Separate 16 x 32-bit width Transmit/Receive FIFO

- Dedicated DMA channel

- IIC: Inter-Integrated Circuit

- Up to 2 channels

- Multi-Master IIC-Bus

- Serial, 8-bit Oriented and Bi-directional Data Transfers

- 100Kbit/s in Standard Mode and up to 400Kbit/s in Fast mode

- Dedicated DMA channel

- ADC: A/D Converters

- Up to 16 channel's Analog Inputs

- 12-bit ADC0 x 2 and 10-bit ADC1

- 4 x Op-amp for 12-bit ADC input level amplification

- supports simultaneous sampling and conversion up to 2-input channels

- Dedicated DMA channel

- OP amp

- 5 ch OP amp

- Can be operated with ADC

- Edge detection function which is related with IMC

- LCDC: LCD Controller

- 4 com x 40 segment

- Static, 1/2 and 1/3 bias mode

- External and internal resistor bias

- General Purpose IO (GPIO)

- Disabling IO port enables the function of peripherals on pins

- Output Open-drain / Push-pull configuration

- Input Pull-up Resistor enable/disable configuration

- GPIO Interrupt

- Two Low Power Modes

- IDLE: Only CPU clock stops

- STOP: Selected system clock and CPU clock stop

- Fast wake-up with internal 8/16/20MHz oscillator (from STOP mode to normal mode)

- Programmable external event/interrupt sources for Wake-up

- POR: Power-On Reset

- LVD: Low Voltage Detection

- LVD for reset with configurable voltage levels

- LVD for interrupt with configurable voltage levels

- PLL: Phase-Locked Loop

- Input Frequency: 4 ~ 8 MHz

- Output Frequency: 8 ~ 75MHz

- Operating Voltage Range

- 2.7V ~ 5.5V

- Operating Frequency Range

- 4 ~ 8 MHz by external main oscillator clock

- 8/16/20MHz by internal main oscillator clock

- 32.768KHz external/internal sub-oscillator clock

- 8 ~ 75 MHz by PLL clock

- Operating Temperature Range

- -40 ~ 85 °C

- Available in 128 ETQFP Package

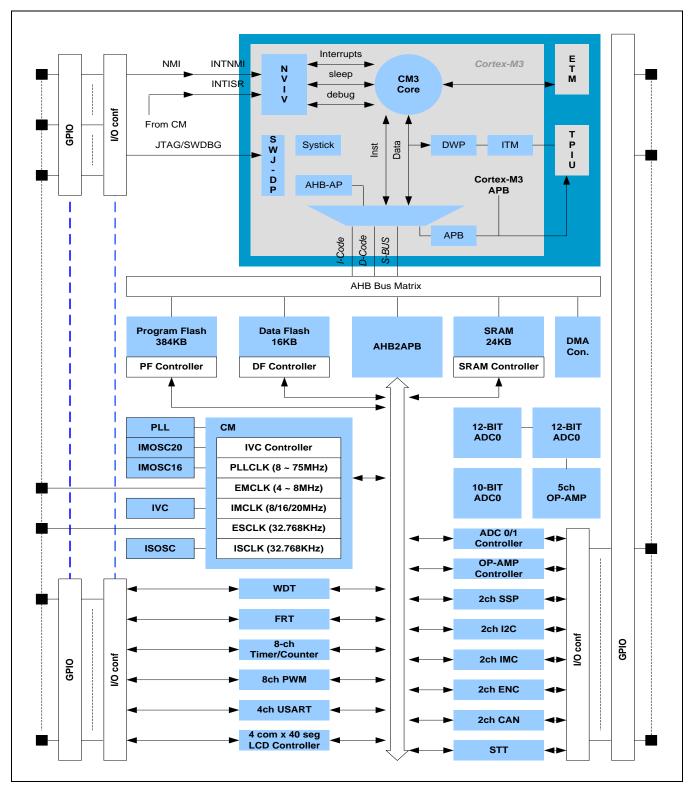

#### 1.4 Block Diagram

Figure 1-1 S3FM02G Block Diagram

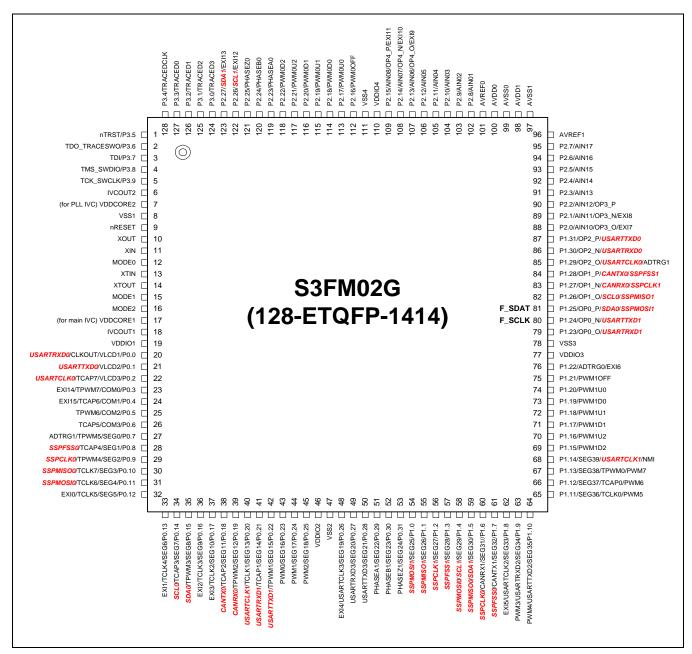

# Pin Configuration

#### 2.1 Pin Configuration

Figure 2-1 Pin Configuration

#### 2.2 Pin Assignments

- D: Digital, A: Analog

- IO: Input and Output (Bi-direction), O: Output, I: Input, P: Power, G: Ground

Table 2-1 Pin Assignments – Pin Number Order

|     | PIN Name          |                   |                   | Default           | PULL              | I/O state       |        |

|-----|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------|--------|

| Num | 1st               | 2nd               | 3rd               | 4th               | @RESET            | up/dn<br>@RESET | @RESET |

| 1   | P3.5              | nTRST             | _                 | _                 | nTRST             | PULL-UP         | I      |

| 2   | P3.6              | TDO/TRACESWO      | П                 | -                 | TDO/<br>TRACESWO  | -               | 0      |

| 3   | P3.7              | TDI               |                   | _                 | TDI               | PULL-UP         | Ţ      |

| 4   | P3.8              | TMS/SWDIO         |                   | _                 | TMS/SWDIO         | PULL-UP         | 1      |

| 5   | P3.9              | TCK/SWCLK         |                   | _                 | TCK/SWCLK         | PULL-UP         | Ţ      |

| 6   | IVCOUT2           | IVCOUT2           | IVCOUT2           | IVCOUT2           | IVCOUT2           | _               | 0      |

| 7   | VDDCORE2          | VDDCORE2          | VDDCORE2          | VDDCORE2          | VDDCORE2          | _               | Р      |

| 8   | VSS1              | VSS1              | VSS1              | VSS1              | VSS1              | _               | G      |

| 9   | nRESET            | nRESET            | nRESET            | nRESET            | nRESET            | PULL-UP         | I      |

| 10  | X <sub>OUT</sub>  | _               | 0      |

| 11  | X <sub>IN</sub>   | _               | I      |

| 12  | MODE0             | MODE0             | MODE0             | MODE0             | MODE0             | PULL-DN         | 1      |

| 13  | X <sub>TIN</sub>  | _               | 1      |

| 14  | X <sub>TOUT</sub> | _               | 0      |

| 15  | MODE1             | MODE1             | MODE1             | MODE1             | MODE1             | PULL-DN         | I      |

| 16  | MODE2             | MODE2             | MODE2             | MODE2             | MODE2             | PULL-DN         | I      |

| 17  | VDDCORE1          | VDDCORE1          | VDDCORE1          | VDDCORE1          | VDDCORE1          | _               | Р      |

| 18  | IVCOUT1           | IVCOUT1           | IVCOUT1           | IVCOUT1           | IVCOUT1           | _               | 0      |

| 19  | VDDIO1            | VDDIO1            | VDDIO1            | VDDIO1            | VDDIO1            | _               | Р      |

| 20  | P0.0              | VLCD1             | CLKOUT            | USARTRXD0         | P0.0              | _               | 1      |

| 21  | P0.1              | VLCD2             |                   | USARTTXD0         | P0.1              | _               | I      |

| 22  | P0.2              | VLCD3             | TCAP7             | USARTCLK0         | P0.2              | _               | 1      |

| 23  | P0.3              | COM0              | TPWM7             | EXI14             | P0.3              | _               | 1      |

| 24  | P0.4              | COM1              | TCAP6             | EXI15             | P0.4              | _               | 1      |

| 25  | P0.5              | COM2              | TPWM6             | _                 | P0.5              | _               | I      |

| 26  | P0.6              | СОМЗ              | TCAP5             | _                 | P0.6              | _               | I      |

| 27  | P0.7              | SEG0              | TPWM5             | ADTRG1            | P0.7              | _               | I      |

| 28  | P0.8              | SEG1              | TCAP4             | SSPFSS0           | P0.8              | _               | I      |

| 29  | P0.9              | SEG2              | TPWM4             | SSPCLK0           | P0.9              | _               | 1      |

|     |        | PIN N  | ame       |           | Default | PULL            | I/O state |

|-----|--------|--------|-----------|-----------|---------|-----------------|-----------|

| Num | 1st    | 2nd    | 3rd       | 4th       | @RESET  | up/dn<br>@RESET | @RESET    |

| 30  | P0.10  | SEG3   | TCLK7     | SSPMISO0  | P0.10   | -               | I         |

| 31  | P0.11  | SEG4   | TCLK6     | SSPMOSI0  | P0.11   | _               | I         |

| 32  | P0.12  | SEG5   | TCLK5     | EXI0      | P0.12   | _               | I         |

| 33  | P0.13  | SEG6   | TCLK4     | EXI1      | P0.13   | _               | I         |

| 34  | P0.14  | SEG7   | TCAP3     | SCL0      | P0.14   | _               | I         |

| 35  | P0.15  | SEG8   | TPWM3     | SDA0      | P0.15   |                 | I         |

| 36  | P0.16  | SEG9   | TCLK3     | EXI2      | P0.16   | _               | I         |

| 37  | P0.17  | SEG10  | TCLK2     | EXI3      | P0.17   | _               | I         |

| 38  | P0.18  | SEG11  | TCAP2     | CANTX0    | P0.18   | _               | I         |

| 39  | P0.19  | SEG12  | TPWM2     | CANRX0    | P0.19   | -               | I         |

| 40  | P0.20  | SEG13  | TCLK1     | USARTCLK1 | P0.20   | -               | I         |

| 41  | P0.21  | SEG14  | TCAP1     | USARTRXD1 | P0.21   | -               | I         |

| 42  | P0.22  | SEG15  | TPWM1     | USARTTXD1 | P0.22   | _               | I         |

| 43  | P0.23  | SEG16  | PWM0      | _         | P0.23   | _               | I         |

| 44  | P0.24  | SEG17  | PWM1      | _         | P0.24   | -               | I         |

| 45  | P0.25  | SEG18  | PWM2      | _         | P0.25   | _               | I         |

| 46  | VDDIO2 | VDDIO2 | VDDIO2    | VDDIO2    | VDDIO2  | _               | Р         |

| 47  | VSS2   | VSS2   | VSS2      | VSS2      | VSS2    | _               | G         |

| 48  | P0.26  | SEG19  | USARTCLK3 | EXI4      | P0.26   | _               | I         |

| 49  | P0.27  | SEG20  | USARTRXD3 | _         | P0.27   | _               | I         |

| 50  | P0.28  | SEG21  | USARTTXD3 | _         | P0.28   | -               | I         |

| 51  | P0.29  | SEG22  | PHASEA1   | _         | P0.29   | _               | I         |

| 52  | P0.30  | SEG23  | PHASEB1   | _         | P0.30   | -               | I         |

| 53  | P0.31  | SEG24  | PHASEZ1   | _         | P0.31   | -               | I         |

| 54  | P1.0   | SEG25  | SSPMOSI1  | _         | P1.0    | _               | I         |

| 55  | P1.1   | SEG26  | SSPMISO1  | _         | P1.1    | _               | I         |

| 56  | P1.2   | SEG27  | SSPCLK1   | _         | P1.2    | _               | I         |

| 57  | P1.3   | SEG28  | SSPFSS1   | -         | P1.3    | _               | I         |

| 58  | P1.4   | SEG29  | SCL1      | SSPMOSI0  | P1.4    | _               | I         |

| 59  | P1.5   | SEG30  | SDA1      | SSPMISO0  | P1.5    | _               | I         |

| 60  | P1.6   | SEG31  | CANRX1    | SSPCLK0   | P1.6    | _               | I         |

| 61  | P1.7   | SEG32  | CANTX1    | SSPFSS0   | P1.7    | _               | I         |

| 62  | P1.8   | SEG33  | USARTCLK2 | EXI5      | P1.8    | -               | I         |

| 63  | P1.9   | SEG34  | USARTRXD2 | PWM3      | P1.9    | _               | I         |

| 64  | P1.10  | SEG35  | USARTTXD2 | PWM4      | P1.10   | _               | I         |

|     |        | PIN N   | PIN Name  |          |                   | PULL            | I/O state |

|-----|--------|---------|-----------|----------|-------------------|-----------------|-----------|

| Num | 1st    | 2nd     | 3rd       | 4th      | Default<br>@RESET | up/dn<br>@RESET | @RESET    |

| 65  | P1.11  | SEG36   | TCLK0     | PWM5     | P1.11             | -               | I         |

| 66  | P1.12  | SEG37   | TCAP0     | PWM6     | P1.12             | -               | I         |

| 67  | P1.13  | SEG38   | TPWM0     | PWM7     | P1.13             | -               | I         |

| 68  | P1.14  | SEG39   | USARTCLK1 | NMI      | P1.14             | -               | I         |

| 69  | P1.15  | PWM1D2  | _         | -        | P1.15             | _               | I         |

| 70  | P1.16  | PWM1U2  | -         | _        | P1.16             | _               | I         |

| 71  | P1.17  | PWM1D1  | _         | _        | P1.17             | _               | I         |

| 72  | P1.18  | PWM1U1  | _         | _        | P1.18             | -               | I         |

| 73  | P1.19  | PWM1D0  | _         | _        | P1.19             | -               | I         |

| 74  | P1.20  | PWM1U0  | _         | _        | P1.20             | -               | I         |

| 75  | P1.21  | PWM1OFF | _         | -        | P1.21             | _               | I         |

| 76  | P1.22  | ADTRG0  | EXI6      | _        | P1.22             | _               | I         |

| 77  | VDDIO3 | VDDIO3  | VDDIO3    | VDDIO3   | VDDIO3            | _               | Р         |

| 78  | VSS3   | VSS3    | VSS3      | VSS3     | VSS3              | _               | G         |

| 79  | P1.23  | OP0_O   | USARTRXD1 | -        | P1.23             | _               | I         |

| 80  | P1.24  | OP0_N   | USARTTXD1 | _        | P1.24             | _               | ı         |

| 81  | P1.25  | OP0_P   | SDA0      | SSPMOSI1 | P1.25             | _               | I         |

| 82  | P1.26  | OP1_O   | SCL0      | SSPMISO1 | P1.26             | _               | I         |

| 83  | P1.27  | OP1_N   | CANRX0    | SSPCLK1  | P1.27             | _               | I         |

| 84  | P1.28  | OP1_P   | CANTX0    | SSPFSS1  | P1.28             | -               | I         |

| 85  | P1.29  | OP2_O   | USARTCLK0 | ADTRG1   | P1.29             | -               | I         |

| 86  | P1.30  | OP2_N   | USARTRXD0 | _        | P1.30             | _               | I         |

| 87  | P1.31  | OP2_P   | USARTXD0  | _        | P1.31             | -               | I         |

| 88  | P2.0   | AIN10   | OP3_O     | EXI7     | P2.0              | -               | I         |

| 89  | P2.1   | AIN11   | OP3_N     | EXI8     | P2.1              | -               | I         |

| 90  | P2.2   | AIN12   | OP3_P     | _        | P2.2              | -               | I         |

| 91  | P2.3   | AIN13   | _         | _        | P2.3              | -               | I         |

| 92  | P2.4   | AIN14   | _         | -        | P2.4              | _               | I         |

| 93  | P2.5   | AIN15   | _         | -        | P2.5              | _               | I         |

| 94  | P2.6   | AIN16   | _         | -        | P2.6              | _               | I         |

| 95  | P2.7   | AIN17   | _         | _        | P2.7              | _               | I         |

| 96  | AVREF1 | AVREF1  | AVREF1    | AVREF1   | AVREF1            | _               | I         |

| 97  | AVSS1  | AVSS1   | AVSS1     | AVSS1    | AVSS1             | _               | G         |

| 98  | AVDD1  | AVDD1   | AVDD1     | AVDD1    | AVDD1             | _               | Р         |

| 99  | AVSS0  | AVSS0   | AVSS0     | AVSS0    | AVSS0             | _               | G         |

|     |        | PIN Na   | Default | PULL   | I/O state |                 |        |

|-----|--------|----------|---------|--------|-----------|-----------------|--------|

| Num | 1st    | 2nd      | 3rd     | 4th    | @RESET    | up/dn<br>@RESET | @RESET |

| 100 | AVDD0  | AVDD0    | AVDD0   | AVDD0  | AVDD0     | -               | Р      |

| 101 | AVREF0 | AVREF0   | AVREF0  | AVREF0 | AVREF0    | -               | I      |

| 102 | P2.8   | AIN01    | _       | -      | P2.8      | -               | 1      |

| 103 | P2.9   | AIN02    | _       | -      | P2.9      | -               | 1      |

| 104 | P2.10  | AIN03    | _       | -      | P2.10     | -               | 1      |

| 105 | P2.11  | AIN04    | _       | -      | P2.11     | -               | 1      |

| 106 | P2.12  | AIN05    | _       | -      | P2.12     | -               | I      |

| 107 | P2.13  | AIN06    | OP4_O   | EXI9   | P2.13     | -               | 1      |

| 108 | P2.14  | AIN07    | OP4_N   | EXI10  | P2.14     | -               | 1      |

| 109 | P2.15  | AIN08    | OP4_P   | EXI11  | P2.15     | _               | I      |

| 110 | VDDIO4 | VDDIO4   | VDDIO4  | VDDIO4 | VDDIO4    | -               | Р      |

| 111 | VSS4   | VSS4     | VSS4    | VSS4   | VSS4      | -               | G      |

| 112 | P2.16  | PWM0OFF  | _       | _      | P2.16     | -               | I      |

| 113 | P2.17  | PWM0U0   | _       | -      | P2.17     | -               | 1      |

| 114 | P2.18  | PWM0D0   | _       | -      | P2.18     | _               | 1      |

| 115 | P2.19  | PWM0U1   | _       | -      | P2.19     | -               | 1      |

| 116 | P2.20  | PWM0D1   | _       | _      | P2.20     | _               | I      |

| 117 | P2.21  | PWM0U2   | _       | -      | P2.21     | _               | I      |

| 118 | P2.22  | PWM0D2   | _       | -      | P2.22     | -               | I      |

| 119 | P2.23  | PHASEA0  | _       | -      | P2.23     | -               | I      |

| 120 | P2.24  | PHASEB0  | _       | -      | P2.24     | _               | I      |

| 121 | P2.25  | PHASEZ0  | _       | -      | P2.25     | -               | I      |

| 122 | P2.26  | SCL1     | EXI12   | -      | P2.26     | -               | I      |

| 123 | P2.27  | SDA1     | EXI13   | _      | P2.27     | -               | I      |

| 124 | P3.0   | TRACED3  | _       | -      | P3.0      | -               | I      |

| 125 | P3.1   | TRACED2  | _       | -      | P3.1      | -               | I      |

| 126 | P3.2   | TRACED1  | _       | _      | P3.2      | _               | I      |

| 127 | P3.3   | TRACED0  | _       | -      | P3.3      | -               | I      |

| 128 | P3.4   | TRACECLK | _       | _      | P3.4      | -               | I      |

#### 2.3 Pin Description

- D: Digital, A: Analog

- IO: Input and Output (Bi-direction), O: Output, I: Input, P: Power, G: Ground

#### 2.3.1 Miscellaneous

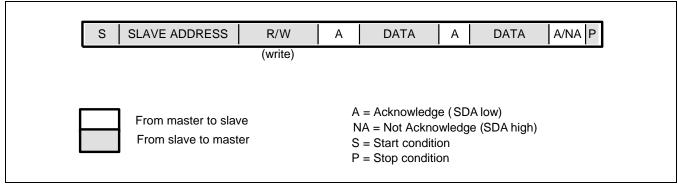

| Name      | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                  | D/A |