# VERSA1: FULLY INTEGRATED MICROCONTROLLER WITH DSP

**Datasheet Rev 3.4**

1

# **VERSA1: FULLY INTEGRATED MICROCONTROLLER WITH DSP**

# **Table of Contents**

| TABLE OF CONTENTS                                            |    |

|--------------------------------------------------------------|----|

| OVERVIEW                                                     |    |

|                                                              |    |

| APPLICATIONS                                                 |    |

| FUNCTIONAL DIA GRAM                                          | 2  |

| FEATURES                                                     |    |

| PINS DESCRIPTION                                             | -  |

| PIN CONFIGURATION                                            |    |

| ABSOLUTE MAXIMUM RATINGS                                     |    |

| ELECTRICAL CHARACTERISTICS                                   |    |

| DETAILED DESCRIPTION                                         |    |

|                                                              |    |

| Memory Organization                                          |    |

| Dual Data Pointers                                           |    |

| Programming interface                                        |    |

| CPU Timing                                                   |    |

| Instruction Timing                                           |    |

| Performance Overview                                         |    |

| Instruction Set                                              |    |

| PERIPHERAL INTERFACES                                        | 15 |

| SPECIAL FUNCTION REGISTERS                                   |    |

|                                                              |    |

| TIMERS/COUNTERS                                              |    |

| TIMERS 0 AND 1                                               |    |

|                                                              |    |

| Model                                                        |    |

| Mode 2                                                       |    |

| Mode 3                                                       |    |

| TIMERS 0, 1, 2 RATE CONTROL                                  |    |

| Timer 2 Mode Control                                         |    |

| Timer 2 Mode Control                                         |    |

| Timer 2 To-bit Timer Modes  Timer 2 Baud Rate Generator Mode |    |

|                                                              |    |

| Serial Interface                                             |    |

| 1 11 0                                                       |    |

| Mode 1  Mode 1 Baud Rate Using Timer 1                       |    |

| Mode 1 Baud Rate Using Timer 1 (serial port 0 only)          |    |

| Mode 1 Transmit                                              |    |

| Mode 1 Receive                                               |    |

| Mode 2                                                       |    |

| Mode 2 Transmit                                              |    |

| Mode 2 Receive                                               |    |

| Mode 3                                                       |    |

| Multiprocessor Communications                                |    |

| BIT ADDRESSING                                               |    |

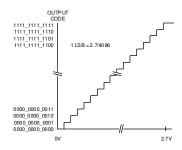

| ANALOG SIGNAL PATH O VERVIEW                                 |    |

| A/D CONVERTER                                                |    |

| SETTING UP THE VERS A1 ADC                                   |    |

| INTERNAL BANDGAP REFERENCE AND PGA                           |    |

| PROGRAMMABLE CURRENT SOURCE                                  |    |

| OTPR MEMORY CALIBRATION VECTORS                              |    |

| VERSA1'S ANA LOG SIGNAL PATH CONTROL SFRS                    |    |

| SPI INTERFACE.                                               |    |

| ~                                                            |    |

| MAC                     | 4                           |

|-------------------------|-----------------------------|

| Using the MAC           | 4                           |

| GENERAL PURPOSE I/O     | 4                           |

| INTERRUPTS              |                             |

| Interrupt Priorities    | 4                           |

| Interrupt Processing    | 4                           |

| Interrupt Masking       |                             |

| Interrupt SFRs          | 5                           |

| Interrupt Sampling      | 5                           |

| Interrupt Latency       | 5                           |

| Single-Step Operation   | 5                           |

| ESET                    |                             |

| Power On Reset          | 5                           |

| STANDARD RESET          |                             |

| POWER SAVING MODES      | 5                           |

| CLOCK CONTROL CIRCUITRY |                             |

| PACKAGE INFORMATION     | 5                           |

| ORDERING INFORMATION    | 5                           |

| ERRATA                  | ERROR! BOOKMARK NOT DEFINED |

| DISCLAIMER              | 5                           |

## FULLY INTEGRATED MICROCONTROLLER WITH DSP

## **Overview**

The VERSA1 is a fully integrated microcontroller based data acquisition system that includes a set of non-traditional on-chip components such as a programmable constant current source driver and a MAC block. The current source driver can be used to excite traditional components such as resistive bridges or thermistors. The MAC block allows the user to perform mathematical calculations to a much higher degree of accuracy and speed than standard microcontroller look-up table based methods.

## **Applications**

- Automotive Applications

- Medical Devices

- o Industrial Controls / Measurement Systems

- o Intelligent Sensors / Instrumentation

- o Consumer Products

- Battery Powered Systems (Instruments, Monitors)

- Pattern Recognition

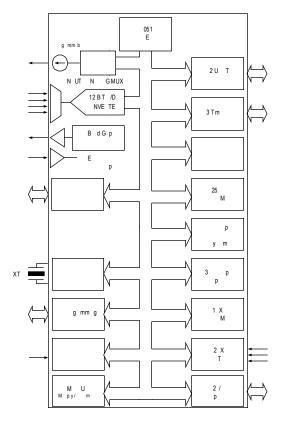

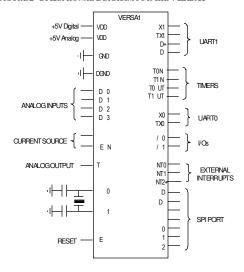

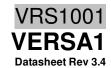

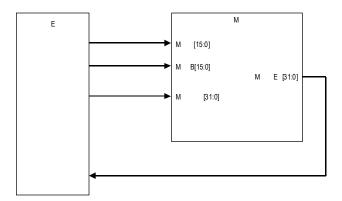

## **Functional Diagram**

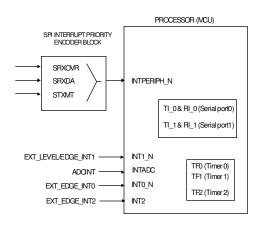

The following figure shows the functional diagram of the VERSA1.

## **Features**

- 8051 Compatible μProcessor

- Standard 8051 Instruction Set

- Dual Data Pointers

- 4 Clocks/Instruction

- Supports industry standard compilers, assemblers, ROM monitors

- o DSP Function via MAC (Multiply/Accumulate Unit)

- On-chip Flash Memory

- 64Kx8 Program/Storage Memory

- 2Kx8 OTPR Storage Memory Block

- In Circuit Flash Programming

- On-chip RAM

- 256x8 RAM Mapped into Internal RAM

- 1Kx8 RAM Mapped into External Memory Space

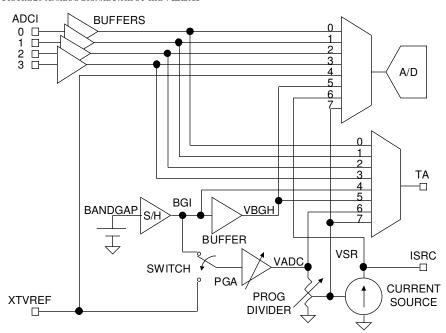

- o 4 Channel Calibrated 12-bit A/D Converter

- 0-2.7 Volts Input Range

- Programmable Continuous Free-Running Conversion with Interrupt to Processor

- Programmable One-Shot Conversion mode

- On-Chip Temperature Calibrated Reference Voltage

- o Analog Output/Reference Loop-Back

- Programmable Current Source

- 2 Full Duplex Asynchronous UARTS

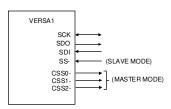

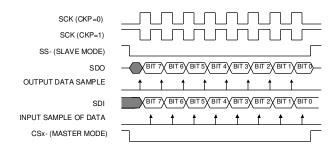

- SPIBus (Master/Slave)

- 3 Addressable Chip Enable Outputs for Controlling Multiple Slaves (Master Mode)

- 2 General Purpose I/Os

- 3 Interrupt Inputs

- o 3 General Purpose Timers/Counters

- Power Saving Features

- Power-on Reset with Brown-Out Detect

- Availlable in Commercial and Industrial temperature versions

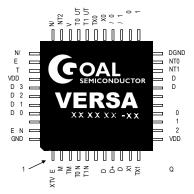

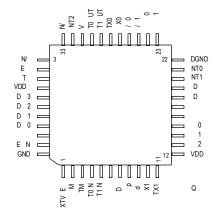

## **VERSA1 Pinout**

0

## **Pins Description**

TABLE 1 PIN OUT DESCRIPTION

| PIN | NAME   | FUNCTION                                                |

|-----|--------|---------------------------------------------------------|

|     |        |                                                         |

| 1   | XTVREF | External Reference Voltage Input (optional)             |

| 2   | PM     | Mode Control Input                                      |

| 3   | FTM    | Mode Control Input                                      |

| 4   | T0IN   | Timer 0 Input                                           |

| 5   | T1 IN  | Timer 1 Input                                           |

| 6   | SCL    | Prog. Interface Clock Input                             |

| 7   | SDA    | Prog. Interface Bi-directional Data Bus                 |

| 8   | Pup    | Put 10K to 100K pull-up to VDD                          |

| 9   | Pdn    | Put 10K to 100K pull-down to GND                        |

| 10  | RX1    | Asynchronous UART1 Receiver Input                       |

| 11  | TX1    | Asynchronous UART1 Transmitter<br>Output                |

| 12  | VDD    | Digital Logic Supply Input                              |

| 13  | CS2-   | SPI Chip Enable Output (Master Mode)                    |

| 14  | CS1-   | SPI Chip Enable Output (Master Mode)                    |

| 15  | CS0-   | SPI Chip Enable Output (Master Mode)                    |

| 16  | SS-    | SPI Chip Enable Input (Slave Mode)                      |

| 17  | SCK    | SPI Clock (Input in Slave Mode, Output in Master Mode)  |

| 18  | SDO    | SPI Data Output Bus                                     |

| 19  | SDI    | SPI Data Input Bus                                      |

| 20  | INT1-  | Interrupt Input (Negative Level Triggered)              |

| 21  | INT0-  | Interrupt Input (Negative Level or Edge Triggered)      |

| 22  | DGND   | Digital Ground                                          |

| 23  | OSC1   | Oscillator Crystal Output                               |

| 24  | OSC0   | Oscillator Crystal Input/External Clock<br>Source Input |

| 25  | I/O1   | Programmable I/O                                        |

| 26  | I/O0   | Programmable I/O                                        |

| 27  | RX0    | Asynchronous UART0 Receiver Input                       |

| 28  | TX0    | Asynchronous UART0 Transmitter Output                   |

| 29  | T1OUT  | Timer 1 Output                                          |

| 30  | T0OUT  | Timer 0 Output                                          |

| PIN | NAME  | FUNCTION                                  |

|-----|-------|-------------------------------------------|

| 31  | VPP   | Flash Programming Voltage Input           |

| 32  | INT2  | Interrupt Input (Positive Edge Triggered) |

| 33  | N/C   | No Connection (leave pin unconnected)     |

| 34  | N/C   | No Connection (leave pin unconnected)     |

| 35  | RES-  | Hardware Reset Input                      |

| 36  | TA    | Analog Output                             |

| 37  | VDDA  | Analog Supply Input                       |

| 38  | ADCI3 | Analog Input for Channel 3                |

| 39  | ADCI2 | Analog Input for Channel 2                |

| 40  | ADCI1 | Analog Input for Channel 1                |

| 41  | ADCI0 | Analog Input for Channel 0                |

| 42  | ISRC  | Programmable Current Source Output        |

| 43  | RESIN | Current Source Reference Input            |

| 44  | AGND  | Analog Ground                             |

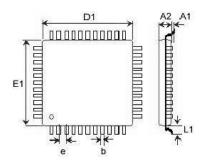

# **Pin Configuration**

## FIGURE 1 VERSA1 PINOUT

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to DGND       | -0.3V, +6V              | Digital Output Voltage to DGND         | $-0.3V, V_{DD}+0.3V$ |

|-------------------------------|-------------------------|----------------------------------------|----------------------|

| V <sub>DDA</sub> to DGND      | -0.3V, +6V              | V <sub>PP</sub> to DGND                | +13V                 |

| AGND to DGND                  | -0.3V, +0.3V            | Power Dissipation                      |                      |

| $V_{DD}$ to $V_{DDA}$         | -0.3V, +0.3V            | o To +75 ℃                             | 1000mW               |

| ADCI (0-3) to AGND            | $-0.3V, V_{DDA} + 0.3V$ | <ul> <li>Derate above +75 ℃</li> </ul> | 10mW/℃               |

| XTVREF to AGND                | $-0.3V, V_{DDA} + 0.3V$ | Operating Temperature range            | -40°to +85℃          |

| Digital Input Voltage to DGND | $-0.3V, V_{DD} + 0.3V$  | Storage Temperature Range              | –65℃ to +150℃        |

|                               |                         | Lead Temperature (soldering, 10sec)    | +300℃                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Electrical Characteristics**

TABLE 2 ELECTRICAL CHARACTERISTICS

| PARAMETER                                                                                                                                           | SYMBOL            | CONDITIONS                | MIN  | TYP   | MAX  | UNITS |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------|------|-------|------|-------|--|

| <b>GENERAL CHARACTERISTICS</b> (V <sub>DD</sub> = +5V, V <sub>DDA</sub> = +5V, T <sub>A</sub> = +25 °C, 16MHz input clock, unless otherwise noted.) |                   |                           |      |       |      |       |  |

| Power Supply Voltage                                                                                                                                | $V_{DD}$          |                           | 4.75 | 5.0   | 5.5  | V     |  |

|                                                                                                                                                     | $V_{DDA}$         |                           | 4.75 | 5.0   | 5.5  | V     |  |

| V <sub>DDA</sub> Power Supply Rejection                                                                                                             |                   |                           |      |       |      |       |  |

| Power Supply Current                                                                                                                                | I <sub>DD</sub>   |                           | 5.5  | -     | 12.5 | mA    |  |

|                                                                                                                                                     | I <sub>DDA</sub>  |                           | 2.5  | -     | 7.5  |       |  |

| Flash Programming Voltage                                                                                                                           | $V_{PP}$          |                           |      | +12   |      | V     |  |

| DIGITAL INPUTS                                                                                                                                      |                   |                           |      |       |      |       |  |

| Minimum High-Level                                                                                                                                  | V <sub>IH</sub>   | $V_{DD} = +5V$            |      | 2.0   |      | V     |  |

| Input Voltage                                                                                                                                       |                   |                           |      |       |      |       |  |

| Maximum Low-Level                                                                                                                                   | V <sub>IL</sub>   | $V_{DD} = +5V$            |      | 8.0   |      | V     |  |

| Input Voltage                                                                                                                                       |                   |                           |      |       |      |       |  |

| Input Current                                                                                                                                       | I <sub>IN</sub>   |                           |      | ±0.05 |      | μΑ    |  |

| Input Capacitance                                                                                                                                   | C <sub>IN</sub>   |                           |      | 5     | 10   | pF    |  |

| DIGITAL OUTPUTS                                                                                                                                     |                   |                           |      |       |      |       |  |

| Minimum High-Level                                                                                                                                  | $V_{OH}$          | I <sub>SOURCE</sub> = 4mA |      | 4.2   |      | V     |  |

| Output Voltage                                                                                                                                      |                   |                           |      |       |      |       |  |

| Maximum Low-Level                                                                                                                                   | $V_{OL}$          | $I_{SINK} = 4mA$          |      | 0.2   |      | V     |  |

| Output Voltage                                                                                                                                      |                   |                           |      |       |      |       |  |

| Output Capacitance                                                                                                                                  | Соит              |                           |      | 10    | 15   | pF    |  |

| Tri-state Output Leakage Current                                                                                                                    | l <sub>oz</sub>   |                           |      |       | 0.25 | μΑ    |  |

| POWER SUPPLY MONITOR                                                                                                                                |                   |                           |      |       |      |       |  |

| V <sub>DD</sub> Trip Point                                                                                                                          | V <sub>TRIP</sub> |                           |      | 3.75  |      | V     |  |

| ANALOG INPUTS                                                                                                                                       |                   |                           |      |       |      |       |  |

| ADCI(0-3) Input Voltage Range                                                                                                                       | V <sub>ADCI</sub> |                           | 0    |       | 2.7  | V     |  |

| ADCI(0-3) Input Resistance                                                                                                                          | R <sub>ADCI</sub> |                           |      | 100   |      | MOhms |  |

| ADCI(0-3) Input Capacitance                                                                                                                         | C <sub>ADCI</sub> |                           |      | 5     |      | pF    |  |

| ADCI(0-3) Input Leakage Current                                                                                                                     | I <sub>ADCI</sub> |                           |      | TBD   |      | nA    |  |

| Channel-to-Channel Crosstalk                                                                                                                        |                   |                           |      | TBD   |      | dB    |  |

| ANALOG OUTPUT  TA Output Valtage (Note 1) | $V_{TA}=V_{RGH}$       |                  | 1.179 |        | 1.23  | V                 |

|-------------------------------------------|------------------------|------------------|-------|--------|-------|-------------------|

| TA Output Voltage (Note 1)                | in Bair                |                  |       |        | 1.23  | •                 |

| TA Output Drive Capabilities              | $V_{TA=}V_{BGH)}$      |                  | 10    |        |       | kOhms             |

| (Maximum Load Resistance)                 |                        |                  |       |        |       |                   |

| CURRENT SOURCE                            | 1                      | T                |       |        |       | 1                 |

| ISRC Current Drive                        | I <sub>ISRC</sub>      | (Note 2, Note 3) |       | 33/133 | 530uA | μΑ                |

| ISRC Output Resistance                    | R <sub>ISRC</sub>      |                  |       | 50     |       | MOhms<br>(Design) |

| ISRC Output Capacitance                   | C <sub>ISRC</sub>      |                  |       | 25     |       | PF (Design)       |

| RESIN Input Ref Resistance                | R <sub>RESIN</sub>     |                  |       | 100    |       | MOhms<br>(Design) |

| ISRC Reference Voltage (low)              | V <sub>resinLow</sub>  |                  | 195   | 200    | 205   | MV (Design)       |

| ISRC Reference Voltage (high)             | V <sub>resinHigh</sub> |                  | 792   | 800    | 808   | MV (Design)       |

| RESIN Input Reference                     | C <sub>RESIN</sub>     |                  |       | 7      |       | PF (Design)       |

| Capacitance                               |                        |                  |       |        |       |                   |

| INTERNAL REFERENCE                        |                        |                  |       |        |       |                   |

| Bandgap Reference Voltage                 |                        |                  | 1.05  |        | 1.21  | V                 |

| (1 <sup>st</sup> order)                   |                        |                  |       |        |       |                   |

| Bandgap Reference Voltage                 |                        |                  | 1.07  |        | 1.24  | V                 |

| (2st order) (Calibration value)           |                        |                  |       |        |       |                   |

| Bandgap Reference Tempco                  |                        |                  | 10    |        | 20    | ppm/℃             |

| EXTERNAL REFERENCE                        | •                      | •                | •     |        |       | •                 |

| Input Impedance                           | R <sub>XTVREF</sub>    |                  |       | 100    |       | MOhms             |

| •                                         |                        |                  |       |        |       | (Design)          |

| PGA                                       | •                      | •                |       |        |       |                   |

| PGA Gain adjustment                       |                        |                  | 2.15  |        | 2.35  |                   |

| PARAMETER                     | SYMBOL                      | CONDITIONS              | MIN | TYP  | MAX  | UNITS |  |

|-------------------------------|-----------------------------|-------------------------|-----|------|------|-------|--|

| ANALOG TO DIGITAL CONVER      | ANALOG TO DIGITAL CONVERTER |                         |     |      |      |       |  |

| ADC Resolution                |                             |                         |     | 12   |      | Bits  |  |

| Differential Non linearity    | DNL                         |                         |     |      | ±10  | LSB   |  |

| Integral Non linearity        | INL                         |                         |     |      | ±1   | LSB   |  |

| Full-Scale Error (Gain Error) |                             | All channels, ADCI(0-3) |     | ±4   |      | LSB   |  |

| Offset Error                  |                             | All channels, ADCI(0-3) |     | ±0.5 |      | LSB   |  |

| Channel-to-Channel Mismatch   |                             | All channels, ADCI(0-3) |     | ±0.5 |      | LSB   |  |

| Conversion Time               |                             | 4 channels              |     | •    | 1.75 | ms    |  |

|                               |                             | Single Channel          |     |      | 0.5  |       |  |

Note 1: TA is the output of an analog multiplexer that can be programmed to switch through one of eight analog inputs -V<sub>ADCI(IO-3)</sub>, V<sub>BGI</sub>, V<sub>BGI</sub>, V<sub>ADC</sub> and V<sub>SR</sub>, which correspond to the 4 analog inputs to the VERSA1, on-chip Bandgap reference, a buffered on-chip reference, on-chip ADC reference and current source reference, respectively.

Note 2: The on-chip current source can be programmed to provide 2 current values using the calibrated internal Bandgap reference and a 6.00k precision feedback resistor between RESIN and analog Ground.

Note 3:The Feedback resistor between RESIN and analog Ground can be lowered to 1.5k resulting in an ISRC maximum output of about 530uA. In such conditions, the resistive element between ISRC output and RESIN should have > 1k in value.

# **Detailed Description**

The following sections will describes the VERSA1 Architecture and peripherals.

FIGURE 2 OPERATIONAL DIAGRAM FOR THE VERSA1

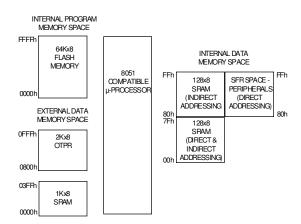

## **Memory Organization**

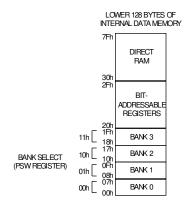

The following figure shows the memory organization of the VERSA1.

#### FIGURE 3 MEMORY ORGANIZATION OF THE VERSA1

At power-up/reset code is executed from the 64Kx8 Flash memory mapped into the processor's internal ROM space. An extra 2Kx8 of Secondary Flash memory is mapped into the external data memory space.

Note that 0000–0005h and 0195–0210h are reserved in the OTPR. A 1Kx8 block of SRAM is also mapped into the external data memory of the VERSA1. This block can be used as general-purpose scratch pad or storage memory. A 256x8 block of SRAM is mapped to the internal data memory space. This block of RAM is broken into 2 sub-blocks, with the upper block accessible via indirect addressing only, and the lower block accessible via both direct and indirect addressing.

The following figure describes access to the lower block of 128 bytes.

#### FIGURE 4 LOWER BLOCK INTERNAL MEMORY MAP

The SFR (Special Function Register) space is also mapped into the upper 128 bytes of internal data memory space. This SFR space is accessible via direct-access only. The SFR space provides the interface to all the on-chip peripherals. The following figure describes this interface.

## FIGURE 5 SFR SPACE ORGANIZATION

## **Dual Data Pointers**

The VERSA1 employs dual data pointers to accelerate data memory block moves. The standard 8051 data pointer (DPTR) is a 16-bit value used to address external data RAM or peripherals. The VERSA1 maintains the standard data pointer as DPTR0 at SFR locations 82h and 83h. It is not necessary to modify the code to use DPTR0.

The VERSA1 adds a second data pointer (DPTR1) at SFR locations 84h and 85h. The SEL bit in the DPTR Select register, DPS (SFR 86h), selects the active pointer. When SEL = 0, instructions that use the DPTR will use DPL0 and DPH0. When SEL = 1, instructions that use the DPTR will use DPL 1 and DPH1. SEL is the bit 0 of SFR location 86h. No other bits of SFR location 86h are used.

All DPTR-related instructions use the currently selected data pointer. To switch the active pointer, toggle the SEL bit. The fastest way to do so is to use the increment instruction (INC DPS). This requires only one instruction to switch from a source address to a destination address; saving application code from having to save source and destination addresses when doing a block move. Using dual data pointers provides significantly increased efficiency when moving large blocks of data. The SFR locations related to the dual data pointers are:

TABLE 3 DUAL DATA POINTER SFR ADDRESSES

| SFR Address | Mnemonic | Description          |

|-------------|----------|----------------------|

| 82h         | DPL0     | DPTR0 low byte       |

| 83h         | DPH0     | DPTR0 high byte      |

| 84h         | DPL1     | DPTR 1 low<br>byte   |

| 85h         | DPH1     | DPTR 1 high byte     |

| 86h         | DPS      | DPTR Select<br>(LSB) |

## **Programming interface**

The Flash Programming Interface on the VERSA1 is a slave based and has 3 specific functions

- Act as a port where all the on-chip peripherals (not including the processor) can be accessed for debugging and test purposes.

- Act as a slave port for applications where the processor is not needed and only the VERSA1 peripherals are used and accessed.

## **CPU Timing**

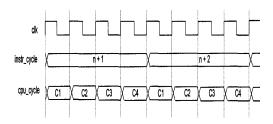

As previously stated, a VERSA1 instruction cycle consists of 4 clock cycles. Each system clock cycle forms a CPU cycle. Therefore, an instruction cycle consists of 4 CPU cycles: C1,

C2, C3, and C4, as illustrated in **Figure 7**, various events occur in each CPU cycle, depending on the type of instruction being executed. Throughout this datasheet, the labels C1, C2, C3, and C4 in timing descriptions refer to the 4 CPU cycles within a particular instruction cycle.

Note that a system clock (clk) is referred as (Fosc / 2).

FIGURE 7 CPU TIMING FOR SINGLE-CYCLE INSTRUCTION

## **Instruction Timing**

Instruction cycles in the VERSA1 are 4 system clock cycles in length, as opposed to the 12 clock cycles per instruction cycle in the standard 8051. This translates to a 3X improvement in execution time for most instructions. However, some instructions require a different number of instruction cycles on the VERSA1 than they do on the standard 8051. In the standard 8051, all instructions except for MUL and DIV take one or two instruction cycles to complete. In the VERSA1 architecture, instructions can take between one and five instruction cycles to complete.

For example, in the standard 8051, the instructions MOVX A, @DPTR and MOV direct, direct each take 2 instruction cycles (24 clock cycles) to execute. In the VERSA1 architecture, MOVX A, @DPTR takes two instruction cycles (8 system clock cycles) and MOV direct, direct takes three instruction cycles (12 clock cycles). Both instructions execute faster on the VERSA1 than they do on the standard 8051, but require different numbers of clock cycles.

For timing of real-time events, use the number of instruction cycles from **Table 5** to calculate the timing of software loops. The size column of **Table 5** indicates the number of memory accesses (bytes) needed to execute the instruction. In most cases, the number of bytes is equal to the number of instruction cycles required to complete the instruction. However, as indicated in **Table 5**, there are some instructions (for example, DIV and MUL) that require a greater number of instruction cycles than memory accesses.

By default, the VERSA1 timer/counters run at 12 system clock cycles per increment so that timer-based events have the same timing as with the standard 8051. The timers can be configured to run at 4 system clock cycles per increment to take advantage of the higher speed of the VERSA1.

## **Performance Overview**

The VERSA1 provides increased performance by executing instructions in a 4-clock bus cycle, as opposed to the 12-clock bus cycle in the standard 8051. The shortened bus timing improves the instruction execution rate for most instructions by a factor of three over the standard 8051 architectures.

The average speed improvement for the entire instruction set is approximately 2.5X, calculated as follows:

| Number of<br>Op codes                                                                        | Speed Improvement |  |  |  |

|----------------------------------------------------------------------------------------------|-------------------|--|--|--|

| 150                                                                                          | 3.0X              |  |  |  |

| 51                                                                                           | 1.5X              |  |  |  |

| 43                                                                                           | 2.0X              |  |  |  |

| 2                                                                                            | 2.4X              |  |  |  |

| Total: 255                                                                                   | Average: 2.5X     |  |  |  |

| Note: Comparison is for VERSA1 and standard 8051 running at the same system clock frequency. |                   |  |  |  |

There is not an exact 3X improvement in speed because some instructions require a different number of instruction cycles on the VERSA1 than they do on the standard 8051. In the standard 8051, all instructions except for MUL and DIV take one or two instruction cycles to complete. In the VERSA1 architecture, instructions can take between one and five instruction cycles to complete. However, because of the 3X faster instruction cycle time, the average speed improvement for all instructions is 2.5X.

#### Instruction Set

All VERSA1 instructions are binary code compatible and perform the same functions that they do in the industry standard 8051. The effects of these instructions on bits, flags, and other status functions are identical to the industry standard 8051. However, the timing of the instructions is different, both in terms of number of clock cycles per instruction cycle and timing within the instruction cycle.

Table 4 defines the symbols and mnemonics used in Table 5

Table 5 lists the VERSA1 instruction set and the number of system clock cycles required to complete each instruction.

TABLE 4 LEGEND FOR INSTRUCTION SET TABLE

| Symbol   | Function                                               |  |  |  |

|----------|--------------------------------------------------------|--|--|--|

| Α        | Accumulator                                            |  |  |  |

| Rn       | Register R0-R7                                         |  |  |  |

| Direct   | Internal register address                              |  |  |  |

| @Ri      | Internal register pointed to by R0 or R1 (except MOVX) |  |  |  |

| rel      | Two's complement offset byte                           |  |  |  |

| bit      | Direct bit address                                     |  |  |  |

| #data    | 8-bit constant                                         |  |  |  |

| #data 16 | 16-bit constant                                        |  |  |  |

| addr 16  | 16-bit destination address                             |  |  |  |

| addr 11  | 11-bit destination address                             |  |  |  |

## TABLE 5 VERSA1 INSTRUCTION SET

| Mnemonic                | Description                             | Size<br>(bytes) | Instr.<br>Cycles | Hex Code |

|-------------------------|-----------------------------------------|-----------------|------------------|----------|

| Arithmetic instructions |                                         |                 |                  |          |

| ADD A, Rn               | Add register to A                       | 1               | 1                | 28-2Fh   |

| ADD A, direct           | Add direct byte to A                    | 2               | 2                | 25h      |

| ADD A, @Ri              | Add data memory to A                    | 1               | 1                | 26-27h   |

| ADD A, #data            | Add immediate to A                      | 2               | 2                | 24h      |

| ADDC A, Rn              | Add register to A with carry            | 1               | 1                | 38-3Fh   |

| ADDC A, direct          | Add direct byte to A with carry         | 2               | 2                | 35h      |

| ADDC A, @Ri             | Add data memory to A with carry         | 1               | 1                | 36-37h   |

| ADDC A, #data           | Add immediate to A with carry           | 2               | 2                | 34h      |

| SUBB A, Rn              | Subtract register from A with borrow    | 1               | 1                | 98-9Fh   |

| SUBB A, direct          | Subtract direct byte from A with borrow | 2               | 2                | 95h      |

| SUBB A, @Ri             | Subtract data memory from A with borrow | 1               | 1                | 96-97h   |

| SUBB A, #data           | Subtract immediate from A with borrow   | 2               | 2                | 94h      |

| INC A                   | Increment A                             | 1               | 1                | 04h      |

| INC Rn                  | Increment register                      | 1               | 1                | 08-0Fh   |

| INC direct              | Increment direct byte                   | 2               | 2                | 05h      |

| INC @Ri                 | Increment data memory                   | 1               | 1                | 06-07h   |

| DEC A                   | Decrement A                             | 1               | 1                | 14h      |

| DEC Rn                  | Decrement register                      | 1               | 1                | 18-1Fh   |

| DEC direct              | Decrement direct byte                   | 2               | 2                | 15h      |

| DEC @Ri                 | Decrement data memory                   | 1               | 1                | 16-17h   |

| INC DPTR                | Increment data pointer                  | 1               | 3                | A3h      |

| MUL AB                  | Multiply A by B                         | 1               | 5                | A4h      |

| DIV AB                  | Divide A by B                           | 1               | 5                | 84h      |

| DA A                    | Decimal adjust A                        | 1               | 1                | D4h      |

| Mnemonic             | Description                           | Size<br>(bytes) | Instr.<br>Cycles | Hex Code |

|----------------------|---------------------------------------|-----------------|------------------|----------|

| Logical Instructions |                                       |                 |                  |          |

| ANL A, Rn            | AND register to A                     | 1               | 1                | 58-5Fh   |

| ANL A, direct        | AND direct byte to A                  | 2               | 2                | 55h      |

| ANL A, @Ri           | AND data memory to A                  | 1               | 1                | 56-57h   |

| ANL A, #data         | AND immediate to A                    | 2               | 2                | 54h      |

| ANL direct, A        | AND A to direct byte                  | 2               | 2                | 52h      |

| ANL direct, #data    | AND immediate data to direct byte     | 3               | 3                | 53h      |

| ORL A, Rn            | OR register to A                      | 1               | 1                | 48-4Fh   |

| ORL A, direct        | OR direct byte to A                   | 2               | 2                | 45h      |

| ORL A, @Ri           | OR data memory to A                   | 1               | 1                | 46-47h   |

| ORL A, #data         | OR immediate to A                     | 2               | 2                | 44h      |

| ORL direct, A        | OR A to direct byte                   | 2               | 2                | 42h      |

| ORL direct, #data    | OR immediate data to direct byte      | 3               | 3                | 43h      |

| XRL A, Rn            | Exclusive-OR register to A            | 1               | 1                | 68-6Fh   |

| XRL A, direct        | Exclusive-OR direct byte to A         | 2               | 2                | 65h      |

| XRL A, @Ri           | Exclusive-OR data memory to A         | 1               | 1                | 66-67h   |

| XRL A, #data         | Exclusive-OR immediate to A           | 2               | 2                | 64h      |

| XRL direct, A        | Exclusive-OR A to direct byte         | 2               | 2                | 62h      |

| XRL direct, #data    | Exclusive-OR immediate to direct byte | 3               | 3                | 63h      |

| CLR A                | Clear A                               | 1               | 1                | E4h      |

| CPL A Compliment A   |                                       | 1               | 1                | F4h      |

| SWAP A               | Swap nibbles of A                     | 1               | 1                | C4h      |

| RLA Rotate A left    |                                       | 1               | 1                | 23h      |

| RLC A                | RLC A Rotate A left through carry 1   |                 | 1                | 33h      |

| RRA                  | Rotate A right                        | 1               | 1                | 03h      |

| RRCA                 | Rotate A right through carry          | 1               | 1                | 13h      |

| Mnemonic                   | Description                                  | Size<br>(bytes) | Instr.<br>Cycles | Hex Code |

|----------------------------|----------------------------------------------|-----------------|------------------|----------|

| Data Transfer Instructions |                                              |                 |                  |          |

| MOV A, Rn                  | Move register to A                           | 1               | 1                | E8-EFh   |

| MOV A, direct              | Move direct byte to A                        | 2               | 2                | E5h      |

| MOV A, @Ri                 | Move data memory to A                        | 1               | 1                | E6-E7h   |

| MOV A, #data               | Move immediate to A                          | 2               | 2                | 74h      |

| MOV Rn, A                  | Move A to register                           | 1               | 1                | F8-FFh   |

| MOV Rn, direct             | Move direct byte to register                 | 2               | 2                | A8-AFh   |

| MOV Rn, #data              | Move immediate to register                   | 2               | 2                | 78-7Fh   |

| MOV direct, A              | Move A to direct byte                        | 2               | 2                | F5h      |

| MOV direct, Rn             | Move register to direct byte                 | 2               | 2                | 88-8Fh   |

| MOV direct, direct         | Move direct byte to direct byte              | 3               | 3                | 85h      |

| MOV direct, @Ri            | Move data memory to direct byte              | 2               | 2                | 86-87h   |

| MOV direct, #data          | Move immediate to direct byte                | 3               | 3                | 75h      |

| MOV @Ri, A                 | Move A to data memory                        | 1               | 1                | F6-F7h   |

| MOV @Ri, direct            | Move direct byte to data memory              | 2               | 2                | A6-A7h   |

| MOV @Ri, #data             | Move immediate to data memory                | 2               | 2                | 76-77h   |

| MOV DPTR, #data            | Move immediate to data pointer               | 3               | 3                | 90h      |

| MOVC A, @A+DPTR            | Move code byte relative DPTR to A            | 1               | 3                | 93h      |

| MOVC A, @A+PC              | Move code byte relative PC to A              | 1               | 3                | 83h      |

| MOVX A, @Ri                | Move external data (A8 or A16 if MPAGE) to A | 1               | 3                | E2-E3h   |

| MOVX A, @DPTR              | Move external data (A 16) to A               | 1               | 3                | E0h      |

| MOVX @Ri, A                | Move A to external data (A8 or A16 if MPAGE) | 1               | 3                | F2-F3h   |

| MOVX @DPTR, A              | Move A to external data (A 16)               | 1               | 3                | F0h      |

| PUSH direct                | Push direct byte onto stack                  | 2               | 2                | C0h      |

| POP direct                 | Pop direct byte from stack                   | 2               | 2                | D0h      |

| XCH A, Rn                  | Exchange A and register                      | 1               | 1                | C8-CFh   |

| XCH A, direct              | Exchange A and direct byte                   | 2               | 2                | C5h      |

| XCH A, @Ri                 | Exchange A and data memory                   | 1               | 1                | C6-C7h   |

| XCHD A, @Ri                | Exchange A and data memory nibble            | 1               | 1                | D6-D7h   |

| Mnemonic               | Description                 | Size (bytes) | # Cycles | Hex Code |

|------------------------|-----------------------------|--------------|----------|----------|

| Branching Instructions |                             |              |          |          |

| ACALL addr 11          | Absolute call to subroutine | 2            | 3        | 11-F1h   |

| LCALL addr 16          | Long call to subroutine     | 3            | 4        | 12h      |

| RET                    | Return from subroutine      | 4            | 22h      |          |

| RETI                   | Return from interrupt       | 1            | 4        | 32h      |

| Mnemonic                            | Description                                      | Size<br>(bytes) | # Cycles | Hex Code |  |  |

|-------------------------------------|--------------------------------------------------|-----------------|----------|----------|--|--|

| AJMP addr 11                        | Absolute jump unconditional                      | 2               | 3        | 01-E1h   |  |  |

| LJMP addr 16                        | Long jump unconditional                          | 3               | 4        | 02h      |  |  |

| SJMP rel                            | Short jump (relative address)                    | 2               | 3        | 80h      |  |  |

| JC rel                              | Jump on carry = 1                                | 2               | 3        | 40h      |  |  |

| JNC rel                             | Jump on carry = 0                                | 2               | 3        | 50h      |  |  |

| JB bit, rel                         | Jump on direct bit = 1                           | 3               | 4        | 20h      |  |  |

| JNB bit, rel                        | Jump on direct bit = 0                           | 3               | 4        | 30h      |  |  |

| JBC bit, rel                        | Jump on direct bit = 1 and clear                 | 3               | 4        | 10h      |  |  |

| JMP @A+DPTR                         | Jump indirect relative DPTR                      | 1               | 3        | 73h      |  |  |

| JZ rel                              | Jump on accumulator = 0                          | 2               | 3        | 60h      |  |  |

| JNZ rel                             | Jump on accumulator 1 = 0                        | 2               | 3        | 70h      |  |  |

| CJNE A, direct, rel                 | Compare A, direct JNE relative                   | 3               | 4        | B5h      |  |  |

| CJNE A, #d, rel                     | Compare A, immediate JNE relative                | 3               | 4        | B4h      |  |  |

| CJNE Rn, #d, rel                    | Compare reg, immediate JNE relative              | 3               | 4        | B8-BFh   |  |  |

| CJNE @Ri, #d, rel                   | Compare ind, immediate JNE relative              | 3               | 4        | B6-B7h   |  |  |

| DJNZ Rn, rel                        | Decrement register, JNZ relative                 | 2               | 3        | D8-DFh   |  |  |

| DJNZ direct, rel                    | Decrement direct byte, JNZ relative              | 3               | 4        | D5h      |  |  |

| Miscellaneous Instruction           |                                                  | •               |          |          |  |  |

| NOP                                 | NO operation 1 1 00h                             |                 |          |          |  |  |

| There is an additional reserved op- | code (A5) that performs the same function as NOF | P.              |          |          |  |  |

| All mnemonics are copyright © Inte  | el Corporation 1980.                             |                 |          |          |  |  |

| Mnemonic                 | Description                                       | Size<br>(bytes) | # Cycles | Hex Code |  |

|--------------------------|---------------------------------------------------|-----------------|----------|----------|--|

| Boolean Instructions     |                                                   |                 |          |          |  |

| CLR C                    | Clear carry                                       | 1               | 1        | C3h      |  |

| CLR bit                  | Clear direct bit                                  | 2               | 2        | C2h      |  |

| SETB C                   | Set carry                                         | 1               | 1        | D3h      |  |

| SETB bit                 | 2                                                 | 2               | D2h      |          |  |

| CPL C Complement carry 1 |                                                   |                 |          | B3h      |  |

| CPL bit                  | CPL bit Complement direct bit 2                   |                 |          |          |  |

| ANL C, bit               | AND direct bit to carry                           | 2               | 2        | 82h      |  |

| ANL C, /bit              | AND direct bit inverse to carry                   | 2               | 2        | B0h      |  |

| ORL C, bit               | OR direct bit to carry 2 2 72h                    |                 |          | 72h      |  |

| ORL C, /bit              | DRL C, /bit OR direct bit inverse to carry 2 2 AC |                 |          |          |  |

| MOV C, bit               | Move direct bit to carry 2 2 A2h                  |                 |          |          |  |

| MOV bit, C               | Move carry to direct bit                          | 2               | 2        | 92h      |  |

## **Peripheral Interfaces**

## **Special Function Registers**

The Special Function Registers (SFRs) control several of the features of the VERSA1. Most of the VERSA1 SFRs are identical to the standard 8051 SFRs. However, there are additional SFRs that control features that are not available in the standard 8051.

**Table 6** lists the VERSA1 SFRs and indicates which SFRs are not included in the standard 8051 SFR space. When writing software for the VERSA1, use equate statements to define the SFRs that are specific to the VERSA1. SFR bit positions that contain a 0 or a 1 cannot be written to and, when read, always return the value shown (0 or 1). SFR bit positions that contain "-" are available but not used. The last column of **Table 6** shows the reset value of VERSA1 SFRs.

TABLE 6 SPECIAL FUNCTION REGISTERS

| SFR Register | SFR<br>Adrs | Bit 7   | Bit 6   | Bit 5    | Bit 4     | Bit 3          | Bit 2     | Bit 1      | Bit 0      | Reset Value |

|--------------|-------------|---------|---------|----------|-----------|----------------|-----------|------------|------------|-------------|

| SP           | 81h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0111b  |

| DPL0         | 82h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| DPH0         | 83h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| DPL1         | 84h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| DPH1         | 85h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| DPS          | 86h         | 0       | 0       | 0        | 0         | 0              | 0         | 0          | SEL        | 0000 0000b  |

| PCON         | 87h         | SMOD0   | 0       | 1        | 1         | GF1            | GF0       | 0          | 0          | 0011 0000b  |

| TCON         | 88h         | TF1     | TR1     | TF0      | TR0       | IE1            | IT1       | IE0        | IT0        | 0000 0000b  |

| TMOD         | 89h         | GATE    | C/!T    | M1       | M0        | GATE           | C/!T      | M1         | M0         | 0000 0000b  |

| TL0          | 8Ah         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| TL1          | 8Bh         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| TH0          | 8Ch         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| TH1          | 8Dh         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| CKCON        | 8Eh         | 0       | 0       | T2M      | T1M       | T0M            | 0         | 0          | 1          | 0000 0001b  |

| SPC_FNC      | 8Fh         | 0       | 0       | 0        | 0         | 0              | 0         | 0          | WRS        | 0000 0000b  |

| EXIF         | 91h         | -       | -       | IE3      | IE2       | 1              | 0         | 0          | 0          | 0000 1000b  |

| MPAGE        | 92h         | AD15    | AD14    | AD13     | AD12      | AD11           | AD10      | AD9        | AD8        | 0000 0000b  |

| ADCCTRL      | 94h         | SV0     | MANUAL  | ONESHOT  | ADCENABLE | ADCIC          | ADCIE     | CONT       | BGENABLE   | 0000 0000b  |

| BGAPCAL      | 95h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| ADCALADR     | 96h         | 0       | 0       | 0        | CALDSBL   | CALADR3        | CALADR2   | CALADR1    | CALADR0    | 0000 0000b  |

| ADCALDAT     | 97h         | 0       | 0       | 0        | DTBL4     | DTBL3          | DTBL2     | DTBL1      | DTBL0      | 0000 0000b  |

| SCON0        | 98h         | SM0_0   | SM1_0   | SM2_0    | REN_0     | TB8_0          | RB8_0     | TI_0       | RI_0       | 0000 0000b  |

| SBUF0        | 99h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| ADCSTAT      | 9Ch         | 0       | 0       | 0        | 0         | 0              | 0         | 0          | ADCINT     | 0000 0000b  |

| ADCD0LO      | A4h         | ADCD7_0 | ADCD6_0 | ADCD5_0  | ADCD4_0   | ADCD3_0        | ADCD2_0   | ADCD1_0    | ADCD0_0    | 0000 0000b  |

| ADCD0HI      | A5h         | 0       | 0       | 0        | 0         | ADCD11_0       | ADCD10_0  | ADCD9_0    | ADCD8_0    | 0000 0000b  |

| ADCD1LO      | A6h         | ADCD7_1 | ADCD6_1 | ADCD5_1  | ADCD4_1   | ADCD3_1        | ADCD2_1   | ADCD1_1    | ADCD0_1    | 0000 0000b  |

| ADCD1HI      | A7h         | 0       | 0       | 0        | 0         | ADCD11_1       | ADCD10_1  | ADCD9_1    | ADCD8_1    | 0000 0000b  |

| IE           | A8h         | EA      | ES1     | ET2      | ES0       | ET1            | EX1       | ET0        | EX0        | 0000 0000b  |

| ADCD2LO      | ACh         | ADCD7_2 | ADCD6_2 | ADCD5_2  | ADCD4_2   | ADCD3_2        | ADCD2_2   | ADCD1_2    | ADCD0_2    | 0000 0000b  |

| ADCD2HI      | ADh         | 0       | 0       | 0        | 0         | ADCD11_2       | ADCD10_2  | ADCD9_2    | ADCD8_2    | 0000 0000b  |

| ADCD3LO      | AEh         | ADCD7_3 | ADCD6_3 | ADCD5_3  | ADCD4_3   | ADCD3_3        | ADCD2_3   | ADCD1_3    | ADCD0_3    | 0000 0000b  |

| ADCD3HI      | AFh         | 0       | 0       | 0        | 0         | ADCD11_3       | ADCD10_3  | ADCD9_3    | ADCD8_3    | 0000 0000b  |

| SPICTRL      | B4h         | 0       | 0       | SPICSS_1 | SPI_CSS_0 | SPIMCLK_1      | SPIMCLK_0 | SPICLKP    | SPIMA_SL   | 0000 0000b  |

| SPIRX        | B5h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| SPITX        | B6h         | -       | -       | -        | -         | -              | -         | -          | -          | 0000 0000b  |

| SPIIE        | B7h         | 0       | 0       | 0        | 0         | 0              | SPIRXOVIE | SPIRXDAIE  | SPITXEMPIE | 0000 0000b  |

| IP           | B8h         | 1       | 0       | 0        | PS0       | PT1            | PX1       | PT0        | PX0        | 1000 0000b  |

| IOCTRL       | BAh         | 0       | 0       | 0        | 0         | IODIRCTRL<br>1 | IOOUT1    | IODIRCTRL0 | IOOUT0     | 0000 0000b  |

| SFR Register | SFR<br>Adrs | Bit 7             | Bit 6             | Bit 5             | Bit 4             | Bit 3            | Bit 2            | Bit 1            | Bit 0      | Reset Value |

|--------------|-------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|------------------|------------|-------------|

| IOREAD       | BBh         | 0                 | 0                 | 0                 | 0                 | 0                | 0                | IOREAD1          | IOREAD0    | 0000 0000b  |

| SPIINTSTAT   | BCh         | 0                 | 0                 | 0                 | 0                 | 0                | SPIRXOV          | SPIRXDA          | SPITXEMP   | 0000 0000b  |

| SPIRXOVC     | BDh         | X_7               | X_6               | X_5               | X_4               | X_3              | X_2              | X_1              | X_0        | 0000 0000b  |

| SCON1        | C0h         | SM0_1             | SM1_1             | SM2_1             | REN_1             | TB8_1            | RB8_1            | TI_1             | RI_1       | 0000 0000b  |

| SBUF1        | C1h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| MACACC0*     | C4h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| MACACC1*     | C5h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| MACACC2*     | C6h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| MACACC3*     | C7h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| T2CON        | C8h         | TF2               | FIRQT2            | RCLK              | TCLK              | 0                | TR2              | 0                | -RL2       | 0000 0000b  |

| RCAP2L       | CAh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| RCAP2H       | CBh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| TL2          | CCh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| TH2          | CDh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| PSW          | D0h         | CY                | AC                | F0                | RS1               | RS0              | OV               | F1               | Р          | 0000 0000b  |

| S1ACTIVATEL  | D7h         | S1EN              | 0                 | 0                 | 0                 | 0                | 1                | 0                | 0          | 0000 0100b  |

| EICON        | D8h         | SMOD1             | 1                 | EPFI              | PFI               | EXT2             | 0                | 0                | 0          | 0100 0000b  |

| Reserved     | D9h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| Reserved     | DAh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 1111 1111b  |

| Reserved     | DBh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 1111 1111b  |

| Reserved     | DCh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 1111 1111b  |

| Reserved     | DDh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| Reserved     | DEh         | 0                 | 0                 | 0                 | 0                 | -                | -                | _                | -          | 0000 0000b  |

| Reserved     | DFh         | 0                 | 0                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| ACC          | E0h         | -                 | -                 | -                 | -                 |                  | -                | _                | -          | 0000 0000b  |

| INTSRC       | E4h         | -                 | -                 | -                 | -                 | -                | _                | -                | -          | 0000 0000b  |

| CLKDIV       | E5h         | 0                 | 0                 | 0                 | 0                 | DIVCTL_2         | DIVCTL_1         | DIVCTL_0         | NORMSPD    | 0000 0000b  |

| MACA0*       | E6h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| MACA1*       | E7h         | _                 | _                 | -                 | _                 | _                | _                | _                |            | 0000 0000b  |

| EIE          | E8h         | 1                 | 1                 | 1                 | EIE2              | 0                | 0                | EX3              | EX2        | 1110 0000b  |

| MACRES0**    | EAh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| MACRES1**    | EBh         | _                 | _                 | -                 | -                 | -                | _                | -                | _          | 0000 0000b  |

| MACRES2**    | ECh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| MACRES3**    | EDh         | _                 | -                 | -                 | -                 | -                | _                | -                | _          | 0000 0000b  |

| MACBO*       | EEh         | _                 | -                 | _                 | _                 | -                | _                | _                | _          | 0000 0000b  |

| MACB1*       | EFh         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| В            | F0h         | _                 | _                 | _                 | -                 | _                | _                | -                | _          | 0000 0000b  |

| CONVRLO      | F5h         | -                 | _                 | -                 | -                 | -                | _                | -                | -          | 0000 0000b  |

| CONVRMED     | F6h         | -                 | -                 | _                 | _                 | _                | _                | _                | _          | 0000 0000b  |

| CONVRHI      | F7h         | -                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

| EIP          | F8h         | 1                 | 1                 | 1                 | PEI2              | 0                | 0                | PEX3             | PEX2       | 1110 0000b  |

| PGACTRL      | F9h         | DPGA6             | DPGA5             | DPGA4             | DPGA3             | DPGA2            | DPGA1            | DPGA0            | PGA ENABLE | 0000 0000b  |

| ISRC1        | FAh         | C1_6              | C1_5              | C1_4              | C1_3              | C1_2             | C1_1             | C1_0             | ISRCENABLE | 0000 0000b  |

| ISRC2        |             |                   |                   |                   |                   |                  |                  |                  | SV1        | 0000 0000b  |

| INMUX        | FBh<br>FCh  | C4_6<br>BGAPORDER | C4_5<br>MUXCTRL_2 | C4_4<br>MUXCTRL 1 | C4_3<br>MUXCTRL_0 | C4_2<br>IBUFEN_3 | C4_1<br>IBUFEN_2 | C4_0<br>IBUFEN_1 | IBUFEN_0   | 0000 0000b  |

|              |             |                   |                   | _                 |                   |                  |                  |                  |            |             |

| OUTMUX       | FDh         | 0                 | 0                 | 0                 | -                 | MU XB_2          | MU XB_1          | MU XB_0          | TAENABLE   | 0000 0000b  |

| ADCCkDIV     | FEh         | _                 | -                 | -                 | -                 | -                | -                | -                | -          | 0000 0000b  |

Notes: \*These registers are write only, \*\*These registers are read only

The following SFRs are related to CPU operation and program execution:

81h SP Stack Pointer

D0h PSW Program Status Word (Table 7)

E0h ACC Accumulator Register

F0h B B Register

**Table 7** lists the functions of the bits in the PSW SFR. Detailed descriptions of the remaining SFRs appear with the associated hardware descriptions in Chapter 3 of this datasheet.

#### TABLE 7 PSW REGISTER -SFR D0H

| Bit# | Mnemonic | Function                                                                                                                                                                                                                     |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | CY       | Carry flag. Set to 1 when the last arithmetic operation resulted in a carry (during addition) or borrow (during subtraction), otherwise cleared to 0 by all arithmetic operations.                                           |

| 6    | AC       | Auxiliary carry flag. Set to 1 when the last arithmetic operation resulted in a carry into (during addition) or borrow from (during subtraction) the high order nibble, otherwise cleared to 0 by all arithmetic operations. |

| 5    | F0       | User flag 0. Bit-addressable, general purpose flag for software control.                                                                                                                                                     |

| 4    | RS1      | Register bank select bits used to select a register bank in internal RAM                                                                                                                                                     |

| 3    | RS0      | 0 0 Register bank 0, addresses 00h-07h 0 1 Register bank 0, addresses 08h-0Fh 1 0 Register bank 0, addresses 10h-17h 1 1 Register bank 0, addresses 18h-1Fh                                                                  |

| 2    | OV       | Overflow flag. Set to 1 when the last arithmetic operation resulted in a carry (addition), borrow (subtraction), or overflow (multiply or divide). Otherwise, the bit cleared to 0 by all arithmetic operations.             |

| 1    | F1       | User flag 1. Bit-addressable, general purpose flag for software control.                                                                                                                                                     |

| 0    | Р        | Parity flag. Set to 1 when the modulo-2 sum of the 8-bits in the accumulator is 1 (odd parity), cleared to 0 on even parity.                                                                                                 |

#### Timers/Counters

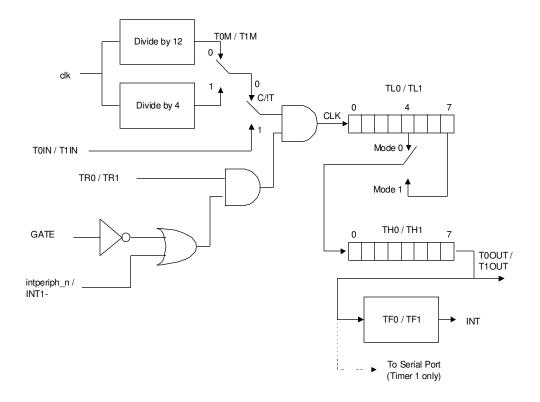

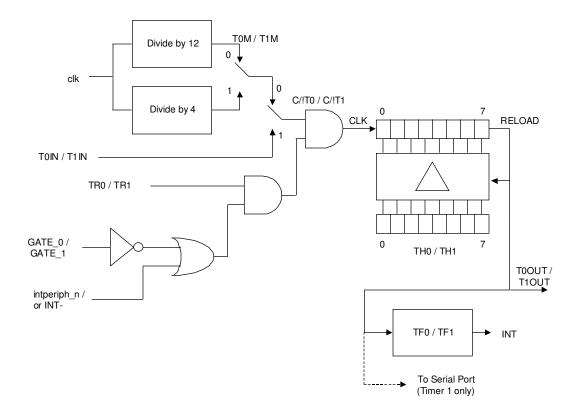

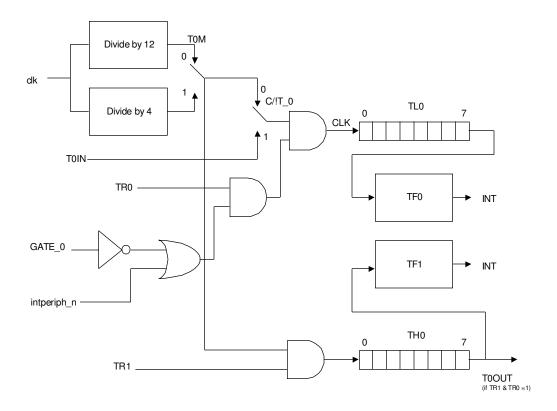

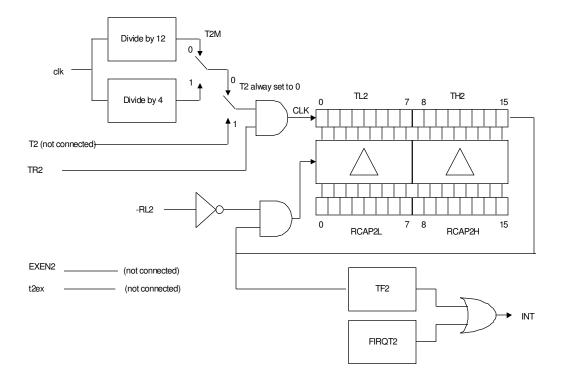

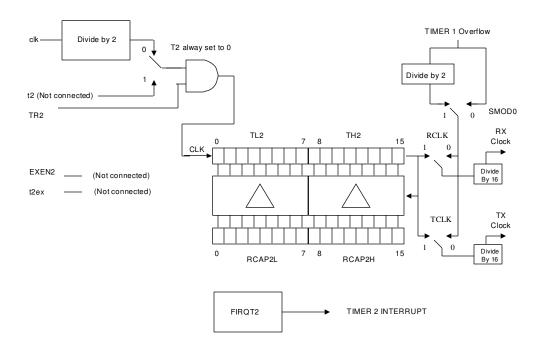

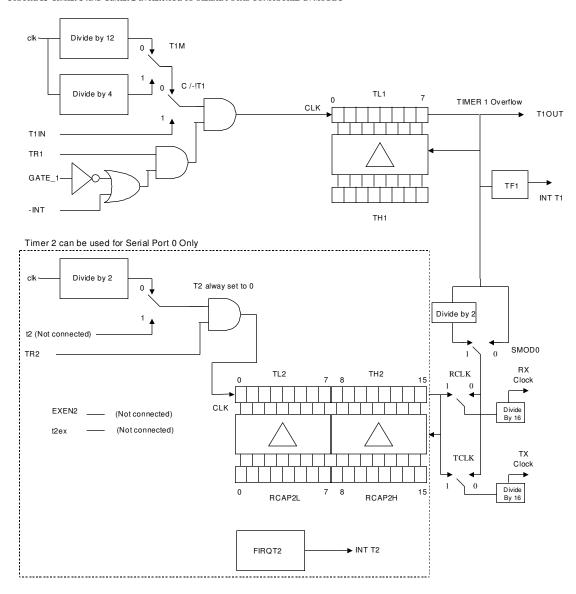

The VERSA1 includes three timer/counters (Timer 0, Timer 1 and Timer 2). Timer 0 and Timer 1 can operate as either a timer with a clock rate based on the system clock, or as an event counter clocked by the T0IN (Timer 0) and T1IN (Timer 1). Timer 2 can only operate in 16-bits timer mode. It can serve as serial port baud rate generator.

Each timer/counter consists of a 16-bit register that is accessible by software as two SFRs:

- o **Timer 0** -TL0 and TH0

- Timer 1 -TL1 and TH1

- Timer2 -TL2 and TH2

## Timers 0 and 1

Timers 0 and 1 each operate in four modes, as controlled through the TMOD SFR (Table 8) and the TCON SFR (Table 10). The four modes are:

- 13-bit timer/counter (mode 0)

- o **16-bit** timer/counter (mode 1)

- 8-bit counter with auto-reload (mode 2)

- Two 8-bit counters (mode 3)

#### TABLE 8 TMOD REGISTER -SFR 89H

| Bit# | Mnemonic | Function                                                                                                                                                                                                          |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | GATE_1   | Timer 1 gate control. When GATE_1 = 1, Timer 1 will clock only when INT1- = 1 and TR1 (TCON.6) = 1. When GATE_1 = 0, Timer 1 will clock only when TR1 = 1, regardless of the state of INT1                        |

| 6    | C/!T_1   | Counter/Timer select. When $C/!T_1 = 0$ , Timer 1 is clocked by clk/4 or clk/12, depending on the state of T1M (CKCON.4). When $C/!T_1 = 1$ , Timer 1 is clocked by T1 IN.                                        |

| 5    | M1_1     | Timer 1 mode select bit 1                                                                                                                                                                                         |

| 4    | M0_1     | Timer 1 mode select bit 0                                                                                                                                                                                         |

| 3    | GATE_0   | Timer 0 gate control. When $GATE_0 = 1$ , Timer 0 will clock only when intperiph_n = 1 and TR0 (TCON.4) = 1. When $GATE_0 = 0$ , Timer 0 will clock only when $TR0 = 1$ , regardless of the state of intperiph_n. |

| 2    | C/!T_0   | Counter/Timer select. When $C/!T_0 = 0$ , Timer 0 is clocked by clk/4 or clk/12, depending on the state of T0M (CKCON.3). When $C/!T_0 = 1$ , Timer 0 is clocked by T0 IN.                                        |

| 1    | M1_0     | Timer 0 mode select bit 1                                                                                                                                                                                         |

| 0    | M0_0     | Timer 0 mode select bit 0                                                                                                                                                                                         |

The following table describes the different modes of operation for M1\_x and M0\_x mode select pins for Timer 0 and Timer 1.

## TABLE 9 TIMER 0 / TIMER 1 MODES

| M1_x | M0_x | Mode                                   |

|------|------|----------------------------------------|

| 0    | 0    | Mode 0: 13-bit counter                 |

| 0    | 1    | Mode 1:16-bit counter                  |

| 1    | 0    | Mode 2: 8-bit counter with auto-reload |

| 1    | 1    | Mode 3: Two 8-bit counters             |

#### TABLE 10 TCON REGISTER SFR 88H

| Bit# | Mnemonic | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | TF1      | Timer 1 overflow flag. This flag is set to 1 when the Timer 1 count overflows. It is cleared when the microcontroller executes the interrupt service routine.                                                                                                                                                                                                                                                                                                                                                                                                                      |

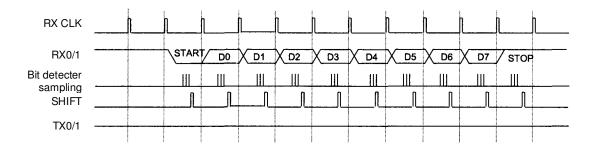

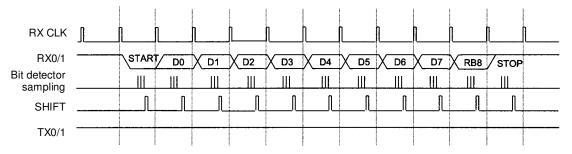

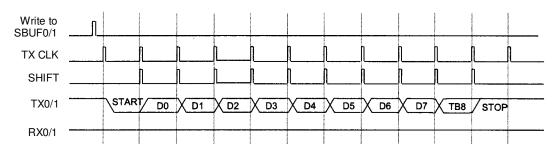

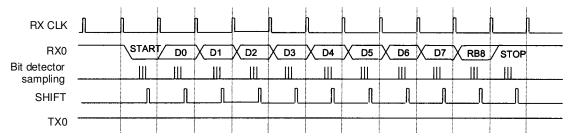

| 6    | TR1      | Timer 1 run control bit. Set this bit to 1 to enable Timer 1 counting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |