### **8-BIT MICROCONTROLLER**

#### Table of Contents-

| 1  |            | RAL DESCRIPTION                             |   |

|----|------------|---------------------------------------------|---|

| 2  |            | URES                                        |   |

| 3  |            | S INFORMATION LIST                          |   |

|    | 3.1        | Lead Free (RoHS) Parts information list     |   |

| 4  | -          | ONFIGURATION                                | - |

| 5  |            | ESCRIPTION                                  |   |

| 6  |            | DRY ORGANIZATION                            |   |

|    | 6.1<br>6.2 | Program Flash Memory1<br>Data Flash Memory1 |   |

|    |            | -                                           |   |

|    | 6.3        | Data Memory (accessed by MOVX)              |   |

|    | 6.4        | Scratch-pad RAM and Register Map1           |   |

|    | 6.5        | Working Registers1                          | 6 |

|    | 6.6        | Bit addressable Locations1                  | 6 |

|    | 6.7        | Stack1                                      | 6 |

| 7  | SPEC       | IAL FUNCTION REGISTERS1                     | 7 |

|    | 7.1        | SFR Location Table1                         | 7 |

|    | 7.2        | SFR Detail Bit Descriptions2                | 1 |

| 8  | INSTF      | RUCTION7                                    | 1 |

| 9  | POWE       | ER MANAGEMENT8                              | 1 |

|    | 9.1        | Idle Mode8                                  | 1 |

|    | 9.2        | Power Down Mode8                            | 1 |

| 10 | RESE       | T CONDITIONS                                | 2 |

|    | 10.1       | External Reset8                             | 2 |

|    | 10.2       | Power-On Reset (POR)8                       | 2 |

|    | 10.3       | Watchdog Timer Reset8                       | 2 |

|    | 10.4       | Software Reset8                             | 2 |

|    | 10.5       | Brownout Reset                              | 2 |

|    | 10.6       | Reset State8                                | 2 |

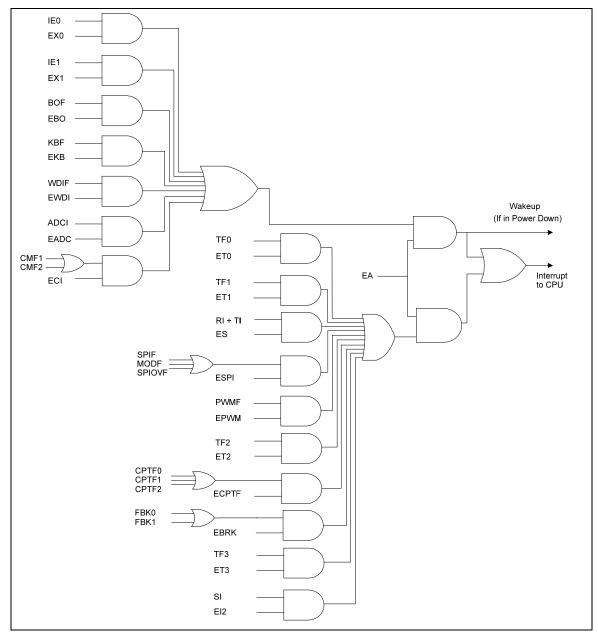

| 11 | INTEF      | RRUPTS                                      | 4 |

|    | 11.1       | Interrupt Sources                           | 4 |

|    | 11.2       | Priority Level Structure                    | 6 |

|    |            |                                             |   |

|    | 11.3       | Interrupt Response Time8                    | 8 |

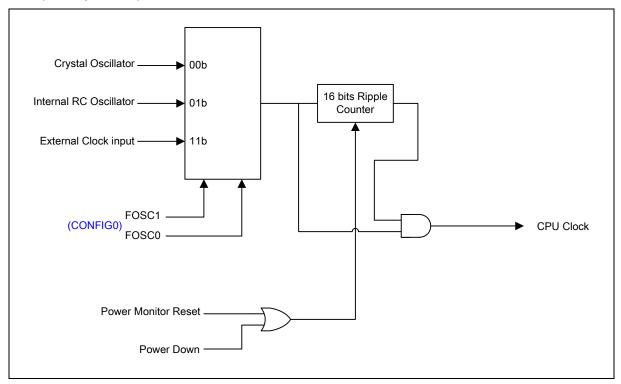

|    | 12.1  | On-Chip RC Oscillator Option             | 89  |

|----|-------|------------------------------------------|-----|

|    | 12.2  | External Clock Input Option              | 90  |

| 13 | POWE  | ER MONITORING FUNCTION                   | 91  |

|    | 13.1  | Power On Detect                          | 91  |

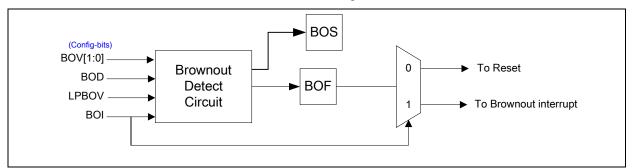

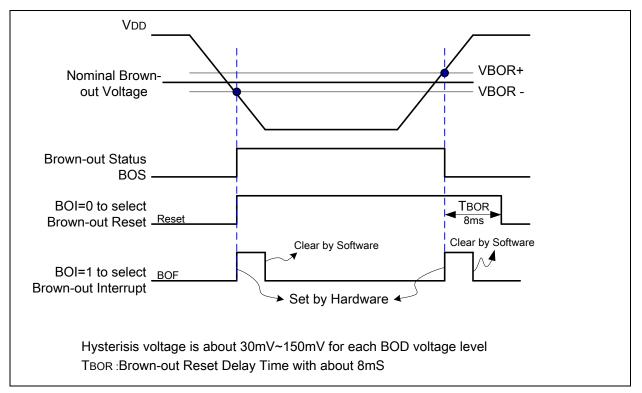

|    | 13.2  | Brownout Detect                          | 91  |

|    | 13.3  | SFR of Brown-out Detection               | 92  |

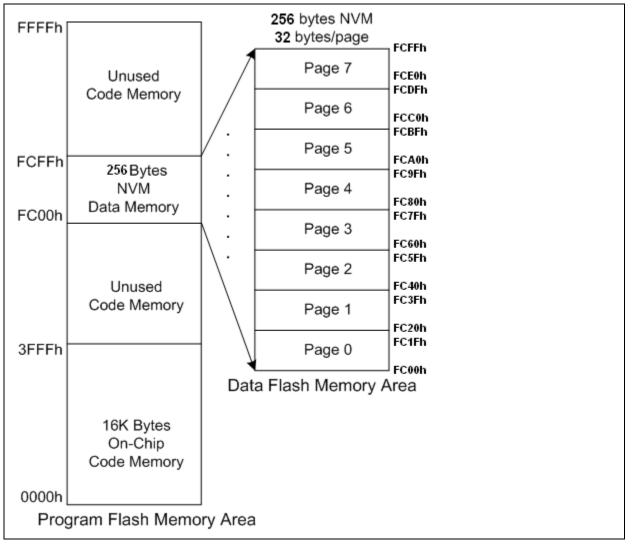

| 14 | NVM   | MEMORY                                   | 93  |

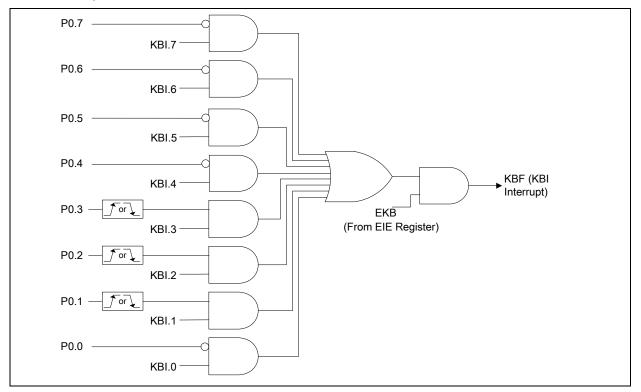

| 15 |       | OARD INTERRUPT (KBI)                     |     |

| 16 |       | ORT CONFIGURATION                        |     |

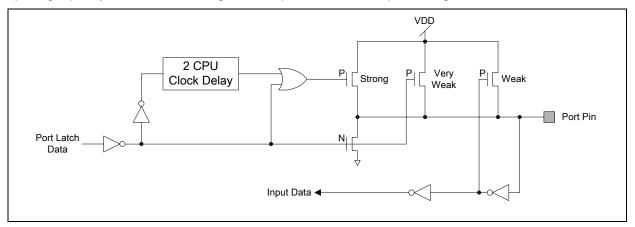

|    | 16.1  | Quasi-Bidirectional Output Configuration |     |

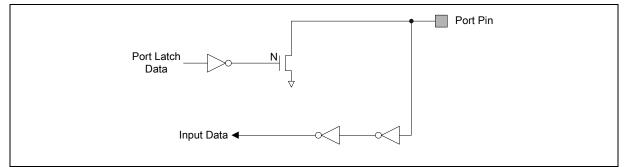

|    | 16.2  | Open Drain Output Configuration          | 96  |

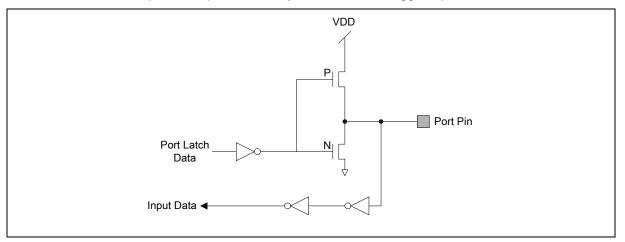

|    | 16.3  | Push-Pull Output Configuration           | 96  |

|    | 16.4  | Input Only Configuration                 | 97  |

|    | 16.5  | SFR of I/O Port Configuration            | 97  |

| 17 | PROG  | RAMMABLE TIMERS/COUNTERS                 | 98  |

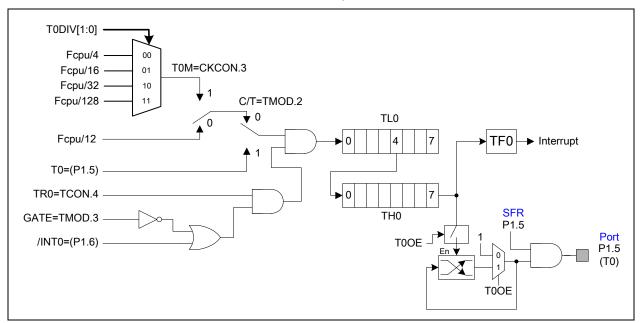

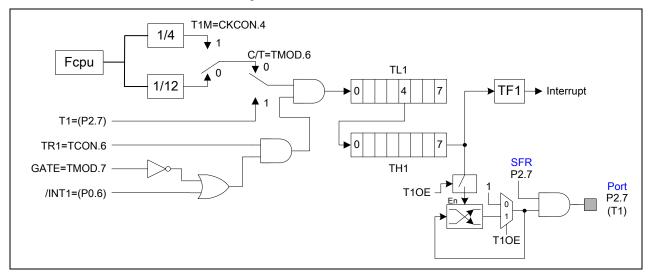

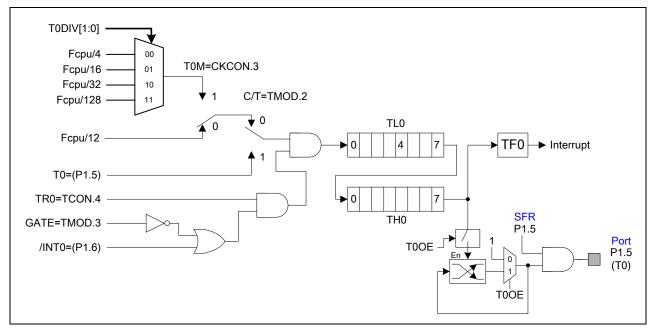

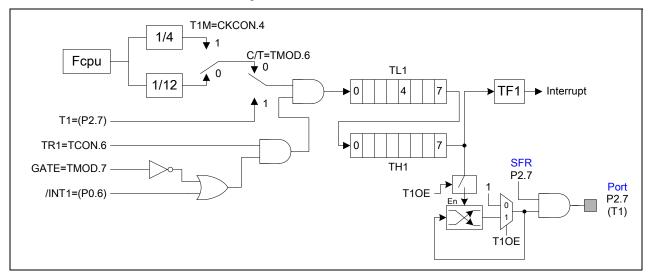

|    | 17.1  | TIMER/COUNTERS 0 & 1                     | 98  |

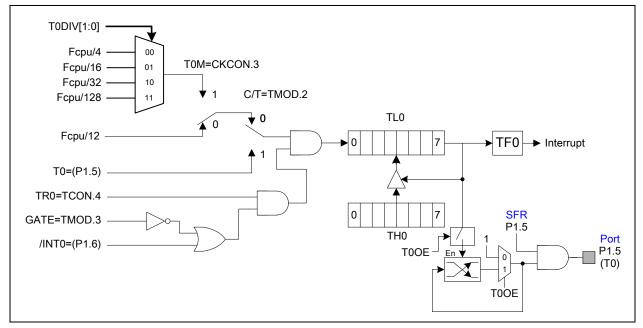

|    | 17.2  | Time-Base Selection                      | 98  |

|    | 17.3  | MODE 0                                   | 98  |

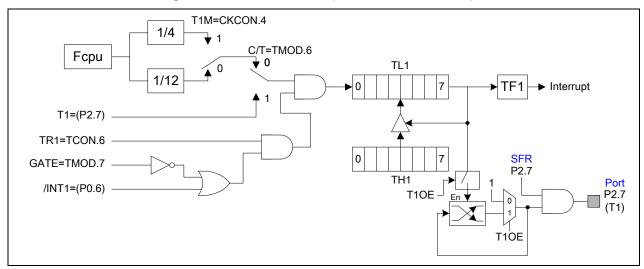

|    | 17.4  | MODE 1                                   | 99  |

|    | 17.5  | MODE 2                                   | 100 |

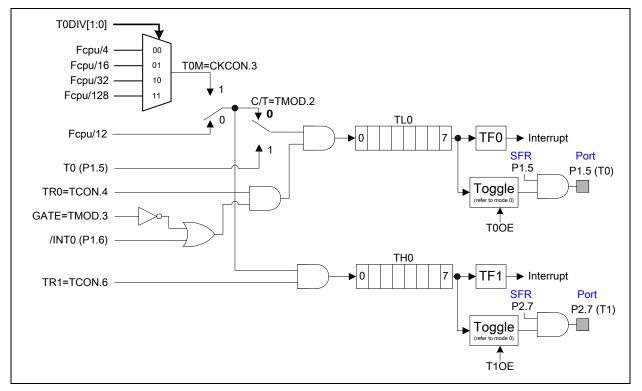

|    | 17.6  | MODE 3                                   | 101 |

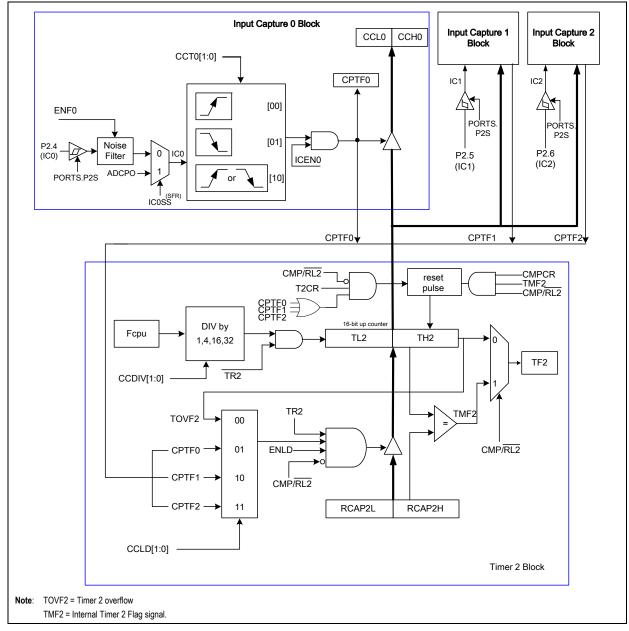

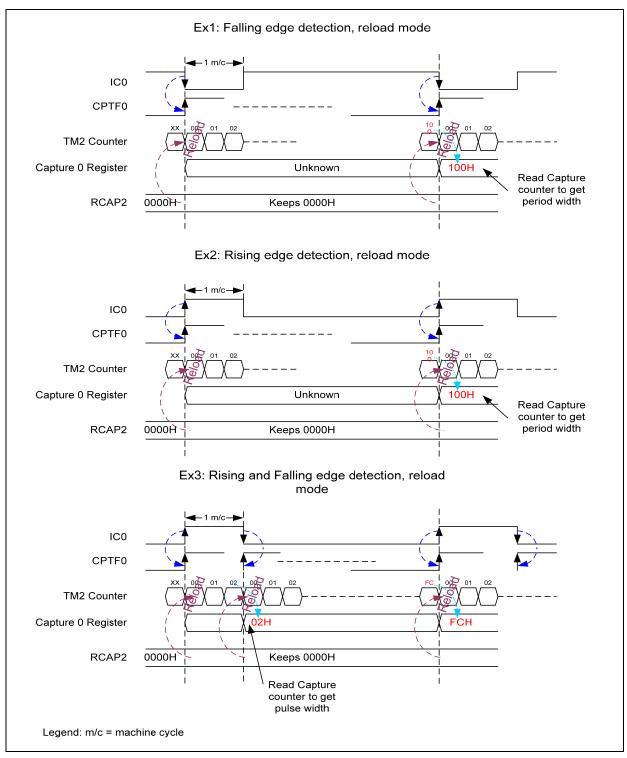

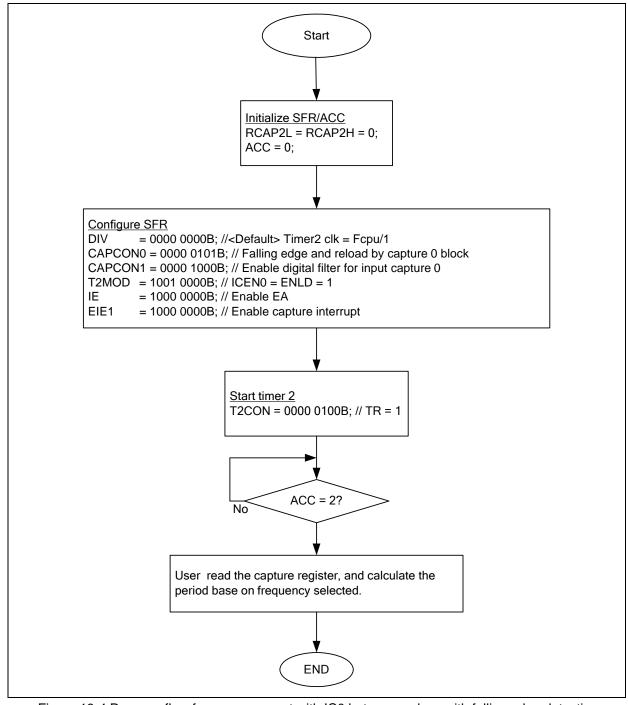

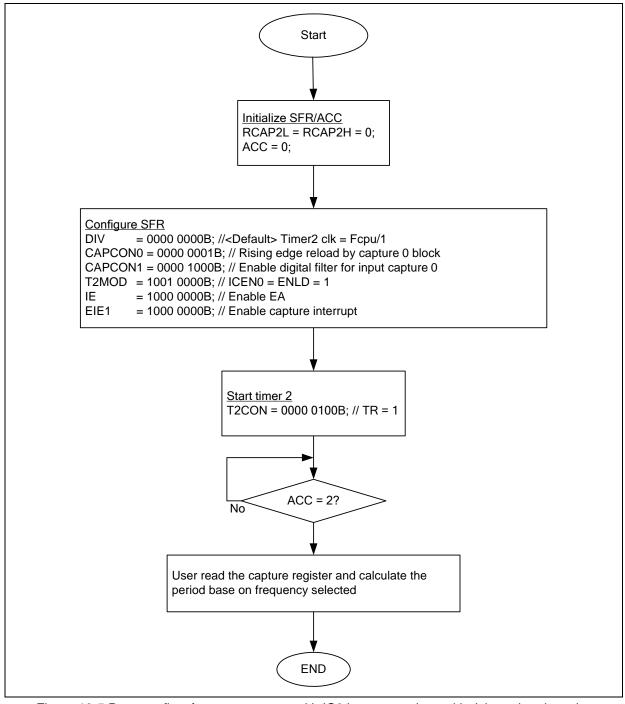

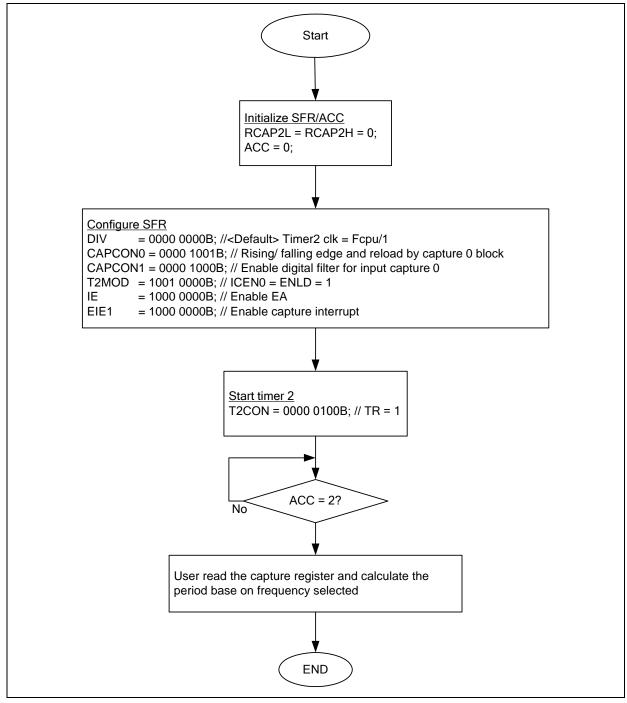

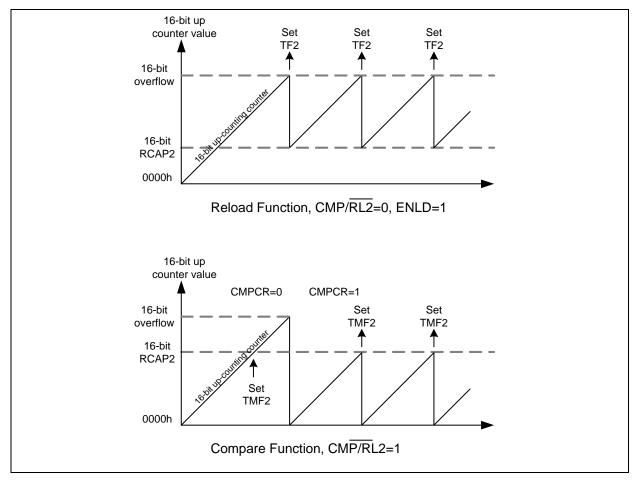

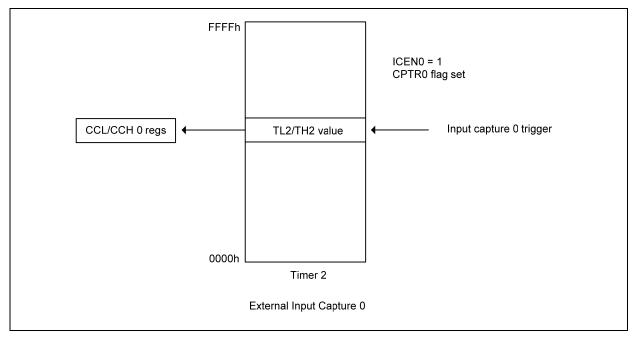

| 18 | TIMEF | R2/INPUT CAPTURE MODULES                 | 103 |

|    | 18.1  | Capture Mode                             | 103 |

|    | 18.2  | Compare Mode                             | 111 |

|    | 18.3  | Reload Mode                              | 111 |

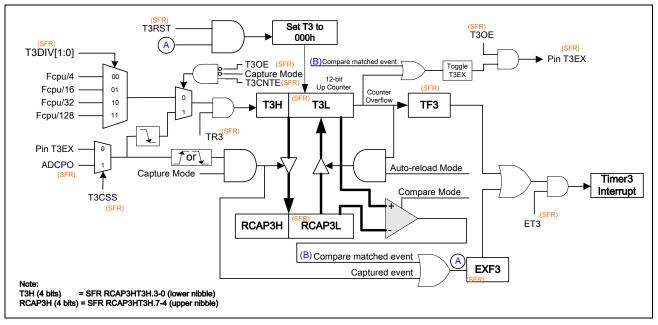

| 19 | TIMEF | 23                                       | 112 |

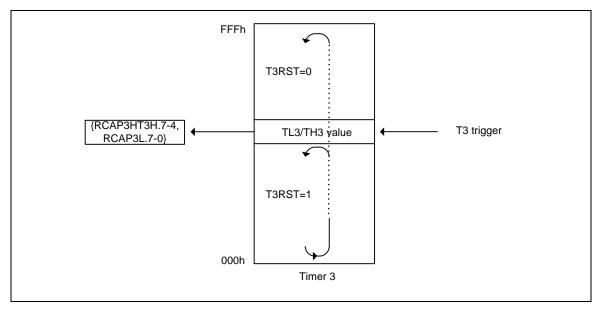

|    | 19.1  | Timer/Counter Mode                       | 113 |

|    | 19.2  | Capture Mode                             | 113 |

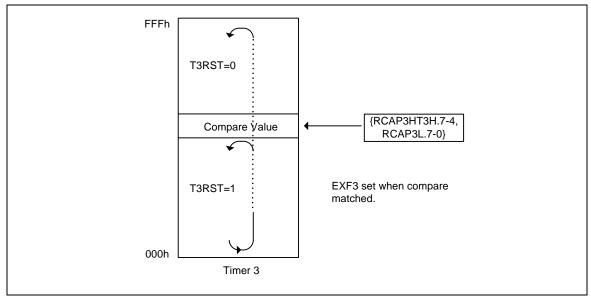

|    | 19.3  | Compare Mode                             | 114 |

|    | 19.4  | Auto-reload Mode                         | 115 |

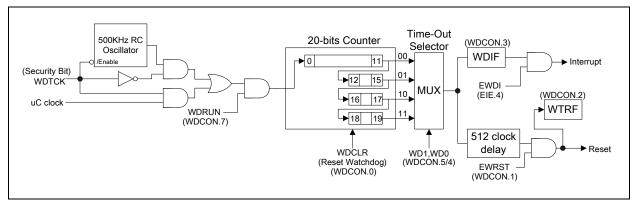

| 20 | WATC  | HDOG TIMER                               | 115 |

|    | 20.1  | WATCHDOG CONTROL                         | 116 |

|    | 20.2  | CLOCK CONTROL of Watchdog                | 117 |

| 21 | SERIA | AL PORT (UART)                           | 118 |

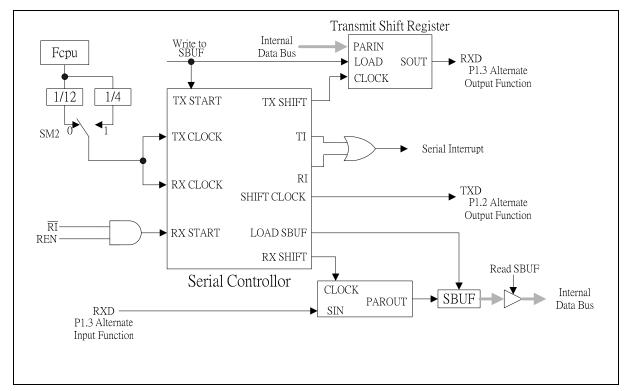

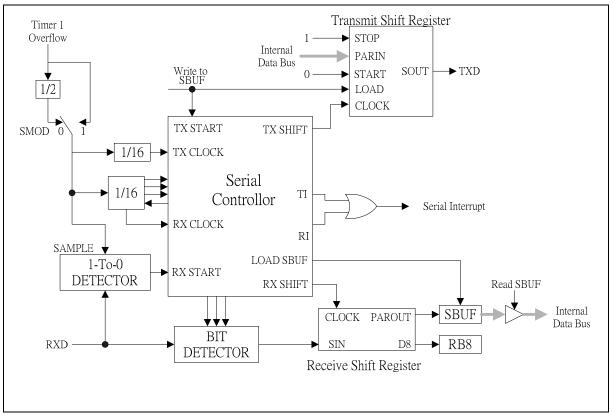

|    | 21.1  | MODE 0                                   | 118 |

|    | 21.2  | MODE 1                                   | 119 |

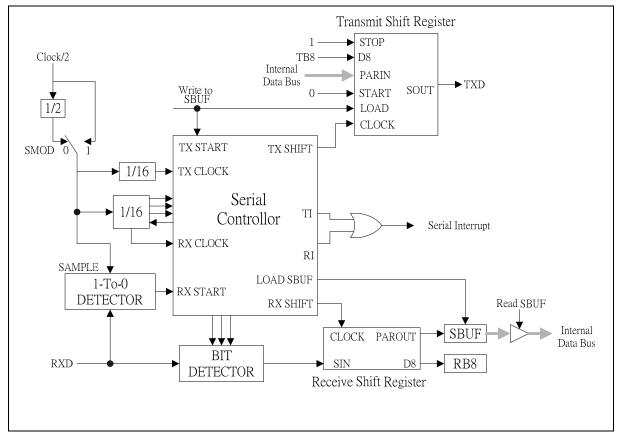

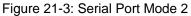

|     | 21.3   | MODE 2                                                | 121                             |

|-----|--------|-------------------------------------------------------|---------------------------------|

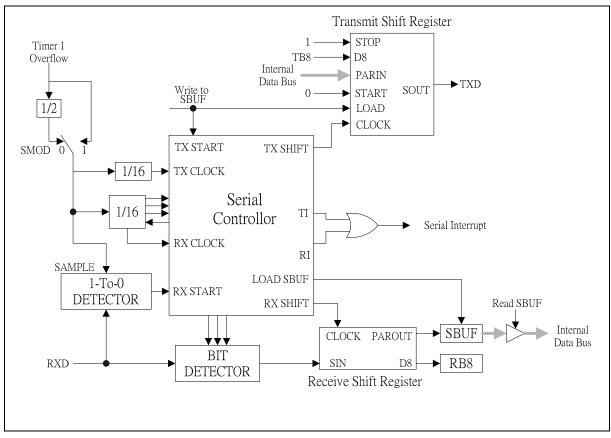

|     | 21.4   | MODE 3                                                | 122                             |

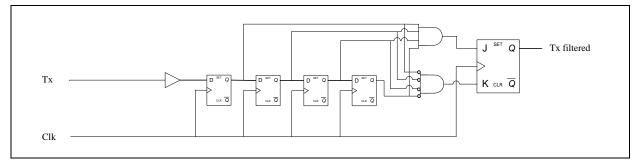

|     | 21.5   | Framing Error Detection                               | 123                             |

|     | 21.6   | Multiprocessor Communications                         | 123                             |

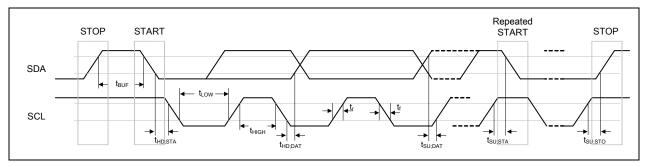

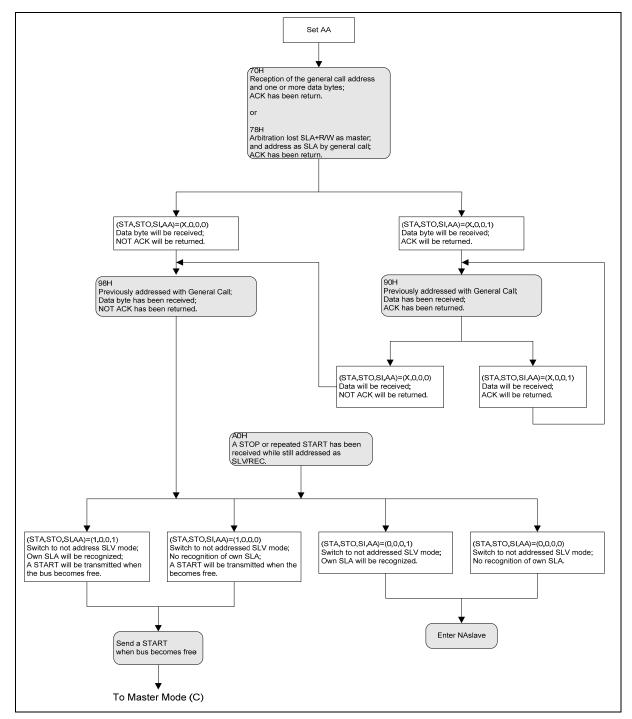

| 22  | I2C SI | ERIAL CONTROL                                         | 125                             |

|     | 22.1   | I2C Port                                              | 125                             |

|     | 22.2   | SFR for I2C Function                                  | 126                             |

|     |        | 22.2.1 I2C Address Registers, I2ADDR                  |                                 |

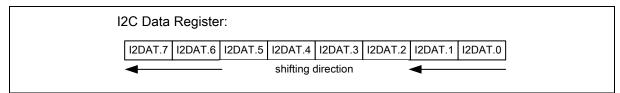

|     |        | 22.2.2 I2C Data Register, I2DAT                       |                                 |

|     |        | 22.2.3 I2C Control Register, I2CON                    |                                 |

|     |        | 22.2.4 I2C Status Register, I2STATUS                  |                                 |

|     |        | 22.2.5 I2C Clock Baud Rate Bits, I2CLK                |                                 |

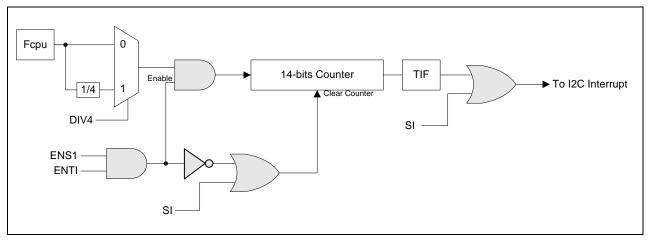

|     |        | 22.2.6 I2C Time-out Counter Register, I2TOC           |                                 |

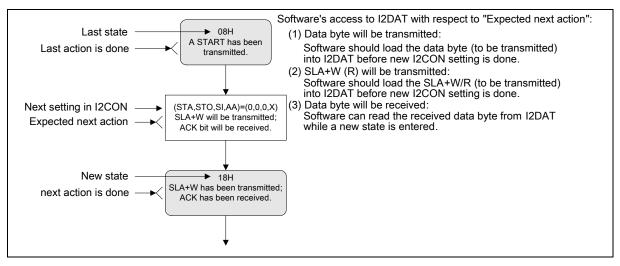

|     | 22.3   | Modes of Operation                                    |                                 |

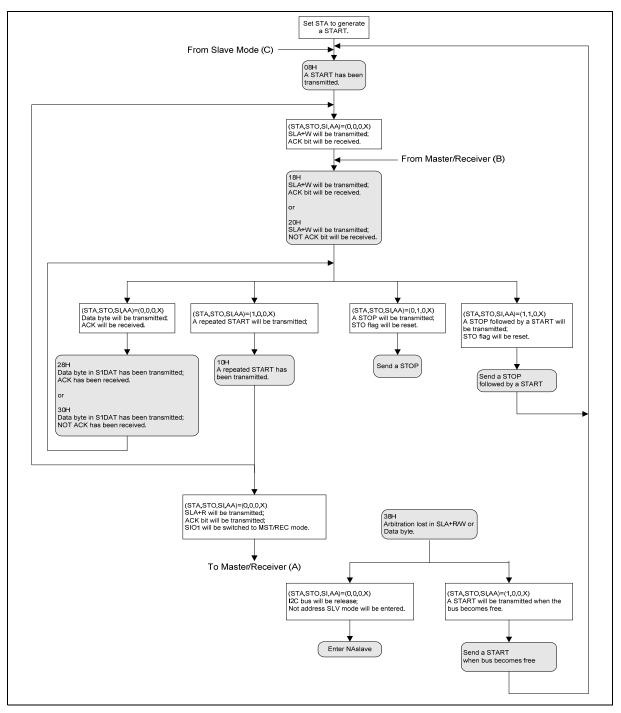

|     |        | 22.3.1 Master Transmitter Mode                        |                                 |

|     |        | 22.3.1 Master Transmitter Mode                        |                                 |

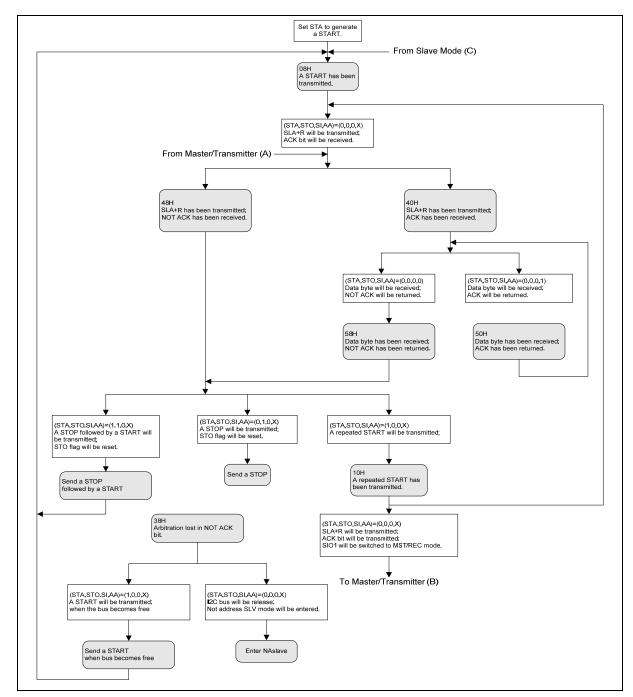

|     |        | 22.3.2 Master Receiver Mode                           |                                 |

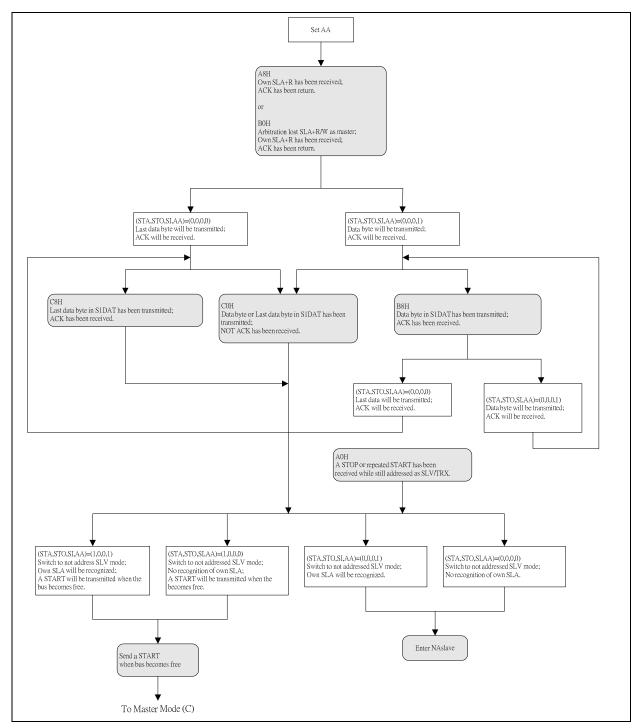

|     |        | 22.3.4 Slave Transmitter Mode                         |                                 |

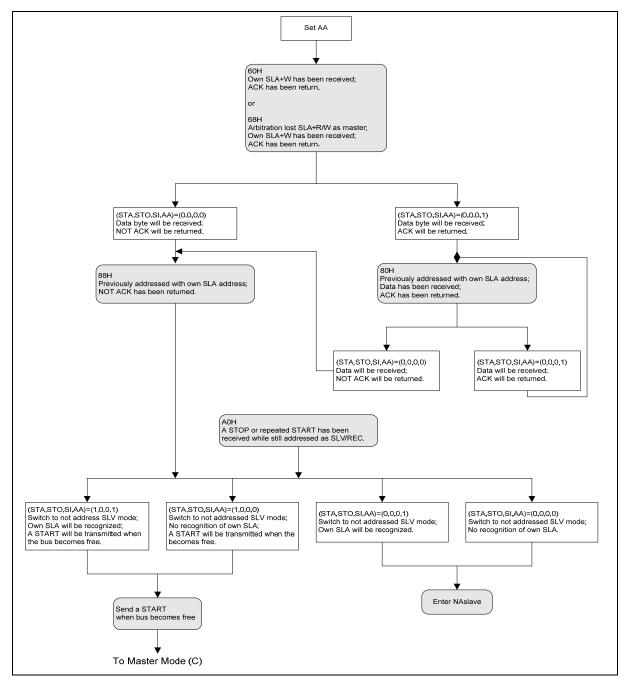

|     | 22.4   | Data Transfer Flow in Five Operating Modes            |                                 |

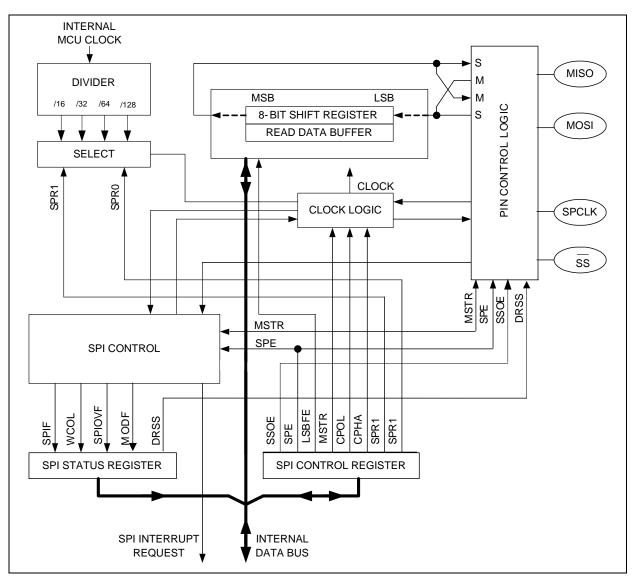

| 23  |        | AL PHERIPHERAL INTERFACE (SPI)                        |                                 |

| 23  |        |                                                       |                                 |

|     | 23.1   | General descriptions                                  |                                 |

|     | 23.2   | Block descriptions                                    |                                 |

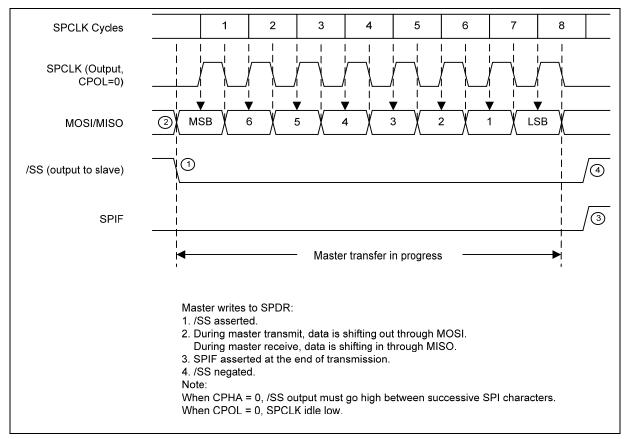

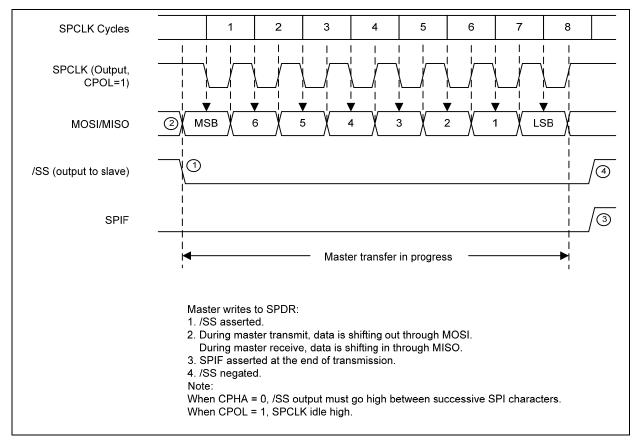

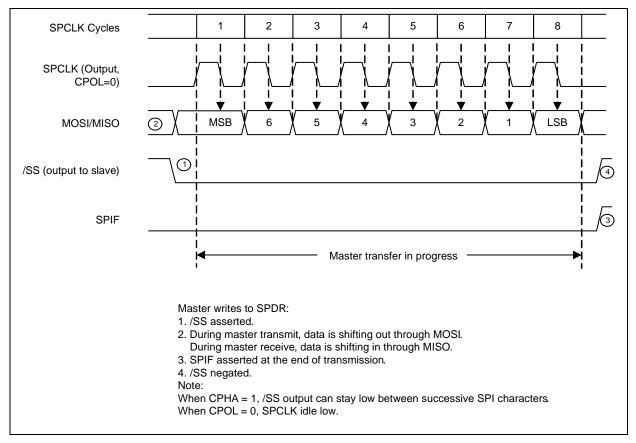

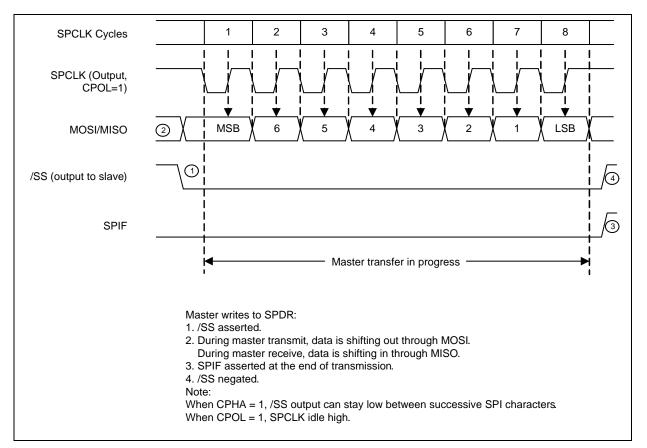

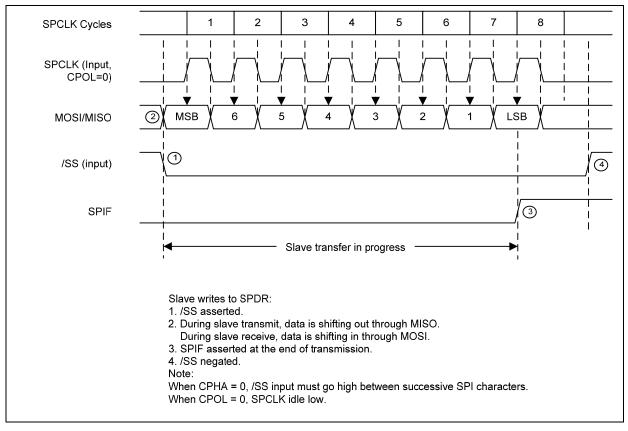

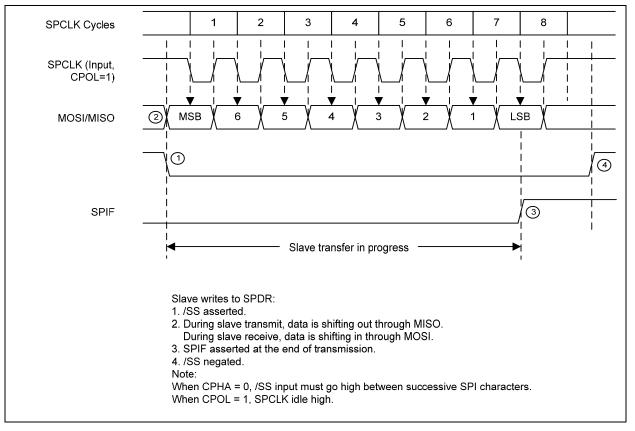

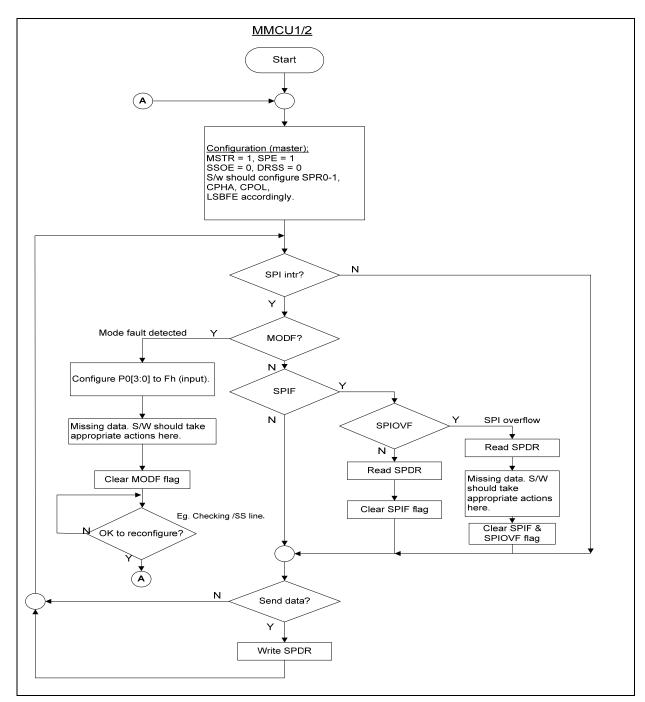

|     | 23.3   | Functional descriptions                               | 138                             |

|     |        | 23.3.1 Master mode                                    |                                 |

|     |        | 23.3.2 Slave Mode                                     |                                 |

|     |        | 23.3.3 Slave select                                   |                                 |

|     |        | 23.3.4 Slave Select output enable                     |                                 |

|     |        | 23.3.5 SPI I/O pins mode                              |                                 |

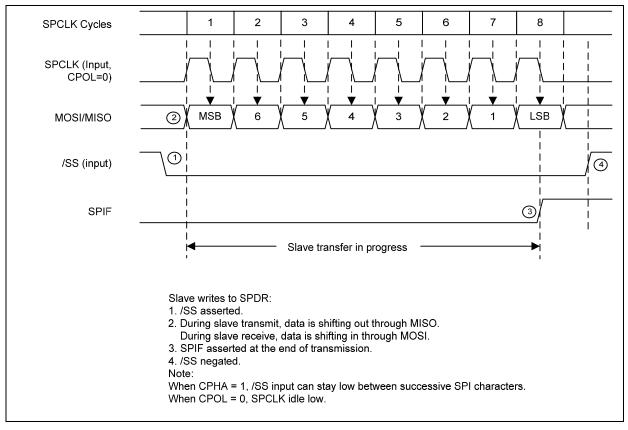

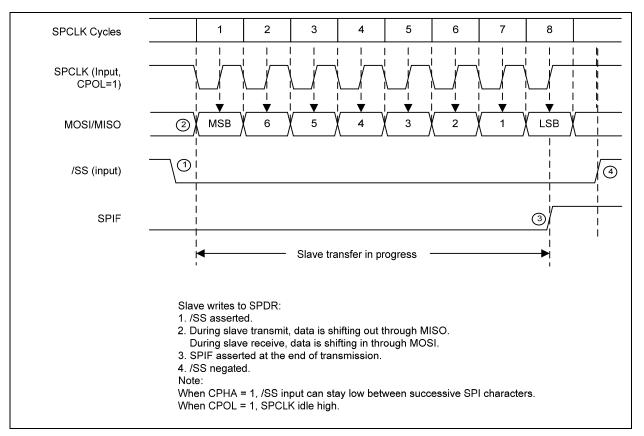

|     |        | 23.3.6 Programmable serial clock's phase and polarity |                                 |

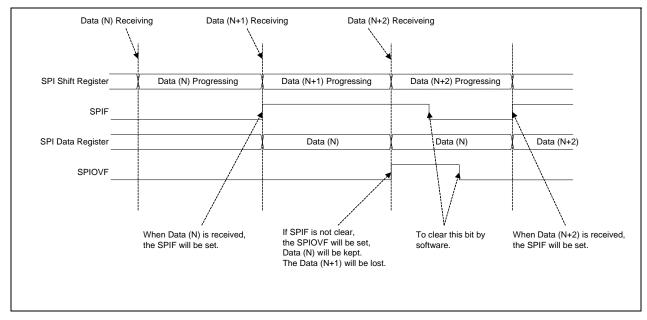

|     |        | 23.3.7 Receive double buffered data register          |                                 |

|     |        | 23.3.8 LSB first enable                               |                                 |

|     |        | 23.3.9 Write Collision detection                      |                                 |

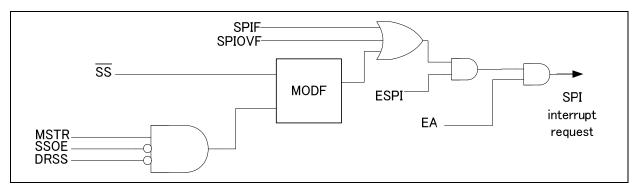

|     |        | 23.3.10 Transfer complete interrupt                   |                                 |

| ~ ( |        | 23.3.11 Mode Fault                                    |                                 |

| 24  |        |                                                       |                                 |

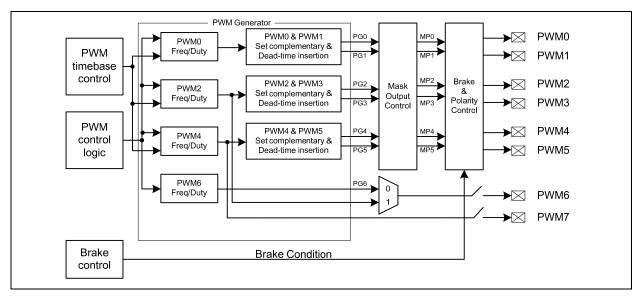

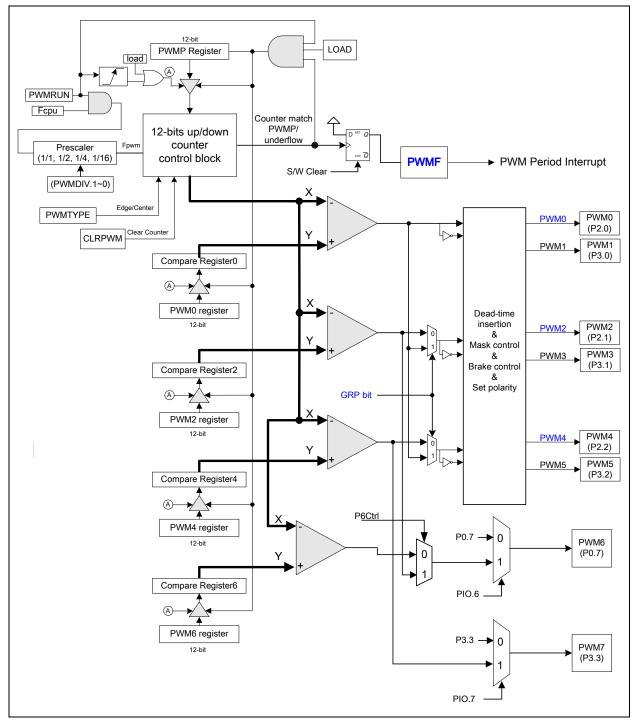

| 25  |        | E-WIDTH-MODULATED (PWM) OUTPUTS                       |                                 |

|     | 25.1   | PWM Features                                          | 155                             |

|     | 25.2   | PWM Operation                                         | 157                             |

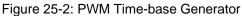

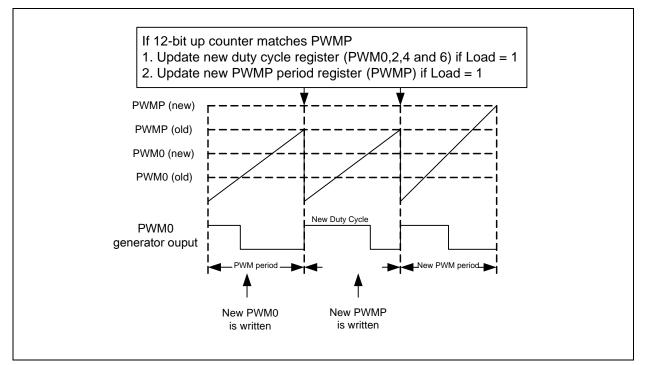

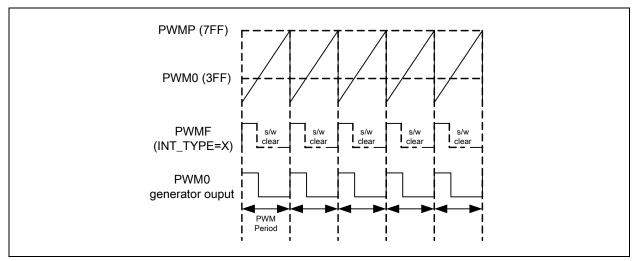

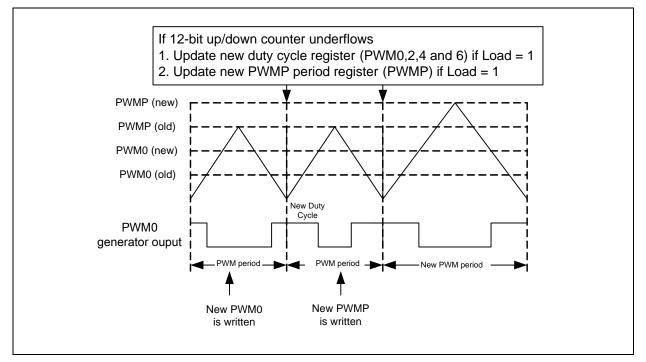

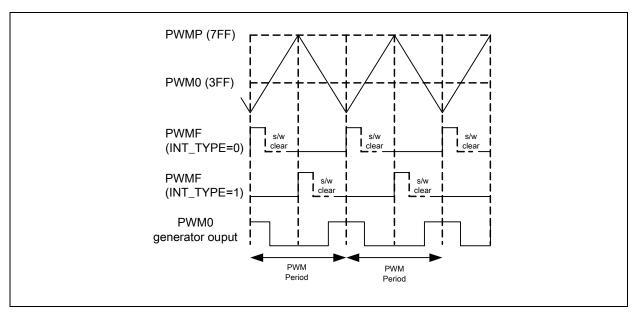

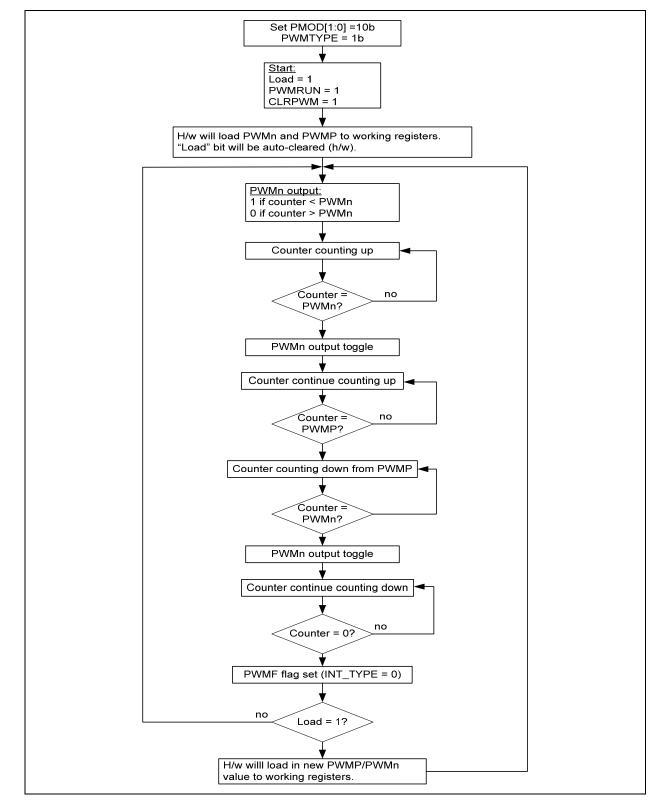

|     |        | 25.2.1 PWM Operation Mode                             | 158                             |

|     |        | 25.2.2 Edge aligned PWM (up-counter)                  | 158                             |

|     |        | 25.2.3 Center Aligned PWM (up/down counter)           |                                 |

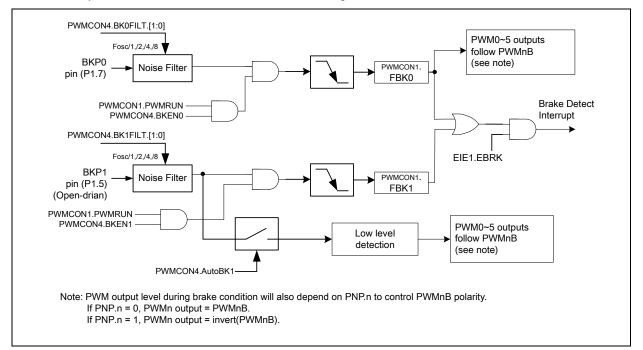

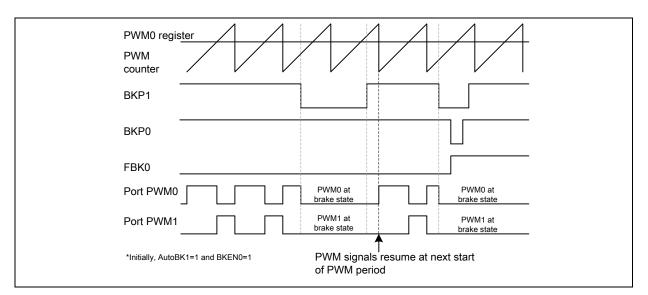

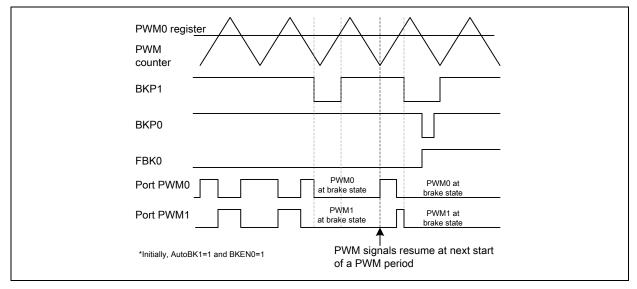

|     | 25.3   | PWM Brake Function                                    |                                 |

|     |        | Publication Release Date: Fe<br>- 3 -                 | bruary 3, 2010<br>Revision V0.1 |

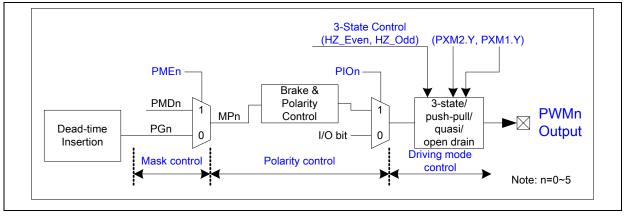

|    | 25.4  | PWM Output Driving Control                        | 166 |

|----|-------|---------------------------------------------------|-----|

|    | 25.5  | PWM modes                                         | 166 |

|    |       | 25.5.1 Independent mode                           | 166 |

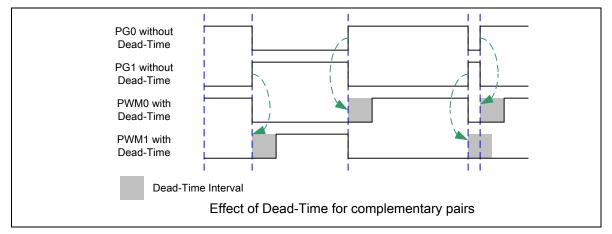

|    |       | 25.5.2 Complementary mode                         | 167 |

|    |       | 25.5.3 Synchronous mode                           |     |

|    |       | 25.5.4 Group mode                                 |     |

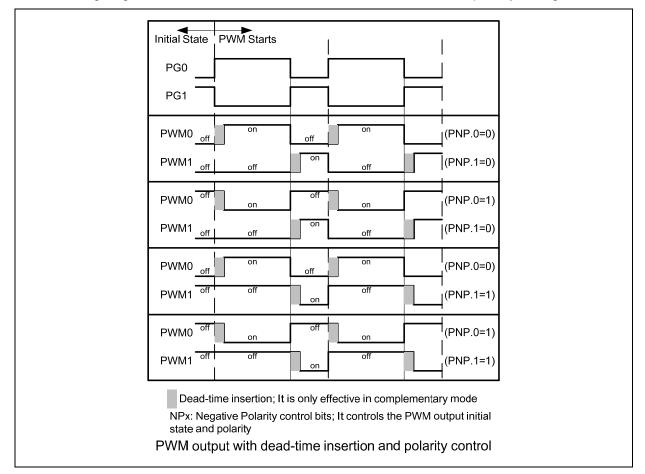

|    | 25.6  | Polarity Control                                  |     |

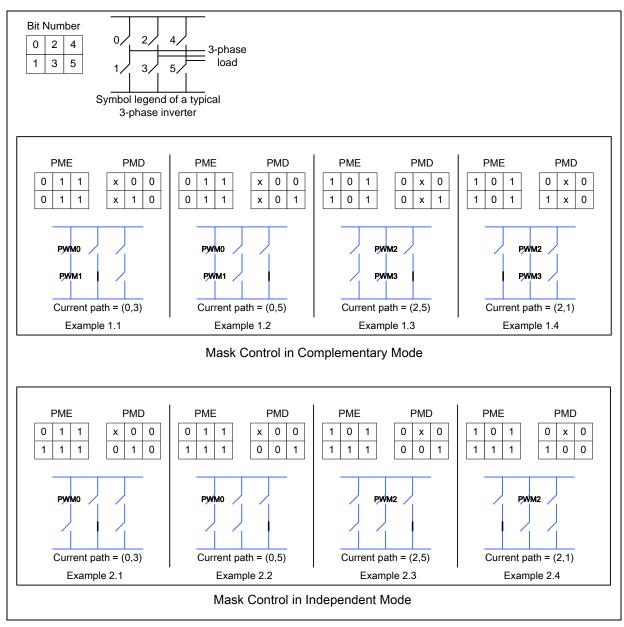

|    | 25.7  | PWM Mask Output                                   |     |

|    | 25.8  | SFR of PWM Unit                                   | 172 |

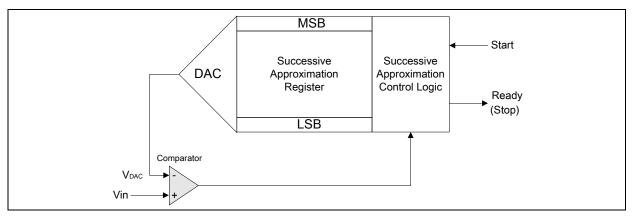

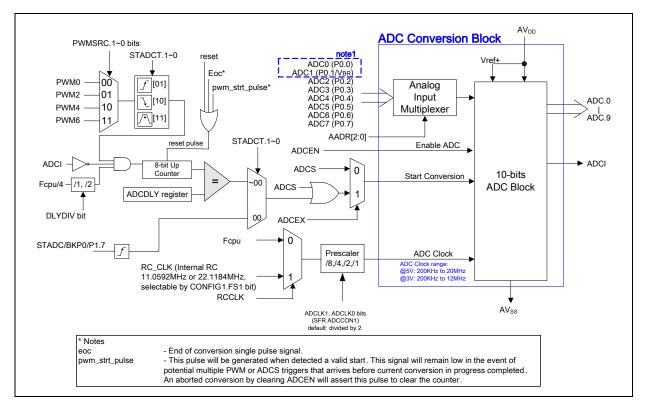

| 26 | ANALO | DG-TO-DIGITAL CONVERTER (ADC)                     | 173 |

|    | 26.1  | Operation of ADC                                  | 173 |

|    |       | 26.1.1 Normal Operation of ADC                    |     |

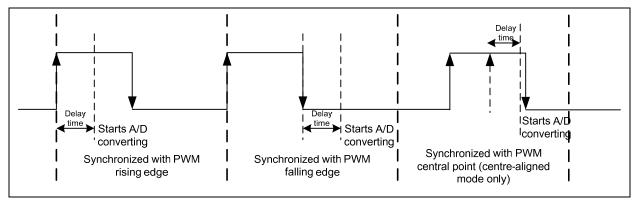

|    |       | 26.1.2 ADC Start Synchronous with PWM             |     |

|    | ~~~~  | 26.1.3 ADC Converting in Power-dwon and Idle Mode |     |

|    | 26.2  | ADC Resolution and Analog Supply:                 |     |

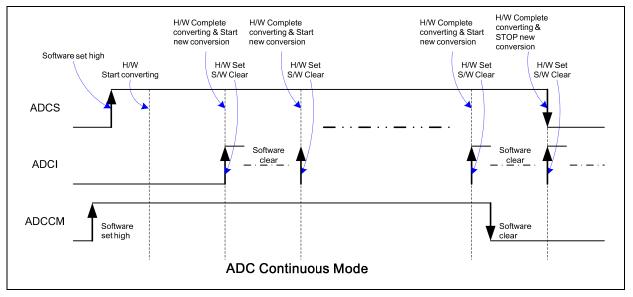

|    | 26.3  | ADC Continuous Mode                               |     |

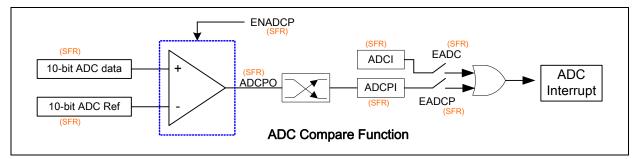

|    | 26.4  | ADC Compare Function                              | 176 |

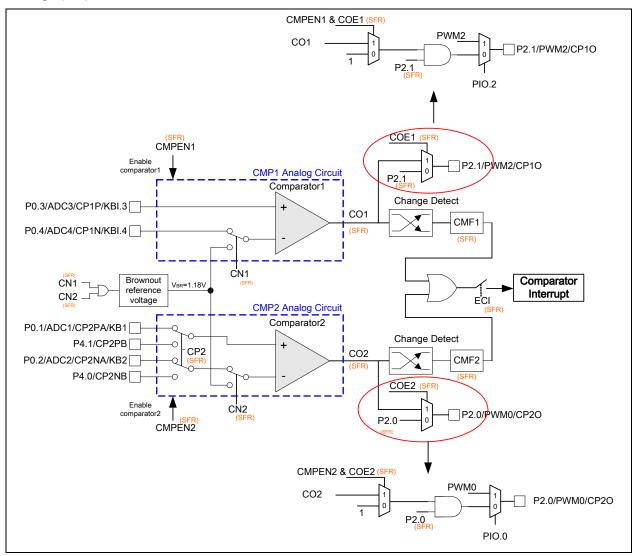

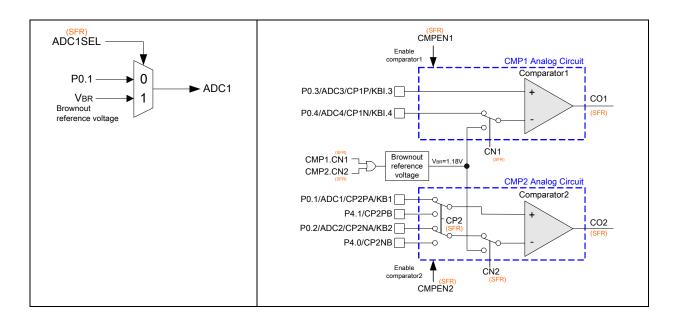

| 27 |       | DG COMPARATORS                                    |     |

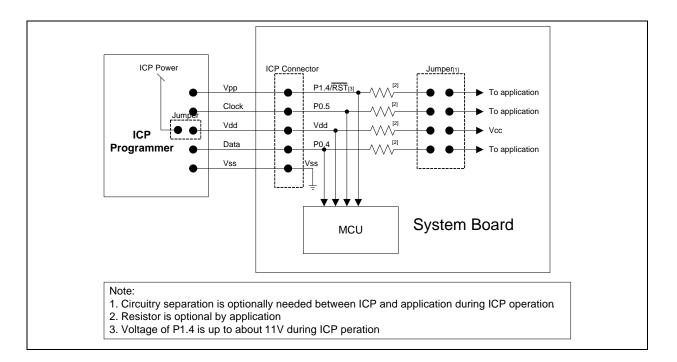

| 28 | •     | N-CIRCUIT PROGRAM) FLASH PROGRAM                  |     |

| 29 |       | IG BITS                                           |     |

|    | 29.1  | CONFIG0                                           | 180 |

|    | 29.2  | CONFIG1                                           | 182 |

| 30 | ELECT | TRICAL CHARACTERISTICS                            | 184 |

|    | 30.1  | Absolute Maximum Ratings                          | 184 |

|    | 30.2  | DC Electrical Characteristics                     | 185 |

|    | 30.3  | ADC Converter DC Electrical Characteristics       | 187 |

|    | 30.4  | Comparator Electrical Characteristics             | 188 |

|    | 30.5  | AC Electrical Characteristics                     | 189 |

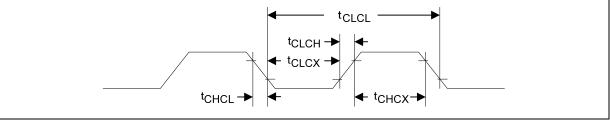

|    |       | 30.5.1 External Clock Characteristics             | 189 |

|    |       | 30.5.2 Supplied Voltage-Frequency                 | 189 |

|    |       | 30.5.3 Internal RC Oscillator Characteristics     | 189 |

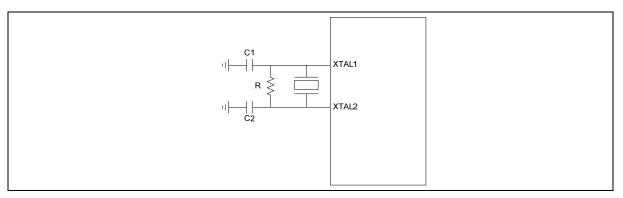

|    |       | 30.5.4 Typical Crystal Application Circuits       |     |

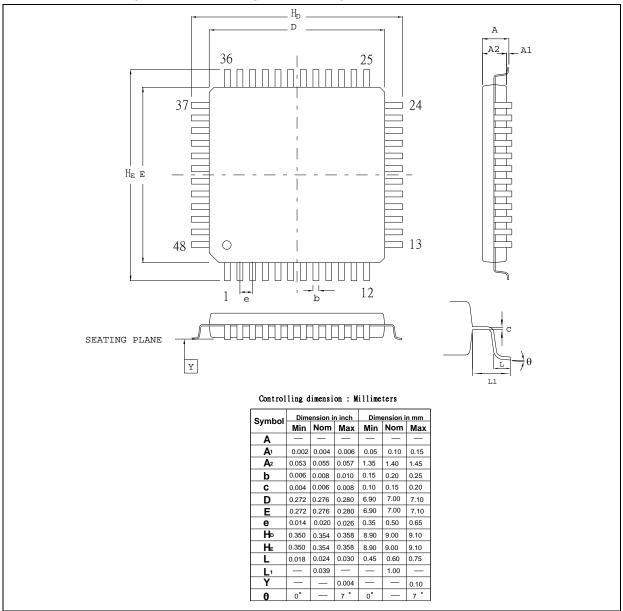

| 31 | PACK  | AGE DIMENSIONS                                    |     |

|    | 31.1  | 48L LQFP (7x7x1.4mm footprint 2.0mm)              | 191 |

| 32 | APPLI | CATION NOTE                                       | 192 |

|    | 32.1  | Programming note                                  | 192 |

|    |       | 32.1.1 Access to brownout reference voltage       |     |

|    |       | 32.1.2 ADC programming note                       |     |

|    | 32.2  | MCU hardware note                                 | 194 |

|    | 32.2.1              | Types of I/O pins |     |

|----|---------------------|-------------------|-----|

| 33 | <b>REVISION HIS</b> | STORY             | 195 |

#### **1 GENERAL DESCRIPTION**

N79E235 series are 8-bit Turbo 51 microcontrollers which have embedded Flash that can be programmed by ICP (In Circuit Program) or by writer. The instruction sets of the N79E235 series are fully compatible with the standard 8052. N79E235 series contain a **16K/8K** bytes of main Flash EPROM; a **256** bytes of RAM; **256** bytes AUX-RAM; **256** bytes NVM Data Flash EPROM support; **two** 16-bit timer/counters; **one** 16-bit timer with 3 capture inputs; **one** 12-bit capture/compare/auto-reload timer; **8**-channel multiplexed 10-bit A/D converter; **8**-channel 12-bit PWM that includes 6-channel for 3 pairs complementary PWM; **three** serial ports that includes a SPI, an I2C and an enhanced full duplex serial port; **two** analog comparators; 3-level selectable Brownout detector. These peripherals are supported by **XX** sources of four-level interrupt capability. To facilitate programming and verification, the Flash EPROM inside N79E235 series allow the program memory to be programmed and read electronically. Once the code is confirmed, the user can protect the code for security.

N79E235 series, built-in rich functions and peripheral, suit to home appliance and general application.

## nuvoTon

#### 2 FEATURES

- Fully static design 8-bit Turbo 51 CMOS microcontroller;

- Operating temperature range and operating frequency

- N79E23xA/N79E23xRA series: -40°C ~85°C

- $V_{DD} = 4.5V$  to 5.5V @40MHz

- $V_{DD} = 3.0V$  to 5.5V @24MHz

- $V_{DD} = 2.4V$  to 5.5V @8MHz

- 85x85xFlexible CPU clock source configurable by config-bit and software:

- High speed external oscillator: Up to 40MHz Crystal and resonator (enabled by config-bit).

- Internal oscillator: Nominal 22MHz/11MHz (selected by config-bit) N79E23xA series: 22MHz/11MHz with ±25% accuracy N79E23xRA series: 22.1184MHz/11.0592MHz with ±2% accuracy, at 3.3V/25°C

- On-chip Memory

- 16K/8K bytes of Application Program Flash memory, with ICP and External Writer programmable mode.

- 256 bytes (8 pages x 32 bytes) Data Flash for customer data storage used and 10K writer cycles; Data Flash program/erase V<sub>DD</sub>=3.0V to 5.5V

- 256 bytes of on-chip scratch-pad RAM.

- 256 bytes of auxiliary RAM, software-selectable, accessed by MOVX instruction.

- Maximum 36 I/O pins.

- Four outputs mode and TTL/Schmitt trigger selectable Port.

- 17 interrupts source with four levels of priority.

- Four timer/counters.

- Two 16-bit timer/counters

- One 16-bit timer supports 3 capture inputs capability for hall sensor feedback.

- One 12-bit timer supports 12-bit auto reload timer, capture and compare mode.

- Three serial ports

- One enhanced full duplex UART port with framing error detection and automatic address recognition.

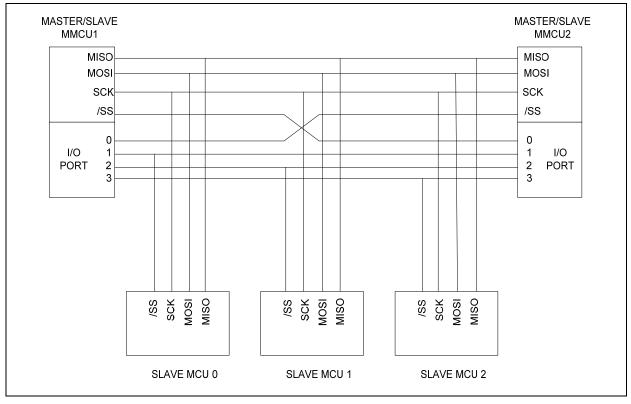

- One SPI with master/slave capability.

- One I2C with master/slave capability.

- Four independent 12-bit PWM duty control units with maximum 8 port pins:

- Six PWM output channels with mask control for BLDC application.

- Three pairs complementary PWM with programmable dead-time insertion

- Independent polarity setting for each channel

- Two brake/fault input pins

- Up to two channels PWM independent from paired PWM channels.

- Eight-channel multiplexed with 10-bits A/D converter.

- Two analog comparators with optional internal reference voltage input at negative end.

- Eight-keypad interrupt inputs.

- Built-in power management.

- Idle mode

- Power down mode

- LED drive capability (20mA) on all port pins.

- Config-bits selectable 3 levels( 4.5V/3.8V/2.6V) Brown-Out voltage detect interrupt and reset.

- Independent Programmable Watchdog Timer.

- Program and Data Flash security protection.

- Development Tools:

- JTAG ICE(In Circuit Emulation) tool

- ICP(In Circuit Programming) writer

- Packages:

- Lead Free (RoHS) LQFP 48: N79E235ALG series (-40°C ~85°C)

- Lead Free (RoHS) LQFP 48: N79E235RALG series (-40°C ~85°C)

- Lead Free (RoHS) LQFP 48: N79E234ALG series (-40°C ~85°C)

- Lead Free (RoHS) LQFP 48: N79E234RALG series (-40°C ~85°C)

#### **3 PARTS INFORMATION LIST**

#### 3.1 Lead Free (RoHS) Parts information list

Table 3-1 Lead Free (RoHS) Parts information list

| PART NO.    | PROGRAM<br>FLASH<br>EPROM | RAM       | DATA<br>FLASH<br>EPROM | TEMP<br>℃ | INTERNAL<br>RC OSC <sup>1</sup> | PACKAGE |

|-------------|---------------------------|-----------|------------------------|-----------|---------------------------------|---------|

| N79E235ALG  | 16KB                      | 256B+256B | 256B                   | -40~85°C  | 22MHz ±<br>25%                  | LQFP-48 |

| N79E235RALG | 16KB                      | 256B+256B | 256B                   | -40~85°C  | 22.1184MHz<br>± 2%              | LQFP-48 |

| N79E234ALG  | 8KB                       | 256B+256B | 256B                   | -40~85°C  | 22MHz ±<br>25%                  | LQFP-48 |

| N79234RALG  | 8KB                       | 256B+256B | 256B                   | -40~85°C  | 22.1184MHz<br>± 2%              | LQFP-48 |

Note:

1. Factory calibration condition:  $V_{DD}$ =3.3V, TA = 25°C

### nuvoTon

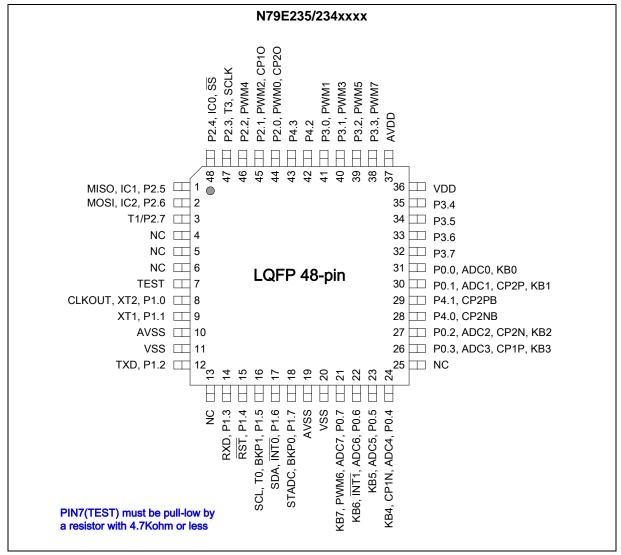

#### **4 PIN CONFIGURATION**

### **5 PIN DESCRIPTION**

| SYMBOL | Alternate<br>Function 1 | Alternate<br>function 2 | Alternate<br>function 3 | Туре                                        | DESCRIPTIONS                            |  |  |  |

|--------|-------------------------|-------------------------|-------------------------|---------------------------------------------|-----------------------------------------|--|--|--|

|        | VI                      | DD                      | Р                       | POWER SUPPLY: Supply voltage for operation. |                                         |  |  |  |

|        | VS                      | SS                      |                         | Р                                           | GROUND: Ground potential.               |  |  |  |

|        | AV                      | DD                      |                         | Р                                           | ANALOG Power Supply                     |  |  |  |

|        | AV                      | 'SS                     |                         | Р                                           | ANALOG GROUND.                          |  |  |  |

| P0.0   | ADC0                    |                         | KB0                     | I/O                                         | Port0:                                  |  |  |  |

| P0.1   | ADC1                    | CP2PA                   | KB1                     | I/O                                         | Support 4 mode output and 2 mode input. |  |  |  |

| P0.2   | ADC2                    | CP2NA                   | KB2                     | I/O                                         | Multifunction pins.                     |  |  |  |

| P0.3   | ADC3                    | CP1P                    | KB3                     | I/O                                         |                                         |  |  |  |

| P0.4   | ADC4                    | CP1N                    | KB4                     | I/O                                         |                                         |  |  |  |

| P0.5   | ADC5                    |                         | KB5                     | I/O                                         |                                         |  |  |  |

| P0.6   | ADC6                    | /INT1                   | KB6                     | I/O                                         |                                         |  |  |  |

| P0.7   | ADC7                    | PWM6                    | KB7                     | I/O                                         |                                         |  |  |  |

| P1.0   | XT2                     | CLKOUT                  |                         | I/O                                         | Port1:                                  |  |  |  |

| P1.1   | XT1                     |                         |                         | I/O                                         | Support 4 mode output and 2 mode input. |  |  |  |

| P1.2   | TXD                     |                         |                         | I/O                                         | Multifunction pins.                     |  |  |  |

| P1.3   | RXD                     |                         |                         | I/O                                         | P1.5 and P1.6 are permanently in        |  |  |  |

| P1.4   | /RST                    |                         |                         | <mark>I, H(rst)</mark>                      | Open-Drain type.                        |  |  |  |

| P1.5   | то                      | SCL                     | BKP1                    | D                                           |                                         |  |  |  |

| P1.6   | /INT0                   | SDA                     |                         | D                                           |                                         |  |  |  |

| P1.7   |                         | STADC                   | BKP0                    | I/O                                         |                                         |  |  |  |

| P2.0   | PWM0                    | CP2O                    |                         | I/O                                         | Port2:                                  |  |  |  |

| P2.1   | PWM2                    | CP1O                    |                         | I/O                                         | Support 4 mode output and 2 mode input. |  |  |  |

| P2.2   | PWM4                    |                         |                         | I/O                                         | Multifunction pins.                     |  |  |  |

| P2.3   | ТЗ                      | SCLK                    |                         | I/O                                         |                                         |  |  |  |

| P2.4   | IC0                     | /SS                     |                         | I/O                                         |                                         |  |  |  |

## nuvoTon

| SYMBOL               | Alternate<br>Function 1 | Alternate<br>function 2 | Alternate<br>function 3 | Туре | DESCRIPTIONS                                        |

|----------------------|-------------------------|-------------------------|-------------------------|------|-----------------------------------------------------|

| P2.5                 | IC1                     | MISO                    |                         | I/O  |                                                     |

| P2.6                 | IC2                     | MOSI                    |                         | I/O  |                                                     |

| P2.7                 | T1                      |                         |                         | I/O  |                                                     |

| P3.0                 | PWM1                    |                         |                         | I/O  | Port3:                                              |

| P3.1                 | PWM3                    |                         |                         | I/O  | Support 4 modes output and 2 modes input.           |

| P3.2                 | PWM5                    |                         |                         | I/O  | Multifunction pins.                                 |

| P3.3 <sup>*</sup>    | PWM7                    |                         |                         | I/O  |                                                     |

| P3.4 <sup>**</sup>   |                         |                         |                         | I/O  |                                                     |

| P3.5 <sup>**</sup>   |                         |                         |                         | I/O  |                                                     |

| P3.6 <sup>**</sup>   |                         |                         |                         | I/O  |                                                     |

| P3.7 <sup>**</sup>   |                         |                         |                         | I/O  |                                                     |

| P4.0 <sup>*/**</sup> |                         | CP2NB                   |                         | I/O  | Support 4 modes output and 2                        |

| P4.1 <sup>*/**</sup> |                         | CP2PB                   |                         | I/O  | -modes input.                                       |

| P4.2 <sup>*/**</sup> |                         |                         |                         | I/O  |                                                     |

| P4.3 <sup>*/**</sup> |                         |                         |                         | I/O  |                                                     |

| TEST                 |                         |                         |                         | Ι    | Must be pull-low by a resistor with 4.7Kohm or less |

TYPE: P: P: power, I: input, O: output, I/O: bi-directional with 4-type I/O modes,, H: Internal pull-up, L: Internal pull low, D: Open Drain

Notes:

- During Power-on-reset, all port pins are in tri-stated.

- After power-on-reset, all port pins state will follow CONFIG0.PRHI bit definition.

- All digital input pins support software enabled schmitt trigger buffer which is selected by SFR PORTS (ECH).

In application if MCU pins need external pull-up, it is recommended to add a pull-up resistor (10K $\Omega$ ) between pin and power(V<sub>DD</sub>) instead of directly wiring pin to V<sub>DD</sub> for enhancing EMC.

### 6 MEMORY ORGANIZATION

N79E235 series separate the memory into two separate sections, the Program Memory and the Data Memory. The Program Memory is used to store the instruction op-codes, while the Data Memory is used to store data or for memory mapped devices.

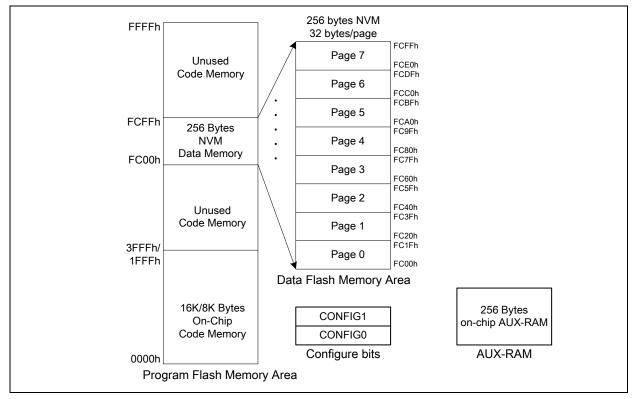

Figure 6-1 N79E235 series Memory Map

#### 6.1 Program Flash Memory

The Program Memory on N79E235 series can be up to **16K/8K** bytes long. All instructions are fetched for execution from this memory area. The MOVC instruction can also access this memory region.

#### 6.2 Data Flash Memory

The NVM Data Memory of Flash EPROM on the N79E235 series is **256** bytes long, with page size of 16 bytes. The N79E235 series read the content of data memory by using "MOVC A, @A+DPTR". To write data is by NVMADDRL, NVMDAT and NVMCON SFR's registers.

#### 6.3 Data Memory (accessed by MOVX)

N79E235 provides 256 bytes AUX RAM accessed by the MOVX instruction. The data memory region is from 0000H to 00FFH. Figure 6-1 shows the memory map for this product series.

#### 6.4 Scratch-pad RAM and Register Map

As mentioned before, N79E235 series have separate Program and Data Memory areas. The on-chip 256 bytes scratch pad RAM is in addition to the external memory. There are also several Special Function Registers (SFRs) which can be accessed by software. The SFRs can be accessed only by direct addressing, while the on-chip RAM can be accessed by either direct or indirect addressing.

| FFH<br>80H | Indirect<br>RAM<br>Addressing                | SFR<br>Direct<br>Addressing<br>Only |   |  |

|------------|----------------------------------------------|-------------------------------------|---|--|

| 7FН<br>00Н | Direct<br>&<br>Indirect<br>RAM<br>Addressing |                                     | _ |  |

#### Figure 6-2 N79E235 series RAM and SFR Memory Map

Since the scratch-pad RAM is only 256 bytes it can be used only when data contents are small. There are several other special purpose areas within the scratch-pad RAM. These are illustrated in next figure.

| FFH               |    |    |    |       |      |    |    |    |

|-------------------|----|----|----|-------|------|----|----|----|

|                   |    |    | In | direc | t RA | M  |    |    |

| 80H<br>7FH        |    |    |    |       |      |    |    |    |

|                   |    |    | D  | irect | RAI  | M  |    |    |

| 30H<br>2FH        | 7F | 7E | 7D | 7C    | 7B   | 7A | 79 | 78 |

| 2EH               | 77 | 76 | 75 | 74    | 73   | 72 | 71 | 70 |

| 2DH               | 6F | 6E | 6D | 6C    | 6B   | 6A | 69 | 68 |

| 2CH               | 67 | 66 | 65 | 64    | 63   | 62 | 61 | 60 |

| 2BH               | 5F | 5E | 5D | 5C    | 5B   | 5A | 59 | 58 |

| 2AH               | 57 | 56 | 55 | 54    | 53   | 52 | 51 | 50 |

| 29H               | 4F | 4E | 4D | 4C    | 4B   | 4A | 49 | 48 |

| 28H               | 47 | 46 | 45 | 44    | 43   | 42 | 41 | 40 |

| 27H               | 3F | 3E | 3D | 3C    | 3B   | ЗA | 39 | 38 |

| 26H               | 37 | 36 | 35 | 34    | 33   | 32 | 31 | 30 |

| 25H               | 2F | 2E | 2D | 2C    | 2B   | 2A | 29 | 28 |

| 24H               | 27 | 26 | 25 | 24    | 23   | 22 | 21 | 20 |

| 23H               | 1F | 1E | 1D | 1C    | 1B   | 1A | 19 | 18 |

| 22H               | 17 | 16 | 15 | 14    | 13   | 12 | 11 | 10 |

| 21H               | 0F | 0E | 0D | 0C    | 0B   | 0A | 09 | 08 |

| 20H               | 07 | 06 | 05 | 04    | 03   | 02 | 01 | 00 |

| 1FH<br>18H<br>17H |    |    |    | Bar   | nk 3 |    |    |    |

| 10H               |    |    |    | Bar   | nk 2 |    |    |    |

| 0ĔH<br>08H<br>07H |    |    |    | Bar   | nk 1 |    |    |    |

| 00H               |    |    |    | Bar   | nk O |    |    |    |

Figure 6-3 Scratch-pad RAM

#### 6.5 Working Registers

There are four sets of working registers, each consisting of eight 8-bit registers. These are termed ads Banks 0, 1, 2, and 3. Individual registers within these banks can be directly accessed by separate instructions. These individual registers are named as R0, R1, R2, R3, R4, R5, R6 and R7. However, at any one time N79E235 series can work with only one particular bank. The bank selection is done by setting RS1-RS0 bits in the PSW. The R0 and R1 registers are used to store the address for indirect accessing.

#### 6.6 Bit addressable Locations

The Scratch-pad RAM area from location 20h to 2Fh is byte as well as bit addressable. This means that a bit in this area can be individually addressed. In addition some of the SFRs are also bit addressable. The instruction decoder is able to distinguish a bit access from a byte access by the type of the instruction itself. In the SFR area, any existing SFR whose address ends in a 0 or 8 is bit addressable.

#### 6.7 Stack

The scratch-pad RAM can be used for the stack. This area is selected by the Stack Pointer (SP), which stores the address of the top of the stack. Whenever a jump, call or interrupt is invoked the return address is placed on the stack. There is no restriction as to where the stack can begin in the RAM. By default however, the Stack Pointer contains 07h at reset. The user can then change this to any value desired. The SP will point to the last used value. Therefore, the SP will be incremented and then address saved onto the stack. Conversely, while popping from the stack the contents will be read first, and then the SP is decreased.

#### 7 SPECIAL FUNCTION REGISTERS

N79E235 series use Special Function Registers (SFRs) to control and monitor peripherals and their Modes. The SFRs reside in the register locations 80-FFh and are accessed by direct addressing only. Some of the SFRs are bit addressable. This is very useful in cases where we wish to modify a particular bit without changing the others. The SFRs that are bit addressable are those whose addresses end in 0 or 8. N79E235 series contain all the SFRs present in the standard 8052. However some additional SFRs are added. In some cases the unused bits in the original 8052, have been given new functions. The list of the SFRs is as follows.

| F8         | IP1                  |        | P4M1   | P4M2                 | PWMCON4 | PWM6L    | PWM6H                | AUXR2   |

|------------|----------------------|--------|--------|----------------------|---------|----------|----------------------|---------|

| F0         | В                    |        |        | SPCR                 | SPSR    | SPDR     | PADIDS               | IP1H    |

| E8         | EIE1                 |        |        |                      | PORTS   | PME      | PMD                  | IP2H    |

| E0         | ACC                  | ADCCON | ADCH   | ADCCON1              | CCL0    | CCH0     | CCL1                 | CCH1    |

| D8         | WDCON <sup>(3)</sup> | PWMPL  | PWM0L  |                      | PWMCON1 | PWM2L    |                      | PWMB    |

| D0         | PSW                  | PWMPH  | PWM0H  |                      | EIE2    | PWM2H    |                      | PWMCON3 |

| C8         | T2CON                | T2MOD  | RCAP2L | RCAP2H               | TL2     | TH2      | NVMCON               | NVMDAT  |

| C0         | I2CON                | I2ADDR | T3CON  | PNP                  |         |          | NVMADDRL             | ТА      |

| B8         | IP0                  | SADEN  |        |                      | I2DATA  | I2STATUS | I2CLK                | I2TIMER |

| В0         | P3                   | P0M1   | P0M2   | P1M1                 | P1M2    | P2M1     | P2M2                 | IP0H    |

| <b>A</b> 8 | IE                   | SADDR  |        | DTCNT <sup>(3)</sup> | CMP1    | CMP2     | PDTC0 <sup>(3)</sup> | ADCDLY  |

| A0         | P2                   | KBI    | AUXR1  | CAPCON0              | CAPCON1 | P4       | CCL2                 | CCH2    |

| 98         | SCON                 | SBUF   | IP2    | PIO                  | ADCRL   | ADCRH    | P3M1                 | P3M2    |

| 90         | P1                   | T3L    | RCAP3L | RCAP3HT3H            |         |          | PWM4L                | PWM4H   |

| 88         | TCON                 | TMOD   | TL0    | TL1                  | TH0     | TH1      | CKCON                |         |

| 80         | P0                   | SP     | DPL    | DPH                  |         |          | DIV                  | PCON    |

#### 7.1 SFR Location Table

Table 7-1 Special Function Register Location Table

Note:

1. The SFRs in the column with dark borders are bit-addressable

2. The table is condensed with eight locations per row. Empty locations indicate that these are no registers at these addresses.

3. With Timed Access Protection on write operation.

| SYMBOL  | DEFINITION                            | ADDRESS | MSB           | BIT ADDRES   | SS, SYMBOL   |                 | LSB          | RESET        |               |               |                                                                                                        |

|---------|---------------------------------------|---------|---------------|--------------|--------------|-----------------|--------------|--------------|---------------|---------------|--------------------------------------------------------------------------------------------------------|

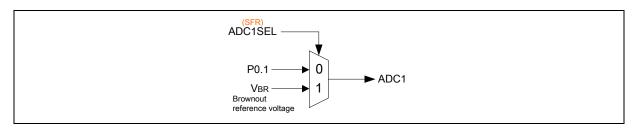

| AUXR2   | AUXR2 CONTROL REGISTER                | FFH     | T1OE          | TIOE TOOE P  |              | PCMP2DI<br>DS.0 | -            | ENCLK        | ADC1SEL       | -             | 0000 0000b                                                                                             |

| PWM6H   | PWM 6 HIGH BITS REGISTER              | FEH     |               | -            |              |                 | PWM6.11      | WM6.10       | PWM6.9        | PWM6.8        | XXXX 0000b                                                                                             |

| PWM6L   | PWM 6 LOW BITS REGISTER               | FDH     | PWM6.7        | PWM6.6       | PWM6.5       | PWM6.4          | PWM6.3       | PWM6.2       | PWM6.1        | PWM6.0        | 0000 0000b                                                                                             |

| PWMCON4 | PWM CONTROL REGISTER 4                | FCH     | BK1FILT.1     | BK1FILT.0    | BK0FILT.1    | BK0FILT.0       | AUTOBK<br>1  | -            | BKEN1         | BKEN0         | 0000 0X00b                                                                                             |

| P4M2    | PORT 4 OUTPUT MODE 2                  | FBH     | -             | -            | -            | -               | P4M2.3       | P4M2.2       | P4M2.1        | P4M2.0        | XXXX 0000b                                                                                             |

| P4M1    | PORT 4 OUTPUT MODE 1                  | FAH     | -             | -            | -            | -               | P4M1.3       | P4M1.2       | P4M1.1        | P4M1.0        | XXXX 0000b                                                                                             |

| IP1     | INTERRUPT PRIORITY 1                  | F8H     | (FF)<br>PCAP  | (FE)<br>PPWM | (FD)<br>PBRK | (FC)<br>PWDI    | (FB)<br>-    | (FA)<br>PCI  | (F9)<br>PKB   | (F8)<br>Pl2   | 0000 X000b                                                                                             |

| IP1H    | INTERRUPT HIGH PRIORITY 1             | F7H     | PCAPH         | PPWMH        | PBRKH        | PWDIH           | -            | PCIH         | PKBH          | PI2H          | 0000 X000b                                                                                             |

| PADIDS  | PORT ADC DIGITAL INPUTS<br>DISABLE    | F6H     | PADIDS.7      | PADIDS.6     | PADIDS.5     | PADIDS.4        | PADIDS.3     | PADIDS.2     | PADIDS.1      | PADIDS.0      | 0000 0000b                                                                                             |

| SPDR    | SERIAL PERIPHERAL DATA<br>REGISTER    | F5H     | SPD.7         | SPD.6        | SPD.5        | SPD.4           | SPD.3        | SPD.2        | SPD.1         | SPD.0         | XXXX XXXXb                                                                                             |

| SPSR    | SERIAL PERIPHERAL STATUS<br>REGISTER  | F4H     | SPIF          | WCOL         | SPIOVF       | MODF            | DRSS         | -            | -             | -             | 0000 0XXXb                                                                                             |

| SPCR    | SERIAL PERIPHERAL<br>CONTROL REGISTER | F3H     | SSOE          | SPE          | LSBFE        | MSTR            | CPOL         | CPHA         | SPR1          | SPR0          | 0000 0100b                                                                                             |

| PCH     | PC COUNTER HIGH REGISTER              | F2H     |               |              |              |                 |              |              |               |               | 0000 0000b                                                                                             |

| PCL     | PC COUNTER LOW REGISTER               | F1H     |               |              |              |                 |              |              |               |               | 0000 0000b                                                                                             |

| В       | B REGISTER                            | F0H     | (F7)          | (F6)         | (F5)         | (F4)            | (F3)         | (F2)         | (F1)          | (F0)          | 0000 0000b                                                                                             |

| IP2H    | INTERRUPT HIGH PRIORITY 2             | EFH     | -             | PT2H         | -            | -               | PSPIH        | -            | -             | PET3H         | X0XX 0XX0b                                                                                             |

| PMD     | PWM MASK DATA REGISTER                | EEH     | -             | -            | PMD.5        | PMD.4           | PMD.3        | PMD.2        | PMD.1         | PMD.0         | XX00 0000b                                                                                             |

| PME     | PWM MASK ENABLE<br>REGISTER           | EDH     | -             | -            | PME.5        | PME.4           | PME.3        | PME.2        | PME.1         | PME.0         | XX00 0000b                                                                                             |

| PORTS   | PORT SHMITT REGISTER                  | ECH     | -             | -            | -            | P4S             | P3S          | P2S          | P1S           | P0S           | XXX0 0000b                                                                                             |

| EIE1    | INTERRUPT ENABLE 1                    | E8H     | (EF)<br>ECPTF | (EE)<br>EPWM | (ED)<br>EBRK | (EC)<br>EWDI    | (EB)<br>-    | (EA)<br>ECI  | (E9)<br>EKB   | (E8)<br>EI2C  | 0000 X000b                                                                                             |

| CCH1    | INPUT CAPTURE 1 HIGH                  | E7H     | CCH1.7        | CCH1.6       | CCH1.5       | CCH1.4          | CCH1.3       | CCH1.2       | CCH1.1        | CCH1.0        | 0000 0000b                                                                                             |

| CCL1    | INPUT CAPTURE 1 LOW                   | E6H     | CCL1.7        | CCL1.6       | CCL1.5       | CCL1.4          | CCL1.3       | CCL1.2       | CCL1.1        | CCL1.0        | 0000 0000b                                                                                             |

| CCH0    | INPUT CAPTURE 0 HIGH                  | E5H     | CCH0.7        | CCH0.6       | CCH0.5       | CCH0.4          | CCH0.3       | CCH0.2       | CCH0.1        | CCH0.0        | 0000 0000b                                                                                             |

| CCL0    | INPUT CAPTURE 0 LOW                   | E4H     | CCL0.7        | CCL0.6       | CCL0.5       | CCL0.4          | CCL0.3       | CCL0.2       | CCL0.1        | CCL0.0        | 0000 0000b                                                                                             |

| ADCCON1 | ADC CONTROL REGISTER 1                | E3H     | ADCLK.1       | ADCLK.0      | STADCT.1     | STADCT.0        | DLYDIV       | ADCCM        | PWMSRC<br>.1  | PWMSRC<br>.0  | 0000 0000b                                                                                             |

| ADCH    | ADC CONVERTER RESULT                  | E2H     | ADC.9         | ADC.8        | ADC.7        | ADC.6           | ADC.5        | ADC.4        | ADC.3         | ADC.2         | XXXX XXXXb                                                                                             |

| ADCCON  | ADC CONTROL REGISTER                  | E1H     | ADC.1         | ADC.0        | ADCEX        | ADCI            | ADCS         | AADR2        | AADR1         | AADR0         | XX00 0000b                                                                                             |

| ACC     | ACCUMULATOR                           | E0H     | (E7)          | (E6)         | (E5)         | (E4)            | (E3)         | (E2)         | (E1)          | (E0)          | 0000 0000b                                                                                             |

| PWMB    | PWM BRAKE OUTPUT                      | DFH     | -             | -            | PWM5B        | PWM4B           | PWM3B        | PWM2B        | PWM1B         | PWM0B         | XX00 0000b                                                                                             |

| PWM2L   | PWM 2 LOW BITS REGISTER               | DDH     | PWM2.7        | PWM2.6       | PWM2.5       | PWM2.4          | PWM2.3       | PWM2.2       | PWM2.1        | PWM2.0        | 0000 0000b                                                                                             |

| PWMCON1 | PWM CONTROL REGISTER 1                | DCH     | PWMRUN        | LOAD         | PWMF         | CLRPWM          | FBK1         | FBK0         | PMOD.1        | PMOD.0        | 0000 0000b                                                                                             |

| PWM0L   | PWM 0 LOW BITS REGISTER               | DAH     | PWM0.7        | PWM0.6       | PWM0.5       | PWM0.4          | PWM0.3       | PWM0.2       | PWM0.1        | PWM0.0        | 0000 0000b                                                                                             |

| PWMPL   | PWM COUNTER LOW<br>REGISTER           | D9H     | PWMP0.7       | PWMP0.6      | PWMP0.5      | PWMP0.4         | PWMP0.3      | PWMP0.2      | PWMP0.1       | PWMP0.0       | 0000 0000b                                                                                             |

| WDCON   | WATCH-DOG CONTROL                     | D8H     | (DF)<br>WDRUN | (DE)<br>-    | (DD)<br>WD1  | (DC)<br>WD0     | (DB)<br>WDIF | (DA)<br>WTRF | (D9)<br>EWRST | (D8)<br>WDCLR | EXTERNAL<br>RESET:<br>0X00 0X00b<br>WATCHDOG<br>RESET:<br>0X000100b<br>POWER ON<br>RESET<br>0X00 0000b |

| PWMCON3 | PWM CONTROL REGISTER 3                | D7H     | HZ_Even       | HZ_Odd       | GRP          | PWMTYPE         | -            | -            | P6CTRL        | INT_TYP       | XX00 XX00b                                                                                             |

|         |                                       |         |               | 000          | 5.0          |                 |              |              |               | E             |                                                                                                        |

| SYMBOL   | DEFINITION                          | ADDRESS | MSB             |                 |               | BIT ADDRES    | S, SYMBOL            |                      |                      | LSB             | RESET                                   |

|----------|-------------------------------------|---------|-----------------|-----------------|---------------|---------------|----------------------|----------------------|----------------------|-----------------|-----------------------------------------|

| PWM2H    | PWM 2 HIGH BITS REGISTER            | D5H     | -               | -               | -             | -             | PWM2.11              | PWM2.10              | PWM2.9               | PWM2.8          | XXXX 0000b                              |

| EIE2     | INTERRUPT ENABLE 2                  | D4H     | -               | ET2             | -             | -             | ESPI                 | -                    | EADCP                | ET3             | X0XX 0X00b                              |

| PWM0H    | PWM 0 HIGH BITS REGISTER            | D2H     | -               | -               | -             | -             | PWM0.11              | PWM0.10              | PWM0.9               | PWM0.8          | XXXX 0000b                              |

| PWMPH    | PWM COUNTER HIGH<br>REGISTER        | D1H     | -               | -               | -             | -             | PWMP.11              | PWMP.10              | PWMP.9               | PWMP.8          | XXXX 0000b                              |

| PSW      | PROGRAM STATUS WORD                 | D0H     | (D7)<br>CY      | (D6)<br>AC      | (D5)<br>F0    | (D4)<br>RS1   | (D3)<br>RS0          | (D2)<br>OV           | (D1)<br>F1           | (D0)<br>P       | 0000 0000b                              |

| NVMDATA  | NVM DATA                            | CFH     | NVMDATA<br>.7   | NVMDATA.<br>6   | NVMDATA.<br>5 | NVMDATA<br>.4 | NVMDAT<br>A.3        | NVMDAT<br>A.2        | NVMDAT<br>A.1        | NVMDAT<br>A.0   | 0000 0000b                              |

| NVMCON   | NVM CONTROL                         | CEH     | EER             | EWR             | -             | -             | -                    | -                    | -                    | -               | 00XX XXXXb                              |

| TH2      | TIMER 2 MSB                         | CDH     | TH2.7           | TH2.6           | TH2.5         | TH2.4         | TH2.3                | TH2.2                | TH2.1                | TH2.0           | 0000 0000b                              |

| TL2      | TIMER 2 LSB                         | CCH     | TL2.7           | TL2.6           | TL2.5         | TL2.4         | TL2.3                | TL2.2                | TL2.1                | TL2.0           | 0000 0000b                              |

| RCAP2H   | TIMER 2 RELOAD MSB                  | СВН     |                 | RCAP2H.6        | RCAP2H.5      |               | RCAP2H.              | RCAP2H.              | RCAP2H.              | RCAP2H.         | 0000 0000b                              |

| RCAP2L   | TIMER 2 RELOAD LSB                  | CAH     | RCAP2L.7        | RCAP2L.6        | RCAP2L.5      | RCAP2L.4      | RCAP2L.<br>3         | RCAP2L.<br>2         | RCAP2L.              | RCAP2L.         | 0000 0000b                              |

| T2MOD    | TIMER 2 MODE                        | C9H     | ENLD            | ICEN2           | ICEN1         | ICEN0         | T2CR                 | CMPCR                | -                    | -               | 0000 00XXb                              |

| T2CON    | TIMER 2 CONTROL                     | C8H     | TF2             | -               | -             | -             | -                    | TR2                  | -                    | CMP/RL2         | 0XXX X0X0b                              |

| TA       | TIMED ACCESS PROTECTION             | C7H     | TA.7            | TA.6            | TA.5          | TA.4          | TA.3                 | TA.2                 | TA.1                 | TA.0            | 0000 0000b                              |

| NVMADDRL | NVM LOW BYTE ADDRESS                | C6H     | NVMADDR<br>.7   | NVMADDR.<br>6   | NVMADDR<br>.5 | NVMADDR<br>.4 | NVMADD<br>R.3        | NVMADD<br>R.2        | NVMADD<br>R.1        | NVMADD<br>R.0   | 0000 0000b                              |

| NVMADDRH | NVM HIGH BYTE ADDRESS               | C5H     | -               | -               | -             | -             | -                    | -                    | -                    | NVMADD<br>R.8   | XXXX XXX0b                              |

| PNP      | PWM NEGATIVE POLRARITY              | СЗН     | -               | -               | PNP.5         | PNP.4         | PNP.3                | PNP.2                | PNP.1                | PNP.0           | XX00 0000b                              |

| T3CON    | TIMER 3 CONTOL                      | C2H     | TF3             | EXF3            | T3CNTE        | T3OE          | T3RST                | TR3                  | T3MOD.1              | T3MOD.0         | 0000 0000b                              |

| I2ADDR   | I2C ADDRESS1                        | C1H     | ADDR.7          | ADDR.6          | ADDR.5        | ADDR.4        | ADDR.3               | ADDR.2               | ADDR.1               | GC              | XXXX XXX0b                              |

| I2CON    | I2C CONTROL REGISTER                | C0H     | (C7)<br>-       | (C6)<br>ENSI    | (C5)<br>STA   | (C4)<br>STO   | (C3)<br>SI           | (C2)<br>AA           | (C1)<br>-            | (C0)<br>-       | X00000XXb                               |

| I2TOC    | I2C TIMER-OUT COUNTER<br>REGISTER   | BFH     | -               | -               | -             | -             | -                    | ENTI                 | DIV4                 | TIF             | XXXX X000b                              |

| I2CLK    | I2C CLOCK RATE                      | BEH     | I2CLK.7         | I2CLK.6         | I2CLK.5       | I2CLK.4       | I2CLK.3              | I2CLK.2              | I2CLK.1              | I2CLK.0         | 0000000b                                |

| I2STATUS | I2C STATUS REGISTER                 | BDH     | B7              | B6              | B5            | B4            | B3                   | B2                   | B1                   | B0              | 1111 1000b                              |

| I2DAT    | I2C DATA REGISTER                   | BCH     | I2DAT.7         | I2DAT.6         | I2DAT.5       | I2DAT.4       | I2DAT.3              | I2DAT.2              | I2DAT.1              | I2DAT.0         | XXXX XXXXb                              |

| SADEN    | SLAVE ADDRESS MASK                  | B9H     | SADEN.7         | SADEN.6         | SADEN.5       | SADEN.4       | SADEN.3              | SADEN.2              | SADEN.1              | SADEN.0         | 0000 0000b                              |

| IP0      | INTERRUPT PRIORITY                  | B8H     | (BF)<br>-       | (BE)<br>PADC    | (BD)<br>PBO   | (BC)<br>PS    | (BB)<br>PT1          | (BA)<br>PX1          | (B9)<br>PT0          | (B8)<br>PX0     | X000 0000b                              |

| IP0H     | INTERRUPT HIGH PRIORITY             | B7H     | -               | PADCH           | PBOH          | PSH           | PT1H                 | PX1H                 | PT0H                 | PX0H            | X000 0000b                              |

| P2M2     | PORT 2 OUTPUT MODE 2                | B6H     | P2M2.7          | P2M2.6          | P2M2.5        | P2M2.4        | P2M2.3               | P2M2.2               | P2M2.1               | P2M2.0          | 0000 0000b                              |

| P2M1     | PORT 2 OUTPUT MODE 1                | B5H     | P2M1.7          | P2M1.6          | P2M1.5        | P2M1.4        | P2M1.3               | P2M1.2               | P2M1.1               | P2M1.0          | 0000 0000b                              |

| P1M2     | PORT 1 OUTPUT MODE 2                | B4H     | P1M2.7          | -               | -             | -             | P1M2.3               | P1M2.2               | P1M2.1               | P1M2.0          | 000X 0000b                              |

| P1M1     | PORT 1 OUTPUT MODE 1                | B3H     | P1M1.7          | -               | -             | -             | P1M1.3               | P1M1.2               | P1M1.1               | P1M1.0          | 000X 0000b                              |

| P0M2     | PORT 0 OUTPUT MODE 2                | B2H     | P0M2.7          | P0M2.6          | P0M2.5        | P0M2.4        | P0M2.3               | P0M2.2               | P0M2.1               | P0M2.0          | 0000 0000b                              |

| P0M1     | PORT 0 OUTPUT MODE 1                | B1H     | P0M1.7          | P0M1.6          | P0M1.5        | P0M1.4        | P0M1.3               | P0M1.2               | P0M1.1               | P0M1.0          | 0000 0000b                              |

| P3       | PORT 3                              | B0H     | (B7)<br>P3.7    | (B6)<br>P3.6    | (B5)<br>P3.5  | (B4)<br>P3.4  | (B3)<br>P3.3         | (B2)<br>P3.2         | (B1)<br>P3.1<br>PWM3 | (B0)<br>P3.0    | 1111 1111b <sup>(1)</sup><br>0000 0000b |

| ADCDLY   | ADC DELAY START REGISTER            | AFH     | OPN<br>ADCDLY.7 | OPP<br>ADCDLY.6 | ADCDLY.5      | ADCDLY.4      | PWM7<br>ADCDLY.<br>3 | PWM5<br>ADCDLY.<br>2 | -                    | PWM1<br>ADCDLY. | 0000 0000b                              |

| PDTC0    | PWM DEAD TIME CONTROL 0<br>REGISTER | AEH     | -               | -               | -             | -             | -                    | DTENB4               | DTENB2               | DTENB0          | XXXX X000b                              |

| CMP2     | COMPARATOR 1 CONTROL<br>REGISTER    | ADH     | -               | HYSEN2          | CMPEN2        | CP2           | CN2                  | COE2                 | CO2                  | CMF2            | XX0X 0000b                              |

| CMP1     | COMPARATOR 1 CONTROL<br>REGISTER    | ACH     | -               | HYSEN1          | CMPEN1        | -             | CN1                  | COE1                 | CO1                  | CMF1            | XX0X 0000b                              |

| DTCNT    | PWM DEAD TIME COUNTER<br>REGISTER   | ABH     | DTCNT.7         | DTCNT.6         | DTCNT.5       | DTCNT.4       | DTCNT.3              | DTCNT.2              | DTCNT.1              | DTCNT.0         | 0000 0000b                              |

| SADDR    | SLAVE ADDRESS                       | A9H     | SADDR.7         | SADDR.6         | SADDR.5       | SADDR.4       | SADDR.3              | SADDR.2              | SADDR.1              | SADDR.0         | 0000 0000b                              |

| IE       | INTERRUPT ENABLE                    | A8H     | (AF)<br>EA      | (AE)<br>EADC    | (AD)<br>EBO   | (AC)<br>ES    | (AB)<br>ET1          | (AA)<br>EX1          | (A9)<br>ET0          | (A8)<br>EX0     | 0000 0000b                              |

# nuvoTon

| SYMBOL    | DEFINITION                                            | ADDRESS | MSB                                 |                                      |                                   | BIT ADDRES                          | SS, SYMBOL                          |                                      |                                      | LSB                                | RESET                                   |

|-----------|-------------------------------------------------------|---------|-------------------------------------|--------------------------------------|-----------------------------------|-------------------------------------|-------------------------------------|--------------------------------------|--------------------------------------|------------------------------------|-----------------------------------------|

| CCH2      | INPUT CAPTURE 2 HIGH                                  | A7H     | CCH2.7                              | CCH2.6                               | CCH2.5                            | CCH2.4                              | CCH2.3                              | CCH2.2                               | CCH2.1                               | CCH2.0                             | 0000 0000b                              |

| CCL2      | INPUT CAPTURE 2 LOW                                   | A6H     | CCL2.7                              | CCL2.6                               | CCL2.5                            | CCL2.4                              | CCL2.3                              | CCL2.2                               | CCL2.1                               | CCL2.0                             | 0000 0000b                              |

| P4        | PORT 4                                                | A5H     | -                                   | -                                    | -                                 | -                                   | P4.3                                | P4.2                                 | P4.1<br>CP2PB                        | P4.0<br>CP2NB                      | XXXX 1111b <sup>(1)</sup><br>XXXX 0000b |

| CAPCON1   | CAPTURE CONTROL 1                                     | A4H     | -                                   | ICOSS                                | ENF2                              | ENF1                                | ENF0                                | CPTF2                                | CPTF1                                | CPTF0                              | X000 0000b                              |

| CAPCON0   | CAPTURE CONTROL 0                                     | A3H     | CCT2.1                              | CCT2.0                               | CCT1.1                            | CCT1.0                              | CCT0.1                              | CCT0.0                               | CCLD.1                               | CCLD.0                             | 0000 0000b                              |

| AUXR1     | AUX FUNCTION REGISTER 1                               | A2H     | KBF                                 | BOD                                  | BOI                               | LPBOD                               | SRST                                | ADCEN                                | RCCLK                                | BOS                                | 0X00 0000b                              |

| KBI       | KEYBOARD INTERRUPT                                    | A1H     | KBI.7                               | KBI.6                                | KBI.5                             | KBI.4                               | KBI.3                               | KBI.2                                | KBI.1                                | KBI.0                              | 0000 0000b                              |

| P2        | PORT 2                                                | AOH     | (A7)<br>P2.7<br>T1                  | (A6)<br>P2.6<br>IC2<br>MOSI          | (A5)<br>P2.5<br>IC1<br>MISO       | (A4)<br>P2.4<br>IC0<br>/SS          | (A3)<br>P2.3<br>T3<br>SCLK          | (A2)<br>P2.2<br>PWM4                 | (A1)<br>P2.1<br>PWM2<br>CP1O         | (A0)<br>P2.0<br>PWM0<br>CP2O       | 1111 1111b <sup>(1)</sup><br>0000 0000b |

| P3M2      | PORT 3 OUTPUT MODE 2                                  | 9FH     | P3M2.7                              | P3M2.6                               | P3M2.5                            | P3M2.4                              | P3M2.3                              | P3M2.2                               | P3M2.1                               | P3M2.0                             | 0000 0000b                              |

| P3M1      | PORT 3 OUTPUT MODE 1                                  | 9EH     | P3M1.7                              | P3M1.6                               | P3M1.5                            | P3M1.4                              | P3M1.3                              | P3M1.2                               | P3M1.1                               | P3M1.0                             | 0000 0000b                              |

| ADCRH     | ADC COMPARE REFERENCE<br>HIGH DATA REGISTER           | 9DH     | ADCR.9                              | ADCR.8                               | ADCR.7                            | ADCR.6                              | ADCR.5                              | ADCR.4                               | ADCR.3                               | ADCR.2                             | XXXX XXXXb                              |

| ADCRL     | ADC COMPARE REFERENCE<br>LOW DATA/COMPARE<br>REGISTER | 9CH     | ADCR.1                              | ADCR.0                               | ADCPO                             | ADCPI                               | -                                   | -                                    | T3CSS                                | ENADCP                             | XX10 XX00b                              |

| PIO       | PWM IO REGISTER                                       | 9BH     | PIO.7                               | PIO.6                                | PIO.5                             | PIO.4                               | PIO.3                               | PIO.2                                | PIO.1                                | PIO.0                              | d0000 0000b                             |

| IP2       | INTERRUPT PRIORITY 2                                  | 9AH     | -                                   | PT2                                  | -                                 | -                                   | PSPI                                | -                                    | -                                    | PET3                               | X0XX 0XX0b                              |

| SBUF      | SERIAL BUFFER                                         | 99H     | SBUF.7                              | SBUF.6                               | SBUF.5                            | SBUF.4                              | SBUF.3                              | SBUF.2                               | SBUF.1                               | SBUF.0                             | XXXX XXXXb                              |

| SCON      | SERIAL CONTROL                                        | 98H     | (9F)<br>SM0/FE                      | (9E)<br>SM1                          | (9D)<br>SM2                       | (9C)<br>REN                         | (9B)<br>TB8                         | (9A)<br>RB8                          | (99)<br>TI                           | (98)<br>RI                         | 0000 0000b                              |

| PWM4H     | PWM 4 HIGH BITS REGISTER                              | 97H     | -                                   | -                                    | -                                 | -                                   | PWM4.11                             | PWM4.10                              | PWM4.9                               | PWM4.8                             | XXXX 0000b                              |

| PWM4L     | PWM 4 LOW BITS REGISTER                               | 96H     | PWM4.7                              | PWM4.6                               | PWM4.5                            | PWM4.4                              | PWM4.3                              | PWM4.2                               | PWM4.1                               | PWM4.0                             | 0000 0000b                              |

| RCAP3HT3H | TIMER 3 RELOAD MSB                                    | 93H     | RCAP3.11                            | RCAP3.10                             | RCAP3.9                           | RCAP3.8                             | T3.11                               | T3.10                                | T3.9                                 | T3.8                               | 0000 0000b                              |

| RCAP3L    | TIMER 3 RELOAD LSB                                    | 92H     | RCAP3.7                             | RCAP3.6                              | RCAP3.5                           | RCAP3.4                             | RCAP3.3                             | RCAP3.2                              | RCAP3.1                              | RCAP3.0                            | 0000 0000b                              |

| TL3       | TIMER 3 LSB                                           | 91H     | T3.7                                | T3.6                                 | T3.5                              | T3.4                                | T3.3                                | T3.2                                 | T3.1                                 | T3.0                               | 0000 0000b                              |

| P1        | PORT 1                                                | 90H     | (97)<br>P1.7<br>STADC<br>BKP0       | (96)<br>P1.6<br>/INT0<br>SDA         | (95)<br>P1.5<br>T0<br>SCL<br>BKP1 | (94)<br>P1.4<br>/RST                | (93)<br>P1.3<br>RXD                 | (92)<br>P1.2<br>TXD                  | (91)<br>P1.1<br>XT1                  | (90)<br>P1.0<br>XT2<br>CLKOUT      | 1111 1111b <sup>(1)</sup><br>0000 0000b |

| CKCON     | CLOCK CONTROL                                         | 8EH     | -                                   | -                                    | -                                 | T1M                                 | TOM                                 | -                                    | -                                    | -                                  | XXX0 0XXXb                              |

| TH1       | TIMER HIGH 1                                          | 8DH     | TH1.7                               | TH1.6                                | TH1.5                             | TH1.4                               | TH1.3                               | TH1.2                                | TH1.1                                | TH1.0                              | 0000 0000b                              |

| TH0       | TIMER HIGH 0                                          | 8CH     | TH0.7                               | TH0.6                                | TH0.5                             | TH0.4                               | TH0.3                               | TH0.2                                | TH0.1                                | TH0.0                              | 0000 0000b                              |

| TL1       | TIMER LOW 1                                           | 8BH     | TL1.7                               | TL1.6                                | TL1.5                             | TL1.4                               | TL1.3                               | TL1.2                                | TL1.1                                | TL1.0                              | 0000 0000b                              |

| TL0       | TIMER LOW 0                                           | 8AH     | TL0.7                               | TL0.6                                | TL0.5                             | TL0.4                               | TL0.3                               | TL0.2                                | TL0.1                                | TL0.0                              | 0000 0000b                              |

| TMOD      | TIMER MODE                                            | 89H     | GATE                                | C/T                                  | M1                                | M0                                  | GATE                                | C/T                                  | M1                                   | M0                                 | 0000 0000b                              |

| TCON      | TIMER CONTROL                                         | 88H     | (8F)<br>TF1                         | (8E)<br>TR1                          | (8D)<br>TF0                       | (8C)<br>TR0                         | (8B)<br>IE1                         | (8A)<br>IT1                          | (89)<br>IE0                          | (88)<br>ITO                        | 0000 0000b                              |

| PCON      | POWER CONTROL                                         | 87H     | SMOD                                | SMOD0                                | BOF                               | POR                                 | GF1                                 | GF0                                  | PD                                   | IDL                                | 00XX 0000b                              |

| DIV       | DIVIDER                                               | 86H     | CCDIV.1                             | CCDIV.0                              | PWMDIV.1                          | PWMDIV.0                            | T3DIV.1                             | T3DIV.0                              | T0DIV.1                              | T0DIV.0                            | 0000 0000b                              |

| DPH       | DATA POINTER HIGH                                     | 83H     | DPH.7                               | DPH.6                                | DPH.5                             | DPH.4                               | DPH.3                               | DPH.2                                | DPH.1                                | DPH.0                              | 0000 0000b                              |

| DPL       | DATA POINTER LOW                                      | 82H     | DPL.7                               | DPL.6                                | DPL.5                             | DPL.4                               | DPL.3                               | DPL.2                                | DPL.1                                | DPL.0                              | 0000 0000b                              |

| SP        | STACK POINTER                                         | 81H     | SP.7                                | SP.6                                 | SP.5                              | SP.4                                | SP.3                                | SP.2                                 | SP.1                                 | SP.0                               | 0000 0111b                              |

| P0        | PORT 0                                                | 80H     | (87)<br>P0.7<br>ADC7<br>PWM6<br>KB7 | (86)<br>P0.6<br>ADC6<br>/INT1<br>KB6 | (85)<br>P0.5<br>ADC5<br>KB5       | (84)<br>P0.4<br>ADC4<br>CP1N<br>KB4 | (83)<br>P0.3<br>ADC3<br>CP1P<br>KB3 | (82)<br>P0.2<br>ADC2<br>CP2NA<br>KB2 | (81)<br>P0.1<br>ADC1<br>CP2PA<br>KB1 | (80)<br>P0.0<br>ADC0<br>OPO<br>KB0 | 1111 1111b <sup>(1)</sup><br>0000 0000b |

Note: 1. If config0.PRHI=1, the initial value is FFh at reset. If config0.PRHI=0, the initial value is 00h at reset

#### 7.2 **SFR Detail Bit Descriptions**

#### PORT 0

| PORT | PORT 0 Initial=1111_111k |      |      |      |      |      |      |             |

|------|--------------------------|------|------|------|------|------|------|-------------|

| Bit: | 7                        | 6    | 5    | 4    | 3    | 2    | 1    | 0           |

|      | P0.7                     | P0.6 | P0.5 | P0.4 | P0.3 | P0.2 | P0.1 | P0.0        |

|      | Mnemonic: P0 Address: 80 |      |      |      |      |      |      | ddress: 80h |

Mnemonic: P0

P0.7-0: General purpose Input/Output port. Most instructions will read the port pins in case of a port read access, however in case of read-modify-write instructions, the port latch is read. If config0.PRHI=1, the initial value is FFh at reset. If config0.PRHI=0, the initial value is 00h at reset. These alternate functions are described below.

| BIT | NAME | FUNCTION                                                                  |

|-----|------|---------------------------------------------------------------------------|

| 7   | P0.7 | ADC7 or PWM6 or KB7 pin or I/O pin by alternative.                        |

| 6   | P0.6 | ADC6 or /INT1 or KB6 or I/O pin by alternative.                           |

| 5   | P0.5 | ADC5 or KB5 or Clock (ICP function) pin or I/O pin by alternative.        |

| 4   | P0.4 | ADC4 or CP1N or KB4 or Data (ICP function) pin or I/O pin by alternative. |

| 3   | P0.3 | ADC3 or CP1P or KB3 pin or I/O pin by alternative.                        |

| 2   | P0.2 | ADC2 or CP2NA or KB2 pin or I/O pin by alternative.                       |

| 1   | P0.1 | ADC1 or CP2PA or KB1 pin or I/O pin by alternative.                       |

| 0   | P0.0 | ADC0 or KB0 pin or I/O pin by alternative.                                |

Note: The initial value of the port is set by CONFIG0.PRHI bit. The default setting for CONFIG0.PRHI =1 which the alternative function output is turned on upon reset. If CONFIG0.PRHI is set to 0, the user has to write a 1 to port SFR to turn on the alternative function output.

| STAC | K POINTER                 |       |                                                                                                                                       |       |          |       | Initial= | 0000 0111b  |  |  |

|------|---------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-------|----------|-------------|--|--|

| Bit: | 7                         | 6     | 5                                                                                                                                     | 4     | 3        | 2     | 1        | 0           |  |  |

|      | SP.7                      | SP.6  | SP.5                                                                                                                                  | SP.4  | SP.3     | SP.2  | SP.1     | SP.0        |  |  |

|      | Mnemonic: SP Address: 81h |       |                                                                                                                                       |       |          |       |          |             |  |  |

| BIT  | NAME                      |       | FUNCTION                                                                                                                              |       |          |       |          |             |  |  |

| 7-0  | SP.[7:0]                  |       | The Stack Pointer stores the Scratch-pad RAM address where the stack begins. In other words it always points to the top of the stack. |       |          |       |          |             |  |  |

| DATA | POINTER L                 | .ow   |                                                                                                                                       |       |          |       | Initial= | 0000 0000b  |  |  |