## 8051 RISC Microcontroller

# High-Speed, 8051-Compatible, With SRAM and Extended Functions

## 1. Description

The TSCR8051 8-bit microcontroller is software compatible with the millions of devices that have been produced since Intel<sup>®</sup> introduced the 8051 line in 1980. It executes all ASM51 instructions and uses the same instruction set as the 8031. Its Reduced Instruction Set Computer (RISC) core executes many of its instructions in a single clock cycle, providing a significant speed advantage over traditional 8051 devices that execute an instruction every twelve clock cycles. With clock speeds of up to 200 MHz, this device is an 8051 performance leader.

The TSCR8051 features 128KBKBytes of partitionable Data and Program memory and extended 32-bit capabilities including an IEEE 754-compliant floating-point coprocessor with comparator, a multiply/divide unit, a population counter, and a leading-zero counter.

## 2. Features

- Industry standard 8051 / 8031 software compatible

- RISC architecture with up to x12 speed advantage / MHz over traditional 8051 family devices

- Four speed grades: 100, 150, 180, and 200 MHz

- 128KB of additional high-speed SRAM memory

- IEEE 754-compliant floating point coprocessor for full arithmetic capabilities – up to 100 MFlops

- Extended 32-bit computing functions including population counter, leading zero counter, and floating-point comparator

- Dual data pointers for fast data block moves

- Full 8051-compatible architecture including:

- o Four 8-bit bi-directional ports

- o 256 Bytes of "Scratch Pad" memory

- o Three 16-bit timer/counters

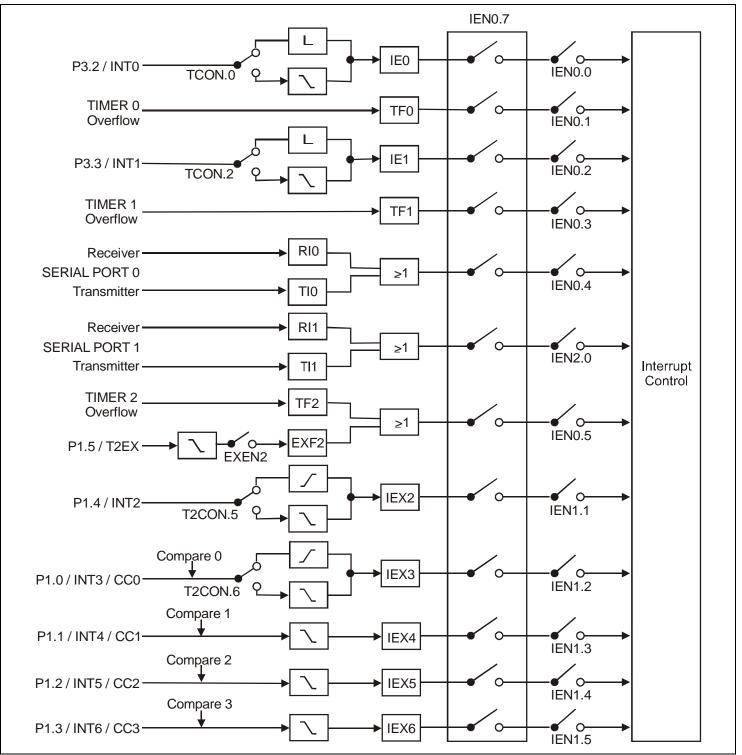

- Interrupt controller with 12 interrupt sources and 4 priority levels

- o 15-bit programmable watchdog timer

- Core 8-bit arithmetic logic unit and 16-bit multiplication division unit

- o Two full-duplex serial ports

- Four capture/compare units to generate pulse width modulated signals

- Special Function Register (SFR) interface, serving up to 50 SFR devices

| 3. Part Numbering<br>Options | Marking |

|------------------------------|---------|

| Packages:                    |         |

| 44 PLCC                      | XXXXX   |

| 68 PLCC                      | XXXXX   |

| 100 TQFP                     | XXXXX   |

| Operating Temperature:       |         |

| Standard, 0° to 70° C        | S       |

| Extended (planned)           | E       |

| Speed Grade:                 |         |

| 66 MHz                       | -06     |

| 100 MHz                      | -10     |

| 150 MHz                      | -15     |

| 180 MHz                      | -18     |

| 200 MHz                      | -20     |

Part number example: **TSCxxxxPS-06**

#### 4. Operating Voltages

$\begin{array}{l} V_{\text{DDQ,}} \, V_{\text{DDQF}} = 3.3 \pm .3 \ \text{VDC} \\ V_{\text{DD}} = 1.8 \pm .2 \ \text{VDC} \end{array}$

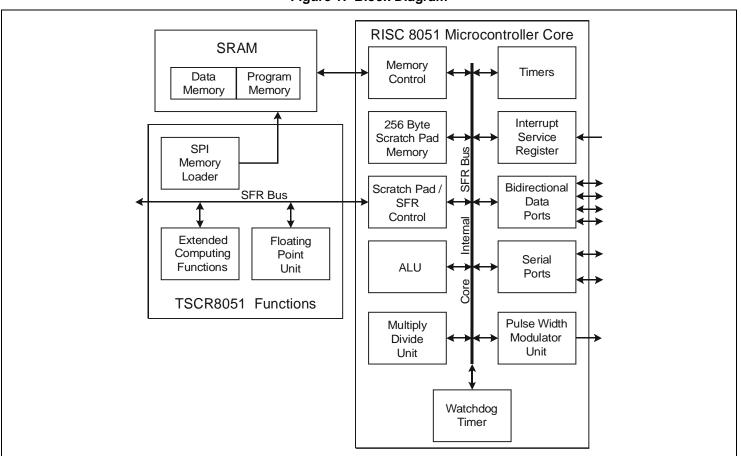

#### Figure 1: Block Diagram

## 5. Table of Contents

| 1. | Description                   | 1  |

|----|-------------------------------|----|

| 2. | Features                      | 1  |

| 3. | Part Numbering                | 1  |

| 4. | Operating Voltages            | 1  |

| 5. | Table of Contents             | 2  |

| 6. | Table of Figures              | 2  |

| 7. | Table of Tables               | 3  |

| 8. | Block Diagram                 | 4  |

| 9. | Pin-Out                       | 4  |

| 1( | 0. Special Function Registers | 9  |

| 1  | 1. Memory                     | 32 |

| 12 | 2. Instruction Set            | 34 |

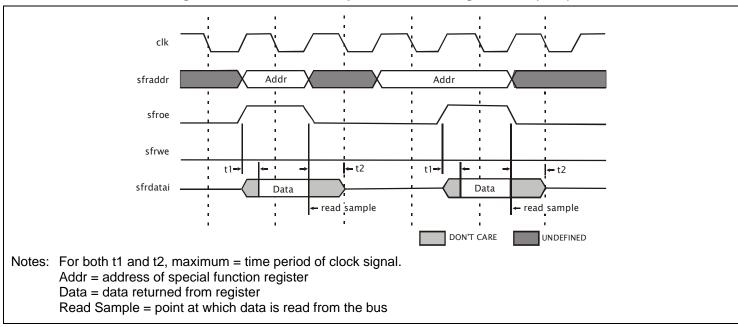

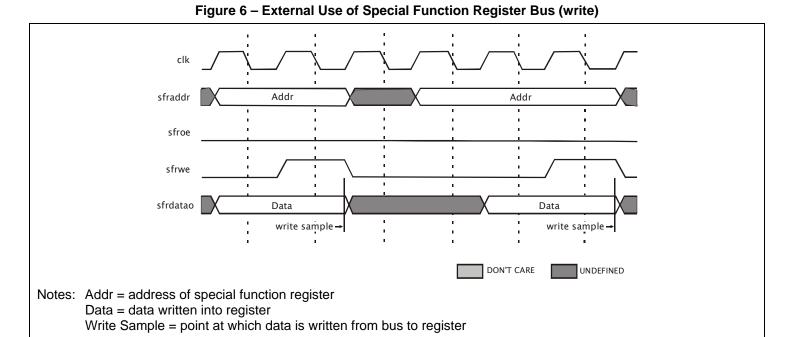

| 1: | 3. External SFR Timing        | 42 |

| 14 | 4. Hardware Overview          | 43 |

|    |                               |    |

| 15. | Core Engine                          | 43 |

|-----|--------------------------------------|----|

| 16. | Multiplication / Division Unit (MDU) | 43 |

| 17. | Timers                               | 45 |

| 18. | Serial Ports                         | 51 |

| 19. | Interrupts                           | 54 |

| 20. | Floating Point Unit (FPU)            | 57 |

| 21. | Extended Computing Functions         | 57 |

| 22. | SPI Memory Loader                    | 58 |

| 23. | Reset Control                        | 58 |

| 24. | Power Management                     | 58 |

| 25. | Device Specifications                | 59 |

| 26. | Package Dimensions                   | 59 |

| 27. | Document History                     | 60 |

|     |                                      |    |

## 6. Table of Figures

| Figure 1: Block Diagram2     |  |

|------------------------------|--|

| Figure 2: 44 PPLC, Top View4 |  |

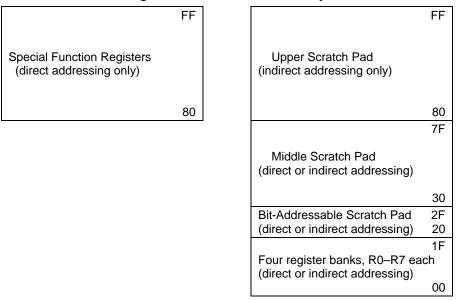

| Figure 3 – Scratch Pad Memory                                             | 32 |

|---------------------------------------------------------------------------|----|

| Figure 4 – SRAM Memory Layout                                             |    |

| Figure 5 – External Use of Special Function Register Bus (read)           |    |

| Figure 6 – External Use of Special Function Register Bus (write)          | 42 |

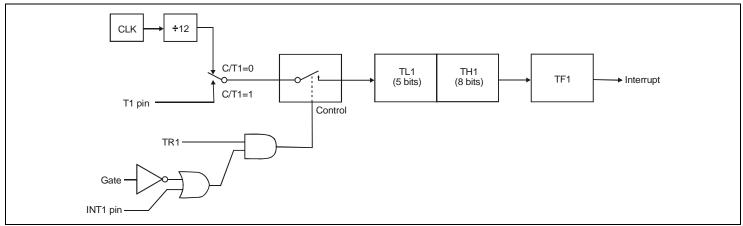

| Figure 7 – Timer/Counter 1 in Mode 0                                      |    |

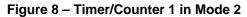

| Figure 8 – Timer/Counter 1 in Mode 2                                      | 47 |

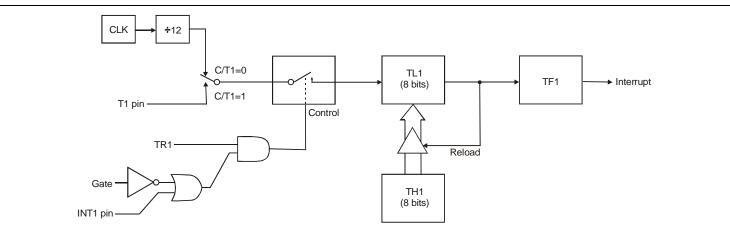

| Figure 9 – Timer/Counter 0 in Mode 3                                      | 47 |

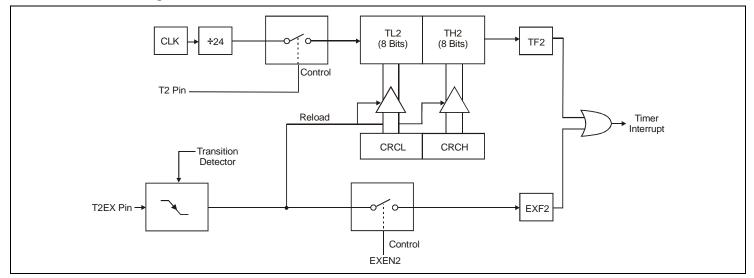

| Figure 10 – Timer 2 as Gated Timer: Prescaler Select = 1, Reload Mode = 1 | 49 |

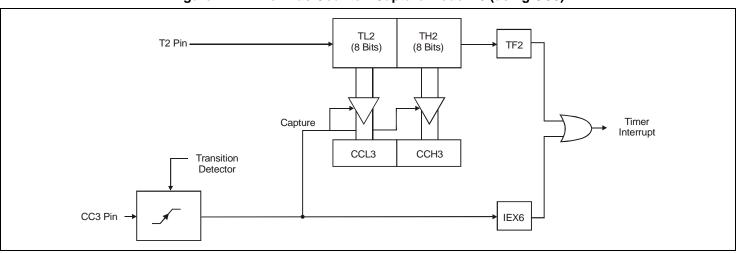

| Figure 11 – Timer 2 as Counter: Capture Mode = 0 (using CC3)              | 50 |

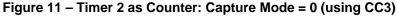

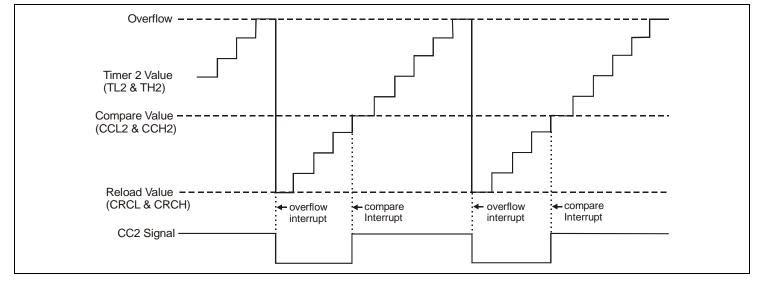

| Figure 12 – Timer 2: Reload Mode = 0, Compare Mode = 0 (using CC2)        | 50 |

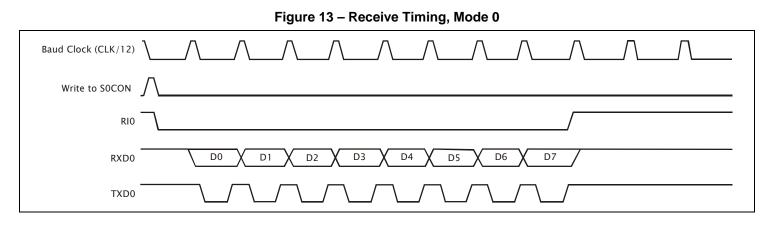

| Figure 13 – Receive Timing, Mode 0                                        | 52 |

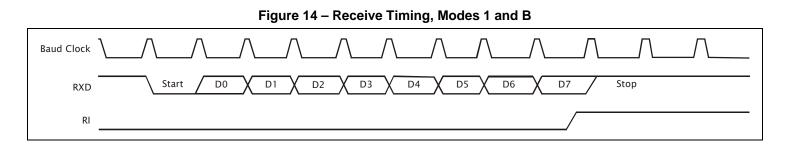

| Figure 14 – Receive Timing, Modes 1 and B                                 | 53 |

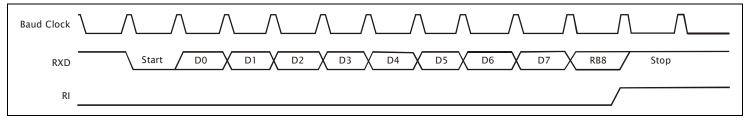

| Figure 15 – Receive Timing, Modes 2, 3, and A                             |    |

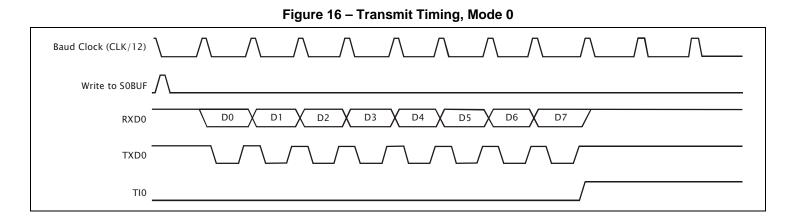

| Figure 16 – Transmit Timing, Mode 0                                       | 53 |

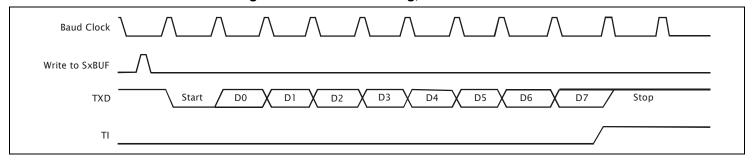

| Figure 17 – Transmit Timing, Modes 1 and B                                | 53 |

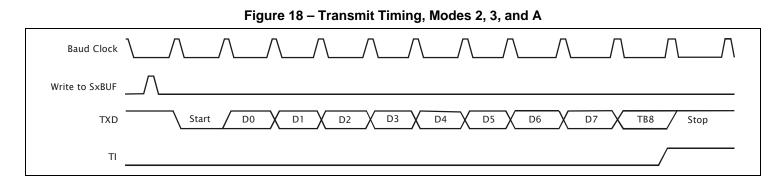

| Figure 18 – Transmit Timing, Modes 2, 3, and A                            |    |

| Figure 19 – Interrupt Processing                                          | 56 |

|                                                                           |    |

## 7. Table of Tables

| 5  |

|----|

| 9  |

| 34 |

| 34 |

| 85 |

| 86 |

| 87 |

| 88 |

| 88 |

| 39 |

| 4  |

| 4  |

| 5  |

| 54 |

| 55 |

| 55 |

| 57 |

| 57 |

| 58 |

|    |

## 8. Block Diagram

- 9. Pin-Out

- 9.1. 44 PLCC

## Figure 2: 44 PPLC, Top View

|   |    | 6  | 5  | 4  | 3     | 2    | 1   | 44   | 43    | 42 | 41 | 40  |    |  |

|---|----|----|----|----|-------|------|-----|------|-------|----|----|-----|----|--|

|   | /  |    | 0  | •  |       | -    | •   |      |       |    |    |     |    |  |

| - | 7  |    |    |    |       |      | •   |      |       |    |    |     | 39 |  |

| - | 8  |    |    |    |       |      |     |      |       |    |    |     | 38 |  |

|   | 9  |    |    |    |       |      |     |      |       |    |    |     | 37 |  |

|   | 10 |    |    |    |       |      |     |      |       |    |    |     | 36 |  |

|   | 11 |    |    |    |       |      |     |      |       |    |    |     | 35 |  |

|   | 12 |    |    | Pl | astic | lead | ded | chip | carri | er |    |     | 34 |  |

|   | 13 |    |    |    |       |      |     |      |       |    |    |     | 33 |  |

| - | 14 | 32 |    |    |       |      |     |      |       |    |    |     |    |  |

| - | 15 |    |    |    |       |      |     |      |       |    |    |     | 31 |  |

| - | 16 |    |    |    |       |      |     |      |       |    |    |     | 30 |  |

| - | 17 |    |    |    |       |      |     |      |       |    |    |     | 29 |  |

| _ |    | 10 | 10 | 00 | 01    | 00   | 0.0 | 0.4  | 05    | 0( | 07 | 0.0 |    |  |

|   |    | 18 | 19 | 20 | 21    | 22   | 23  | 24   | 25    | 26 | 27 | 28  |    |  |

|   |    |    |    |    |       |      |     |      |       |    |    |     |    |  |

|     | Table 1: 44 PLCC Pinout |  |     |            |  |     |          |  |     |          |  |

|-----|-------------------------|--|-----|------------|--|-----|----------|--|-----|----------|--|

| No. | ΝΑΜΕ                    |  | No. | NAME       |  | No. | NAME     |  | No. | ΝΑΜΕ     |  |

| 1   | Vdd Core                |  | 12  | SD_IN      |  | 23  | SD/CLK   |  | 34  | Vss      |  |

| 2   | P1.0                    |  | 13  | P3.1/TxD   |  | 24  | P2.0/A8  |  | 35  | #EA      |  |

| 3   | P1.1                    |  | 14  | P3.2/#INT0 |  | 25  | P2.1/A9  |  | 36  | P0.7/AD7 |  |

| 4   | P1.2                    |  | 15  | P3.3/#INT1 |  | 26  | P2.2/A10 |  | 37  | P0.6/AD6 |  |

| 5   | P1.3                    |  | 16  | P3.4/T0    |  | 27  | P2.3/A11 |  | 38  | P0.5/AD5 |  |

| 6   | P1.4                    |  | 17  | P3.5/T1    |  | 28  | P2.4/A12 |  | 39  | P0.4.AD4 |  |

| 7   | P1.5                    |  | 18  | P3.6/#WR   |  | 29  | P2.5/A13 |  | 40  | P0.3/AD3 |  |

| 8   | P1.6/SCL                |  | 19  | P3.7/#RD   |  | 30  | P2.6/A14 |  | 41  | P0.2/AD2 |  |

| 9   | P1.7/SDA                |  | 20  | CLK1       |  | 31  | P2.7/A15 |  | 42  | P0.1/AD1 |  |

| 10  | RST                     |  | 21  | CLK0       |  | 32  | #PSEN    |  | 43  | P0.0/AD0 |  |

| 11  | P3.0/RxD                |  | 22  | Vss        |  | 33  | ALE      |  | 44  | Vdd      |  |

9.2.

**68 PLCC**

Not available at time of revision.

## 9.3. 100 TQFP

Not available at time of revision.

## 9.4. Pin Descriptions

|                |      |                                                                                                                                                                                                                                                                                                                                                                                                                       |                | PORT PINS       |                                                                                    |  |  |  |  |  |  |

|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                | Thes | e are 8-bit bi-directio                                                                                                                                                                                                                                                                                                                                                                                               | nal I/O ports. | Each consists o | of a latch, output driver, and input buffer.                                       |  |  |  |  |  |  |

| Symbol         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                           |                |                 |                                                                                    |  |  |  |  |  |  |

| PORT0<br>[7:0] | I/O  | An open-drain port. Pins set to 1 will float and can be used as high impedance inputs. PORT0 pins must be polarized to $V_{DDQ}$ or $V_{SSQ}$ in order to prevent any parasitic current consumption.                                                                                                                                                                                                                  |                |                 |                                                                                    |  |  |  |  |  |  |

| PORT1<br>[7:0] | I/O  | A port with internal pull-ups. Pins set to 1 are pulled high and can be used as inputs. Input pins that are externally pulled low will source current because of the internal pull-ups.<br>In addition to general purpose I/O, PORT1 has alternate functions that may be accessed through the Special Function Registers. Data can be read or written through any pin that is not being used for alternate functions. |                |                 |                                                                                    |  |  |  |  |  |  |

|                |      | Pin                                                                                                                                                                                                                                                                                                                                                                                                                   | Name           | Туре            | Description                                                                        |  |  |  |  |  |  |

|                |      | PORT1[0]                                                                                                                                                                                                                                                                                                                                                                                                              | INT3           | Input           | External Interrupt 3                                                               |  |  |  |  |  |  |

|                |      |                                                                                                                                                                                                                                                                                                                                                                                                                       | CC0            | Input           | Capture/Compare 0                                                                  |  |  |  |  |  |  |

|                |      |                                                                                                                                                                                                                                                                                                                                                                                                                       | RXD1           | Input           | Serial Port 1 Receive Pin (see page 51)                                            |  |  |  |  |  |  |

|                |      | PORT1[1]                                                                                                                                                                                                                                                                                                                                                                                                              | INT4           | Input           | External Interrupt 4                                                               |  |  |  |  |  |  |

|                |      |                                                                                                                                                                                                                                                                                                                                                                                                                       | CC1            | Input           | Capture/Compare 1                                                                  |  |  |  |  |  |  |

|                |      |                                                                                                                                                                                                                                                                                                                                                                                                                       | TXD1           | Output          | Serial Port 1 Transmit Pin (see page 51)                                           |  |  |  |  |  |  |

|                |      | PORT1[2]                                                                                                                                                                                                                                                                                                                                                                                                              | INT5           | Input           | External Interrupt 5                                                               |  |  |  |  |  |  |

|                |      |                                                                                                                                                                                                                                                                                                                                                                                                                       | CC2            | Input           | Capture/Compare 2                                                                  |  |  |  |  |  |  |

|                |      | PORT1[3]                                                                                                                                                                                                                                                                                                                                                                                                              | INT6           | Input           | External Interrupt 6                                                               |  |  |  |  |  |  |

|                |      |                                                                                                                                                                                                                                                                                                                                                                                                                       | CC3            | Input           | Capture/Compare 3                                                                  |  |  |  |  |  |  |

|                |      | PORT1[4]                                                                                                                                                                                                                                                                                                                                                                                                              | INT2           | Input           | External Interrupt 2                                                               |  |  |  |  |  |  |

|                |      | PORT1[5]                                                                                                                                                                                                                                                                                                                                                                                                              | T2EX           | Input           | Timer 2 External Reload Trigger                                                    |  |  |  |  |  |  |

|                |      | PORT1[6]                                                                                                                                                                                                                                                                                                                                                                                                              |                |                 | No Alternate Function                                                              |  |  |  |  |  |  |

|                |      | PORT1[7]                                                                                                                                                                                                                                                                                                                                                                                                              | T2             | Input           | Timer 2 Counter Trigger or Timer Gate                                              |  |  |  |  |  |  |

| PORT2<br>[7:0] | I/O  |                                                                                                                                                                                                                                                                                                                                                                                                                       |                |                 | lled high and can be used as inputs. Input pins that use of the internal pull-ups. |  |  |  |  |  |  |

| PORT3<br>[7:0] | I/O  | A port with internal pull-ups. Pins set to 1 are pulled high and can be used as inputs. Input pins that are externally pulled low will source current because of the internal pull-ups.<br>In addition to general purpose I/O, PORT3 has alternate functions that may be accessed through the Special Function Registers. Data can be read or written through any pin that is not being used for alternate functions. |                |                 |                                                                                    |  |  |  |  |  |  |

|                |      | Pin                                                                                                                                                                                                                                                                                                                                                                                                                   | Name           | Туре            | Description                                                                        |  |  |  |  |  |  |

|                |      | PORT3[0]                                                                                                                                                                                                                                                                                                                                                                                                              | RXD0           | Input           | Serial Port 0 Receive Pin (see page 51)                                            |  |  |  |  |  |  |

|                |      | PORT3[1]                                                                                                                                                                                                                                                                                                                                                                                                              | TXD0           | Output          | Serial Port 0 Transmit Pin (see page 51)                                           |  |  |  |  |  |  |

|                |      | PORT3[2]                                                                                                                                                                                                                                                                                                                                                                                                              | INT0           | Input           | External Interrupt 0                                                               |  |  |  |  |  |  |

|                |      | PORT3[3]                                                                                                                                                                                                                                                                                                                                                                                                              | INT1           | Input           | External Interrupt 1                                                               |  |  |  |  |  |  |

|                |      | PORT3[4]                                                                                                                                                                                                                                                                                                                                                                                                              | Т0             | Input           | Timer 0 Counter Trigger                                                            |  |  |  |  |  |  |

|                |      | PORT3[5]                                                                                                                                                                                                                                                                                                                                                                                                              | T1             | Input           | Timer 1 Counter Trigger                                                            |  |  |  |  |  |  |

|                |      | PORT3[6]                                                                                                                                                                                                                                                                                                                                                                                                              |                |                 | No Alternate Function                                                              |  |  |  |  |  |  |

|                |      | PORT3[7]                                                                                                                                                                                                                                                                                                                                                                                                              |                |                 | No Alternate Function                                                              |  |  |  |  |  |  |

## Pin Descriptions (continued)

|                 | CLOCK AND RESET PINS |                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|-----------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol          | Туре                 | Description                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

| CLK_0,<br>CLK_1 | Input                | <b>Clock Differential Inputs</b> : These signals (combined) form the internal system clock. They are designed to work with a differential clock oscillator and will not work with a crystal. These signals are ignored if CLK_OVR is asserted.           |  |  |  |  |  |  |  |

| LCLK            | Input                | <b>Program Memory Loading Clock</b> : Drives program memory loading circuitry. After program memory is loaded, this signal is ignored unless CLK_OVR is asserted. This pin is designed to work with a clock oscillator and will not work with a crystal. |  |  |  |  |  |  |  |

| CLK_OUT         | Output               | System Clock Output: Provides access to the internal clock for external SFR circuitry.                                                                                                                                                                   |  |  |  |  |  |  |  |

| RESET           | Input                | Global Reset: A high level for 2 clock cycles (if oscillator is running) resets the hardware.                                                                                                                                                            |  |  |  |  |  |  |  |

| CLK_OVR         | Input                | Clock Override: When asserted, LCLK is used in place of CLK as the system clock.                                                                                                                                                                         |  |  |  |  |  |  |  |

|        | SERIAL PERIPHERAL INTERFACE (SPI) PINS |                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

|--------|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Symbol | Туре                                   | Description                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| SD_IN  | Input                                  | Serial Data Input for SPI: program memory input. Immediately upon power-up or after reset, program memory is loaded from an SPI-compatible device.                                      |  |  |  |  |  |  |  |  |

| SD_OUT | Output                                 | Serial Data Output for SPI                                                                                                                                                              |  |  |  |  |  |  |  |  |

| SD_CLK | Output                                 | <b>Serial Data Clock</b> : During program memory loading, SD_CLK is equivalent to either LCLK or the system clock, depending on the status of the LCLK_EN input (see Clock Pins above). |  |  |  |  |  |  |  |  |

| SD_CS_ | Output                                 | Serial Data Chip Select (active low) for SPI                                                                                                                                            |  |  |  |  |  |  |  |  |

| SD_BSY | Output                                 | Serial Data Busy: Asserted during SPI program memory loading.                                                                                                                           |  |  |  |  |  |  |  |  |

| POWER AND GROUND PINS |        |                                                           |  |  |  |  |  |  |

|-----------------------|--------|-----------------------------------------------------------|--|--|--|--|--|--|

| Symbol                | Туре   | Description                                               |  |  |  |  |  |  |

| Vdd                   | Power  | 1.8 V Power Supply                                        |  |  |  |  |  |  |

| Vddq                  | Power  | 3.3 V Power Supply                                        |  |  |  |  |  |  |

| VDDQF                 | Power  | 3.3 V Filtered Power Supply for differential clock buffer |  |  |  |  |  |  |

| VSS, VSSQ, VSSQF      | Ground | Ground for VDD, VDDQ, VDDQF                               |  |  |  |  |  |  |

|        | MISCELLANEOUS PINS |                                                                                                                                                                     |  |  |  |  |  |

|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol | Туре               | Description                                                                                                                                                         |  |  |  |  |  |

| PMODE  | Input              | <b>Memory Page Mode</b> affects the meaning of registers PPG, DRPG, and DWPG, and the mapping of logical memory addresses. See section 11.2 on page 32 for details. |  |  |  |  |  |

| SWD    | Input              | Start Watchdog Timer: If held high during reset, the watchdog timer starts immediately after the reset.                                                             |  |  |  |  |  |

|                         | DEBUG PINS |                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Symbol Type Description |            |                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| DC2, DC1, DC0           | Input      | <b>Debug Control</b> : These signals select which internal signals are available on the DBG bus.<br>They control the debug multiplexer, which chooses among various signals that are accessed<br>during factory testing. During normal operation DC[2:0] should be tied to ground. |  |  |  |  |  |  |

| DBG [7:0]               | Output     | <b>Debug Port</b> : This bus is driven by the debug multiplexer, which chooses among various signals based on the state of the debug control (DC[2:0]) signals. During normal operation these pins will be driven to ground and should not be connected to external circuitry.     |  |  |  |  |  |  |

## Pin Descriptions (continued)

| SPECIAL FUNCTION REGISTER (SFR) PINS                                                            |                                                                                                                                                                                    |                                                                                                                                                                               |  |  |  |  |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol                                                                                          | Туре                                                                                                                                                                               | Description                                                                                                                                                                   |  |  |  |  |

| SFR_I [7:0]                                                                                     | R_I [7:0] Input <b>SFR Input Bus</b> : Allows external SFR circuitry to transmit data to the 8051 core external SFR circuitry is not used, these signals should be tied to ground. |                                                                                                                                                                               |  |  |  |  |

| SFR_O [7:0] Output SFR Output Bus: Allows the 8051 core to send data to external SFR circuitry. |                                                                                                                                                                                    |                                                                                                                                                                               |  |  |  |  |

| SFR_A [6:0]                                                                                     | Output                                                                                                                                                                             | SFR Address Bus: The 8051 core selects external SFR circuitry via these pins.                                                                                                 |  |  |  |  |

| SFR_WE                                                                                          | Output                                                                                                                                                                             | SFR Write Enable: Asserted when the 8051 core is writing to external SFR circuitry.                                                                                           |  |  |  |  |

| SFR_OE                                                                                          | Output                                                                                                                                                                             | SFR Read Enable: Asserted while the core is reading from external SFR circuitry.                                                                                              |  |  |  |  |

| SFR_DE                                                                                          | Input                                                                                                                                                                              | <b>SFR Data Enable</b> : Asserted by external circuitry when writing on the SFR_I bus. If no external SFR circuitry is used, SFR_DE should be tied to ground.                 |  |  |  |  |

| SFR_BE                                                                                          | Input                                                                                                                                                                              | <b>SFR Bus Enable</b> : Asserted by external SFR circuitry to enable communication from the 8051 core. If no external SFR circuitry is used, SFR_BE should be tied to ground. |  |  |  |  |

#### **10.** Special Function Registers

The TSCR8051 has 128 special function registers. Of these, 78 are predefined as shown in the table below. The remaining 50 undefined locations may be implemented via the external SFR bus. Read accesses to undefined locations will return unidentified data (high Z state).

|           | 0/8   | 1/9   | 2/A    | 3/B    | 4/C   | 5/D    | 6/E    | 7/F   |    |

|-----------|-------|-------|--------|--------|-------|--------|--------|-------|----|

| F8        |       |       |        |        |       |        |        |       | FF |

| F0        | В     |       |        |        |       |        |        |       | F7 |

| E8        |       | MD0   | MD1    | MD2    | MD3   | MD4    | MD5    | ARCON | EF |

| E0        | ACC   | PPG   | DRPG   | DWPG   |       |        |        |       | E7 |

| D8        | WDCON |       |        |        |       |        |        |       | DF |

| D0        | PSW   |       |        |        |       |        |        |       | D7 |

| C8        | T2CON |       | CRCL   | CRCH   | TL2   | TH2    |        |       | CF |

| C0        | IRCON | CCEN  | CCL1   | CCH1   | CCL2  | CCH2   | CCL3   | CCH3  | C7 |

| B8        | IEN1  | IP1   | SORELH | S1RELH |       |        |        |       | BF |

| B0        | P3    |       |        | FPUS   | FPUR3 | FPUR2  | FPUR1  | FPUR0 | B7 |

| <b>A8</b> | IEN0  | IP0   | SORELL | FPCS   | OPB3  | OPB2   | OPB1   | OPB0  | AF |

| A0        | P2    |       |        | FPUCON | OPA3  | OPA2   | OPA1   | OPA0  | A7 |

| 98        | S0CON | SOBUF | IEN2   | S1CON  | S1BUF | S1RELL | PCCON  | POPC  | 9F |

| 90        | P1    |       | DPS    |        |       |        | LZCON  | LZC   | 97 |

| 88        | TCON  | TMOD  | TL0    | TL1    | TH0   | TH1    | CKCON  |       | 8F |

| 80        | P0    | SP    | DPL    | DPH    | DPL1  | DPH1   | WDTREL | PCON  | 87 |

#### Table 2: Special Function Register Mapping

## **Special Function Register Descriptions**

The following tables describe the predefined special function registers in the order of their addresses.

| P0: PORT0       |             |          |                                                                                                                                                                                     |          |          |          |          |  |  |  |  |

|-----------------|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----------|----------|--|--|--|--|

| Address         | Reset Value |          | Description                                                                                                                                                                         |          |          |          |          |  |  |  |  |

| 80h             | FFh         |          | Corresponds to the PORT0[7:0] pins. Writing a '1' to any bit allows the corresponding pin to float; writing a '0' holds the pin low ( $V_{SSQ}$ ). See PORT0 description on page 4. |          |          |          |          |  |  |  |  |

|                 | Bit Map     |          |                                                                                                                                                                                     |          |          |          |          |  |  |  |  |

| 7 6 5 4 3 2 1 0 |             |          |                                                                                                                                                                                     |          |          | 0        |          |  |  |  |  |

| PORT0[7]        | PORT0[6]    | PORT0[5] | PORT0[4]                                                                                                                                                                            | PORT0[3] | PORT0[2] | PORT0[1] | PORT0[0] |  |  |  |  |

|                 |             |          |                                                                                                                                                                                     |          |          |          |          |  |  |  |  |

| SP: STACK | SP: STACK POINTER               |                                                                                                                             |  |  |  |  |  |  |  |

|-----------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Address   | Address Reset Value Description |                                                                                                                             |  |  |  |  |  |  |  |

| 81h       | 07h                             | Contains the program stack location. It is incremented before PUSH and CALL instructions; the stack begins at location 08h. |  |  |  |  |  |  |  |

| DPL: DATA POINTER (LOW)         |     |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|---------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Address Reset Value Description |     |                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| 82h                             | 00h | Lower byte of the first data pointer; can be accessed separately (MOV DPL,#data8) or in combination with DPH (MOV DPTR,#data16). Only used when DPS.0 = 0. Generally used to access external code (MOVC A,@A+DPTR) or data space (MOV A,@DPTR). |  |  |  |  |  |  |

| DPH: DAT | DPH: DATA POINTER (HIGH) |                                                                                                                                                  |  |  |  |  |  |  |

|----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Address  | Reset Value              | Description                                                                                                                                      |  |  |  |  |  |  |

| 83h      | 00h                      | Upper byte of the first data pointer; can be accessed separately (MOV DPH,#data8) or in combination with DPL (MOV DPTR,#data16). See DPL, above. |  |  |  |  |  |  |

| DPL1: DATA POINTER (LOW) |             |                                                                                             |  |  |  |  |  |  |  |

|--------------------------|-------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Address                  | Reset Value | Reset Value Description                                                                     |  |  |  |  |  |  |  |

| 84h                      | 00h         | Lower byte of the second data pointer; used in place of DPL when DPS.0 =1 (see DPL, above). |  |  |  |  |  |  |  |

| DPH1: DA | DPH1: DATA POINTER (HIGH) |                                                                                            |  |  |  |  |  |  |

|----------|---------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Address  | Reset Value               | Description                                                                                |  |  |  |  |  |  |

| 85h      | 00h                       | Upper byte of the second data pointer; used in place of DPH when DPS.0=1 (see DPH, above). |  |  |  |  |  |  |

| WDTREL: WATCHDOG TIMER RELOAD |             |                                                               |                                                                                                                                                                                                                                                                       |         |       |  |  |  |  |

|-------------------------------|-------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|--|--|--|--|

| Address                       | Reset Value |                                                               |                                                                                                                                                                                                                                                                       | Descrip | otion |  |  |  |  |

| 86h                           | 00h         | of bits WDT (IEN0.<br>Bit 7 is the Prescal                    | Bits 6-0 are loaded into the watchdog timer when a refresh is triggered by a consecutive setting of bits WDT (IEN0.6) and SWDT (IEN1.6).<br>Bit 7 is the Prescaler Select (PS) bit. When PS = 1 the watchdog is clocked through an additional divide-by-16 prescaler. |         |       |  |  |  |  |

|                               | Bit Map     |                                                               |                                                                                                                                                                                                                                                                       |         |       |  |  |  |  |

| 7                             | 6           | 6         5         4         3         2         1         0 |                                                                                                                                                                                                                                                                       |         |       |  |  |  |  |

| PS                            |             | Watchdog Timer Reload Value                                   |                                                                                                                                                                                                                                                                       |         |       |  |  |  |  |

| PCON: POWER CONTROL REGISTER |                                                                                                            |                                                                      |                          |                  |                  |                |        |               |  |

|------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------|------------------|------------------|----------------|--------|---------------|--|

| Address                      | Reset Value                                                                                                |                                                                      |                          |                  | Descrip          | tion           |        |               |  |

| 87h                          | 00h                                                                                                        | PCON is u                                                            | used for g               | eneral power c   | ontrol. Bits 6-4 | are reserved.  |        |               |  |

|                              |                                                                                                            | Position                                                             | sition Name Bit Function |                  |                  |                |        |               |  |

|                              | PCON.7 SMOD When set, doubles the baud rate of serial port 0 in modes 1, 2, and 3. F details, see page 52. |                                                                      |                          |                  |                  |                |        | 2, and 3. For |  |

|                              |                                                                                                            | PCON.3<br>PCON.2                                                     | Canaral Purnosa Flags    |                  |                  |                |        |               |  |

|                              |                                                                                                            | PCON.1 PD Power-Down: setting to 1 invokes power down (see page 58). |                          |                  |                  |                |        | ).            |  |

|                              |                                                                                                            | PCON.0                                                               | IDL                      | Idle: setting to | 1 invokes idle   | mode (see page | e 58). |               |  |

|                              | Bit Map                                                                                                    |                                                                      |                          |                  |                  |                |        |               |  |

| 7                            | 6                                                                                                          |                                                                      | 5 4 3 2 1 0              |                  |                  |                |        |               |  |

| SMOD                         | -                                                                                                          |                                                                      | _                        | – GF1 GF0 PD IDL |                  |                |        |               |  |

#### TCON: TIMER/COUNTER CONTROL

| Address | Reset Value |          |                                                                                                                 |                                                                                                                | Descrip                                                                                                                                       | tion                |                 |            |  |

|---------|-------------|----------|-----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|------------|--|

| 88h     | 00h         |          | TCON, along with TMOD, controls Timer 0 and Timer 1 properties. For more detail, see the discussion on page 45. |                                                                                                                |                                                                                                                                               |                     |                 |            |  |

|         |             | Position | Name                                                                                                            |                                                                                                                |                                                                                                                                               | <b>Bit Function</b> |                 |            |  |

|         |             | TCON.7   | TF1                                                                                                             |                                                                                                                | ow flag, set by h<br>tware; automation                                                                                                        |                     |                 |            |  |

|         |             | TCON.6   | TR1                                                                                                             | Timer 1 run co                                                                                                 | ontrol bit. If clea                                                                                                                           | red, Timer 1 sto    | ps.             |            |  |

|         |             | TCON.5   | TF0                                                                                                             |                                                                                                                | Timer 0 overflow flag, set by hardware when Timer 0 overflows. Can be cleared by software; automatically cleared when interrupt is processed. |                     |                 |            |  |

|         |             | TCON.4   | TR0                                                                                                             | Timer 0 run control bit. If cleared, Timer 0 stops.                                                            |                                                                                                                                               |                     |                 |            |  |

|         |             | TCON.3   | IE1                                                                                                             | Interrupt 1 Edge: Set by hardware when pin INT1 triggers an interrupt.<br>Cleared when interrupt is processed. |                                                                                                                                               |                     |                 |            |  |

|         |             | TCON.2   | IT1                                                                                                             | Interrupt 1 Type: Selects falling edge (1) or low level (0) on INT1 pin to trigger an interrupt.               |                                                                                                                                               |                     |                 |            |  |

|         |             | TCON.1   | IE0                                                                                                             |                                                                                                                | ge: Set by hardv<br>interrupt is proc                                                                                                         |                     | NT0 triggers an | interrupt. |  |

|         |             | TCON.0   | IT0                                                                                                             | -0 Interrupt 0 Type: Selects falling edge (1) or low level (0) on INT0 pin to trigger an interrupt.            |                                                                                                                                               |                     |                 |            |  |

|         |             |          |                                                                                                                 | Bit                                                                                                            | Мар                                                                                                                                           |                     |                 |            |  |

| 7       | 6           |          | 5                                                                                                               | 4                                                                                                              | 3                                                                                                                                             | 2                   | 1               | 0          |  |

| TF1     | TR1         | Т        | F0                                                                                                              | TR0                                                                                                            | IE1                                                                                                                                           | IT1                 | IE0             | IT0        |  |

| TMOD: TI | MOD: TIMER/COUNTER MODE CONTROL |                                                                                                             |      |                                                                               |                                                                   |                  |                 |             |  |

|----------|---------------------------------|-------------------------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-----------------|-------------|--|

| Address  | Reset Value                     | Description                                                                                                 |      |                                                                               |                                                                   |                  |                 |             |  |

| 89h      | 00h                             | TMOD, along with TCON, controls Timer 0 and Timer 1 properties. For more detail, see discussion on page 45. |      |                                                                               |                                                                   |                  |                 |             |  |

|          |                                 | Position                                                                                                    | Nam  | e                                                                             |                                                                   | Bit Functio      | on              |             |  |

|          |                                 | TMOD.7                                                                                                      | GATE | E1 Setting (                                                                  | GATE1 allows IN                                                   | NT1 to act as an | external gate f | or Timer 1. |  |

|          |                                 | TMOD.6                                                                                                      | C/T  | 1 Counter,                                                                    | /Timer selector f                                                 | for Timer 1: 0 = | timer; 1 = coun | ter.        |  |

|          |                                 | TMOD.5<br>TMOD.4                                                                                            |      | M1-1<br>M0-1 M1-1 and M0-1 select the timer/counter 1 mode (see table below). |                                                                   |                  |                 |             |  |

|          |                                 | TMOD.3                                                                                                      | GATE | E0 Setting (                                                                  | Setting GATE0 allows INT0 to act as an external gate for Timer 0. |                  |                 |             |  |

|          |                                 | TMOD.2                                                                                                      | C/T( | 0 Counter,                                                                    | Counter/Timer selector for Timer 0: 0 = timer; 1 = counter.       |                  |                 |             |  |

|          |                                 | TMOD.1<br>TMOD.0                                                                                            |      | M1-0<br>M0-0 M1-0 and M0-0 select the timer/counter 0 mode (see table below). |                                                                   |                  |                 |             |  |

|          |                                 |                                                                                                             |      | Bit                                                                           | Мар                                                               |                  |                 |             |  |

| 7        | 6                               | 5                                                                                                           |      | 4                                                                             | 3                                                                 | 2                | 1               | 0           |  |

| GATE1    | C/T1                            | M1·                                                                                                         | 1    | M0-1                                                                          | GATE0                                                             | C/T0             | M1-0            | M0-0        |  |

| M1-x | M0-x | TMOD: Timer 0 / Timer 1 Function Table                                                                   |  |  |  |  |  |  |  |

|------|------|----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 0    | 0    | 13-bit Counter/Timer; the 3 high order bits of TLx are unused (undetermined).                            |  |  |  |  |  |  |  |

| 0    | 1    | 16-bit Counter/Timer.                                                                                    |  |  |  |  |  |  |  |

| 1    | 0    | 8-bit auto-reload Counter/Timer. The reload value is in THx. When TLx overflows, THx is copied into TLx. |  |  |  |  |  |  |  |

| 1    | 1    | Timer 1: Halt. Timer 0: Two independent 8-bit Timers / Counters (see page 45).                           |  |  |  |  |  |  |  |

| TLO: TIME | TL0: TIMER 0 (LOW BYTE) |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|-----------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Address   | Reset Value             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 8Ah       | 00h                     | Less significant byte of 16-bit Timer 0; the other byte is TH0. Timer 0 can be configured (using the TMOD register) as either a timer or a counter, and in any of four operating modes.<br>In timer mode, Timer 0 is incremented once every 12 clock cycles.<br>In counter mode, Timer 0 is incremented when a falling edge is observed at pin T0 (PORT3[4]).<br>Timer 0 can also be affected by the INT0 pin and the TCON register; see page 45 for details. |  |  |  |  |  |  |  |

| TL1: TIME | TL1: TIMER 1 (LOW BYTE) |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|-----------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Address   | Reset Value             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 8Bh       | 00h                     | Less significant byte of 16-bit Timer 1; the other byte is TH1. Timer 1 can be configured (using the TMOD register) as either a timer or a counter, and in any of four operating modes.<br>In timer mode, Timer 1 is incremented once every 12 clock cycles.<br>In counter mode, Timer 1 is incremented when a falling edge is observed at pin T1 (PORT3[5]).<br>Timer 1 can also be affected by the INT1 pin and the TCON register; see page 45 for details. |  |  |  |  |  |  |  |

| ТНО: ТІМЕ | TH0: TIMER 0 (HIGH BYTE) |                                                                                            |  |  |  |  |  |  |  |  |

|-----------|--------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Address   | Reset Value              | et Value Description                                                                       |  |  |  |  |  |  |  |  |

| 8Ch       | 00h                      | The more significant byte of 16-bit Timer 0; the other byte is TL0. For function, see TL0. |  |  |  |  |  |  |  |  |

| TH1: TIME | TH1: TIMER 1 (HIGH BYTE) |                                                                                            |  |  |  |  |  |  |  |

|-----------|--------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Address   | Reset Value              | Description                                                                                |  |  |  |  |  |  |  |

| 8Dh       | 00h                      | The more significant byte of 16-bit Timer 1; the other byte is TL1. For function, see TL1. |  |  |  |  |  |  |  |

|           |                          | TH1 can also set the baud rate for serial port 0; see discussion on page 52.               |  |  |  |  |  |  |  |

| CKCON: 0 | CKCON: CLOCK CONTROL |                           |                                                                                                                                                                                                                                                                                                                                                              |         |         |       |         |       |         |       |         |

|----------|----------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|---------|-------|---------|-------|---------|

| Address  | Reset Value          | Description               |                                                                                                                                                                                                                                                                                                                                                              |         |         |       |         |       |         |       |         |

| 8Eh      | 00h                  | the cycle for should be l | ts 7-3 are not implemented; bits 2-0 control the length of the memory access timer, stretching<br>e cycle for slow memory types. Because this device contains high speed RAM, CKCON[2:0]<br>ould be left at the default high-speed setting. Any changes will degrade device performance.<br>(CON[2:0] stretches the memory cycle access time as shown below: |         |         |       |         |       |         |       |         |

|          |                      |                           | ckcon.2                                                                                                                                                                                                                                                                                                                                                      | ckcon.1 | ckcon.0 | value | memaddr | memrd | memaddr | memwr |         |

|          |                      |                           | 0                                                                                                                                                                                                                                                                                                                                                            | 0       | 0       | 0     | 1       | 1     | 2       | 1     |         |

|          |                      |                           | 0                                                                                                                                                                                                                                                                                                                                                            | 0       | 1       | 1     | 2       | 2     | 3       | 1     |         |